# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

1970

# Synthesis heuristics for large asynchronous sequential circuits

Robert Judson Smith

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electrical and Computer Engineering Commons

**Department: Electrical and Computer Engineering**

#### **Recommended Citation**

Smith, Robert Judson, "Synthesis heuristics for large asynchronous sequential circuits" (1970). Doctoral Dissertations. 2047.

https://scholarsmine.mst.edu/doctoral\_dissertations/2047

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# SYNTHESIS HEURISTICS FOR LARGE ASYNCHRONOUS SEQUENTIAL CIRCUITS

Ъу

ROBERT JUDSON SMITH II, 1944-

# A DISSERTATION

Presented to the Faculty of the Graduate School of the

UNIVERSITY OF MISSOURI - ROLLA

In Partial Fulfillment of the Requirements for the Degree

DOCTOR OF PHILOSOPHY

in

ELECTRICAL ENGINEERING

1970

T2369 c.1 88 pages

Weilert R. Alcom

Frank J Kein

190822

#### ABSTRACT

Many well-known synthesis procedures for asynchronous sequential circuits produce minimal or near-minimal results, but are practical only for very small problems. These algorithms become unwieldy when applied to "large" circuits with, for example, three or more input variables and twenty or more internal states.

New heuristic procedures are described which permit the synthesis of very large machines. Although the resulting designs are generally not minimal, the heuristics are able to produce nearminimal solutions orders of magnitude more rapidly than the minimal algorithms.

A method for specifying sequential circuit behavior is presented. Input-output sequences define submachines or modules. When properly interconnected, these modules form the required sequential circuit. It is shown that the waveform and interconnection specifications may easily be translated into flow table form.

A large flow table simplification heuristic is developed. The algorithm may be applied to tables having hundreds of rows, and handles both normal and non-normal mode circuit specifications.

Nonstandard state assignment procedures for normal, fundamental mode asynchronous sequential circuits are examined. An algorithm for rapidly generating large flow table internal state assignments is proposed.

The algorithms described have been programmed in PL/1 and incorporated into an automated design system for asynchronous circuits; the system also includes minimum and near-minimum variable state assignment generators, a code evaluation routine, a design equation

generator, and two Boolean equation simplification procedures. Large sequential circuits designed using the system illustrate the utility of the heuristic procedures.

### ACKNOWLEDGEMENTS

The author would like to express his appreciation to Dr. J. H. Tracey for his guidance, advice and patience during the studies which led to this dissertation. Thanks are also extended to the author's wife, Jean-Marie, and to Sandra Wilson for their diligent typing of this manuscript.

The research described in this dissertation was supported in part by National Science Foundation Grant GK 2017.

# TABLE OF CONTENTS

|         |      | Page                                                     |

|---------|------|----------------------------------------------------------|

|         |      | ii                                                       |

| ACKNOWL | EDGE | MENTSiv                                                  |

| LIST OF | ILL  | USTRATIONSvii                                            |

| LIST OF | TAB  | LESix                                                    |

| I.      | INT  | RODUCTION1                                               |

| II.     | A S  | PECIFICATION TECHNIQUE FOR LARGE ASYNCHRONOUS SEQUENTIAL |

|         | CIR  | CUITS9                                                   |

|         | Α.   | Background9                                              |

|         | в.   | Sequential Circuit Specification Using Input/Output      |

|         |      | Sequences                                                |

|         | С.   | Conversion to Flow Table Form                            |

|         | D.   | A Sequence Translation Computer Program19                |

|         | Ε.   | Extensions and Results20                                 |

| III.    | RED  | UCTION OF LARGE INCOMPLETELY SPECIFIED FLOW TABLES22     |

|         | Α.   | Background22                                             |

|         | в.   | A Flow Table Simplification Heuristic30                  |

|         | С.   | Programmed Implementation and Results43                  |

| IV.     | STA  | TE ASSIGNMENTS FOR LARGE ASYNCHRONOUS SEQUENTIAL         |

|         | CIR  | CUITS50                                                  |

|         | Α.   | Background50                                             |

|         | в.   | A Nonstandard State Assignment Procedure for Large Flow  |

|         |      | Tables55                                                 |

|         | С.   | An Example59                                             |

|         | D.   | A Programmed Implementation of the Procedure61           |

|         |      | Summary                                                  |

|         | E.   | Summary                                                  |

| v.      | AN . | Page AUTOMATED DESIGN SYSTEM66                        |

|---------|------|-------------------------------------------------------|

|         | Α.   | System Overview                                       |

|         | В.   | State Assignment Generation and Evaluation Routines69 |

|         | c.   | Design Equation Generation and Reduction70            |

|         | D.   | Conclusions71                                         |

| APPENDI | x 1. | Experimental Flow Table Simplification72              |

| APPENDI | х 2. | Summary of State Assignment Experiments75             |

| BIBLIOG | RAPH | Y                                                     |

| WTT A   |      |                                                       |

# LIST OF ILLUSTRATIONS

| Figure | s p                                                                            | age  |

|--------|--------------------------------------------------------------------------------|------|

| 1.     | A Typical Flow Table Example A                                                 | 1    |

| 2.     | Asynchronous Sequential Circuit Model                                          | 2    |

| 3.     | A Typical Sequence Specification                                               | .12  |

| 4.     | Sequence Description Example B                                                 | .15  |

| 5.     | Translation of a Sequence into a Flow Table Segment                            | .16  |

| 6.     | Sequence Flow Table Segments for Example B                                     | .17  |

| 7.     | The Module Flow Table for Example B                                            | .18  |

| 8.     | Flow Table Representation of Example B                                         | .18  |

| 9.     | Modular Organization of Example B                                              | . 20 |

| 10.    | Implication Table for Flow Table A                                             | . 24 |

| 11.    | Flow Table and Corresponding Representation                                    | .29  |

| 12.    | Discovery of a New Compatibility Class                                         | . 34 |

| 13.    | Formation of the New Class                                                     | . 34 |

| 14.    | Addition of a Row to the New Class                                             | . 35 |

| 15.    | A Recheck Opportunity                                                          | . 37 |

| 16.    | Flow Table Segment After Rechecking                                            | . 38 |

| 17.    | Partial Flow Table and Single Implication Chain                                | . 39 |

| 18.    | Flow Table Simplification Using Single Implication Chains                      | .41  |

| 19.    | Reorganization of a Reduced Flow Table                                         | . 42 |

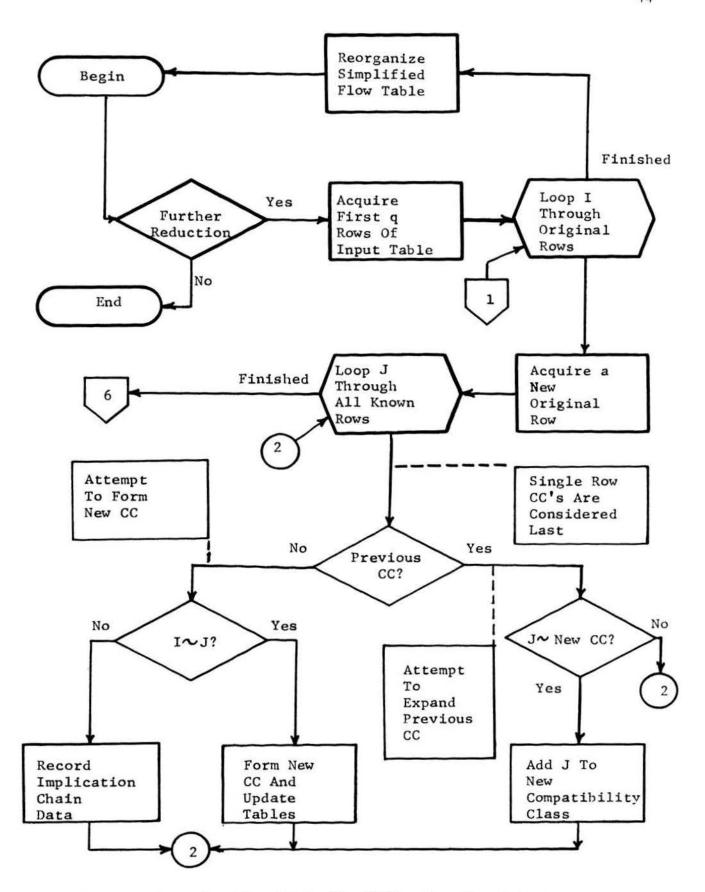

| 20a.   | The Flow Table Simplification Heuristic                                        | . 44 |

| 20ь.   | The Flow Table Simplification Heuristic (Recheck, Chaining and Reorganization) | . 45 |

| 21.    | An Example of the Effect of Look Ahead on Simplification                       | . 47 |

| 22.    | State Assignment Containing a Critical Race                                    | . 51 |

| Figure | Pag                                                                 |

|--------|---------------------------------------------------------------------|

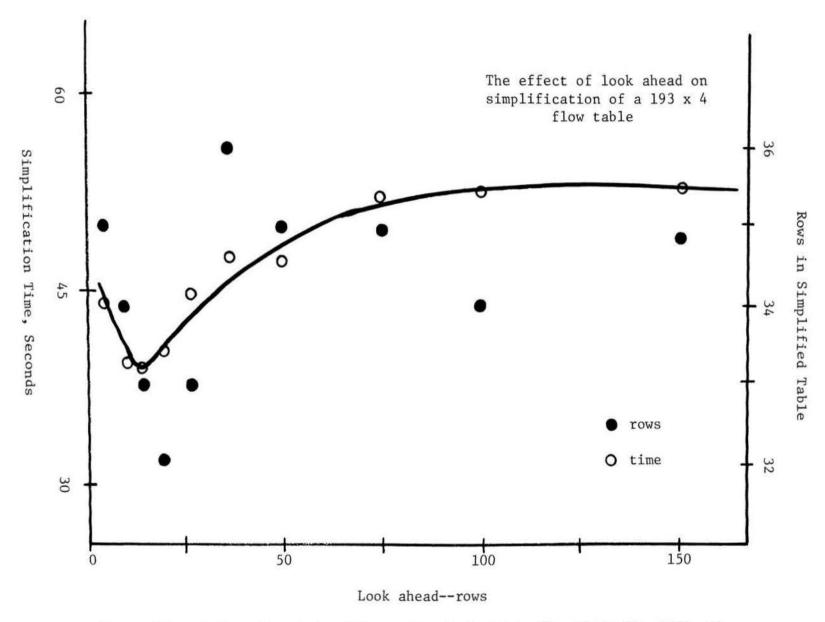

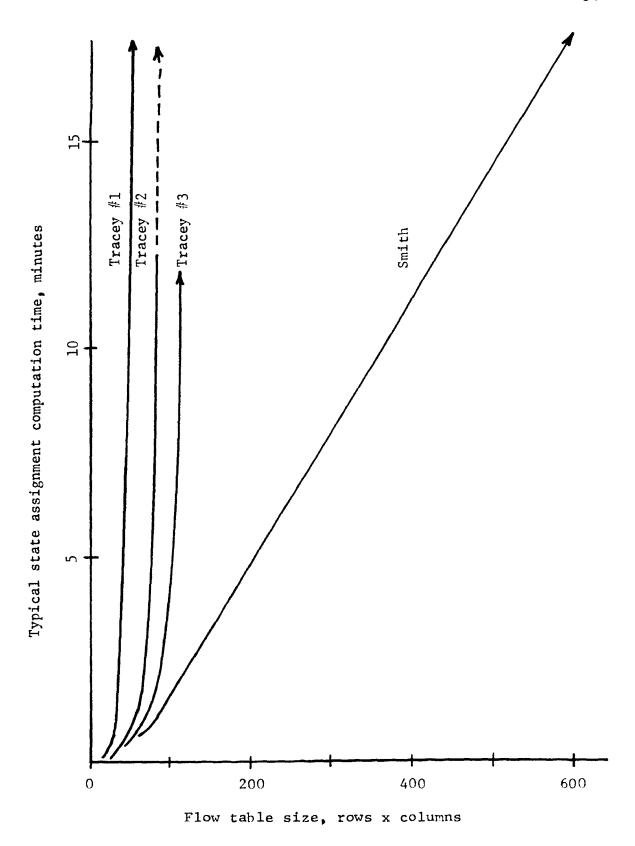

| 23.    | Flow Table Size Versus Typical State Assignment Time Tracey Methods |

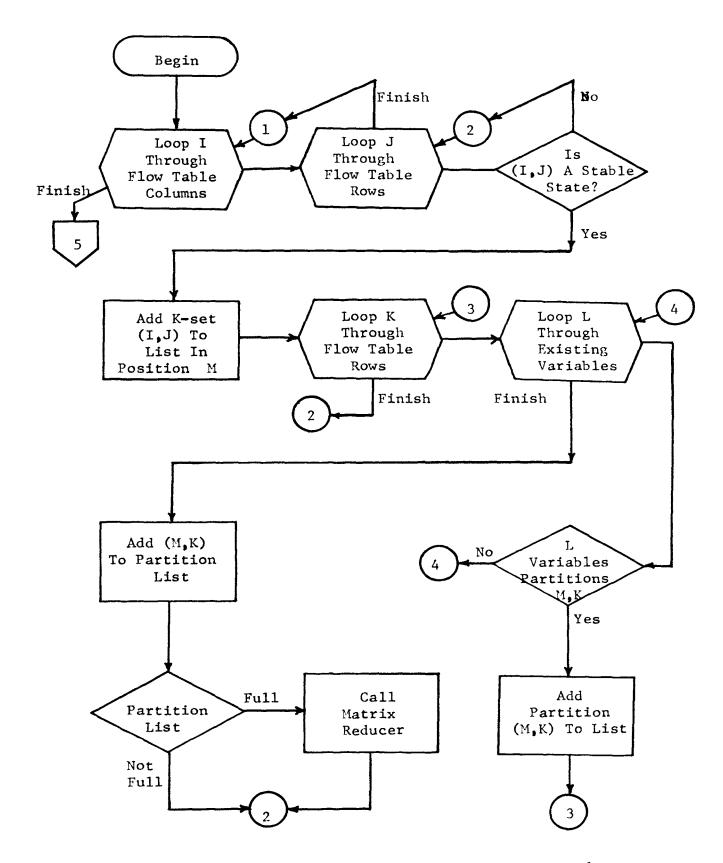

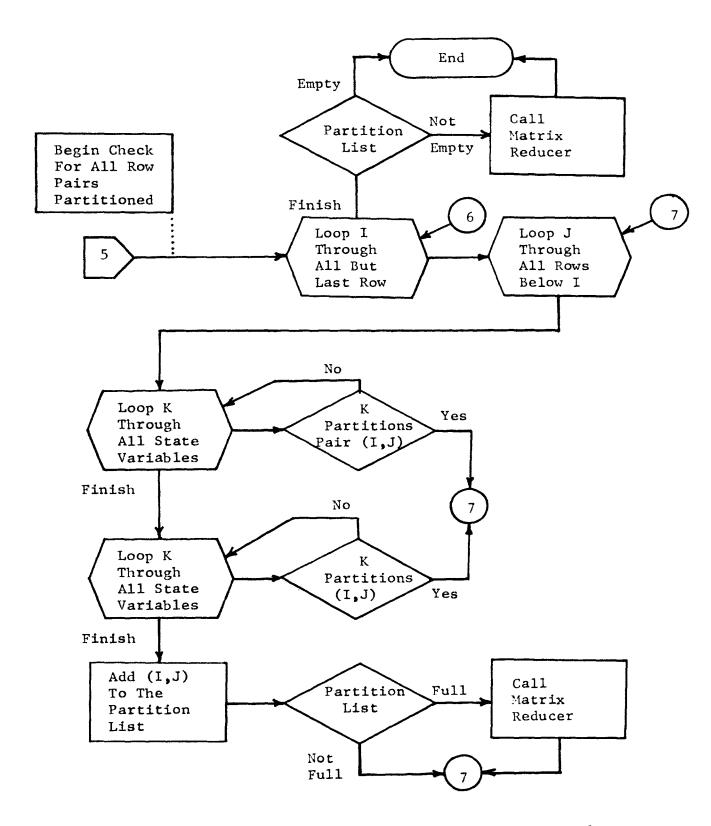

| 24a.   | The Large Flow Table State Assignment Procedure (K-set Partitions)5 |

| 24b.   | The Large Flow Table State Assignment Procedure (Row Partitions)    |

| 25.    | Flow Table D5                                                       |

| 26.    | K-set Partition List for Flow Table D6                              |

| 27.    | State Assignment for Flow Table D6                                  |

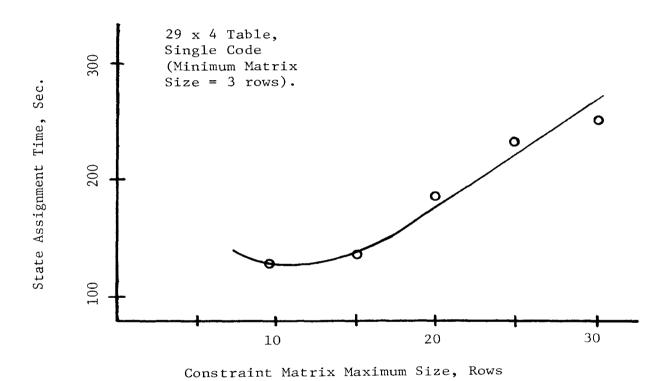

| 28.    | The Effect of Segment Size on Assignment Generation Time            |

| 29.    | Comparison of Four State Assignment Techniques6                     |

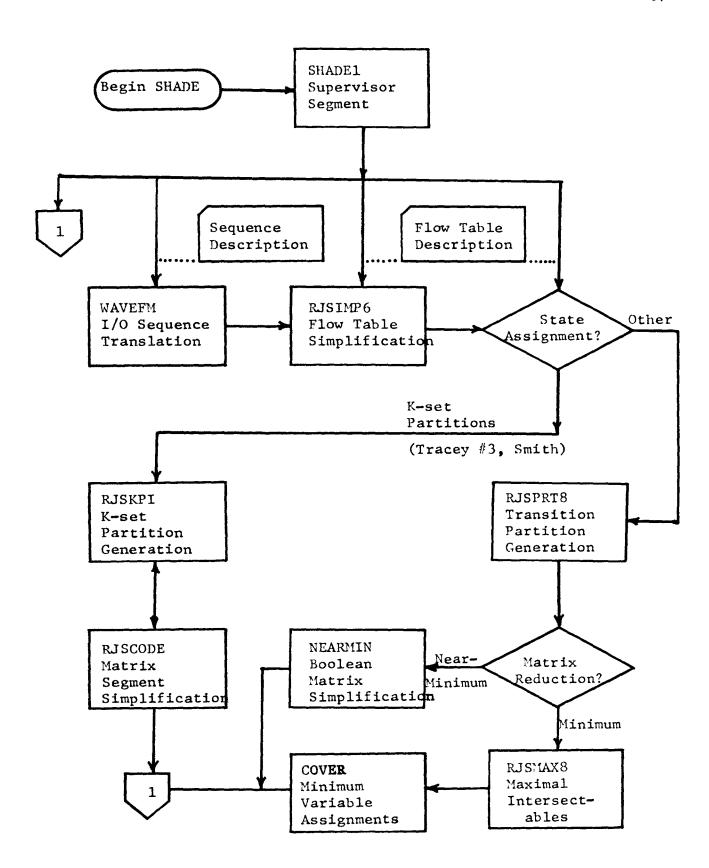

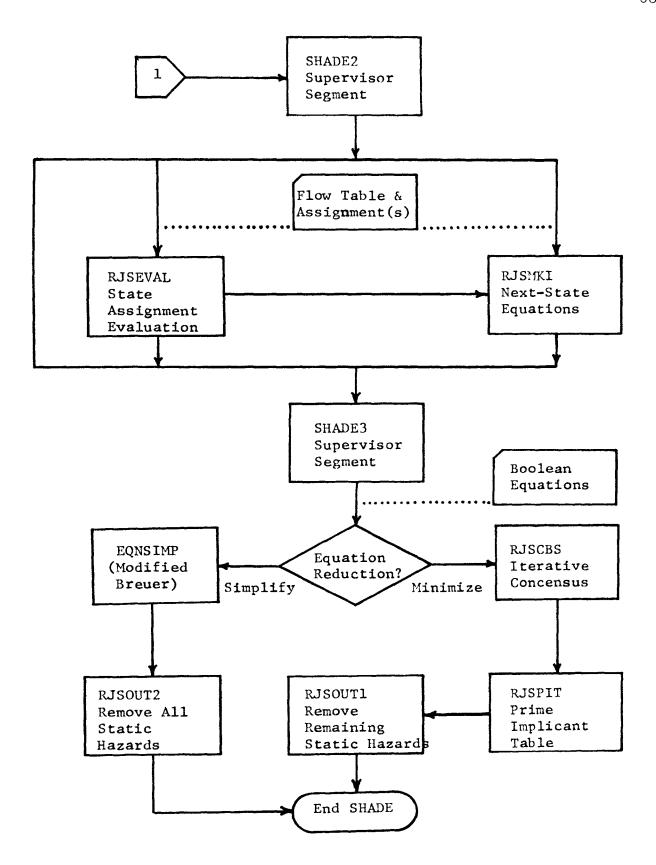

| 30a.   | The SHADE System6                                                   |

| 30ь.   | The SHADE System (continued)6                                       |

# LIST OF TABLES

| ı.   | Simplification of Several Large Flow Tables                  | Page49 |

|------|--------------------------------------------------------------|--------|

| II.  | Varying Look Ahead in Simplification of a 193 x 4 Flow Table | 73     |

| III. | Experimental Flow Table Simplification Results               | 74     |

| IV.  | State Assignment Experiments                                 | 76     |

### I. INTRODUCTION

Sequential circuits which operate without synchronizing (or clock) signals are commonly called asynchronous sequential circuits.

An important advantage of asynchronous design is that the circuit may respond to input changes at basic device speed, rather than awaiting the arrival of clock pulses.

The operation of an asynchronous sequential circuit is often described by means of a flow table (see figure 1). The flow table

|   | <sup>I</sup> 1 | <sup>1</sup> 2 | <sup>1</sup> 3 | <sup>1</sup> 4 |

|---|----------------|----------------|----------------|----------------|

| 1 | 1)/00          | 2              | 1)/11          | 6              |

| 2 | 1              | 2/11           | 4              | 3              |

| 3 | -              | 6              | 1              | 3/00           |

| 4 | <b>4</b> /10   | 6              | 4/10           | 6              |

| 5 | 4              | (5)/10         | 11             | 6              |

| 6 | 1              | <b>6</b> /01   | 1              | 6/00           |

Figure 1. A Typical Flow Table -- Example A

columns represent input states, while the rows represent internal states assumed by the machine. Each flow table entry specifies the next-state resulting from a given input and internal state.

A circuit is said to be operating in the fundamental mode if no change in input state is allowed unless the circuit is stable, i.e., the next-state of the circuit is the present state. Output specifications are usually associated with stable next states. If the next-

state is not the present state, the latter is termed unstable and implies a transition to another state. In normal mode circuits, transitions must be made directly to a stable state. This work is largely concerned with normal, fundamental mode asynchronous sequential circuits.

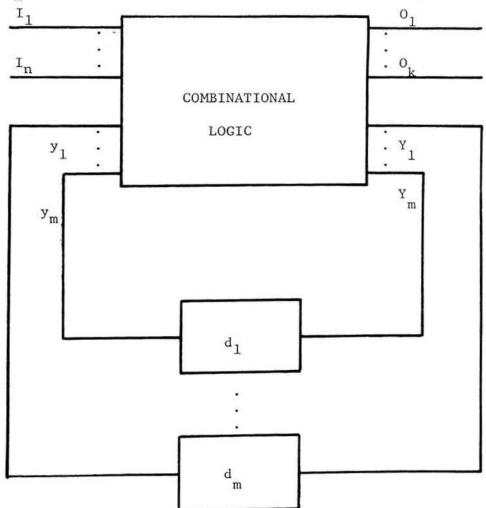

The circuit model to be used throughout is shown in figure 2. The sequential circuit is composed of a set of inputs  $I_1, \ldots, I_n$ , present state variables  $y_1, \ldots, y_m$ , outputs  $0_1, \ldots, 0_k$ , and next-state variables  $Y_1, \ldots, Y_m$ , which after passing through asynchronous delays  $d_1, \ldots, d_m$  become present state variables. The delays usually represent

Figure 2. Asynchronous Sequential Circuit Model.

the propagation times of next-state signals through the combinational logic.

A commonly employed manual synthesis procedure begins with the formulation of a verbal or diagrammatic circuit behavior description. The circuit description is translated into the form of a flow table, usually employing a non-algorithmic procedure. The flow table is then minimized or simplified using one of several available algorithms 2,3,4,5.

A satisfactory internal state assignment must then be found for the reduced flow table. The greatest difficulty in making an asynchronous sequential circuit state assignment is avoiding critical races. A critical race exists when, due to unequal signal transmission delays, there is a possibility that the stable state reached is not the intended one. Huffman<sup>6</sup>, Liu<sup>7</sup>, and others have described universal state assignments which depend only on flow table size. Universal, or standard assignments, are relatively easy to construct and are independent of flow table structure. Tracey<sup>8</sup> has shown how to construct nonstandard codes (dependent on flow table structure) which permit no critical races. Nonstandard codes generally have fewer state variables and yield simpler circuits than standard codes.

Once a critical-race-free code has been generated, the designer forms a transition table by substituting internal state codes for next-state entries in the flow table. Excitation and output Boolean equations are then derived from the transition table. Finally, these design equations are simplified and converted to hardware implementation form.

The above manual synthesis procedure is practical only when

applied to quite small circuits. For larger sequential circuits, several authors have described automated design systems which perform steps of the manual procedure.

Elsey<sup>9</sup> in 1963 described a machine language computer program which accepted a primitive (one stable state per row) flow table. Very elementary simplification procedures were applied to the flow table and a non-normal mode standard assignment was generated. Unsimplified design equations were produced by reading directly from the transition table. Although Elsey's program produced design equations with a large amount of simplification still required, it was able to synthesize extremely large flow tables: a 117 column by 33 row flow table design was produced in 213 seconds.

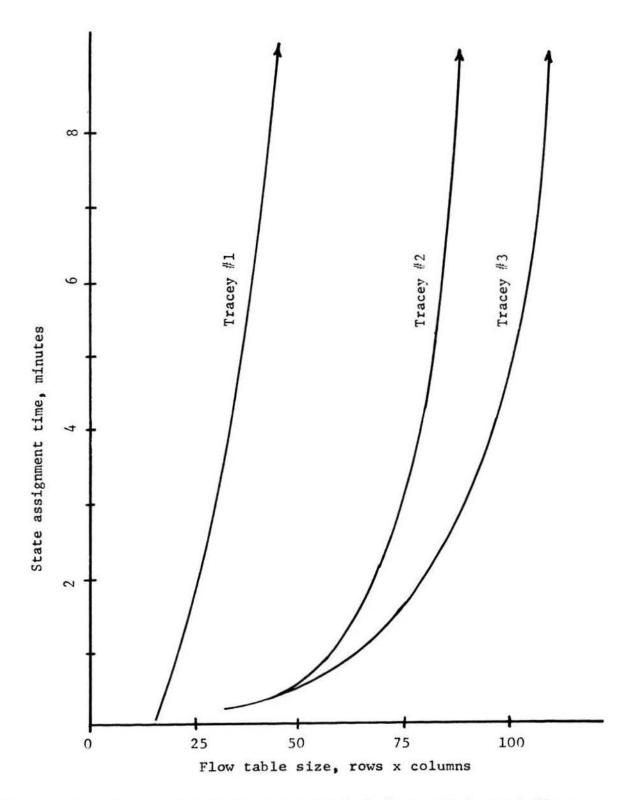

Smith, et. al., have written a PL/1 program<sup>10</sup> which accepts a simplified flow table description of an asynchronous sequential circuit. Either minimum or near-minimum variable state assignments may be generated. An assignment evaluation algorithm predicts which of several codes generated will yield the simplest design equations. A complete set of design equations is then produced without constructing transition or excitation tables. Each design equation is simplified to an irredundant sum of prime implicants, and static hazards are removed. This automated design system functions well for flow tables of up to about 15 rows by four columns, but becomes prohibitively slow for larger flow tables.

Burton and Noaks, in a recent paper, 11 have briefly mentioned any asynchronous design automation program under development. Given a simplified flow table, a redundant state assignment is generated which allows the excitation equations to be readily derived. The

code is then simplified by examining the design equations resulting from the redundant assignment. The program does not presently generate output equations. Since the system is still under development, no performance data have been published.

Tan<sup>12</sup> recently described a computer aided procedure for realization of asynchronous sequential circuits. The circuit to be synthesized is described by a simplified flow table and several state assignments are constructed. The code exhibiting the least amount of state variable dependency is selected for use. Design equations are not generated or simplified.

All of the synthesis procedures described above—both manual and programmed—have serious limitations. The manual procedure can be used only on flow tables having fifty or less next—state entries. Manually exercised minimum or near—minimum variable state assignment algorithms become unmanageable for flow tables of more than eight rows. Manual simplification (or minimization) of Boolean equations of more than seven variables is generally difficult.

None of the automated design systems described adequately deal with the highly significant problem of flow table simplification. The nonstandard state assignment techniques described in (6,7,8) all appear to be unsuitable for large flow tables because they require the manipulation of extremely large amounts of data. Elsey's non-normal mode realizations lead to unnecessarily complex excitation equations. None of the systems cited are capable of simplifying large systems of Boolean equations.

This dissertation describes several algorithms which have been

developed expressly to synthesize very large asynchronous sequential circuits. Emphasis has been placed on reducing synthesis costs without introducing large amounts of hardware redundancy. Heuristic procedures have been used to improve synthesis speed, at the cost of circuit minimality. Since minimal solutions for designs of the size considered are unknown it is not possible to evaluate heuristic solutions in terms of minimal designs. The procedures described herein will rather be justified by comparing their performance on medium and small circuits with previously known algorithms, and by demonstrating their capability to synthesize circuits far larger than the capacity of other algorithms.

A design automation system has been developed to facilitate comparison of various synthesis procedures. With this system, problem descriptions may be entered at any of six stages in the automated design procedure, and synthesis may be interrupted at any later stage. Several of the minimal or near-minimal techniques employed in the system are adoptions of programs previously developed by the author. 10

Other routines, which will not be described in detail, include a state assignment evaluation program<sup>13</sup>, a Boolean equation sum of products simplification routine<sup>14</sup>, and a static hazard removal program. Although the programming system currently operates in a batch processing environment, it is intended to eventually be available in conversational mode.

The asynchronous sequential circuit design programs previously developed require that the circuit be initially described in the form of a flow table. However, complex sequential circuits are usually not perceived initially as flow tables. Often designers think first of

of responses to specific sequences of input states. A specification for the required circuit is then derived by assembling the sequence specifications in some desired manner. The result—usually a very informal description—must then be translated into flow table form. For large circuits (with perhaps five or more inputs and many outputs), the task of writing a flow table description may become quite formidable—a flow table representing a circuit with five input variables has 32 columns.

Chapter Two describes a sequential circuit specification technique which closely resembles the informal "response to input sequences" approach which precedes flow table construction. It is shown that the resulting specification may be translated into either a single flow table, or into a network of interconnected, relatively simple module descriptions.

The simplification of large flow tables is not performed by any of the normal mode design automation systems cited. Since large sequential circuit flow tables are almost always generated in non-minimal form, simplification is desirable in order to reduce large flow table synthesis costs and hardware complexity. Much work has been done in the area of flow table minimization; however, it is shown that minimization is impractical for large flow tables. Little has been published concerning simplification of large flow tables.

Chapter Three describes a heuristic flow table simplification algorithm. It is based on easily detected compatibility relationships and immediate table reduction. A programmed version of the algorithm allows the user to influence the "cost" (i.e., computer time consumed) of a flow table simplification. The procedure may be applied to

either normal or non-normal flow tables.

State assignment techniques incorporated in known synthesis systems have been found inadequate for large flow tables. Chapter Four examines presently available coding procedures and proposes an extension of Tracey's method two $^8$  for use on large flow tables.

# II. A SPECIFICATION TECHNIQUE FOR LARGE ASYNCHRONOUS SEQUENTIAL CIRCUITS

Sequential circuit specifications as originally conceived by designers seldom resemble the familiar flow table form. Often, a designer originates a sequential circuit behavior description in the form of a word statement, or a series of "responses to inputs", which after evaluation and modification is manually translated into flow table or hardware circuit form.

An important facet of a design automation system ignored by previously developed systems 10,11,12 is the translation of designs in originally conceived form into the more tractable flow table form. This chapter presents a sequential circuit description technique which closely resembles the "input/output" thought process and is easily translated into flow table form.

## A. Background

Altman<sup>15</sup> has described a method for translating a sequence of input/output (I/O) specification pairs into a flow table having one stable and one unstable state per row. Each row's stable state corresponds to the input state for an input/response specification; the output associated with this stable state is the specified circuit response. An unstable next state entry in the flow table row corresponding to the previous specification is the only transition leading to the stable state. Likewise, an unstable next state entry causes the transition to the following stable state.

A sequence, as used here, consists of a set of I/O specifications which follow one another such that each has at most one predecessor.

A problem with a sequence description of a sequential circuit is the

possibility of having to repeat long lists of specifications in order to express alternate behaviors at a "branch point;" each string of inputs to which the circuit is to react in a specified manner must be explicitly recorded.

Furthermore, not every sequential circuit can be specified by a finite list of I/O pairs. For example, any circuit which is to produce a repeated sequence of outputs in response to inputs until a certain series of inputs is applied cannot be specified by a single I/O sequence.

A more general formulation of the above problem is the inability of single sequence specifications to describe cyclic behaviors of indeterminate duration.

An input/response description method will next be described which overcomes the above difficulties. It will be shown that this extension of the previously described method increases only slightly the effort required to translate I/O specifications into flow table form.

B. Sequential Circuit Specification Using Input/Output Sequences

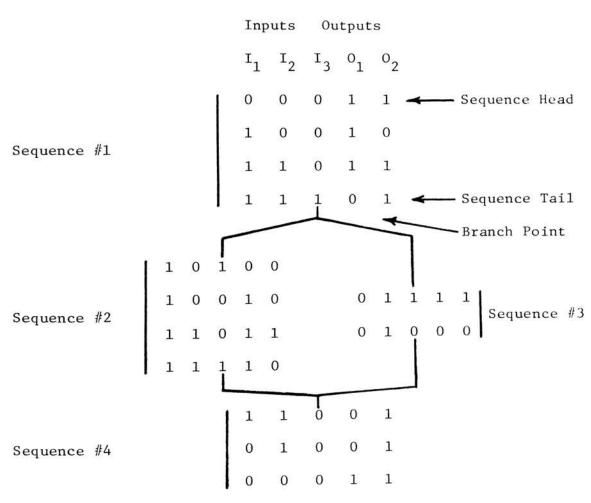

The sequence may be used as a building block to describe more complex circuit behavior. The first I/O pair of a sequence will be called the head of the sequence, and the last specification the tail. At some point in the I/O description of a sequential circuit, it may be desirable to indicate that one of two or more alternate sequences will be followed, depending on the next circuit input. At such a branch point, the sequence previously under development is terminated and the heads of the alternate sequences follow its tail.

Since the sequences are often developed and recorded serially, it

is convenient to introduce the "FOLLOWS" note. This device is used to record, for appropriate sequence heads, the labels associated with preceding sequence tails. Note that a sequence may FOLLOW more than one tail. Conversely, more than one sequence may FOLLOW a tail specification (or a group of them), so long as each head input state is not the head of another of the following sequences.

Figure 3 illustrates the terminology introduced above by showing the sequence representation of a circuit described with a series of I/O pairs.

It is sometimes inconvenient to use "FOLLOWS" notation to describe sequence relationships. For example, the tail of sequence four of figure 3 may be FOLLOWed by HEAD1, but at the time sequence one is recorded the preceding tail name may not be known. A "GO TO" note is provided to simplify such cases. The GO TO instruction, applied to sequence tail specifications, merely lists the labels of the following sequence heads.

Certain other notation conveniences for recording sequences are also adopted. A "\*" or "-" in any position indicates that an input or output line is unspecified for an I/O pair. A blank in any position indicates that the value of the corresponding line has not changed; the last specified value for the variable thus replaces the blank. The latter feature eliminates the needless reproduction of long strings of unchanging variables.

The possibility of leaving some variables unspecified complicates the problem of detecting improper sequences: no specification may require or <a href="imply">imply</a> a change in output without a change in input. Two tests have been devised to detect improper sequences.

Desired response to inputs

| <u>Label</u> | Spe | eci | fic | ati | on | Notes                |

|--------------|-----|-----|-----|-----|----|----------------------|

| HEAD1:       | 0   | 0   | 0   | 1   | 1  |                      |

|              | 1   | 0   | 0   | 1   | 0  |                      |

|              | 1   | 1   | 0   | 1   | 1  |                      |

| TAIL1:       | 1   | 1   | 1   | 0   | 1  |                      |

| HEAD2:       | 1   | 0   | 1   | 0   | O  | FOLLOWS TAIL1        |

| ******       | 1   | 0   | 0   | 1   | 0  |                      |

|              | 1   | 1   | 0   | 1   | 1  |                      |

| TAIL2:       | 1   | 1   | 1   | 1   | 0  |                      |

| HEAD3:       | 0   | 1   | 1   | 1   | 1  | FOLLOWS TAIL1        |

| TAIL3:       | 0   | 1   | 0   | 0   | 0  |                      |

| HEAD4:       | 1   | 1   | 0   | 0   | 1  | FOLLOWS TAIL2, TAIL3 |

| HEAD4.       | 0   | 1   | 0   | 0   | 1  |                      |

| TAIL4:       | 0   | ō   | 0   | 1   | 1  |                      |

b. Sequence specification

Figure 3. A Typical Sequence Specification.

Let the first I/O specification  $W_1$  be composed of input state  $W_1$  and circuit response (output)  $W_1$ ; likewise the second specification is denoted  $W_2$ , composed of  $W_2$  and  $W_2$ .  $W_2$  may properly follow  $W_1$  if:

- 1. At least one input variable specified in both  $^{\rm N}1$  and  $^{\rm N}2$  is 1 in one case and 0 in the other.

- 2. If 1) is not satisfied and  $W_1$  is not a sequence tail, then all of the following must be satisfied: a) Each variable specified in  $N_1$  must correspond to either an identical specified value or a don't care in  $N_2$ ; b) Each variable not specified in  $N_1$  must also be unspecified in  $N_2$ ; c) All output variables specified in  $N_2$  must be specified in  $N_3$  and both must have a common value; d) Output values not specified in  $N_2$  may correspond to either specified or unspecified variables in  $N_3$ .

Rule 2 applies only to input state transitions within a sequence, and reduces to the requirement that  $\mathrm{W}_1$  and  $\mathrm{W}_2$  be indistinguishable.

Consider the possibly improper sequence (4 inputs, two outputs)

W<sub>1</sub> 0\*01 11

W<sub>2</sub> 0101 00,

which fails Test 1. Assuming  $W_1$  is not a sequence tail, application of Test 2a indicates this is an improper sequence—for input state 0101, the specification requires outputs of first 11 then 00. For the pair

W<sub>1</sub> 0101 00

W<sub>2</sub> 0\*01 11,

Test 1 fails. Tests 2a and 2b are satisfied, but Test 2c indicates that this is also an improper specification. For input 0101, the

output is required to be 00 then 11. All parts of Test 2 are, however, satisfied by

Another potential source of difficulty under the proposed description method is the need for unique labels on sequence heads and tails. In order to simplify modification of previously recorded sequences (as design progresses), each I/O specification should have a unique name.

The beginning of a new sequence is implied by a "FOLLOWS" notation. Likewise, a "GO TO" note indicates the end of a sequence. It is not, however, necessary to use a "FOLLOWS" at the start, and a "GO TO" at the end of each sequence. The note "BEGIN" has been adopted to indicate the start of a new sequence; end of a sequence is indicated simply by "END". Sequence heads and tails noted in this manner are assumed to have predecessors and successors which are specified elsewhere.

These notation conventions do not cover the case of a sequence which is implicitly begun or terminated by an <u>explicit</u> reference to, respectively, end of the previous sequence, or beginning of a following sequence. In situations where no notation explicitly indicates a sequence begins or ends, a "FOLLOWS" or "GO TO" instruction referring to the preceding or next sequence is assumed by default. Figure 4 shows a thirteen pair sequence which illustrates the descriptive method presented here.

|            | LABEL    | $\underline{\mathbf{I_1} \ \mathbf{I_2} \ \mathbf{I_3} \ \mathbf{0_1}}$ |   | 3 01 | NOTES |                        |

|------------|----------|-------------------------------------------------------------------------|---|------|-------|------------------------|

| Sequence 1 | ONE      | 0                                                                       | * | *    | 1     | BEGIN                  |

|            | TWO      | 1                                                                       | * | *    | 1     |                        |

| 2          | THREE    | 0                                                                       | 1 | 1    | 1     | (implied sequence end) |

|            | FOUR     | 0                                                                       | 0 | 1    | 0     | FOLLOWS TWO            |

| 3          | FIVE     |                                                                         | 1 | 1    | 0     | FOLLOWS TWO, THREE     |

|            | SIX      |                                                                         | 0 | 1    | 1     |                        |

| - 1        | SEVEN    |                                                                         | 1 | 1    | 1     | GO TO ONE              |

| 4          | EIGHT    | 0                                                                       | 1 | 0    | 1     | FOLLOWS TWO            |

| 1          | NINE     | 0                                                                       | 0 | 0    | 0     | FOLLOWS TWO, EIGHT     |

|            | TEN      |                                                                         | 1 | 0    | 0     |                        |

| 5          | ELEVEN   |                                                                         | 0 | 0    | 0     |                        |

|            | TWELVE   |                                                                         | 1 | 0    | 0     |                        |

|            | THIRTEEN | 0                                                                       | 0 | 0    | 1     | GO TO ONE              |

Figure 4. Sequence Description Example B.

It will next be shown that this type of sequential circuit specification may easily be converted into conventional flow table representation.

# C. Conversion to Flow Table Form

The procedure previously described for converting a sequence to flow table form requires little modification for use under the present scheme. Each input/output pair corresponds to a row of the flow table. Stable state entries (with the specified outputs) appear in all columns corresponding to the input state specification. Thus n unspecified input line values result in 2<sup>n</sup> stable state entries in the appropriate row.

Unstable next-state entries are placed in the preceding row

for each stable state. Since the preceding flow table row represents the last specification in the sequence, the sequence head stable states do not have any unstable next-state entries leading to them.

Consecutive I/O specifications to which proper sequence rule #2 applies are a special case. If there is no stable state in a column of the row  $\mathbb{W}_1$ , the next-state entry for the lower I/O pair  $\mathbb{W}_2$  must be copied into the preceding row position.

Figure 5 shows the flow table segment which exhibits behavior specified by sequence 5 of figure 4.

| $^{\text{I}}_{1}$ | $I_2$ | <sup>1</sup> 3 | $^{\rm o}{}_{\rm 1}$ | STATE       | 000         | 001 | 010         | 011 | 100 | 101 | 110 | 111 |

|-------------------|-------|----------------|----------------------|-------------|-------------|-----|-------------|-----|-----|-----|-----|-----|

| 0                 | 0     | 0              | 0                    | Α           | <b>A</b> /0 |     | В           |     |     |     |     |     |

| 0                 | 1     | 0              | 0                    | A<br>B<br>C | С           |     | <b>B</b> /0 |     |     |     |     |     |

|                   |       |                |                      |             | •           |     |             |     |     |     |     | - 1 |

|                   |       |                |                      | D           |             |     | <b>D</b> /0 |     |     |     |     |     |

| 0                 | 0     | 0              | 1                    | E           | <b>E</b> /1 |     |             |     |     |     |     |     |

Figure 5. Translation of a Sequence into a Flow Table Segment.

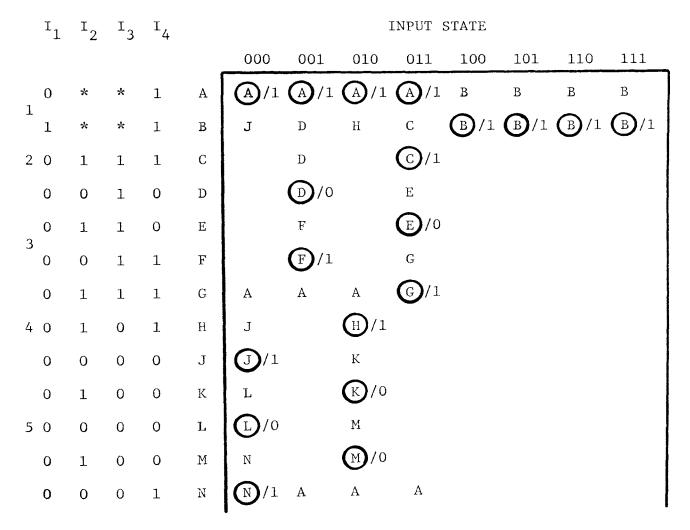

Sequence relationship data provided by "FOLLOWS" and "GO TO" instructions are conveniently recorded in a Module Flow Table (MFT). Each sequence corresponds to a single row of the MFT. Stable states in the MFT record sequence entry input states (obtained from the head I/O pair specification). Unstable next-state entries in exit (tail) input state columns indicate the next sequence to be followed for various input values. A stable and unstable state entry both in the same row and column indicates that an entry input state is also an exit state. In this case, the unstable entry is simply tagged with a minus sign.

Each sequence is translated to flow table segment form and the MFT is completed. A single flow table description of the sequential circuit is then obtained by concatenating all sequence flow table segments. Unstable next-states corresponding to FOLLOWing sequence entry rows are added to the last (tail) row of each segment and flow table translation is completed. Note that the unstable states of a row of the MFT correspond to the unstable states added to the last row of each segment.

Figure 6 shows the flow table segments which are obtained from the circuit description of figure 4.

Figure 6. Sequence Flow Table Segments for Example B.

The Module Flow Table for figure 4 is shown in figure 7; the segments and the MFT have been combined as described into a single flow table shown in figure 8.

| <sup>1</sup> 1 | 12 | <sup>1</sup> 3 | 04 |   |     | INPUT | STATE |     |     |     |     |     |

|----------------|----|----------------|----|---|-----|-------|-------|-----|-----|-----|-----|-----|

|                |    |                |    |   | 000 | 001   | 010   | 011 | 100 | 101 | 110 | 111 |

| 0              | *  | *              | 1  | 1 | -,5 | -,3   | -,4   | -,2 |     |     |     |     |

| 0              | 1  | 1              | 1  | 2 |     | 3     |       | 2   |     |     |     |     |

| 0              | 0  | 1              | 0  | 3 | 1   | -,1   | 1     | 1   |     |     |     | 1   |

| 0              | 1  | 0              | 1  | 4 | 5   |       | 4     |     |     |     |     |     |

| 0              | 0  | 0              | 0  | 5 | -,1 | 1     | 1     | 1   |     |     |     | ı   |

Figure 7. The Module Flow Table for Example B.

| INTERNAL ST | ATE  |      | INPU | T STATE      | 3     |       |       |       |   |

|-------------|------|------|------|--------------|-------|-------|-------|-------|---|

| _           | 000  | 001  | 010  | 011          | 100   | 101   | 110   | 111   |   |

| 1           | 1)/1 | 1/1  | 1)/1 | 1)/1         | 2     | 2     | 2     | 2     |   |

| 2           | 9    | 4    | 8    | 3            | (2)/1 | (2)/1 | (2)/1 | (2)/1 | 1 |

| 3           |      | 4    |      | 3/1          |       |       |       |       | 1 |

| 4           |      | 4/0  |      | 5            |       |       |       |       |   |

| 5           |      | 6    |      | (5)/0        |       |       |       |       |   |

| 6           |      | 6)/1 |      | 7            |       |       |       |       |   |

| 7           | 1    | 1    | 1    | $\sqrt{7}/1$ |       |       |       |       | - |

| 8           | 9    |      | 8/1  |              |       |       |       |       | 1 |

| 9           | 9/0  |      | 10   |              |       |       |       |       |   |

| 10          | 11   |      | 10/  | 0            |       |       |       |       | - |

| 11          | 11)/ | O    | 12   |              |       |       |       |       | 1 |

| 12          | 13   |      | 12/  | 0            |       |       |       |       |   |

| 13          | 13/  | 1 1  | 1    | 1            |       |       |       |       | 1 |

Figure 8. Flow Table Representation of Example B.

### D. A sequence Translation Computer Program

A PL/1 program, WAVEFM, has been written which accepts I/O sequential circuit specifications of the type described. The program also incorporates several useful error detection and editing features.

The improper sequence tests have been incorporated; they produce error messages and terminate translation if an improper list of specifications is presented.

Each specification is required to have a unique 4-character label.

If the I/O pair name has been previously used, an error message is produced and processing ends.

The program accepts "FOLL XXXX,YYYY,..." as FOLLOWS instructions, where XXXX and YYYY are 4-character labels previously used in the description. The GO TO instruction is identical, except for the mnemonic "GOTO". "BEGN" and "END" mark the beginning and end of sequences, while "STOP" in the label field indicates end of the circuit description.

Although now operating in a batch mode environment, the description and translation methods used by WAVEFM should prove most useful in interactive use by circuit designers. Limited text editing features were included in order to provide some "psuedo-interactive" processing by the present version of the program. Thus a "<" causes deletion of a single character immediately to the left of the character deletion symbol and "/" causes the deletion of an entire input record (line).

Another feature incorporated into the program is the capability to provide, on request, an error-free copy of the partial list of circuit specifications and/or the module flow table. Finally, the program may optionally be requested to prepare a list of all branch points for which action in response to some input is not specified.

### E. Extensions and Results

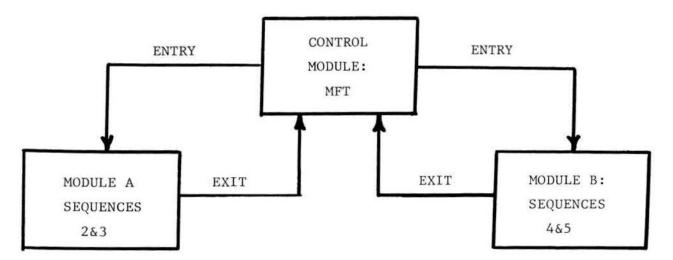

An alternate representation of the desired sequential circuit may be obtained by considering each sequence (or a collection of sequences) as a submachine or module. Each module has one or more entry internal states, and a single exit state. Each module realizes a portion of the sequential behavior required of the desired circuit.

Only one module at a time responds to input stimulii. The active module is selected by a control module which responds to inputs as well as "module exit state" signals. It is interesting to note that the previously developed MFT closely resembles a flow table description of the control module. Figure 9 shows a block diagram of one modular realization of example B of this chapter.

Figure 9. Modular Organization of Example B.

A flow table translation program for modularly organized circuits has not been written, because the design automation system

related to the programming effort presently synthesizes only single flow tables. Little difficulty should be encountered in adopting the translation algorithm to the modular case. Investigation will, however, be required to develop heuristics for determining modular partitioning. The decomposition of a very large sequential circuit description into several smaller ones is a powerful synthesis aid.

The single flow table translation program has been applied to only a few long specification lists. A typical description involved 22 sequences containing a total of 158 four-input, three-output specifications. The 158 row by sixteen column flow table was produced in only 65 seconds.

The flow tables produced by the methods described in this chapter generally can be greatly simplified. Indeed, if these tables are to be used to actually synthesize circuits, it is important to reduce (if possible) the number of internal states (rows) in the flow table. Chapter III is devoted to the problem of simplifying very large flow tables.

# III. REDUCTION OF LARGE INCOMPLETELY SPECIFIED FLOW TABLES

Flow tables often contain more internal states than are required to specify the desired circuit behavior. In such cases it is advantageous to reduce the flow table to more compact form, for synthesis costs increase with flow table size, and circuit complexity is roughly proportional to flow table size. The simplification of completely specified flow tables is much less difficult than that for incompletely specified tables. Since practical asynchronous sequential circuit descriptions are seldom formulated as completely specified tables, the more general, incompletely specified case is treated here.

## A. Background

The following definitions are useful in this chapter. If a sequence of inputs is applied to flow table P when it is initially in internal state r, then this sequence is said to be applicable to r if the state of the flow table is specified after each input, except possibly the last. Thus, when an applicable sequence of inputs is applied, no unspecified next-state entries are encountered, except possibly after the final input. Unspecified flow table entries are taken to imply that behavior of the machine ceases to be of interest once the unspecified state is entered. Stable states which have no output specified imply that circuit outputs will be ignored so long as the output remains unspecified.

Two output states are <u>comparable</u> if they are identical whenever both are specified. Two internal states  $s_a$  and  $s_b$  are <u>compatible</u> if they yield comparable output sequences for all possible input sequences. It is clear that  $s_a$  and  $s_b$  are compatable only if for

each input state their outputs are identical whenever both are specified, and their next-state entries are compatable whenever both next-states are specified.

A <u>compatibility class</u> C is a set of internal states which are all pairwise compatible. A set of states Q is <u>implied</u> by a set of states R if, for all inputs, Q is the set of all specified next-state entries for R. As used herein, this definition will be slightly modified when applied to compatibility class candidates.  $C_a$  implies  $C_{bi}$  if for each input state  $I_i$  either all next-state entries are in  $C_a$  or all next-states are in an implied class  $C_{bi}$ . Using the latter concept of implication, it may be seen that a single class  $C_a$  may imply one or more classes  $C_{bi}$ . Since each of the  $C_{bi}$  may in turn imply other classes, an implication chain may be formed. All compatibility class candidates  $C_a$  which imply others are termed <u>conditionally compatible</u>, since the implied classes of the chain must be subsets of known compatibility classes before compatibility can be established for  $C_a$ .

A <u>maximal compatible</u> (or <u>maximum compatibility class</u>) is one which is not contained in any other compatibility class.

A set of compatibility classes <u>covers</u> a flow table if every state of the flow table is contained in one or more classes of the set.

A set of compatibility classes is  $\underline{\operatorname{closed}}$  if for every input state the set of next-states implied by each class  $C_i$  in the set is contained in at least one of the classes of the set.

It can easily be shown that a reduced flow table which covers the original one may be formed from a closed set of compatibility classes which contains each state of the original table. Each row of the reduced table corresponds to a compatibility class.

Paull and Unger, in a classic paper<sup>2</sup>, presented an algorithm for obtaining maximum compatibility classes for incompletely specified flow tables. An implication table is formed, recording pairwise compatibility. Figure 10 illustrates the implication table for flow table A of figure 1. Dash entries indicate state pairs which are

| 5 | Х   |            |             |            |            |

|---|-----|------------|-------------|------------|------------|

| 4 | 1,4 | 5,6        |             |            |            |

| 3 | -   | 5,6<br>3,6 | 1,4<br>3,6  |            |            |

| 2 | Х   | X          | 1,4 3,6 2,6 | 1,4<br>2,6 |            |

| 1 | 2,6 | 1,4<br>2,5 | X           | 2,6<br>3,6 | 3,6<br>1,4 |

| • | 6   | 5          | 4           | 3          | 2          |

Figure 10. Implication Table for Flow Table A.

compatible, while X's indicate pairs which are incompatible. State pairs which are conditionally compatible have the implied pairs entered in the appropriate cell. Conditional compatibility chains are systematically examined and the final implication table contains no implied pair entries which are not conditionally compatible.

A systematic method is described for obtaining the set of all maximal compatibles from the implication table. The Paull-Unger maximal compatible algorithm is well known and will not be presented

here.

Paull and Unger were unable to present a systematic procedure (other than complete enumeration) for obtaining a minimum closed collection of compatibility classes. They pointed out that an upper bound on the number of states in the minimized flow table is the number of maximal compatibles—but this number is usually greater than the number of rows in the original flow table. Several suggestions are offered for manual minimization of flow tables of up to fifteen rows.

Grasselli and Luccio have published an algorithm<sup>3</sup> which solves the cover and closure problem without resorting to complete enumeration. The incompatibility table is formed and used to produce the set of all maximal compatibles.

A procedure is described for obtaining the collection of all compatibility classes which can be used to construct a minimal flow table. This set of compatibility classes is much smaller than the set of all maximal compatibility classes and their included subclasses. A significant reduction in intermediate data is achieved, but only through increased computation.

The final step in Grasselli's flow table minimization procedure is the construction and reduction of a cover and closure (CC) table, used to select closed sets of compatibility classes which cover the original flow table. The CC table is very similar to a prime implicant table, but is somewhat more difficult to reduce.

Kella<sup>5</sup> recently developed a procedure for finding all minimal covers for an incompletely specified flow table. The generation of all prime compatibility classes is avoided by generating reduced

machines by recursively adding new states, rather than starting with a set of compatibility classes which cover the original flow table.

Only reduced machines with the minimum number of states are considered as new states are added, thus avoiding non-minimal reductions.

A sequential machine  $M_a$  is a <u>partial machine</u> of machine  $M_b$  if the state table of  $M_a$  is included in but less than  $M_b$ . Every transition in  $M_b$  not covered by  $M_a$  is considered unspecified in  $M_b$ . A reduced machine  $\overline{M}_b$  is based on a reduced machine  $\overline{M}_a$  if  $\overline{M}_a$  is a partial machine of  $\overline{M}_b$ .

Kella's procedure begins by finding all state pairs of the original flow table which are pairwise incompatible. An algorithm is then presented for finding all reduced machines  $\mathbf{M}_a$  for the first (i+1) rows of the original table M, which are based on the  $\mathbf{M}_a$  of M(i). Thus the consideration of each row of M in turn leads to the production of all minimal flow tables. The procedure involves finding all maximum compatibility classes for the partial table M(i+1) which include state  $\mathbf{s}_{i+1}$ ; using the list of incompatible states this process is much less difficult than finding the set of all maximum compatibility classes for the original machine.

The three algorithms outlined above have been examined in some detail in order to emphasize the amount of effort required to minimize very large flow tables. For an N-row table, the amount of data and effort required to produce pairwise compatibility or incompatibility information is in general proportional to  $N^2$  for large tables. The amount of computation involved in generating maximum compatibility classes is rather problem dependent, but is roughly

proportional to  $N^6$ .\* Effort expended in developing prime compatibility classes and reducing a CC table also increases approximately exponentially.

The Kella algorithm, while in general requiring less effort than the Grasselli-Luccio procedure, is still far too cumbersome to economically reduce extremely large flow tables.

None of the methods outlined are well suited to automated flow table reduction. All require that an extremely large amount of intermediate data be preserved. Another disadvantage of these techniques is that they produce all minimal flow tables; for large tables it becomes impractical to produce more than a single reduced flow table. Furthermore, experience with other switching theory minimization problems—Boolean functions and asynchronous state assignments, to name just two—has shown that minimization becomes prohibitively costly for very large problems. Although they do not in general produce minimal results, it is clear that economical flow table reduction procedures must simplify rather than minimize large tables.

<sup>\*</sup>There are P =  $(N^2-N)/2$  row-pair comparisons to be made in forming a compatibility or incompatibility table. Suppose that 1-1/r of the row pairs are incompatible. Consider only attempting to form three member compatibility (or incompatibility) classes: three two-sets must be examined for each three-set. There are R = P/r possible two-sets. The number of pair comparison look-ups required is W =  $(\frac{P}{3}) = (\frac{N^2}{3}-N)/2r$ , which is proportional to  $N^6$ . For example,

with N = 10 and r = 4, W = 155; however, for N = 100 and r = 4, W =  $3 \times 10^8$ . This very rapid increase in effort required to produce maximal compatible generator routines for minimum variable state assignments described in (10 and 17). Also see Chapter IV.

One of the least complicated simplification procedures is merging. Two flow table states may be <a href="merged">merged</a> 18 if their next-state entries are the same state whenever both are specified. The state resulting from the merger has a stable state or output specification wherever either of the original states had a stable state or an output specification. Merging thus does not remove redundant stable states; however if there are no redundant stable states, merging produces a minimal flow table. Although merging usually prevents a reduction of large flow tables to minimal form, it is based on a simple relationship between rows which is easily detected.

Two rows of a flow table are <u>equivalent</u> unless in some flow table column a) their outputs are specified to be different, b) the output or next-state of one row is specified and the other is not, or c) the next-state entries of the two rows are not equivalent <sup>19</sup>. Only one of the two or more equivalent rows need be included in a simplified flow table.

## B. A Flow Table Simplification Heuristic

The operating speed or amount of effort required by a large flow table simplification procedure is related to the simplicity of the state relationships detected. It is also affected by the volume of intermediate data which is required to be generated and evaluated. Conversely, the amount of simplification achieved (compared to minimal reduction) is in general improved by detecting complex compatibility relationships and using large amounts of intermediate data.

The algorithm presented below is intended to rapidly produce a simplified—but in general non-minimal—flow table. The table to be simplified is assumed to be incompletely specified, with many next—

state entries unspecified. The simplification method is independent of flow table source; the method described in Chapter II might, for example, be employed to produce such tables. The procedure is designed to be most economical when applied to extremely large (up to several hundred state) flow tables, and is intended primarily for automated design applications.

Two important considerations affect the design of a flow table simplification heuristic. First, the procedure must not require exhaustive computations or comparisons. The effort expended in economically simplifying large flow tables must be literally orders of magnitude less than that characteristic of known minimization procedures.

Digital computer main memory size limitations restrict the volume of data immediately accessible to a simplification program. (Secondary storage is uneconomical for frequently accessed data). The generation of massive blocks of intermediate data is also expensive. Thus a modest amount of data should be utilized by the successful flow table simplification heuristic.

These two constraints have led to the adoption of a simple strategy: only a single set of compatibility classes, representing the reduced table, is generated. Cover is insured by insisting that each state of the original machine be a member of one and only one compatibility class. Closure is preserved by continuously updating next-state and output specifications for the compatibility classes; current closure requirements thus reduce to satisfying compatibility requirements for the partially reduced machine.

The partial machine next-state entries are stored in a two-

dimensional array wherein each row is reserved for a compatibility class, and columns correspond to input states. A Boolean matrix is utilized to store output states associated with stable states. A tag number is associated with each flow table state; if zero, the state is either a single element compatibility class or has not yet been added to the reduced machine. If the tag is negative, the state represents a compatibility class containing two or more elements (states). A positive tag points to the state number (in the reduced machine) which corresponds to the compatibility class containing the row in question; positive tags thus map original machine states into compatibility classes, and eventually into states of the reduced machine.

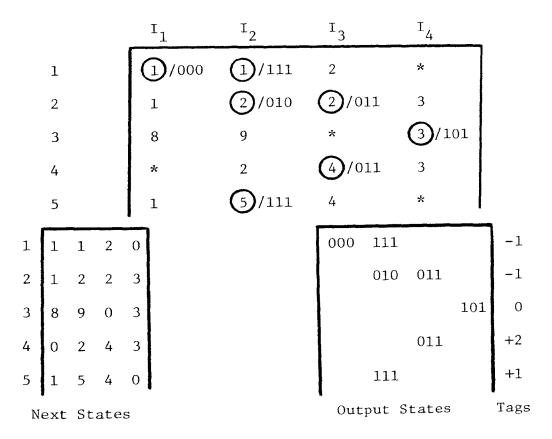

Figure 11. Flow Table and Corresponding Representation.

Next-state zero indicates that the flow table entry is not specified. Row 4 has been combined with row 2, and the resulting compatibility class has been stored in row 2; likewise, rows 1 and 5 have been combined and the resulting class is in row 1.

Each state of the original flow table is considered in turn. To reduce the number of row-pair comparisons performed, row i is compared only with compatibility classes—or rows—in the limited range (i-p) & i & (i+q). Because of this 'look-ahead' provision in the range of comparison for row i, the current status of state (i+q) is used. Thus prior to examining state (i+q) from the original table, the tag numbers must be used to map next-state entries for original row (i+q) into compatibility class references if appropriate.\*

The limited flow table examination range employed here may also be visualized as a "window" which moves down the flow table. Only rows currently exposed in the window are used in flow table simplification.

To minimize the amount of intermediate data, only four simple types of row-pair compatibility test are utilized; this arrangement also improves the operating speed of the simplification procedure drastically.

Consider row i from the unsimplified flow table as it is being added to the reduced table. An attempt is first made to add the row

<sup>\*</sup>This action is actually performed for rows (q+1) and on-the first q rows of the original table 'prime' the reduction procedure and require no updating.

to a compatibility class within the examination range having a negative tag (implying two or more original states in the class). Since the compatibility class is represented by its resulting flow table row, i can be added to class j if it is compatible with (compatibility class) flow table row j.

Two flow table rows are <u>compatible</u>, written x vy, if for each input state having specified next-state in both rows, 1) both next-state entries are identical or 2) both next-state entries are stable states and the output states agree whenever both are specified.\*

Row i is immediately added to the first compatibility class j with which it is compatible. The resulting compatibility class has a stable state and output specification wherever either of the previous rows was stable. If both were stable for some input, only the outputs are combined. For convenience, the new class is placed in the same location as the old compatibility class; this practice generally reduces the number of next-state entries which must be changed, since next-state i is likely to appear less frequently than j. The tag for row i is set equal to j, and known (i.e., within the range "window") next-state entries corresponding to stable states i are changed to j.

Next, an attempt is made to add each lower (k) j) compatibility class to the new class containing state i. Any classes which can be

<sup>\*</sup>This definition is much more restrictive than that usually encountered in the literature. A third condition, that the next-states themselves be compatible, has been discarded in order to develop an economical simplification heuristic. All compatibility classes developed under the restricted definition also satisfy the more general case.

added to the  $\underline{\text{new}}$  class j are included immediately by updating the appropriate tag, next-state and output entries.

Finally, the new class j is checked for compatibility with any single member classes—rows which have previously been found incompatible with all others in the known segment of the reduced table.

The new compatibility class expansion procedure causes compatibility classes which may contain many original table rows to grow quite rapidly; this is advantageous because it quickly decreases the size of the partially reduced table and thus reduces the number of row pair comparisons performed in each step.

If a newly considered flow table row is incompatible with all known compatibility classes (i.e., those in range) with two or more elements, an attempt is made to combine that row with each known single element compatibility class. These classes correspond to rows of the original flow table which have been found incompatible with all known rows. If a single row j is discovered to be compatible with i, a new compatibility class is formed and recorded in the old compatibility class position j as outlined above; the remaining single element classes are also checked for compatibility with new class j, as in the previous new class case.

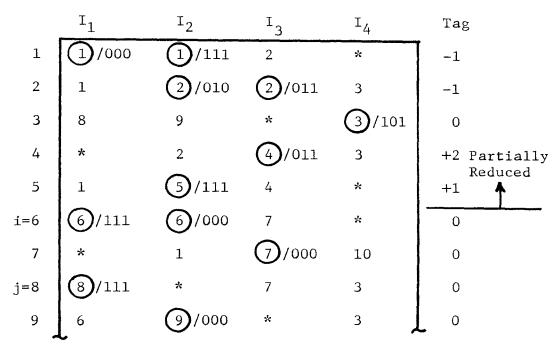

Figure 12 illustrates the formation of a new compatibility class. Row 6 of the original table is added to the partially reduced table composed of classes 1,2, and 3.

Row 6 is incompatible with classes 1 and 2 which represent two or more rows of the original table. Row 6 is conditionally compatible with row 3. With a look-ahead factor of 3, rows 7,8, and 9 are then considered. Rows 6 and 7 are conditionally compatible; then row 8 is

discovered to be compatible with row 6. A new two element class is then formed in row 8. The tag and next-state entry modifications which occur are shown in Figure 13.

Figure 12. Discovery of a New Compatibility Class.

|     | 1<br>1 | $I_2$           | 13    | 14    | Tag        |

|-----|--------|-----------------|-------|-------|------------|

| 1   | 1)/000 | 1)/111          | 2     | *     | -1         |

| 2   | 1      | 2/010           | 2/011 | 3     | -1         |

| 3   | 8      | 9               | *     | 3/101 | 0          |

| 4   | *      | 2               | 4/011 | 3     | +2         |

| 5   | 1      | <b>(5)</b> /111 | 4     | *     | +1         |

| i=6 | 6 /111 | 6/000           | 7     | *     | +8         |

| 7   | *      | 1               | 7/100 | 10    | 0          |

| j=8 | 8/111  | 8/000           | 7     | 3     | <b>-</b> 1 |

| k=9 | 8      | 9/000           | *     | 3     | 0          |

Figure 13. Formation of the New Class

An attempt is then made to add remaining classes or rows to the new class formed in row 8. Row 9 is found to be compatible with class 8 and is thus included in the new class, as shown in figure 14.

|     | <sup>1</sup> 1 | 12      | <sup>1</sup> 3 | 14    | Tag |

|-----|----------------|---------|----------------|-------|-----|

| 1   | 1/000          | 1)/111  | 2              | *     | -1  |

| 2   | 1              | 2/010   | 2/011          | 3     | -1  |

| 3   | 8              | 8       | *              | 3/101 | 0   |

| 4   | *              | 2       | 4/011          | 3     | +2  |

| 5   | 1              | (5)/111 | 4              | *     | +1  |

| 6   | 6)/111         | 6/000   | 7              | *     | +8  |

| 7   | *              | 1       | 7/100          | 10    | 0   |

| j=8 | 8/111          | 8/000   | 7              | 3     | -1  |

| 9   | 8              | 9/000   | *              | 3     | +8  |

|     | l              |         |                | ,     |     |

Figure 14. Addition of a Row to the New Class.

It has been found that for partially reduced incompletely specified flow tables, row pair (i,j) is sometimes the only implicant for class pair (m,n). In this case, the compatibility of pair (i,j) implies that of pair (m,n). However, this situation does not occur frequently enough to justify rechecking the compatibility of each row pair after formation of each new compatibility class. To do so would increase manyfold the amount of effort expended in flow table reduction.

It can be shown, however, that in general only a small fraction of row pairs need be rechecked. Furthermore, these pairs can be easily located during the process of next-state entry updating after

formation of the new compatibility class (i,j).

Theorem: If row pair (k,j) is an implicant of pair (m,n) then both i and j must have stable states under some input state(s), and for at least one of these inputs, both i and j must appear as explicit next-state entries in rows m and n.

Proof: If (m,n) implies (i,j) then i and j must be next-state entries under at least one input state of pair (m,n). Normal mode operation requires that transitions lead directly to stable states, so both i and j must be stable for the given input.

It is clear that the above theorem dramatically reduces the amount of rechecking which needs to be done after compatibility class formation. Rechecking does, however represent a significant increase in computational effort, and should be further justified.

First consider two relatively small compatibility classes i and j. In a large table, it is quite likely that the number of unstable next-state entries leading to them will be small. Rechecking in this case is inexpensive, especially since the number of stable states per row may be small, further reducing the likelihood of both being stable in the same column.

If on the other hand i and j are large compatibility classes having many stable state columns, rechecking may involve a large number of row pairs and thus become less desirable.

In the formation of new compatibility classes described above, at least one of the constituents of the new class is always a single row from the original flow table, i. Rechecking is performed after formation of new classes resulting from the construction of class (i,j). If rechecking discovers compatible state pairs (m,n), they

are immediately combined, but further rechecking based on these "secondary" new classes is not performed.\*

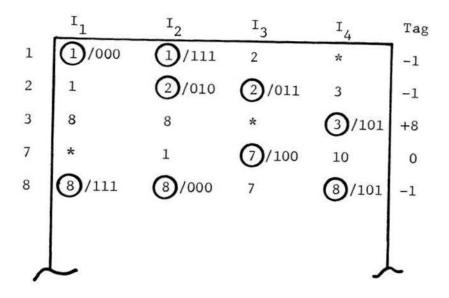

Figure 15 shows the reduced flow table resulting from the simplification illustrated in figure 14. Notice that as new class 8

|    | I <sub>1</sub> | 12    | 13    | 14    | Tag | Recheck |

|----|----------------|-------|-------|-------|-----|---------|

| 1  | 1/000          | 1/111 | 2     | *     | -1  | 0       |

| 2  | 1              | 2/010 | 2/011 | 3     | -1  | 0       |

| 3  | 8              | 8     | *     | 3/101 | 0   | 1       |

| 7  | *              | 1     | 7/100 | 10    | 0   | 0       |

| 8  | 8/111          | 8/000 | 7     | 3     | -1  | 1       |

| Į. | l              |       |       |       |     |         |

Figure 15. A Recheck Opportunity.

was constructed, the recheck flag for row 3 was set due to rows 8 and 9 having stable states under  $\mathbf{I}_2$ , and row 3 having a next-state entry leading to the new stable state.

Rechecking pair (3,8) results in the formation of a new class (3,8) which is placed in row 3. Figure 16 shows the flow table segment after rechecking is completed.

<sup>\*</sup>Experimental simplification of large randomly redundant tables has shown that locating implicants of secondary new classes, although costly, results in little if any increase in overall flow table simplification.

Figure 16. Flow Table Segment After Rechecking.

A row i from the original table is not considered further unless, after the processes described, it is found to be incompatible with all known (in range) classes. Since the amount of reduction achieved may be significantly decreased by such rows, another attempt is made to find compatibility classes containing i.

A <u>single implication chain</u> consists of a collection of state pairs such that each pair of states (excluding perhaps the last) is conditionally compatible and implies <u>only</u> the next pair in the chain.

Figure 17 shows a partial flow table containing a single implication chain.

Since the generation and use of implication data is expensive in terms of both storage and computation, only single implication chains are used in the flow table simplification heuristic. Additional constraints restrict the consideration of implication relations to those situations most likely to produce economical simplification.

Figure 17. Partial Flow Table and Single Implication Chain.

As has already been implied, a row pair (i,j) is used as the first element in an implication chain only if 1) one of the two states is incompatible with all known states, and 2) only a single pair of states (p,q) is implied by (i,j). These pairs are detected as the pair compatibility process previously described is executed: as state j is considered for compatibility with state i, if i and j are conditionally compatible and imply only a single pair of states (implicants) p and q, j is marked. If i is not found compatible with any known state, then an attempt is made to build a single implication chain based on (i,j) implies (p,q).

Implication chains which may be used to find valid compatibility classes terminate in several ways. If the final implicant pair p and q are unconditionally compatible, then all pairs in the chain are compatible. If a pair already in the chain is the only implicant of

the last pair (i.e., the chain closes on itself) then all pairs in the chain are compatible.

A chain building attempt fails if some chain implicant pair (p,q) has two or more implicants, if a pair of implied states are incompatible, or if the chain length exceeds some threshold. The latter has experimentally been shown to be unimportant; the restricted implications considered cause almost all chains to be very short. A fourth type of chain failure closely resembles a closed chain: if one state but not both of an implicant pair has previously appeared in a chain, the chain fails.

If a chain is successfully completed, compatibility classes are calculated in reverse order, beginning with the last class added to the chain. Rechecking may be performed after this operation is completed for all implicant pairs. The advisability of rechecking here is highly problem dependent but usually yields little additional simplification—at a relatively high cost.

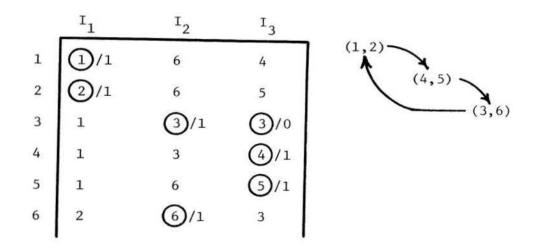

Figure 18 illustrates the simplification obtained by reducing the single implication chain shown in figure 17.

After the process described above has been completed for each original flow table row, the flow table must be reorganized to eliminate the rows with positive tags and to complete the updating of next state entries.

Each row is considered in turn, until all rows have been processed. If row i has a positive tag (indicating inclusion of i in a compatibility class stored elsewhere) the flow table portion consisting of zero or negatively tagged rows above the "known" part of the table (with the window of the known rows based on row i) is

|   | <sup>1</sup> 1 | 12  | <sup>1</sup> 3 | Tag |

|---|----------------|-----|----------------|-----|

| 1 | 1)/1           | 3   | 4              | -1  |

| 2 | 2/1            | 6   | 5              | +1  |

| 3 | 1              | 3/1 | 3/0            | -1  |

| 4 | 1              | 3   | 4/1            | -1  |

| 5 | 1              | 6   | (5)/1          | +4  |

| 6 | 2              | 6/1 | 3              | +3  |

| , | L              |     | ٦              | _   |

Figure 18. Flow Table Simplification Using Single Implication Chains.

examined for unstable entries valued i. These next-state entries are changed to the appropriate state number of the class containing row i. A search is then made to find a row j > i with a zero or negative tag to "fill" the space occupied by the eliminated row i. If such a row is found, next-state entries are changed to reflect the relocation of row j to position i. If no rows are available to fill state i, the flow table reorganization process is complete.

Figure 19 illustrates the flow table reorganization for the reduced table shown in figure 18. Notice that the second row,

|   | 11   | I <sub>2</sub> | 13            | Tag |

|---|------|----------------|---------------|-----|

| 1 | 1)/1 | 3              | 2<br><b>4</b> | -1  |

| 2 | 2/1  | 6              | 5             | +1  |

| 3 | 1    | 3/1            | 3/0           | -1  |

| 4 | 1    | 3              | 4/1           | -1  |

| 5 | 1    | 6              | (5)/1         | +4  |

| 6 | 2    | 6/1            | 3             | +3  |

Before Reorganization.

|   | 11   | 12  | 13  |

|---|------|-----|-----|

| 1 | 1)/1 | 3   | 2   |

| 2 | 1    | 3   | 2/1 |

| 3 | 1    | 3/1 | 3/0 |

Final Form

Figure 19. Reorganization of a Reduced Flow Table.

having a positive tag, is replaced by the lowest row 4 having a negative tag.

The procedure outlined produces excellent simplification if a large portion of the flow table is in the range of consideration. However, the effort implied by such a large range is considerable. Thus, it is recommended that the procedure presented here be applied iteratively using a more economical range. Simplification processing ceases when a simplification yield requirement is not met.

Figure 20 is a brief flow diagram of the flow table simplification heuristic presented here.

# C. Programmed Implementation and Results

The flow table simplification heuristic described has been programmed in PL/1. Although the program will not be described in detail, the performance of the programmed procedure illustrates the utility of the simplification heuristic itself. It should be noted that the program was written in a high level language and emphasized algorithm clarity rather than execution efficiency.

Experience gained in several previously developed flow table simplification algorithms led to a program implementation of the procedure containing several minor modifications of the simplification heuristic described here. These changes permitted the evaluation of constraint placed on various phases of the simplification process.

A rather trivial assumption was also made to allow an experimental simplification routine to be developed more rapidly. It was assumed that, as flow table simplification proceeds, enough memory is available to store all of the partially reduced machine. Thus as row i of the original flow table is added to the reduced machine, it

Figure 20a. The Flow Table Simplification Heuristic.

Figure 20b. The Flow Table Simplification Heuristic (Recheck, Chaining and Reorganization).

is assumed that all compatibility classes containing rows 1 through i-l are stored in main memory. This programming convenience eliminated the need for a partially reduced flow table segment paging and bookkeeping scheme--which although involving very significant extra programming effort is not technically important.

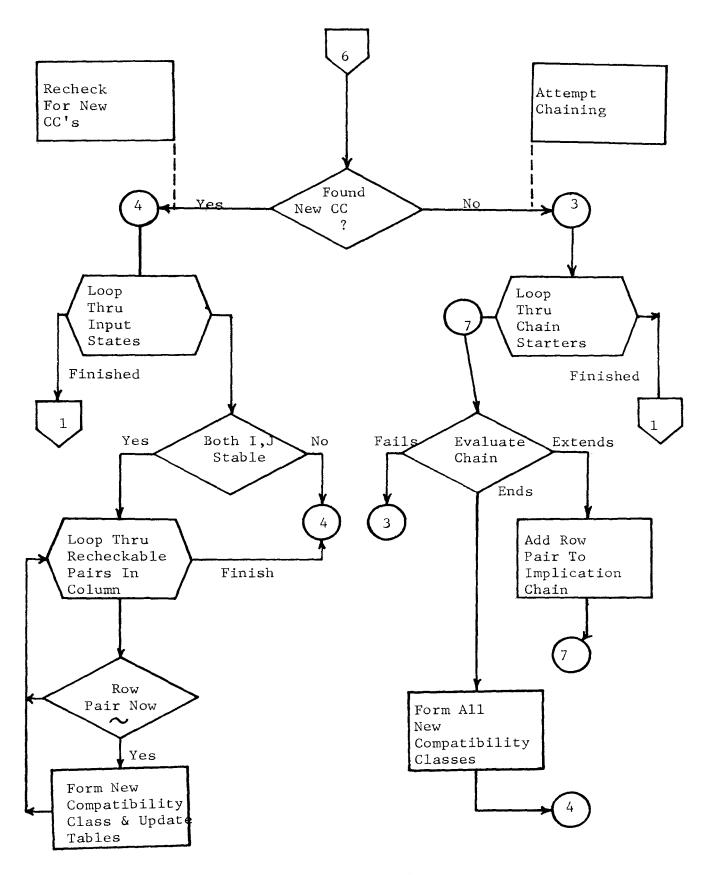

An interesting experimental modification of the program was a provision for varying the degree of "look ahead" used in the procedure. Although computer time costs have restricted experimentation with this parameter, some preliminary results can be reported.

Figure 21 shows a plot of look ahead versus simplification time (using a S/360-50) for a single 193 rows by four column flow table. Also shown on the same graph is the degree of simplification achieved in each case. Although the effects of various degrees of look ahead are highly problem dependent, processing times generally increase as look ahead increases beyond about 10%. The degree of reduction achieved may be less dependent on look ahead, especially for values greater than 10%

The examination of an extremely large number of single implication chains may be undersirable. The programmed simplification procedure thus contained a provision for halting the chain building process after a variable number of chain failures. A variable maximum chain length test was also incorporated (i.e., fail all chains longer than the length limit). Both of these provisions were found to have almost no effect on either the degree of reduction obtained or execution time required. This result is due to the extremely low incidence of long single implication chains in the examples used, and the surprisingly small number of single implication chains discovered.

Figure 21. An Example of the Effect of Look Ahead on Flow Table Simplification

The programmed routine also contained an option for suppression of the iterated simplification feature. It was found that the increased simplification obtained was highly problem dependent. In many instances, virtually no simplification was achieved after the first pass. For other tables, significant reduction was obtained for up to three passes. In all cases, the amount of time required to complete a simplification cycle decreased markedly for successive passes.

The recheck performed after formation of new compatibility classes could also be bypassed in the programmed flow table simplification routine. It was found that rechecking contributes significantly to table reduction, especially on the first iteration.

As has been pointed out previously, minimization procedures for the large flow tables considered here are impractical. Thus no attempt has been made to program a flow table minimization algorithm. Still, some means of evaluating the performance of the heuristic is essential.