Indian Journal of Pure & Applied Physics Vol. 55, April 2017, pp. 254-260

# Compact quadrature oscillator with voltage and current outputs using only single VDTA and grounded capacitors

Worapong Tangsrirat\*

Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang, Bangkok 10520, Thailand

Received 12 November 2015; revised 30 December 2016; accepted 15 February 2017

A possible design of the compact sinusoidal quadrature oscillator using single voltage differencing transconductance amplifier (VDTA) and only two grounded capacitors has been presented. The presented quadrature oscillator provides the following attractive properties: (i) canonic form and resistor less structure; (ii) availability of the explicit quadrature voltage outputs and current outputs; (iii) electronic controllability of the oscillation frequency ( $\omega_0$ ); and (iv) low active and passive sensitivities. To support the validity of the oscillator, PSPICE simulation results have also been provided.

**Keywords:** Voltage differencing transconductance amplifier, Quadrature oscillator, Dual-mode operation, Resistorless circuit, Electronically tunable

#### 1 Introduction

The voltage differencing transconductance amplifier (VDTA) is the recently defined controllable active building block, and increasingly being used in numerous applications. In the more recent works, its applications and advantages especially in the synthesis of active filters<sup>1-6</sup> and sinusoidal oscillators<sup>7-9</sup> have increased considerably as they have been found to be able to provide the electronic tuning through the transconductance gain  $g_m$  of the VDTA, and reduce the number of the passive components used for their circuit realizations<sup>10</sup>.

Sinusoidal quadrature oscillators, i.e., generators producing two identical sinusoidal output signals equally in amplitude and frequency but having 90° phase shifted, are very frequently used in wide scope of electronic engineering applications. For this reason, a number of voltage and current-mode sinusoidal quadrature oscillators have been already realized by utilizing the advantages of different types of versatile active building blocks<sup>9,11-27</sup>. However, the previously quadrature oscillators suffer from one or more of the following disadvantageous features:

- (i) They employ more than one active circuit building block 9,11-21,25-26.

- (ii) They use any external passive resistors, which is not canonic and resistorless structure 11-20,22-27.

- (iii) They do not provide electronic controllability to their circuit parameters  $^{11\text{-}15,18,24\text{-}25}$

- \*E-mail: drworapong@yahoo.com

- (iv) The passive components used in their realization are floating, which is not convenient for integrated circuit implementation <sup>12-15,19-20,22-23,25</sup>.

- (v) They cannot generate voltage-mode and current-mode quadrature signals simultaneously 9,11-23.

In this paper, a simple scheme for the realization of the sinusoidal quadrature oscillator with voltage and current outputs has been considered. To perform a compact and resistorless quadrature oscillator, the circuit is based on the use of a single VDTA and only two grounded capacitors. When compared to the already reported works<sup>9,11-27</sup>, the proposed dual-mode quadrature oscillator exhibits the following salient characteristics: uses only one active element and two grounded capacitors, a resistorless design, dual-mode operation, i.e., voltage and current quadrature outputs, high-impedance current outputs, electronic adjustment of the frequency of oscillation, and low sensitivity performance. The characteristics of the circuit are studied in detail and demonstrated through the PSPICE simulation with acceptable results.

# **2 Circuit Descriptions**

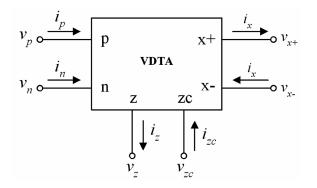

The electrical symbol of the VDTA is shown in Fig. 1. Its ideal characteristic can be described by the following matrix:

$$\begin{bmatrix} i_{p} \\ i_{n} \\ i_{z} \\ i_{x} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ g_{mF} & -g_{mF} & 0 & 0 \\ 0 & 0 & g_{mS} & 0 \end{bmatrix} \begin{bmatrix} v_{p} \\ v_{n} \\ v_{zc} \\ v_{z} \end{bmatrix} \dots (1)$$

where  $g_{mF}$  and  $g_{mS}$  are the first and second transconductance gains of the VDTA, respectively. In general, both transconductance gains are controllable electronically by the external DC bias currents. According to above describing-relations, the differential input voltage  $(v_p-v_n)$  is converted to currents at the terminals z  $(i_z)$  and zc  $(i_{zc})$ , respectively, by the transconductance  $g_{mF}$ , and the corresponding voltage drop at the terminal z is conveyed to currents at the terminals x  $(i_x)$  by the transconductance  $g_{mS}$ .

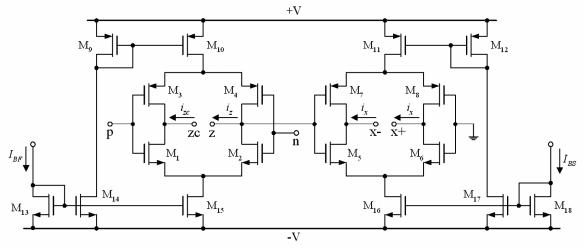

The possible CMOS realization of the VDTA is shown in Fig. 2, which actually consists of two interconnected Arbel-Goldminz transconductances<sup>28</sup>. Each of them realizes two independent electronically tunable transconductance gains  $g_{mF}$  and  $g_{mS}$ . Their values can be approximated as, respectively:

$$g_{mF} \cong \left(\frac{g_1 g_2}{g_1 + g_2}\right) + \left(\frac{g_3 g_4}{g_3 + g_4}\right) \dots (2)$$

Fig. 1 — Circuit representation of the VDTA

and

$$g_{mS} \cong \left(\frac{g_5 g_6}{g_5 + g_6}\right) + \left(\frac{g_7 g_8}{g_7 + g_8}\right)$$

... (3)

where

$$g_i = \sqrt{I_{Bi} \mu C_{ox} \frac{W_i}{L_i}}$$

is the transconductance value

of the *i*-th MOS transistor (i = 1, 2, ..., 8),  $I_{Bi}$  is the bias current of the MOS  $M_i$ ,  $\mu$  is the free carrier mobility in the channel,  $C_{ox}$  is the gate-oxide capacitance per unit area, and  $W_i$  and  $L_i$  are the channel width and length of the transistor  $M_i$ , respectively.

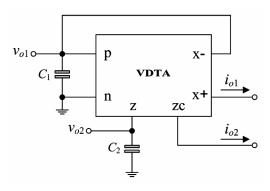

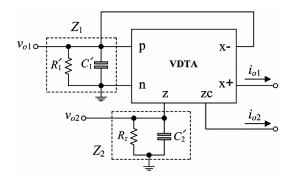

A realization scheme for a compact sinusoidal quadrature oscillator with explicit voltage and current outputs is shown in Fig. 3. The configuration is canonic in component count, since it consists of merely one VDTA and two grounded capacitors. It should be noted that the two quadrature current outputs  $i_{o1}$  and  $i_{o2}$  exhibit high-input impedances that permit the ease of cascading, and both capacitors  $C_1$  and  $C_2$  are grounded that is particularly beneficial from the viewpoint of ease of monolithic integration. A routine circuit analysis of Fig. 3 yields the following results. The voltage transfer function of the first transconductance stage of the VDTA is given by:

$$T_F(s) = \frac{V_{o2}(s)}{V_{o1}(s)} = \frac{g_{mF}}{sC_2} \qquad ... (4)$$

and that of the second transconductance stage is:

$$T_{s}(s) = \frac{V_{o1}(s)}{V_{o2}(s)} = -\frac{g_{ms}}{sC_{1}} \qquad \dots (5)$$

Hence, the loop gain of Fig. 3 can be expressed as:

Fig. 2 — CMOS implementation of the VDTA

$$T_F(s)T_S(s) = -\frac{g_{mF}g_{mS}}{s^2C_1C_2}$$

... (6)

For sinusoidal oscillations, the loop gain is set to unity at  $s = j\omega$ . This, along with Eq. (6), gives the following characteristic equation for Fig. 3:

$$s^2 C_1 C_2 + g_{mF} g_{mS} = 0 ... (7)$$

From Eq. (7), the oscillation frequency can also be obtained as:

$$\omega_o = 2\pi f_o = \sqrt{\frac{g_{mF}g_{mS}}{C_1C_2}}$$

... (8)

For simplicity, if  $g_m = g_{mF} = g_{mS}$  and  $C_1 = C_2$ , then the parameter  $\omega_0$  in Eq. (8) turns to:

$$f_o = \frac{g_m}{2\pi C} \qquad \dots (9)$$

This means that the frequency of oscillation  $f_o$  can be tuned electronically by means of  $g_m$  through adjusting the external bias currents  $I_B = I_{BF} = I_{BS}$ .

Also from Fig. 3, the two marked quadrature voltages ( $v_{o1}$  and  $v_{o2}$ ) and currents ( $i_{o1}$  and  $i_{o2}$ ) are related as, respectively:

$$v_{o2} = -\frac{j\omega C_1}{g_{mS}} v_{o1} \qquad ... (10)$$

and

$$i_{o2} = \frac{j\omega C_2}{g_{mS}} i_{o1}$$

... (11)

which are ensured that the output voltages and the output currents are in quadrature signals.

Fig. 3 — Proposed dual-mode quadrature oscillator

# 3 Tracking Error Analyses and Sensitivity Study

The practical characteristics of the VDTA taking into account the tracking errors of the device can be expressed as:

$$\begin{bmatrix} i_{p} \\ i_{n} \\ i_{z} \\ i_{y} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ \beta_{F} g_{mF} & -\beta_{F} g_{mF} & 0 & 0 \\ 0 & 0 & \beta_{S} g_{mS} & 0 \end{bmatrix} \begin{bmatrix} v_{p} \\ v_{n} \\ v_{zc} \\ v_{z} \end{bmatrix} \dots (12)$$

where  $\beta_F$  and  $\beta_S$  are respectively the non-ideal transconductance gains of the VDTA, which deviate from their ideal values by tracking errors  $\varepsilon_F$  and  $\varepsilon_S$ , where  $|\varepsilon_F|$ ,  $|\varepsilon_S|$  << 1. Therefore, considering the effects of the VDTA non-idealities defined in Eq. (12), the modified  $\omega_o$  of the proposed quadrature oscillator in Fig. 3 can be written as:

... (9)

$$\omega_o = \sqrt{\frac{\beta_F \beta_S g_{mF} g_{mS}}{C_1 C_2}} \qquad ... (13)$$

It is clearly seen from Eq. (13) that the  $\omega_o$ -value is slightly affected by the transconductance tracking errors of the VDTA. However, these deviations can be compensated by pre-distortion of the transconductance gains ( $g_{mF}$  and/or  $g_{mS}$ ) of the VDTA.

The sensitivity of the  $\omega_0$  for the oscillator in Fig. 3 with respect to its active and passive components can be derived as:

$$S_{g_{mF}}^{\omega_o} = S_{g_{mS}}^{\omega_o} = S_{\beta_F}^{\omega_o} = S_{\beta_S}^{\omega_o} = \frac{1}{2}$$

... (14)

and

$$S_{C_1}^{\omega_o} = S_{C_2}^{\omega_o} = -\frac{1}{2}$$

... (15)

From Eqs (14) and (15), all the active and passive sensitivities are within 0.5 in absolute value, which is an advantageous feature of the proposed canonical oscillator.

# **4 Effects of Parasitic Impedances**

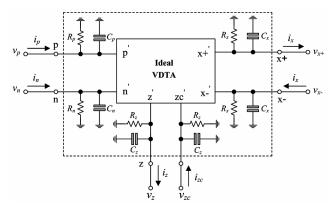

In order to complete non-ideal analysis, it is useful to consider the parasitic elements of the VDTA device used in the quadrature oscillator of Fig. 3. Including the corresponding terminal parasitic elements, the practical model of the VDTA can be shown<sup>5</sup> in Fig. 4. It is seen that there are the parasitic resistances and capacitances  $(R_p//C_p)$ ,  $(R_n//C_n)$ ,  $(R_z//C_z)$ ,  $(R_x//C_x)$

appearing in parallel connection at the corresponding terminals of the VDTA. Typically, these parasitic resistances and capacitances are in the order of several M $\Omega$  and pF, respectively. Considering these parasitic, the oscillator given in Fig. 3 is then modified to Fig. 5, where  $R_1 = (R_p //R_x)$ ,  $C_1 = (C_1//C_p//C_x)$  and  $C_2 = (C_2//C_z)$ . However, in practice, the values of the external capacitors  $C_1$  and  $C_2$  can be considered to be sufficiently larger than the parasitic capacitance values, i.e.,  $C_1 >> (C_p//C_x)$  and  $C_2 >> C_z$ . As a result, it becomes obvious that  $C_1 \cong C_1$  and  $C_2 \cong C_2$ . Therefore, the total impedance at the terminal P ( $Z_1$ ) is approximated to:

$$Z_1 \cong \frac{R_1'}{R_1'C_1s+1} \qquad \dots (16)$$

The action of  $Z_1$  at the terminal p of the actual VDTA limits the performance of the oscillator at the low-frequency range. According to Eq. (16), the operating frequency range can be easily defined as:

Fig. 4 — Practical model of the VDTA including its terminal parasitic impedances

Fig. 5 — Proposed quadrature oscillator of Fig. 3 considering the terminal parasitic impedances of the VDTA

$$f \gg \frac{1}{2\pi (R_p //R_x)C_1}$$

... (17)

In a similar analysis, the frequency restriction stemmed from the z-terminal parasitic impedance  $(Z_2)$  can also be defined as:

$$f \gg \frac{1}{2\pi R_z C_2}$$

... (18)

## 5 Simulation Results and Discussion

The proposed quadrature oscillator with voltage and current outputs in Fig. 3 was simulated using PSPICE program. In simulations, the CMOS-based VDTA circuit given in Fig. 2 was used with the TSMC 0.25  $\mu$ m CMOS process technology, and  $\pm 1.5$  V voltage supply. The aspect ratios of the MOS transistors are indicated in Table 1.

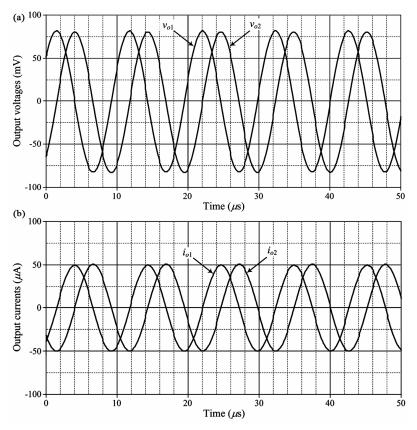

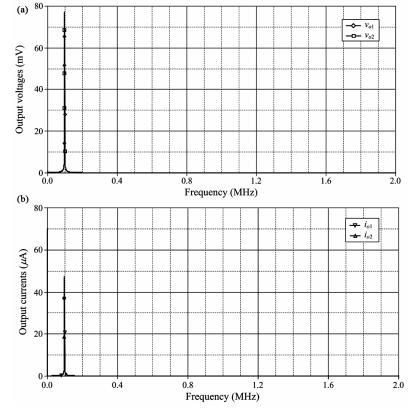

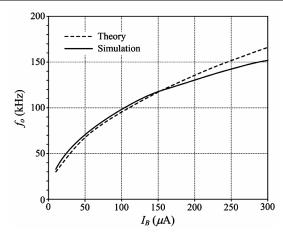

As an example, the proposed quadrature oscillator in Fig. 3 was designed to obtain the oscillation frequency  $f_o = 95$  kHz. By using Eq. (9), the designed component values were calculated as:  $g_m = g_{mF} = g_{mS} = 0.6 \text{ mA/V}$  $(I_B = I_{BF} = I_{BS} = 100 \text{ } \mu\text{A}) \text{ and } C = C_1 = C_2 = 1 \text{ nF}.$ Figure 6 shows the simulated steady-state waveforms of quadrature outputs  $(v_{o1}, v_{o2})$  and  $(i_{o1}, i_{o2})$ . The simulated  $f_0$  was measured as approximately 97 kHz, where the quadrature outputs different in phase by 86°. Figure 7 shows the simulated frequency spectrums of the quadrature output waveforms, where the values of the corresponding total harmonic distortion (THD) at all the outputs were around 2.46 %. Also from the simulation results, the total power consumption was found to be 2.09 mW. For the above designed values, the electronic control property of  $f_o$  with a variable  $I_B$  is displayed in Fig. 8. Obviously, the  $f_o$  is varied from approximately 30 kHz to 166 kHz for  $I_B$ , variation from 10 μA to 300 μA, respectively. A comparison results

Table 1 — Transistor aspect ratios used in the CMOS VDTA circuit of Fig. 2

| Transistors                      | $W/L (\mu m/\mu m)$ |  |  |  |  |

|----------------------------------|---------------------|--|--|--|--|

| $M_1$ - $M_2$                    | 15.75/0.25          |  |  |  |  |

| $M_3$ - $M_4$ , $M_9$ - $M_{10}$ | 20.3/0.25           |  |  |  |  |

| $M_5 - M_6$                      | 14.55/0.25          |  |  |  |  |

| $M_7 - M_8$                      | 23.3/0.25           |  |  |  |  |

| $M_{11}$ - $M_{12}$              | 5.2/0.25            |  |  |  |  |

| $M_{13}$                         | 14.5/0.25           |  |  |  |  |

| $M_{14}$                         | 15.5/0.25           |  |  |  |  |

| $M_{15}$                         | 18/0.25             |  |  |  |  |

| $M_{16}$                         | 3.2/0.25            |  |  |  |  |

| $M_{17} - M_{19}$                | 2.8/0.25            |  |  |  |  |

Fig. 6 — Simulated steady-state waveforms of quadrature outputs (a) output voltages  $v_{o1}$  and  $v_{o2}$  and (b) output currents  $i_{o1}$  and  $i_{o2}$

Fig. 7 — Simulated frequency spectrums of quadrature outputs (a) output voltages  $v_{o1}$  and  $v_{o2}$  and (b) output currents  $i_{o1}$  and  $i_{o2}$

|           |                          |                   | 1 1                    | 1                 |                                    | 2 1            |                           | C       |                              |

|-----------|--------------------------|-------------------|------------------------|-------------------|------------------------------------|----------------|---------------------------|---------|------------------------------|

| Reference | Number of active element | Number of $R + C$ | Grounded elements only | Electronic tuning | Dual-mode<br>quadrature<br>outputs | Technology     | Supply<br>voltages<br>(V) | THD (%) | Total power consumption (mW) |

| [9]       | VDTA = 2                 | 0 + 2             | yes                    | yes               | no                                 | TSMC 0.18-μm   | ±0.9                      | 3.00    | N/A                          |

| [11]      | CCII = 3                 | 4 + 2             | yes                    | no                | no                                 | AD844          | ±12                       | N/A     | N/A                          |

| [12]      | DVCC = 3                 | 3 + 2             | no                     | no                | no                                 | TSMC 0.35-μm   | ±2                        | N/A     | 3.72                         |

| [13]      | CDBA = 2                 | 3 + 2             | no                     | no                | no                                 | AD844          | ±12                       | 1.58    | N/A                          |

| [14]      | CDBA = 2                 | 4 + 2             | no                     | no                | no                                 | AD844          | ±12                       | 2.95    | N/A                          |

| [15]      | CDBA = 2                 | 3 + 2             | no                     | no                | no                                 | AD844          | ±12                       | 1.94    | N/A                          |

| [16]      | CCCDBA = 2               | 1 + 2             | yes                    | yes               | no                                 | TSMC 0.18-μm   | ±2                        | 2.00    | N/A                          |

| [17]      | GCFTA = 1, VF = 1        | 1 + 2             | yes                    | yes               | no                                 | PR100N, NP100N | ±2                        | 1.67    | N/A                          |

| [18]      | DVCC = 3                 | 3 + 2             | yes                    | no                | no                                 | 0.5-µm CMOS    | ±2.5                      | 2.00    | N/A                          |

| [19]      | CDTA = 2                 | 4 + 2             | no                     | yes               | no                                 | MIETEC 0.5-μm  | ±2.5                      | 1.00    | N/A                          |

| [20]      | CFTA = 2                 | 1 + 2             | no                     | yes               | no                                 | MIETEC 0.5-μm  | ±2.5                      | N/A     | N/A                          |

| [21]      | CDTA = 3                 | 0 + 2             | yes                    | yes               | no                                 | PR100N, NP100N | ±3.0                      | 2.50    | N/A                          |

| [22]      | CDTA = 1                 | 1 + 2             | no                     | yes               | no                                 | 0.7-μm CMOS    | N/A                       | 0.16    | N/A                          |

| [23]      | CDTA = 1                 | 1 + 2             | no                     | yes               | no                                 | MIETEC 0.5-μm  | ±2.5                      | 3.00    | N/A                          |

| [24]      | FDCCII = 1               | 2 + 2             | yes                    | no                | no                                 | TSMC 0.18-μm   | ±2.5                      | 2.76    | 118.1                        |

|           | FDCCII = 1,              | 3 + 2             | yes                    | no                | yes                                |                |                           | 2.86    | 129.4                        |

| [25]      | CDBA = 2                 | 3 + 2             | no                     | no                | yes                                | Macro-model    | N/A                       | N/A     | N/A                          |

| [26]      | CDTA = 2                 | 1 + 2             | yes                    | yes               | yes                                | MIETEC 0.5-μm  | ±2.5                      | N/A     | N/A                          |

| [27]      | CCTA = 1                 | 2 + 2             | yes                    | yes               | yes                                | PR100N, NP100N | ±3.0                      | 3.00    | N/A                          |

| This work | VDTA = 1                 | 0 + 2             | yes                    | ves               | yes                                | TSMC 0.25-um   | ±1.5                      | 2.46    | 2.09                         |

Table 2 — Comparative study of the proposed quadrature oscillator in Fig. 3 with the previous designs

#### Notes

N/A = Not Available, CCII = Second-Generation Current Conveyor, DVCC = Differential Voltage Current Conveyor, CDBA = Current Differencing Buffered Amplifier, CCCDBA = Current Controlled Current Differencing Buffered Amplifier, GCFTA = Generalized Current Follower Transconductance Amplifier, UGVF = Unity-Gain Voltage Follower, CDTA = Current Differencing Transconductance Amplifier, CFTA = Current Follower Transconductance Amplifier, FDCCII = Fully- Differential Second-Generation Current Conveyor.

Fig. 8 —  $f_o$  variation with  $I_B$

for the proposed compact quadrature oscillator designed in this work and the previously reported ones<sup>9,11-27</sup> is summarized in Table 2.

#### **6 Conclusions**

This paper proposes a circuit design for a compact resistorless sinusoidal quadrature oscillator. The proposed dual-mode quadrature oscillator features the following salient benefits simultaneously: (i) uses only one VDTA and two grounded capacitors, which is a canonical and resistorless configuration; (ii) produces voltage-mode as well as current-mode quadrature outputs explicitly; (iii) provides high-output impedance quadrature currents, thus permit the feature of cascadability; (iv) offers an electronic tuning of the oscillation frequency; and (v) has low active/passive sensitivity performance. It has been shown by PSPICE program that the simulation results agree well with the theoretical conclusions.

### Acknowledgment

This work is supported by the Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang (KMITL). The author also would like to thank Ms Sasitaporn Theingjit for performing the circuit simulations.

#### References

- 1 Yesil A, Kacar F & Kuntman H, *Radio Eng*, 20 (2011) 632.

- 2 Prasad D, Bhaskar D R & Srivastava M, Indian J Pure Appl Phys, 51 (2013) 864.

- 3 Yesil A & Kacar F, Radioengineering, 22 (2013) 1016.

- 4 Satansup J, Pukkalanun T & Tangsrirat W, Circuits Syst Signal Process, 32 (2013) 945.

- 5 Satansup J & Tangsrirat W, Microelectron J, 45 (2014) 613.

- 6 Jerabek J, Sotner R & Vrba K, Rev Roum Sci Technol, 59 (2014) 163.

- 7 Prasad D & Bhaskar D R, ISRN Electron, 2012 (2012) doi: 10.5402/2012/382560.

- 8 Herencsar N, Sotner R, Koton J, Misurec J & Vrba K, *Elektron Elektrotech*, 19 (2013) 87.

- 9 Prasad D, Srivastava M & Bhaskar D R, Circuits Syst, 4 (2013) 169.

- Biolek D, Senani R, Biolkova V & Kolka Z, Radio Eng, 17 (2008) 15.

- 11 Minhaj N, Int J Electron, 94 (2007) 663.

- 12 Maheshwariang S, Mohan J & Chauhan D S, J Circuits Syst Comput, 19 (2010) 1597.

- 13 Tangsrirat W & Pisitchalermpong S, Frequenz, 61 (2007) 102.

- 14 Tangsrirat W, Pukkalanun T & Surakampontorn W, Act Passive Electron Compon, (2008) 247171.

- 15 Tangsrirat W, Prasertsom D, Piyatat T & Surakampontorn W, Int J Electron, 95 (2008) 1119.

- 16 Khateb F, Jaikla W, Kubanek D & Khatib N, Analog Integr Circuits Signal Process, 74 (2013) 4199.

- 17 Herencsar N, Vrba K, Koton J & Lahiri A, Int J Electron, 97 (2010) 897.

- 18 Maheshwariang S & Chaturvedi B, *Int J Circuits Theor Appl*, 39 (2011) 427.

- 19 Keskin A U & Biolek D, IEE Proc Circuits Devices Syst, 153 (2006) 214.

- 20 Lahiri A, IEICE Electron Exp, 6 (2009) 135.

- 21 Tangsrirat W & Tanjaroen W, Indian J Pure Appl Phys, 48 (2010) 363.

- 22 Jaikla W, Siripruchyanun M, Bajer J & Biolek D, Radio Eng, 17 (2008) 33.

- 23 Jin J & Wang C, Int J Electron Commun (AEU), 66 (2012) 933.

- 24 Horng J W, Hou C L, Chang C M, Chou H P, Lin C T & Wen Y H, ETRI J, 28 (2006) 486.

- 25 Maheshwariang S & Khan I A, J Act Passive Electron Dev, 2 (2007) 137.

- 26 Lahiri A, Analog Integr Circuits Signal Process, 61 (2009) 199.

- 27 Lahiri A, Radio Eng, 18 (2009) 522.

- 28 Arbel A F & Goldminz L, Analog Integr Circuits Signal Process, 2 (1992) 243.