Indian Journal of Pure & Applied Physics Vol. 55, February 2017, pp. 97-103

# Design and performance analysis of a new efficient coplanar quantum-dot cellular automata adder

Gurmohan Singh<sup>a</sup>\*, Balwinder Raj<sup>b</sup> & R K Sarin<sup>b</sup>

<sup>a</sup>Centre for Development of Advanced Computing (C-DAC), Mohali 160 071, India <sup>b</sup>Electronics and Communication Engineering Department, Dr B R Ambedkar National Institute of Technology, Jalandhar 144 011, India

Received 10 May 2016; revised 7 September 2016; accepted 5 October 2016

Quantum-dot cellular automata (QCA) nanotechnology has the potential for revolutionizing the way computers are used. QCA computing has numerous advantages of ultra-low energy dissipation, improved performance and high device density. An adder is the most elementary component in arithmetic units of processors. Lot of work has been in progress to design and implement efficient adder circuits in QCA nanotechnology. This paper presents design and performance analysis of a new efficient coplanar adder in QCA nanotechnology. The proposed adder design uses 20% less QCA cells as compared to previous similar design due to better arrangement of QCA cells in the layout and has a delay of 1 clock cycle with an area of  $0.04 \ \mu m^2$ . The proposed adder has 19% less average leakage energy dissipation, 28% less average switching energy dissipation, and 25% less average energy dissipation than the best reported previous coplanar adder design. The cost function of proposed efficient adder is equal to best reported previous coplanar adder.

Keywords: Quantum cellular automata (QCA), Majority gate, Coplanar, QCA designer, QCA pro, Cost function

## **1** Introduction

Present CMOS technology has been facing several technological and fundamental challenges. This has slowed down the pace of CMOS technology and researchers are exploring alternate viable technologies those can replace CMOS in future circuits and systems<sup>1</sup>. Nanocomputing in broader sense refers to computing systems realized from nanoscale devices. Current nanocomputing research covers the study of novel nanoscale devices, quantum dots, heterostructures, carbon nanotubes, single electron structures and various molecules. These devices and structures exhibit quantum mechanical nature of the electrons. QCA has been identified as one of the key technologies for future computing applications. QCA is an emerging nanocomputing model that encodes, processes, and transfers digital information in a new way. QCA nanotechnology adopts transistor-less approach and employs arrays of QCA cells interacting among themselves by Coulombic repulsion over large arrays. The alignment of electrons at the edges provides the computational output. An external clock signal controls the alignment and the QCA circuits operate on the principle of Boolean logic<sup>2</sup>.

R Feynman, a Nobel laureate on December 29<sup>th</sup> 1959, delivered an excellent talk entitled "There's plenty of room at the bottom: an invitation to enter a new field of physics" on miniaturization to nanoscale. This opened multitude of new opportunities in this field<sup>3</sup>. G Bourianoff reviewed developments in the silicon industry over the past few decades to identify need of emerging nanoscale technologies. He categorized the devices, architectures, variables, and data representations that fall in this new space of emerging nanoscale technologies<sup>4</sup>. T V Gopal discussed trends, directions and applications in the field of nanocomputing<sup>5</sup>. Lent *et al.* from Notre Dame University in 1993 proposed a new paradigm called Ouantum-dot Cellular Automata (OCA), a new nanostructure comprising of quantum-dots. QCA computing paradigm can process binary data at very high speed with extremely small power consumption<sup>6</sup>. Walus et al. have developed a design tool and explored it for QCA nanotechnology. They emphasized the need to develop new design and simulation tools to explore new emerging QCA based circuits and architectures<sup>7-8</sup>. Vankamamidi et al.9 introduced techniques for clocking of the QCA circuits and systems. The critical path length in each clocking zone is reduced utilizing 2D techniques. Srivastava et al.

<sup>\*</sup>Corresponding author (E-mail: gurmohan@cdac.in)

introduced the model for energy dissipation in QCA circuits<sup>10</sup> and a power estimation tool QCA Pro<sup>11</sup>.

## 2 Quantum-Dot Cellular Automata (QCA)

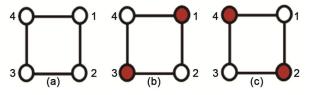

Quantum dots are minuscule nanostructures arranged in arrays for meaningful computation. QCA architecture exploits arrangement of individual electrons that interact by Coulombic repulsion. This brought a major change in information processing way from the prevailing transistor based current switching circuits and systems. QCA approach implement a smart binary information processing method suitable for nanostructures. This new approach overcame limitations of transistor based circuits and systems. The polarization of QCA cell represents the binary information stored in the arrays of QCA cells. Polarization is the extent to which electronic charges align along the two cell diagonals. The standard solid state QCA cell has a cell height and width of 18 nm and quantum-dot diameter<sup>12</sup> of 5 nm. Figure 1(a)shows a typical quantum cellular automata (QCA) cell. Two electrons within a cell can tunnel amongst the four quantum-dots and no tunneling is permissible between nearby cells. The physical mechanism responsible for interactions within a cell is quantummechanical tunneling. At nanoscale the electron wave function starts leaking out of the restricting potential of a dot. The rate of this leaking can be restricted by having optimal spacing between quantum-dots of a cell during fabrication<sup>13-14</sup>. The quantum dots in a square QCA cell are assigned slot numbers clockwise from the dot 1 to 4 shown in Fig. 1(a). Figure 1(b) and (c) shows cell representing binary state '1' and '0', respectively. The two states in which electrons are in position '1' and '3' and '2' and '4' represent two stable ground states. These states are used for meaningful computations in digital circuits.

#### 2.1 QCA nanostructures

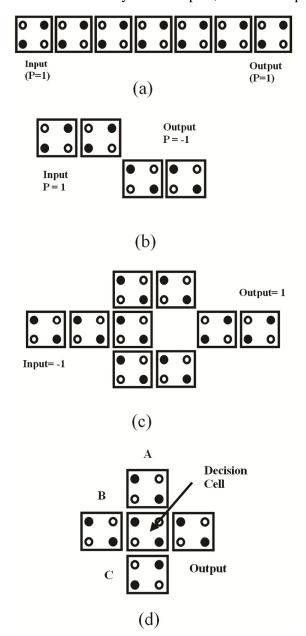

The two anti-podal stable ground states in a QCA cell are used to characterize two logic levels in digital circuits. Figure 2(a) shows a typical QCA binary wire realization<sup>15-16</sup>. The polarization of input QCA cell is fixed and it propagates to output QCA cell through

Fig. 1 – (a) Basic four-dot cell, (b) Binary logic '1' encoding, and (c) Binary logic '0' encoding

Coulombic interactions occurring between nearby cells in the array, thus realizing a binary wire. There is no flow of electric charge when information propagates from input to output; only electronic polarization propagates towards output resulting in extremely low power dissipation. Figure 2(b) and (c) represents two different inverter realizations. Figure 2 (d) depicts a 3-input majority gate. It is the most fundamental device structure used in QCA circuits and systems. The middle cell is called decision cell and it is surrounded by 3 fixed inputs, labeled as input

Fig. 2 – (*a*) a QCA binary wire, (*b*) an inverter (c) an alternate inverter configuration, and (d) Majority  $\text{Gate}^7$

A, input B, input C and one output. The decision cell acquires polarization according to polarization of majority of inputs. The output cell may drive other cells or wires. The majority gate can also function as programmable 'AND' and 'OR' gates provided one of its inputs is set at polarization state '-1' or '1'. So, any Boolean function can be realized in QCA logic using majority gates and inverters.

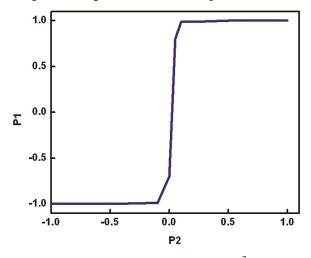

#### 2.2 Cell-cell response

The polarization of an isolated cell is different and adjusts if it is encircled by other cells. Figure 3 illustrates that polarization of a cell 1 (P1) is influenced by polarization of its nearby cell (P2). If there is a minute variation in polarization of cell 2, it may result in complete change in polarization of cell 1 by dynamically preferring one arrangement above the other. The steepness of polarization response curve is determined by the ratio of the quantum tunneling energy to the Coulombic energy for electrons on nearby sites. Presence of Coulomb repulsion within a cell tends to keep electrons apart. A careful design of cells must have strong nonlinear coupling characteristics. This response curve has two bistable states which forms the basis for digital computation. The nonlinear saturation is basically equivalent to gain facilitating in refurbishing signal levels stage after stage. The major advantage is that no power dissipation is involved when switching takes place from one state to another<sup>17-18</sup>.

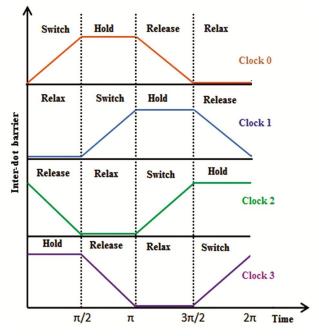

## 2.3 QCA clocking

The clock signal in QCA circuits plays a vital role in realizing timing. The layout of QCA cells in a circuit is partitioned into different clock zones. During clocking each zone is provided with a

Fig. 3 - The cell-cell response curve<sup>7</sup>

particular phase. A QCA cell experiences four clock zones- clock 0, clock 1, clock 2 and clock 3. Each clock zone has four different phases labeled as Switch, Hold, Release, and Relax. There is a phase shift of 90° between four successive phases of a clock zone. Figure 4 elaborates four phase switching realized in each clocking phases in different clock zones. The cells are unpolarized initially and inter-dot potential barriers are in low state before switching phase. The QCA cells start unpolarizing and their inter-dot potential barriers are low in switch phase. Then the inter-dot barriers are gradually raised and the electrons transfer amongst the quantum-dots in a cell starts and the QCA cells assume one of two ground state polarization states, i.e., either P = 1 or  $\tilde{P} = -1$  according to state of their input cells<sup>9,18-19</sup>. The inter-dot tunneling barriers become high at the end of switch phase. In the hold phase, high state of tunneling barriers is maintained. During release phase, inter-dot tunneling barriers are lowered and QCA cells are allowed to become unpolarized. In relax clock phase, inter-dot tunneling barriers remain lowered and OCA cells are in an unpolarized state. Information transfers in a pipelined manner from inputs towards outputs during four clock zones.

# **3** Evolution of QCA Adders

One of the most basic components in arithmetic units is the full adder (FA). So, design of a robust adder in QCA technology is basic necessity for a high

Fig. 4 – Clocking phases in different clock zones<sup>15</sup>

performance arithmetic unit. Lot of research work has been going on towards design of structurally robust and efficient OCA adders. Broadly, depending on wire crossing method QCA adders are classified into two categories- coplanar and multi-layer. In coplanar adders all QCA cells are arranged in the same plane, whereas in multi-layer adders QCA cells are arranged in different planes. Tougaw and Lent proposed first OCA-based 1-bit full adder (FA) design comprising of five majority gates, three inverters, and 9 wire crossovers. It utilizes 192 QCA cells. Another QCA FA proposed by Wang et al. comprises of three majority gates and two inverters, 6 wire crossovers and utilizes only 145 QCA cells<sup>20</sup>. Hänninen et al. proposed a new QCA adder layout comprising of three majority gates and two inverters, 3 wire crossovers and utilizes only 102 QCA cells<sup>21</sup>. Abedi et al. introduced a new coplanar adder design that uses clock-zone based technique to eliminate wire crossover problem. It comprises of three majority gates and two inverters, and utilizes only 59 QCA cells with no wire crossovers<sup>22</sup>. Apart from coplanar adders, new OCA adder designs, multi-layer adder designs, and fault-tolerance in adders have been presented by many researchers<sup>23-31</sup>. The major advantages offered by multi-layer adder deign are the reduced complexity and delay. However, multi-layer designs impose several fabrication related constraints. The fabrication cost for a multi-layer design is considered to be 3 times than that of a coplanar design.

# 4 Proposed Coplanar QCA Adder Design

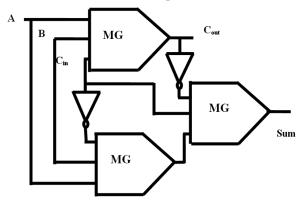

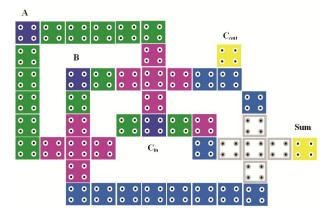

A new highly area efficient coplanar QCA adder design is proposed in this section. The schematic of the proposed coplanar adder is shown in Fig. 5. It comprises of 3 majority gates and two inverters with no wire crossing. The proposed QCA adder uses only 47 QCA cells and area efficient as compared to other coplanar adders reported in literature. This new design has latency of only 1 clock cycle. Figure 6 shows QCA implementation of the proposed coplanar QCA adder. Table 1 shows comparison of coplanar QCA full adders in terms of performance metricsnumber of majority gates, number of inverters, number of wire-crossings, delay, and OCA cells. It is evident that proposed coplanar QCA adder employs same number of majority gates and inverters as reported in best coplanar QCA adder<sup>30</sup> with no wirecrossing and delay of 1 clock cycle. Also the proposed adder design uses 20% less QCA cells due to better arrangement of QCA cells in the layout.

It also avoids use of clock-zone based technique to eliminate wire cross-over problem as optimization of delay of a complex QCA circuits becomes very tedious task.

### **5** Simulation Results

The functional verification of the proposed design as well as of previous coplanar full adder designs reported in literature has been performed using QCA designer version 2.0.3 tool. The coherence vector simulation parameters used are: cell width =18 nm, cell height =18 nm, dot diameter =5 nm, relaxation time = $1 \times 10^{-15}$  s, time-step = $0.1 \times 10^{-15}$  s, total

Fig. 5 - Schematic design of proposed coplanar adder

Fig. 6 - QCA implementation of proposed coplanar adder

Table 1 – Comparison of coplanar QCA full adders

| Coplanar<br>adders     | Number<br>of majority<br>gates | Number<br>of<br>inverters | Number<br>of wire-<br>crossings | 2    | Number<br>of QCA<br>cells |

|------------------------|--------------------------------|---------------------------|---------------------------------|------|---------------------------|

| Tougaw <sup>12</sup>   | 5                              | 3                         | 9                               | 1.25 | 192                       |

| Wang <sup>20</sup>     | 3                              | 2                         | 6                               | 1.25 | 145                       |

| Hänninen <sup>21</sup> | <sup>1</sup> 3                 | 2                         | 3                               | 2    | 102                       |

| Abedi <sup>22</sup>    | 3                              | 2                         | 0                               | 1    | 59                        |

| Proposed adder         | 3                              | 2                         | 0                               | 1    | 47                        |

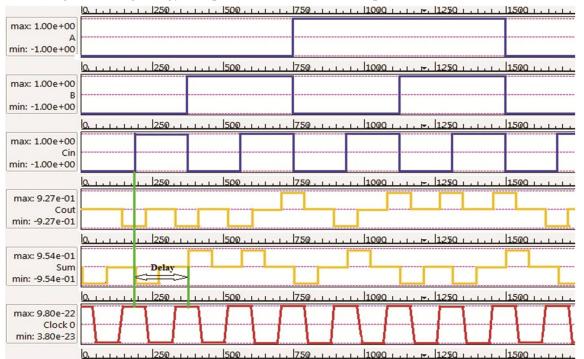

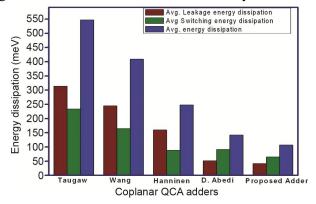

simulation time = $7.0 \times 10^{-11}$  s, clock high = $9.8 \times 10^{-22}$  J, clock low =  $3.8 \times 10^{-23}$  J, clock shift =0, clock amplitude factor =2.0, radius of effect =80.0 nm, relative permittivity =12.9, and layer separation =11.5nm. Figure 7 presents the simulation waveforms for the proposed coplanar full adder design. The output 'Sum' is high when inputs (ABC<sub>in</sub>) are '001', '010', '100', and '111'. Similarly output carry 'Cout' is high when inputs (ABC<sub>in</sub>) are '011', '101', '110', and '111'. As evident from simulation results, the output 'Sum' appears after a delay of 1 clock cycle and output carry 'Cout' after a delay of 0.75 clock cycles. An accurate power estimation tool QCA Pro has been used for energy dissipation results and generating thermal layout of the proposed adder design. Table 2 lists energy dissipation results of coplanar QCA full adders and Fig. 8 shows the bargraph comparison of computed leakage energy dissipation, average switching energy dissipation, and

average energy dissipation with reported QCA adder circuits. The results reveals that proposed adder design dissipate 28% less switching energy, 19% less average leakage energy and 25% less average energy as compared to previous best coplanar adder circuit at  $1.0E_k$  tunneling energy level.

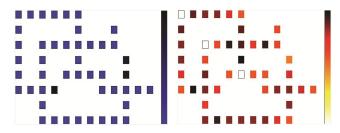

Figure 9(a) shows layout of polarization level of each cell in the proposed adder. The darker cells indicate higher levels of polarization. Figure 9(b) illustrates thermal layouts generated using QCA Pro tool for the proposed coplanar adder circuit. The dark cells in the circuit represent more average energy dissipation. The polarization level layout and thermal layout have been generated by simulating the proposed adder circuit considering all inputs from 000 to 111 for tunneling energy level of  $1.0E_k$  and 2.0 K temperature.

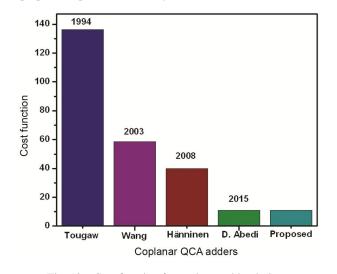

A set of new cost functions has been proposed suitable for performance evaluation of QCA circuits<sup>32</sup>.

Fig. 7 - Simulation waveforms for the proposed coplanar adder design

Table 2 - Comparison of energy dissipation results of coplanar QCA full adders

| Coplanar adders        | Average leakage energy dissipation (meV) | Switching energy dissipation (meV) | Average energy dissipation (meV) |

|------------------------|------------------------------------------|------------------------------------|----------------------------------|

| Tougaw <sup>12</sup>   | 313.84                                   | 233.3                              | 547.16                           |

| Wang <sup>20</sup>     | 244.50                                   | 164.56                             | 409.05                           |

| Hänninen <sup>21</sup> | 160.06                                   | 87.89                              | 247.95                           |

| Abedi <sup>22</sup>    | 51.41                                    | 90.92                              | 142.33                           |

| Present study          | 41.68                                    | 65.17                              | 106.86                           |

The cost function can be computed by Eq. (2) as follows:

$$\operatorname{Cost}_{\operatorname{QCA}} = (M^{\mathsf{K}} + I + C^{\mathsf{I}}) \times T^{\mathsf{p}}, \ 1 \le k, \ l, \ p \qquad \dots (1)$$

where, M, C, and I represent number of majority gates, number of wire crossovers, and inverters respectively. The term T represent delay of the circuit and k, l, p are exponential weightings for majority gate count, wire crossover count and delay.

Fig. 8 – Bar-graph comparison of proposed adder design with previous reported designs

Fig. 9 – (a) Layout of polarization level of proposed adder design and (b) Thermal layout for average energy dissipated in each cell of proposed coplanar adder design

Fig. 10 – Cost function for coplanar adder designs

The cost functions provide different metrics in accordance with values assigned to k, l and p. The values assigned to k, l and p are decided according to the overall design optimization goal. The cost function have been evaluated for Taugaw<sup>12</sup>, Wang<sup>20</sup>, Hänninen<sup>21</sup>, Abedi<sup>22</sup>, and the proposed coplanar QCA adder circuits for generalized case of k=2, l=2, and p=1 as shown in Fig. 10. The Taugaw adder has highest cost function value, i.e., it is complex and poor in performance. The best reported Abedi QCA adder<sup>22</sup> and proposed adder have equal cost function value. It means the proposed coplanar adder is not complex and is better in performance.

# **6** Conclusions

This paper presents design and performance analysis of a new efficient coplanar OCA adder design. The proposed QCA adder design has been functionally verified using QCA designer tool and energy dissipation computations have been performed using QCAPro tool. The proposed adder design utilizes '3' three-input majority gates and two inverters only. It uses only 47 normal QCA cells with an area of 0.04  $\mu$ m<sup>2</sup> and has delay of 1 clock cycle. It has 20% less QCA cells as compared to previous similar design due to better arrangement of QCA cells in the layout. The proposed adder circuit uses no wire cross-over. The proposed adder dissipates 19% less average leakage energy, 28% less average switching energy, and 25% less average energy than best reported previous coplanar adder design. It has cost function equal to best reported previous design.

#### References

- 1 International Technology Roadmap for Semiconductors (ITRS) 2005 (Online). Available: http://www.itrs.net

- 2 Lent C S, Taugaw P D, Porod W & Berstein G H, Nanotechnology, 4 (1993) 49.

- 3 Feynman R, *Eng Sci*, California Institute of Technology, 22 (1960).

- 4 Bourianoff G, Computer, 36 (2003) 44.

- 5 Gopal T V, Nanocomputing, (Anna University), 2011.

- 6 Lent C S, Taugaw P D & Porod W, *Quantum cellular* automata: The physics of computing with arrays of quantum dot molecules, Proceeding of the workshop on physics and computation, Dallas, Texas, (1994) 5.

- 7 Walus K, Dysar T J, & Jullien G A, *IEEE Trans* Nanotechnol, 3 (2004) 26.

- 8 Wang W, Walus K & Jullien G A, *Quantum-dot cellular automata adders*, Third IEEE Conf. on Nanotechnology, San Francisco, CA, USA, (2003) 12-14.

- 9 Vankamamidi V, Ottavi M & Lombardi F, IEEE Trans Comput-Aided Design Integr Circuits Syst, 27 (2008) 34.

- 10 Srivastava S, Sarkar S & Bhanja S, *IEEE Trans Nanotechnol*, 8 (2009) 116.

- 11 Srivastava S, Asthana A, Bhanja S & Sarkar S, 2011 IEEE International Symposium on Circuits and Systems, (2011) 2377.

- 12 Taugaw P D & Lent C S, J Appl Phys, 75 (1994) 1818.

- 13 Lent C S & Tougaw P D, J Appl Phys, 74 (1993) 6227.

- 14 Porod W, Lent C S & Bernstein G H, Int J Electro, 86 (1999) 549.

- 15 Lent C S & Tougaw P D, *Proc IEEE*, 85 (1997) 541.

- 16 Orlov A O, Amlani I & Bernstein G H, Sci Mag, 227 (1997) 928.

- 17 Amlani I, Orlov A O, Kummamuru R K & Bernstein G H, Appl Phys Lett, 77 (2000) 738.

- 18 Timler J & Lent C S, J Appl Phys 91 (2002) 823.

- 19 Hennessy K & Lent C S, J Vac Sci Technol B: Microelectron Process Phenom, 19 (2001) 1752.

- 20 Zhang R, Walus K, Wang W, Jullien G A, *IEEE Int Symp Circuits Syst*, (2005) 2522.

- 21 Hänninen I & Takala J, Arithmetic design on quantum-dot cellular automata nanotechnology, Int Symp on Systems: Architecture, Modeling, and Simulation, Greece, (2008) 43.

- 22 Abedi D, Jaberipur G & Sangsefidi M, *IEEE Trans* Nanotechnol, 14 (2015) 497

- 23 Cho H & Swartzlander E E, Pipelined carry lookahead adder design in quantum-dot cellular automata, Thirty-Ninth

Asilomar Conference on Signals, Systems and Computers, Pacific Grove, CA, (2005) 1191.

- 24 Cho H & Swartzlander E E, Modular design of conditional sum adders using quantum-dot cellular automata, Sixth IEEE Conference on Nanotechnol, Cincinnati, USA, (2006) 363.

- 25 Cho H & Swartzlander E E, *IEEE Trans Nanotechnol*, 6 (2007) 374.

- 26 Navi K, Farazkish R, Sayedsalehi S & Azghadi M R, *Microelectronics*, 41 (2010) 820.

- 27 Hänninen I & Takala J, J Sign Process Syst, 58 (2010) 87.

- 28 Pudi V & Sridharan S, *IEEE Trans VLSI Syst*, 19 (2011) 1535.

- 29 Bruschi F, Perini V & Rana D Sciuto, An efficient quatun-dot cellular automata adder, Design, Automation, & Test in Europe Conference & Exhibition, Grenoble, France, (2011) 1220.

- 30 Liu W, Lu L, O Neill M & Swartzlander E E, *IEEE Trans Nanotechnol*, 13 (2014) 476.

- 31 Hayati M & Rezaei A, Int J Circuits Theor Appl, 43 (2014) 1446.

- 32 Liu W, Lu L, O' Neill M & Swartzlander E E, *IEEE Int Symp Circuits Syst*, (2012) 1347.