Missouri University of Science and Technology Scholars' Mine

Electrical and Computer Engineering Faculty Research & Creative Works

**Electrical and Computer Engineering**

01 Jun 2005

# Environmental-Based Characterization of SoC-Based Instrumentation Systems for Stratified Testing

N. J. Park

Koshy M. George

Nohpill Park

Minsu Choi Missouri University of Science and Technology, choim@mst.edu

et. al. For a complete list of authors, see https://scholarsmine.mst.edu/ele\_comeng\_facwork/1595

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

## **Recommended Citation**

N. J. Park et al., "Environmental-Based Characterization of SoC-Based Instrumentation Systems for Stratified Testing," *IEEE Transactions on Instrumentation and Measurement*, vol. 54, no. 3, pp. 1241-1248, Institute of Electrical and Electronics Engineers (IEEE), Jun 2005. The definitive version is available at https://doi.org/10.1109/TIM.2005.847131

This Article - Journal is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# Environmental-Based Characterization of SoC-Based Instrumentation Systems for Stratified Testing

N.-J. Park, K. M. George, Nohpill Park, Minsu Choi, Yong-Bin Kim, and Fabrizio Lombardi

Abstract—This paper proposes a novel environmental-based method for evaluating the good yield rate (GYR) of systems-on-chip (SoC) during fabrication. Testing and yield evaluation at high confidence are two of the most critical issues for the success of SoC as a viable technology. The proposed method relies on different features of fabrication, which are quantified by the so-called Fabrication environmental parameters (EPs). EPs can be highly correlated to the yield, so they are analyzed using statistical methods to improve its accuracy and ultimately direct the test process to an efficient execution. The novel contributions of the proposed method are: 1) to establish an adequate theoretical foundation for understanding the fabrication process of SoCs together with an assurance of the yield at a high confidence level and 2) to ultimately provide a realistic approach to SoC testing with an accurate yield evaluation. Simulations are provided to demonstrate that the proposed method significantly improves the confidence interval of the estimated yield as compared with existing testing methodologies such as random testing (RT).

*Index Terms*—System on a chip, fault coverage, defect level, fabrication environmental parameter (EP), good yield rate (GYR), random testing (RT), stratified testing (ST).

#### NOMENCLATURE

| EP    | (Fabrication) environmental parameter. |

|-------|----------------------------------------|

| GYR   | Good yield rate.                       |

| IP    | Intellectual property.                 |

| KGY   | Known-good-yield.                      |

| RT    | Random testing.                        |

| ST    | Stratified testing.                    |

| SoC   | System-on-chip.                        |

| MCM   | Multichip module.                      |

| ANOVA | Analysis of variance.                  |

|       | -                                      |

### I. INTRODUCTION

T HE increasing demand on high operational speed, density, and customization for high-performance computing has motivated the development and design of new instrumentation and measurement systems. Due to its many advantages [1]–[10], SoC is emerging as one of the key technology for the development of high-performance instrumentation [11]. The rapid advances for manufacturing complex integrated circuits have been

M. Choi is with the Department of Electrical and Computer Engineering, University of Missouri-Rolla, Rolla, MO 65409 USA (e-mail: choim@umr.edu).

Y.-B. Kim and F. Lombardi are with the Department of Electrical and Computer Engineering, Northeastern University, Boston, MA 02115 USA (e-mail: ybk@ece.neu.edu; lombardi@ece.neu.edu).

Digital Object Identifier 10.1109/TIM.2005.847131

made possible by the complex integration of a large number of components and devices. Today, a complete system can be integrated and assembled on a single chip (e.g., SoC). The miniaturized size as well as performance benefits (such as low power consumption, high speed and thermal dissipation) have made possible a rapidly expanding market for SoC.

SoCs are generally manufactured by integrating a set of embedded IP cores; these cores are designed and procured from different core providers and integrated with in-house custom-logic designs on a single chip. The embedded core-based manufacturing of such a system necessitates new methods and procedures for testing, repair and yield management due to the unavailability of *a priori* information about the embedded IP cores and their relation with the custom logic design.

For an SoC it is imperative to adequately assure and improve the fabrication yield with multiple IP cores at integration [27]–[29]. For an efficient integration of embedded IP cores, few variables can reveal the relevant information pertaining to the manufacturing yield of the IP cores throughout the fabrication and design flow [30]. Furthermore, to facilitate seamless integration of IP cores into in-house custom-logic designs, the IP cores can have configurable features [31] to create a flexible environment for the integration and manufacturing process as the ultimate objective is to attain a high yield.

The main objective of the proposed method is two-fold: 1) to provide a better understanding of the integration and fabrication of SoCs for acceptable yield at a high confidence level and 2) to propose an efficient test approach for evaluating the GYR. The proposed method relies on a set of features which can be experimentally established in the fabrication process; these features affect the yield and test quality, and are extracted and quantified; in this paper they are referred to as the EPs. EPs can be highly correlated to the GYR. The correlation between EPs can be used together with other fabrication-related parameters to develop an estimate of the GYR and an effective stratified-based test process for the SoCs. Moreover, the proposed approach can also be used to assure an adequate level of yield of the SoCs. However, the correlation in the environmental-based parameters (such as for example temperature, stress and pressure) and related estimators (such as yield and defect level) is not readily available to designers; therefore, their applicability to test methodologies (such as sampling-based ST) must be assessed. To address these issues a new and adequate measure, referred to as the GYR, is introduced in this paper. GYR is used to efficiently guide the fabrication process-related techniques (such as ST and yield assurance) at a high confidence level.

This paper is organized as follows. In Section II, the current literature as related to SoC testing is reviewed; previous works

Manuscript received June 15, 2003; revised September 19, 2004.

N.-J. Park, K. M. George, and N. Park are with the Department of Computer Science, Oklahoma State University, Stillwater, OK 74078 USA (e-mail: noh@a.cs.okstate.edu; kmg@a.cs.okstate.edu; npark@a.cs.okstate.edu).

are also introduced. The principles and the characterization of the proposed method are described in Section III. Performance evaluation of the proposed environmental-based testing method and its comparison with a random sampling-based test method are presented in Section IV. In the final section, discussion and conclusions are presented.

#### II. REVIEW AND PRELIMINARY

Today's high density and complexity of IC technology such as MCM and SoC allow the design of complex digital instrumentation systems. These systems require an extensive test process to assure proper fabrication and reliable products; different methods have been proposed to address testing of these systems [16]-[25]. However, it is almost impossible to test these chips exhaustively due to the excessive time overhead and severe limitations in both controllability and observability (inclusive of electrical access for example). This severely restricts the use of conventional approaches [12], [15], [16] for manufacturing test of today's technologies such as MCM and SoC. Novel approaches musy be adopted to guarantee the quality of the incoming bare (unpackaged) chips prior to either module assembly or IP core integration. Together with other features (such as the structural integrity and performance of the assembled devices or chips), isolation and repair of defective parts have been advocated [15].

Exhaustive testing for defect and/or fault detection is too costly and impractical when manufacturing SoCs [16]-[19]. A different method that partially avoids many of the disadvantages of exhaustive testing, is based on sampling, i.e., chips are tested from a randomly sampled set, hence, such method is referred to as random sampling-based testing. A stratified method has been proposed for testing MCM systems [16]. Its advantages are the improvement in quality level and cost-effectiveness. This approach referred to as the lowest yield-stratum first-testing (LYSFT) considers the unevenness of KGY of stratification as a criterion for testing the chips on a MCM for quality enhancement. An MCM is composed of a number of sets (or strata) of chips with a KGY. Each stratum is procured from a separate manufacturer [16]. Stratified-based testing and yield assurance of MCMs are, however, fundamentally different from SoC due to the unavailability of a priori yield information, or the so-called unknown-good-yield problem [5].

As an SoC is designed and manufactured using deeply embedded IP cores on a single chip, in practice it is not possible to rely on conventional testing and yield evaluation methods. There is no *a priori* information or data available on the yield of the fabricated IPs due to the different integration and manufacturing processes of the cores. This is also different from previous technologies in which the KGY of chips [application-specific IC (ASIC) or MCM] for example is extracted from physical-level information. Also, due to higher density and complexity at deep submicron level, conventional fabrication methods are facing tremendous challenges for manufacturing SoCs. SoC manufacturing has encountered substantial problems for attaining an acceptable yield at high confidence level for a realistic testing technique. For SoCs, conventional testing methods are impractical and costly; methods based on Very Large Scale Integration (VLSI) for ASIC and MCM are not effective because they may not capture the new processes involved in SoC manufacturing. Moreover, wafer or chip level information has limited relevance due to the different integration processes of the IP cores and the lack of known physical-level features on the yield. For example, custom optimized ASICs have a well-exercised yield; MCMs have been characterized using a KGY. Since there is no significant information available during the integration and testing of the embedded IP cores, past work on correlation between fabrication and related features (such as yield and defect level), is not fully applicable.

The proposed method employs a set of features which experimentally appear in the fabrication process and directly affect the yield and test quality. These features are extracted and quantified; they are referred in this paper as the EPs. EPs can be also highly correlated and through an extensive statistical analysis, they can be used to derive a stratified-based test process and to assess the yield of the SoC. Then, the GYR is used as a criterion to effectively guide the ST while retaining a high coverage. An accurate GYR is established by using the proposed method in which highly correlated EPs are categorized at different levels through a characterization of different EPs and a statistical analysis of their correlations. This process can identify the stratification criteria for selecting (or sampling) the chips (as components of the SoC) and testing them by providing statistical information on whether or not an EP has a significant impact on the GYR. This is possible because SoCs from the same wafer are fabricated under an homogeneous environment, i.e., no significant variations occur within a wafer. Therefore, sampling is conducted at SoC-level and EPs are used to guide the sampling-based testing process through a novel characterization process; this process effectively relies on a statistical test hypothesis technique that employs the ANOVA method. Different measures such as the level in each EP for a given SoC fabrication condition, or the stratification variables for sampling-based testing to estimate the GYR, are employed. Having identified a proper stratification structure, a post-stratified sampling-based test process is conducted to estimate the unbiased estimator of GYR by using a ratio estimation technique. This paper will provide an efficient theoretical framework to realize a new SoC-specific testing method and to enhance the confidence level of the estimated GYR with high accuracy. Ultimately, the efficient testing of the SoC as final product will be assessed by assemblying the IP cores.

#### III. PROPOSED ENVIRONMENTAL-BASED TESTING

The proposed ST method firstly identifies and selects a set of EPs that are highly correlated with GYR, using a multiway classification technique. Next, it builds a stratified sampling-based testing framework in which the EPs are divided into levels as test criterion. Finally, an unbiased estimator is derived for the GYR with minimum variance as a solution for evaluating the yield of an SoC at fabrication. As an example, a numerical experiment is provided to show that the proposed method significantly improves the confidence interval of the estimated yield compared with conventional RT.

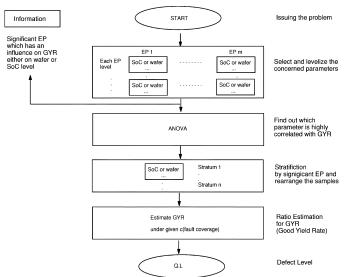

Fig. 1. Proposed environmental-based testing.

|       | D                               |     | D                    |                                   |

|-------|---------------------------------|-----|----------------------|-----------------------------------|

|       | $B_1$                           |     | $B_q$                | mean                              |

|       | $y_{111}$                       | ••• | $y_{1q1}$            |                                   |

| А     | :                               |     | :                    |                                   |

| $A_1$ | $y_{11r}$                       | ••• | $y_{1qr}$            | $\overline{y}_{1}$                |

|       | $\overline{y}_{11.}$            |     | $\overline{y}_{1q.}$ |                                   |

|       | $y_{211}$                       |     | $y_{2q1}$            |                                   |

|       | :                               |     | :                    |                                   |

| $A_2$ | $y_{21r}$                       |     | $y_{2qr}$            | $\overline{y}_{2}$                |

|       | $\overline{y}_{21.}$            |     | $\overline{y}_{2q.}$ |                                   |

| :     | :                               | :   | :                    | :                                 |

|       | $y_{p11}$                       |     | $y_{pq1}$            |                                   |

|       | :                               |     | :                    |                                   |

| $A_p$ | $y_{p1r}$                       | ••• | $y_{pqr}$            | $\overline{y}_{3}$                |

|       | $\overline{\overline{y}}_{p1.}$ | ••• | $\overline{y}_{pq.}$ |                                   |

| Mean  | $\overline{y}_{.1.}$            |     | $\overline{y}_{.q.}$ | Total mean $\overline{y}_{\dots}$ |

Fig. 2. Sample treatment table for two-way classification method.

The proposed procedure to estimate the GYR, is shown in Fig. 1; it consists of different steps which will be outlined in more detail in the following sections. The proposed method has the following unique features as corresponding to each of these steps: through an environmental-based method the EPs and their levels which could be correlated with the GYR, are identified; through a statistical analysis the acceptance test of the EPs and outcome with respect to the correlation with the GYR are established; the stratification conditions for sampling-based testing of the SoCs are then identified; with high accuracy the GYR is estimated through a ratio procedure.

#### A. Environmental Characterization

The environmental characterization of an SoC is dependent on many parameters, and referred to as EPs. An EP can be identified at physical level (such as temperature or pressure) as well as at technology level (line width, power consumption for example). The interaction among EPs can affect different measures (such as GYR) during the fabrication of a SoC.

A *two-way classification* method is proposed for identifying the EPs which can be highly correlated with the GYR. This can

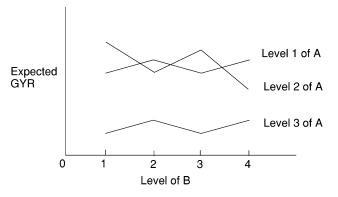

Fig. 3. Interaction between two EPs, A and B.

be extended to a *multi-way classification* without loss of generality [26]. In this paper, for simplicity a two-way classification process is presented for justifying the technical rationale.

Each *level* represents a range of values for EP in the environmental characterization. For instance, suppose two EPs are selected, i.e., the temperature (denoted by  $A = \{A_i\}, i = 1, ..., p$  in level form) and the pressure (denoted by  $B = \{B_j\}, j = 1, ..., q$  in level form). So, there are  $p \times q$  so-called *treatments* (i.e., each treatment is a coparameter of  $A_i$  and  $B_j$ ). Within each treatment a set of SoCs is sampled, i.e.,  $y_{ijk}$  represents the sampled SoCs within the range of the *i*th level of A, the *j*th level of B; and the *r*th sample in the *ij*th treatment, where  $1 \leq i \leq p, 1 \leq j \leq q$ . A sample treatment table can be generated. For example, the levels of each EP can be given as follows: Levels of A (temperature):  $A_1(100 \text{ °C}), A_2(105 \text{ °C}), A_3(110 \text{ °C}), \ldots, A_p$ ; Levels of B (pressure):  $B_1(100 \text{ N/m}^2), B_2(105 \text{ N/m}^2), B_3(110 \text{ N/m}^2), \ldots, B_q$ .

A sample treatment table is shown in Table II, where the total sample size is pqr (where r is the number of SoCs or sample size selected in each treatment). Note that  $\overline{y_{ij}} = (1/r) \sum_{k=1}^{r} y_{ijk}, i = 1, \dots, p; j = 1, \dots, q$  is the mean GYR in each treatment;  $\overline{y_{i..}} = (1/qr) \sum_{j=1}^{q} \sum_{k=1}^{r} y_{ijk}, i =$  $1, \dots, p$  is the mean GYR in each level of  $A; \overline{y_{\cdot j}} =$  $(1/pr) \sum_{i=1}^{p} \sum_{k=1}^{r} y_{ijk}, i = 1, \dots, j = 1, \dots, q$  is the mean GYR in each level of  $B; \overline{y_{...}} = (1/pqr) \sum_{i=1}^{p} \sum_{k=1}^{r} y_{ijk}$ is the total mean GYR from the sampled SoCs.

A novel feature of the proposed ST is the capability to quantify interactions among pairs of EPs (and possibly resulting in an inconsistent deviation from the expected GYR value, if any). This is illustrated in Fig. 3 for A and B; these plots represent the expected response (such as GYR), under the joint effect of A and B. In Fig. 3, the lower two curves are consistent while the top curve (Level 2 of A) is not. Any curve(s) inconsistent with the others (e.g., the Level 2 of A) indicates that there exists dependency between A and B. In this case, sampling for each treatment should be constructed with replacement.

The theoretical model of the two-way classification method (as used in the proposed approach) can be expressed statistically as follows.

Let  $Y_{ijk}$  be the observed GYR of a tested SoC sample within the *i*th level of A, the *j*th level of B, and the *r*th sample of SoC in the *ij*th treatment with  $1 \le i \le p, 1 \le j \le q, 1 \le k \le r$ , hence

$$Y_{ijk} = \mu + \alpha_i + \beta_j + \gamma_{ij} + e_{ijk}, \qquad i = 1, 2, \dots, p$$

$$j = 1, 2, \dots, q, \quad k = 1, 2, \dots, r \quad (1)$$

where  $\mu$  is the total mean GYR from the sampled SoCs;  $\alpha_i$  is the  $Y_{ijk}$  in the *i*th treatment of A;  $\beta_j$  is the  $Y_{ijk}$  in the *j*th treatment of B;  $\gamma_{ij}$  is the interaction between the *i*th treatment and the *j*th treatment.

Let  $e_{ijk}$  be the residual, i.e., the difference between the observed and estimated GYRs, and this can be expressed as

$$e_{ijk} \sim N(0, \sigma^2).$$

(2)

As  $Y_{ijk}$  in each  $\alpha_i, \beta_j, \gamma_{ij}$  is the deviation from the corresponding mean value

$$\sum_{i=1}^{p} \alpha_i = 0 \quad \sum_{j=1}^{q} \beta_j = 0$$

(3)

and

$$\sum_{i=1}^{p} \gamma_{ij} = \sum_{j=1}^{q} \gamma_{ij} = 0.$$

(4)

#### B. Statistical Analysis

By using the model and the equations given previously, a statistical acceptance method such as the *F*-test can be conducted next. The F-test is based on a sum of the squares technique and is used to determine whether to accept an EP, i.e., based on the environmental characterization whether the EP is highly correlated with the GYR under a specified significance level (denoted by  $\alpha$ ); this is the probability of making an erroneous decision when selecting an EP (in generally, its value is rather low). To conduct the F-test two new expressions must be derived. The first equation is the difference (denoted by  $y_{ijk} - \overline{y_{...}}$ ) between the observed GYR ( $y_{ijk}$ ) and the total mean ( $\overline{y_{...}}$ ) of the GYR from the sampled SoCs, i.e.

$$y_{ijk} - \overline{y_{...}} = (\overline{y_{i...}} - \overline{y_{...}}) + (\overline{y_{.j.}} - \overline{y_{...}}) + (\overline{y_{ij}} - \overline{y_{i...}} - \overline{y_{...}}) + (y_{ijk} - \overline{y_{ij}}).$$

(5)

By squaring and summing both sides, then

$$\sum_{i=1}^{p} \sum_{j=1}^{q} \sum_{k=1}^{r} (y_{ijk} - \overline{y_{...}})^2$$

$$= qr \sum_{i=1}^{p} (\overline{y_{i..}} - \overline{y_{...}})^2$$

$$+ pr \sum_{j=1}^{q} (\overline{y_{.j.}} - \overline{y_{...}})^2$$

$$+ r \sum_{i=1}^{p} \sum_{j=1}^{q} (y_{ij} - \overline{y_{i..}} - \overline{y_{.j.}} + \overline{y_{...}})^2$$

$$+ \sum_{i=1}^{p} \sum_{j=1}^{q} \sum_{k=1}^{r} (y_{ijk} - \overline{y_{ij}})^2$$

(6)

where  $\sum_{i=1}^{p} \sum_{j=1}^{q} \sum_{k=1}^{r} (y_{ijk} - \overline{y_{...}})^2 = \text{SST}$  is the sum of the squares (i.e., the variation of each sampled SoC);  $qr \sum_{i=1}^{p} (\overline{y_{i..}} - \overline{y_{...}})^2 = \text{SSA}$  is the sum of the squares (it represents the variation of A);  $pr \sum_{j=1}^{q} (\overline{y_{.j.}} - \overline{y_{...}})^2 = \text{SSB}$  is the sum of the squares (it represents the variation of B);  $r \sum_{i=1}^{p} \sum_{j=1}^{q} (y_{ij} - \overline{y_{i..}} - \overline{y_{...}})^2 = \text{SS} (A * B)$  is the sum of the squares which represents the interaction between A and B; this process is denoted by  $*; \sum_{i=1}^{p} \sum_{j=1}^{q} \sum_{k=1}^{r} (y_{ijk} - \overline{y_{ij}})^2 = \text{SSE}$  is the sum of the squares to represent the residual, i.e., it is the probability of

TABLE I Test Hypothesis

| EP  | Hypothesis                                               | F-test                    |

|-----|----------------------------------------------------------|---------------------------|

| А   | $H_0: \alpha_1 = \alpha_2 = \dots = \alpha_p = 0$        | $F = \frac{MSA}{MSE}$     |

| В   | $H_0: \beta_1 = \beta_2 = \ldots = \beta_q = 0$          | $F = \frac{MSB}{MSE}$     |

| A*B | $H_0: \gamma_{ij} = 0, i = 1, \dots, p, j = 1, \dots, q$ | $F = \frac{MS(A*B)}{MSE}$ |

|     | where $\alpha$ : confidence level                        |                           |

accepting the EP if it is highly correlated with GYR after the F-test.

A test hypothesis must be made to conduct the F-test based on the previous expressions; in this case, the hypothesis is that there exists at least a nonzero EP level; otherwise, there exists a joint effect by the interaction between the two EPs. The summary of the test hypothesis is given in Table I.

The test hypothesis is based on the ANOVA of the two-way classification. The statistical parameters are shown in Table II.

In Table II, if each *F*-value does not satisfy the significance probability (i.e., SProb), then the respective EP is rejected; moreover if the interaction between A and B (i.e., (A \* B)) does not satisfy the significance probability (i.e.,  $P(F < f_3)$ ), then (A \* B) has no statistical correlation with GYR. Using this method, the EPs, and their levels which could be highly correlated to the GYR, can be found together with the interactions among EPs. This information will be used to provide a better understanding of the SoC fabrication process, and to establish a criterion for stratified sampling-based testing. Note that an ultimate objective in yield modeling and analysis is to obtain the true value of the yield (given a confidence interval and a confidence level). However, in practice, the true yield value can not be readily obtained.

The proposed estimation-based method is an alternative. A point estimator has a variance which is the confidence interval with respect to various confidence levels, and then theoretically the true value is supposed to be within this confidence interval. Therefore, theoretically, it is obvious that the proposed stratified-sampling-based ST is superior to RT

$$V(\hat{y_{\text{et}}}) \le V(\hat{y_{\text{rt}}}). \tag{7}$$

This indicates that the proposed ST can offer a tighter GYR interval than RT and, thus, ST is more efficient than RT.

#### C. Stratification for Sampling-Based Testing

In the proposed method, a *stratified sampling* is employed for testing SoCs. A sampling-based testing approach for SoCs is different from a conventional method because the GYR is the ratio estimator under the assumption that the variance of GYRs of the sampled SoCs (denoted by  $S_h^2$ ) is homogeneous in each stratum. The variance is asymptotically given by

$$V(Y_{\rm conv}) = \frac{N-n}{Nn} \bar{S}_h^2 \left[ 1 + \frac{1}{\bar{n}_h} \left( \frac{L-1}{L} \right) \right] \tag{8}$$

where  $\bar{S}_h^2$  is the mean of  $S_h^2$ ; N is the total number of sampled SoCs;  $\bar{n}_h = n/L, n$  is the total number of sampled SoCs, and L is the total number of strata. If  $\bar{n}_h$  is large enough, then the variance of  $Y_{\text{conv}}$  is

$$V(Y_{\rm conv}) = \frac{N-n}{Nn}\bar{S}_h^2.$$

(9)

| - | EP     | SS      | d.f.       | MS                         | F value        | SProb.        |  |

|---|--------|---------|------------|----------------------------|----------------|---------------|--|

| - | А      | SSA p-1 |            | MSA=SSA/(p-1)              | f1=MSA/MSE     | $P(F \ge f1)$ |  |

| - | В      | SSB     | q-1        | MSB=SSB/(q-1)              | f2=MSB/MSE     | $P(F \ge f2)$ |  |

|   | (A*B)  | SS(A*B) | (p-1)(q-1) | MS(A*B)=SS(A*B)/(p-1)(q-1) | f3=MS(A*B)/MSE | $P(F \ge f3)$ |  |

| - | Resid. | SSE     | pq(r-1)    | MSE=SSE/pq(r-1)            |                |               |  |

|   | Total  | SST     | par-1      |                            |                |               |  |

TABLE II ANOVA RESULTS FOR THE TWO-WAY CLASSIFICATION

where SS is the sum of the squares, MS is the mean square, d.f. is the degree of freedom, the F-value is the F-test for the hypothesis

TABLE

III

Accuracy Comparison for Proposed Method Versus Random Sampling-Based Testing

|             | GYR estimator  | Confidence interval | GYR estimator      | Confidence interval |

|-------------|----------------|---------------------|--------------------|---------------------|

| Sample size | $(y_r)$ of     | $(S_{y_r})$ of      | $(y_e)$ of         | $(S_{y_e})$ of      |

|             | random testing | random testing      | stratified testing | stratified testing  |

| 10          | 83.8           | 8.24                | 87.3               | 0.66                |

| 20          | 85.2           | 8.80                | 86.1               | 0.46                |

| 30          | 85.2           | 9.25                | 86.5               | 0.26                |

| 40          | 85.3           | 8.87                | 86.6               | 0.21                |

| 50          | 85.6           | 8.58                | 86.8               | 0.16                |

| 60          | 86.4           | 8.40                | 86.6               | 0.14                |

| 70          | 86.5           | 8.47                | 86.7               | 0.12                |

| 80          | 87.1           | 8.28                | 86.8               | 0.10                |

| 90          | 86.9           | 8.24                | 86.8               | 0.09                |

| 100         | 86.7           | -                   | 86.7               | -                   |

Next, the sampled SoCs from the treatments in the environmental characterization are rearranged to build a new framework with the EPs which were accepted by the F-test.

#### D. Estimate of GYR

or

The true value of Y (or GYR) can be expressed by

$$Y = \frac{\sum_{h=1}^{L} N_{h} Y_{h}}{N} = \frac{\sum_{h=1}^{L} \sum_{i=1}^{N_{h}} y_{hi}}{N} = \frac{A}{N}$$

(10)

where A is the number of SoCs which have been tested and diagnosed as fault free, thus, contributing to the GYR; L is the number of strata.

Then,  $\hat{y}_{st}$ , (i.e., the estimator of Y) can be expressed by

$$\hat{y}_{\rm st} = \frac{\sum_{h}^{L} N_h \hat{y}_h}{N} \tag{11}$$

$$\hat{y}_h = \frac{\sum_{i=1}^{n_h} Y_i}{y_{hi}} = \frac{a_h}{n_h}$$

(12)

where  $a_h$  is the number of SoCs in the GYR for the *h*th stratum. Intuitively,  $\hat{y}_{st}$  is an unbiased estimator of Y such that

$$E(\hat{Y}_{\rm st}) = \frac{\sum_{h}^{L} N_h E(\hat{Y}_h)}{N} = \frac{\sum_{h}^{L} N_h y_h}{N} = Y.$$

(13)

Its variance is then given by [13], [14] as follows:

$$V(\hat{Y}_{\rm st}) = \frac{1}{N^2} \sum_{h}^{L} N_h^2 \frac{N_h - n_h}{N_h - 1} \frac{S_h^2}{n_h}.$$

(14)

Therefore, the estimator of GYR for the proposed method and its variance can be established. Note that hereafter Y will be used as an abbreviation of the GYR.

For stratified sampling-based test, the unbiased estimator of Y is given by  $\hat{y}_{st}$ , and its variance is given by

$$V(\hat{y}_{\rm st}) = \frac{1}{N^2} \sum N_h^2 \frac{N_h - n_h}{N_h - 1} \frac{S_h^2}{n_h} \approx \frac{1}{N^2} \sum N_h^2 \frac{S_h^2}{n_h}.$$

(15)

For comparison with random sampling-based test, the unbiased estimator of Y is

$$\hat{y}_r = \frac{\sum_{i=1}^n \hat{y}_i}{n} \tag{16}$$

and its variance is

$$V(\hat{y}_r) = \frac{S^2}{n} \left(\frac{N-n}{N-1}\right) \approx \frac{S^2}{n}.$$

(17)

Using these estimators, the accuracy (denoted by  $\hat{y}_{st}$  and  $\hat{y}_r$ , respectively) versus the actual value Y can be assessed.

#### **IV. SIMULATION RESULTS**

In the initial analysis it was assumed that the sampled SoCs are manufactured in a fabrication environment as described previously and the value corresponding to the observed Y of an SoC is randomly generated for the EPs. The total number of SoCs to be tested is 100. In the simulation, the actual value of Y (i.e., GYR) is assumed to be 86.7. After having identified the highly correlated EPs and their levels, then the observed Ys of the sampled SoCs can be rearranged into strata.

Y for the proposed method and random sampling-based testing can be calculated using the sample SoC variance for various sizes as shown in Table III.

The numerical simulation model and the steps for the proposed test method can be described as follows.

1) Random generation of GYR samples: Let Y be the GYR of each SoC satisfying the condition  $Y_1, Y_2, \ldots, Y_{100}$  and

$70 \leq Y_i < 100$ . 100 randomly generated values are saved.

- 2) Stratification of the GYR samples: a three-level stratification technique is used, i.e., EP level 1 ( $70 \le Y_i < 80$ ), level 2 ( $80 \le Y_i < 90$ ) and level 3 ( $90 \le Y_i < 100$ ).

- 3) GYR estimator  $(y_r)$  and confidence interval  $(S_{y_r})$  of RT: for each sample size *n*, the GYR estimator of  $y_r$  for RT can be obtained as

$$\hat{y}_r = \frac{\sum_{i=1}^n Y_i}{n}.$$

(18)

Its confidence interval can be calculated as

$$V(\hat{y}_r) = \frac{S^2}{n} \tag{19}$$

where

$$S^{2} = \frac{\sum_{i=1}^{n} (Y_{i} - \bar{Y})^{2}}{(n-1)}.$$

(20)

4) The GYR estimator (y<sub>e</sub>) and the confidence interval (Sy<sub>r</sub>) of the proposed method are then found as: for each sample size n, the GYR estimator of the proposed method (y<sub>e</sub>) can be calculated as

$$\hat{y}_e = \frac{\sum_{i=1}^h N_i \cdot \hat{y}_i}{N} \tag{21}$$

where for each sample size selected

$$\hat{y}_h = \frac{\sum_{i=1}^{n_h} Y_i}{n_h}.$$

(22)

And h is the number of strata and  $n_h$  is the sample size of each stratum. Then, the confidence interval for each selected sample size, is given by

$$V(\hat{y}_e) = \frac{1}{N^2} \sum_{i=1}^h N_h^2 \frac{S_h^2}{n_h}$$

(23)

where

$$S_h^2 = \frac{\sum_{i=1}^{n_h} (Y_i - \bar{Y})^2}{(n_h - 1)}.$$

(24)

The GYR estimators and confidence intervals of RT (the proposed method) for different sample sizes (n = 10, 20, ..., 100) are shown in the first and second (third and fourth) columns of Table III, respectively.

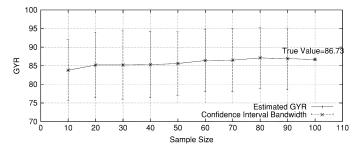

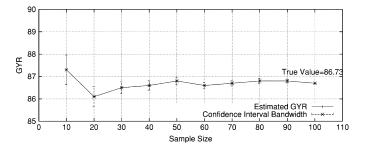

Comparison is made with respect to the confidence interval of the two testing methods (the proposed and a RT) as shown in Figs. 4 and 5 with respect to the true value of Y (i.e., GYR) on the vertical axis. Figs. 4 and 5 show that there is a significant increase in accuracy compared with random sampling-based testing; and also it is evident that there is less disagreement between the true value of Y and the value as estimated by the proposed method. Such disagreement is higher when the value of Y found by random sampling testing is utilized. This indicates

Fig. 4. Confidence interval of RT.

Fig. 5. Confidence interval of proposed testing.

that the proposed method improves both the accuracy of Y and its confidence level.

#### V. DISCUSSION AND CONCLUSION

We have presented an environmental-based characterization method for testing and assessing the GYR of SoC with high confidence during fabrication. The EPs have been identified as criteria to establish the GYR with high confidence. These criterion parameters highly correlated to the GYR can be used as a guidance to the stratification process in selection and sampling SoCs for testing on a wafer. The proposed environmentalbased ST technique is based on the two statistical techniques such as a statistical testing hypothesis (referred to as the environmental design) and the analysis method ANOVA, in order to identify the manufacturing parameters that affect the GYR of the SoCs, and to manage the stratified sampling-based test method. The experimental simulation results have demonstrated that there is a significant improvement in confidence interval by the proposed ST compared with the conventional random sampling-based testing; a remarkable difference in GYR estimated by ST compared with the one by the random sampling test has also been observed. This shows ST is an efficient and effective way to achieve an accurate yield estimation. Therefore, the proposed environmental-based characterization method will ultimately provide a sound theoretical yet practical foundation for testing and assessing the GYR of SoC with high confidence during fabrication.

#### REFERENCES

R. A. Bergamaschi, S. Bhattacharya, R. Wagner, C. Fellenz, M. Muhlada, F. White, J.-M. Daveau, and W. R. Lee, "Automating the design of SoCs using cores," *IEEE Des. Test Comput.*, vol. 18, no. 5, pp. 32–45, Sep.–Oct. 2001.

- [2] T. Bautista and A. Nunez, "Quantitative study of the impact of design and synthesis options on processor core performance," in *Proc. 19th IEEE VLSI Test Symp.*, Apr.–May 2001, pp. 169–175.

- [3] S.-Y. Chiang, "Foundries and the dawn of an open IP era," *IEEE Computer*, vol. 34, no. 4, pp. 43–46, Apr. 2001.

- [4] S. Ravi, G. Lakshminarayana, and N. K. Jha, "Testing of core-based systems-on-a-chip," *IEEE Trans. Computer-Aided Design Integr. Circuits Syst.*, vol. 20, no. 3, pp. 426–439, Mar. 2001.

- [5] N.-J. Park, B. Jin, K. M. George, N. Park, and M. Choi, "Regressive testing for system-on-chip with unknown-good-yield," in *Proc. IEEE DFT*, 2003.

- [6] F. J. Meyer and N. Park, "Predicting the yield efficacy of a defect-tolerant embedded core," in *Proc. IEEE Int. Symp. Defect Fault Tolerance in VLSI Systems*, Oct. 2000, pp. 30–38.

- [7] S. Dey, D. Panigrahi, L. Chen, C. N. Taylor, K. Sekar, and P. Sanchez, "Using a soft core in a SoC design: Experiences with picoJava," *IEEE Des. Test Comput.*, vol. 17, no. 3, pp. 60–71, Jul.–Sep. 2000.

- [8] I. Ghosh, S. Dey, and N. K. Jha, "A fast and low-cost testing technique for core-based system-chips," *IEEE Trans. Computer-Aided Design Integr. Circuits Syst.*, vol. 19, no. 8, pp. 863–877, Aug. 2000.

- [9] R. K. Gupta and Y. Zorian, "Introducing core-based system design," IEEE Des. Test Comput., vol. 14, no. 4, pp. 15–25, Oct.–Dec. 1997.

- [10] A. M. Rincon, C. Cherochetti, J. A. Monzel, D. R. Stauffer, and M. T. Trick, "Core design and system-on-a-chip integration," *IEEE Des. Test Comput.*, vol. 14, no. 4, Oct.–Dec. 1997.

- [11] M. Oberle, R. Reutemann, R. Hertle, and Q. Huang, "A 10-mW two-channel fully integrated system-on-chip for eddy-current position sensing in biomedical devices," *IEEE J. Solid-State Circuits*, vol. 37, no. 7, pp. 916–925, Sep. 2001.

- [12] J. K. Hagge and R. J. Wagner, "High-yield assembly of multichip modules through known-good IC's and effective test strategies," *Proc. IEEE*, vol. 80, no. 12, pp. 1965–1994, Dec. 1992.

- [13] A. Flint, "Testing multichip modules," *IEEE Spectr.*, vol. 31, no. 3, pp. 59–62, Mar. 1994.

- [14] C. Bolchini *et al.*, "A wafer level testability approach based on an improved scan insertion technique," *IEEE Trans. Comp., Packag., Manuf. Technol.*, vol. 18, no. 3, pp. 438–447, Aug. 1995.

- [15] Y. Zorian, "A structured testability approach for multichip modules based on BIST and boundary-scan," *IEEE Trans. Comp., Packag., Manuf. Technol.*, vol. 17, no. 3, pp. 283–290, Aug. 1994.

- [16] N. Park and F. Lombardi, "Stratified testing of multichip module systems under uneven known-good-yield," in *Proc. IEEE Int. Symp. Defect and Fault Tolerance in VLSI System*, Nov. 1999, p. 192.

- [17] J. K. Hagge and R. J. Wagner, "High-yield assembly of multichip modules through known-good IC's and effective test strategies," *Proc. IEEE*, vol. 80, no. 12, pp. 1965–1994, Dec. 1992.

- [18] C. M. Habiger and R. M. Lea, "Cost and delivery benefits of fault-tolerant multichip modules for massively parallel computing," in *Proc. IEEE Int. Workshop DFT in VLSI Systems*, Venice, Italy, Oct. 1993.

- [19] M. Lubaszewski, M. Marzouki, and M. H. Touati, "A pragmatic test and diagnosis methodology for partially testable MCMs," in *Proc. IEEE MCMC*, Mar. 1994, pp. 108–113.

- [20] D. P. Siewiorek and R. S. Swqrz, *Reliable Computer System, Design, and Evaluation*, 2nd ed. Bedford, MA: Digital, 1992.

- [21] W.-B. Jone, "Defect level estimation of circuit testing using sequential statistical analysis," *IEEE Trans. Computer-Aided Design Integr. Circuits Syst.*, vol. 12, no. 2, pp. 336–348, Feb. 1993.

- [22] R. L. Wadsack, "Fault coverage in digital integrated circuits," *Bell Syst. Tech. J.*, vol. 57, pp. 1475–1488, May–Jun. 1978.

- [23] T. W. Williams and N. C. Brown, "Defect level as a function of fault coverage," *IEEE Trans. Comput.*, vol. C-30, pp. 987–988, Dec. 1981.

- [24] T. W. Williams, "Test length in a self-testing environment," *IEEE Des. Test Comput.*, vol. 2, pp. 59–63, Apr. 1985.

- [25] E. J. McCluskey and F. Buelow, "IC quality and test transparency," *IEEE Trans. Ind. Electron.*, no. 5, pp. 197–202, May 1989.

- [26] R. G. D. Steel, J. H. Torrie, and D. A. David, *Principles and Procedures of Statistics*. New York: McGraw-Hill, 1996.

- [27] M. S. Quasem, J. Zhigang, and S. K. Gupta, "Benefits of a SoC-specific test methodology," *IEEE Des. Test Comput.*, vol. 20, no. 3, pp. 68–77, May–Jun. 2003.

- [28] Y. Zorian, "Leveraging infrastructure IP for SoC yield," in *Proc. IEEE Asian Test Symp.*, Nov. 16–19, 2003, pp. 3–4.

- [29] Y. Zorian and S. Shoukourian, "Embedded memory test and repair: Infrastructure IP for SoC yield," *IEEE Des. Test Comput.*, vol. 20, no. 3, pp. 58–66, May–Jun. 2003.

- [30] P. Coussy, A. Baganne, and E. Martin, "A design methodology for integrating IP into SoC systems," in *Proc. IEEE Custom Integrated Circuit Conf.*, May 12–15, 2002, pp. 307–310.

- [31] J. Zhao, W. Chen, and S. Wei, "Parameterized IP core design," in Proc. Int. Conf. ASIC, Oct. 23–25, 2001, pp. 744–747.

**N. J. Park** received the B.S. degree in economics from Yonsei University, Seoul, Korea, the M.S. degree in statistics from Seoul National University, Seoul, Korea, and the M.B.A. degree (marketing major) from Yonsei University, Seoul, Korea. He is currently working toward the Ph.D. degree in the Computer Science Department, Oklahoma State University, Stillwater.

He worked for A.C. Nielsen (world-wide marketing research company), Korea, for six years as a Manager in the Statistics Division and currently is

working for KCIS Co. Ltd., Scoul, Korea, as a Vice President. His research interests include statistical modeling, analysis and forecasting, risk analysis, management and forecasting, parallel/distributed computing systems, defect/fault tolerant computing and testing, and marketing research.

**K. M. George** received the Ph.D. degree in mathematics from the State University of New York, Stony Brook, in 1976.

He is currently a Professor in the Computer Science Department, Oklahoma State University, Stillwater, OK. His current areas of research include parallel and distributed computing, computer architecture, and mathematical modeling and simulation.

Nohpill Park received the B.S. and M.S. degree in computer science from Seoul National University, Seoul, Korea, in 1987 and 1989, respectively, and the Ph.D. degree from Texas A&M University, College Station, in 1997. Since 1999, he has been an Associate Professor in

the Computer Science Department, Oklahoma State University, Stillwater. His research interests include computer architecture, defect and fault tolerant systems, testing and quality assurance of digital systems, parallel and distributed computer systems, multichip

module systems, programmable digital systems, and system on chip.

**Minsu Choi** (S'00–M'02) received the B.S., M.S., and Ph.D. degrees in computer science from Oklahoma State University, Stillwater, in 1995, 1998, and 2002, respectively.

He is currently an Assistant Professor in the Electrical and Computer Engineering Department, University of Missouri, Rolla. His research mainly focuses on computer architecture and VLSI, embedded systems, fault tolerance, testing, quality assurance, reliability modeling and analysis, configurable computing, parallel and distributed systems and depend-

able instrumentation and measurement.

Dr. Choi is a Member of the Golden Key National Honor Society and Sigma Xi.

Yong-Bin Kim was born in Seoul, South Korea, in 1960. He received the B.S. degree in electrical engineering from Sogang University, Seoul, South Korea, in 1982, the M.S. degree in computer engineering from New Jersey Institute of Technology, Newark, in 1989, and the Ph.D. degree in computer science from Colorado State University, Fort Collins, in 1996.

From 1982 to 1987, he was with the Electronics and Telecommunications Research Institute, South Korea, as a Member of Technical Staff. From 1990

to 1993, he was a Senior Design Engineer with Intel Corporation, and involved in micro-controller chip design and Intel P6 microprocessor chip design. From 1993 to 1996, he was with Hewlett Packard., Fort Collins, CO, as a Member of Technical Staff, and involved in HP PA-8000 RISC microprocessor chip design. From 1996 to 1998, he was with Sun Microsystems, Palo Alto, CA as an individual contributor, and involved in 1.5 GHz Ultra Sparc5 CPU chip design. From 1998 to 2000, he was an Assistant Professor in the Department of Electrical Engineering, University of Utah, Provo. He is currently a Zraket Endowed Professor in the Department of Electrical and Computer Engineering, Northeastern University, Boston, MA. His research focuses on high-speed low-power VLSI circuit design and methodology.

Fabrizio Lombardi received the B.Sc. degree (with honors) in electronic engineering from the University of Essex, Essex, U.K., in 1977, the Master in Microwaves and Modern Optics, Diploma in Microwave Engineering degrees from University College London, London, U.K., both in 1978, and the Ph.D. degree from the University of London, U.K., in 1982.

In 1977, he joined the Microwave Research Unit, University College London. He is currently the Holder of the International Test Conference (ITC)

Endowed Professorship at Northeastern University, Boston, MA. From 1998 to 2004, he was Chair of the Department of Electrical and Computer Engineering, Northeastern University. Prior to joining Northeastern University he was a faculty member with Texas Tech University, University of Colorado at Boulder, and Texas A&M University. His research interests are testing and design of digital systems, quantum computing, Automatic Test Equipment systems, configurable/network computing, defect tolerance, and CAD VLSI. He has authored and coauthored numerous publications in these areas and has edited six books.

Dr. Lombardi was an Associate Editor of the IEEE TRANSACTIONS ON COMPUTERS (1996–2000). He was a Distinguished Visitor of the IEEE Computer Society (IEEE CS) (1990–1993). Since 2000, he has been the Associate Editor-In-Chief of the IEEE TRANSACTIONS ON COMPUTERS. He is also currently an Associate Editor of the *IEEE Design and Test Magazine* and a Distinguished Visitor of the IEEE CS. He is also the Chair of the Committee on Nanotechnology Devices and Systems of the Test Technology Technical Council of the IEEE.