## Missouri University of Science and Technology Scholars' Mine

**Electrical and Computer Engineering Faculty** Research & Creative Works

**Electrical and Computer Engineering**

01 Feb 2002

# High-Performance Inter-PCB Connectors: Analysis of EMI **Characteristics**

Xiaoning Ye

James L. Drewniak Missouri University of Science and Technology, drewniak@mst.edu

Jim Nadolny

David M. Hockanson

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

## **Recommended Citation**

X. Ye et al., "High-Performance Inter-PCB Connectors: Analysis of EMI Characteristics," IEEE Transactions on Electromagnetic Compatibility, vol. 44, no. 1, pp. 165-174, Institute of Electrical and Electronics Engineers (IEEE), Feb 2002.

The definitive version is available at https://doi.org/10.1109/15.990723

This Article - Journal is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# High-Performance Inter-PCB Connectors: Analysis of EMI Characteristics

Xiaoning Ye, *Member, IEEE*, James L. Drewniak, *Senior Member, IEEE*, Jim Nadolny, and David M. Hockanson, *Member, IEEE*

Abstract—Electromagnetic interference (EMI) coupling associated with inter-board connection is investigated herein. Two experimental techniques, based on  $|S_{21}|$  measurements, including both common-mode current and near-field measurements, are reported. Both methods, as well as finite difference time domain (FDTD) modeling, were used as experimental and numerical tools for inter-printed-circuit-board (inter-PCB) connector evaluation. The EMI performance of a lab-constructed stacked-card connector, and a commercially available module-on-backplane connector were studied. EMI characteristics of the connectors are demonstrated by investigating a few aspects of the design: type of shield/ground blade for signal return, number and length of ground pins, signal pin designation, etc. Good agreement is achieved between the measurements and the FDTD modeled results.

$\label{lower_lower} Index\ Terms — Common-mode\ current,\ finite-difference\ time\ domain\ (FDTD),\ inter-printed-circuit-board\ (inter-PCB)\ connector,\ near\ field,\ S\ parameter.$

#### I. INTRODUCTION

ULTIBOARD configurations are common applications in high-speed digital designs, where connectors are used to route signals between different printed circuit boards (PCBs). The signal-return impedance of the connector (in most cases the inductance associated with the signal-return geometry) is typically small. However, it is not always negligible. When the current flows through the signal return geometry, a potential difference can develop between different PCB planes due to this nonzero signal-return impedance. The planes are of appreciable electrical extent and function as radiators at several hundred megahertz or higher, and can result in electromagnetic interference (EMI) problems [1]–[4].

Electronic devices are operating at increasingly faster speeds and consuming more power, which significantly increases EMI concerns at high frequencies. Connectors have been identified as a major cause of radiated emissions for systems using gigabit technology [5]. Proper design of the inter-board connector

Manuscript received February 23, 2001; revised October 31, 2001.

- X. Ye was with the Department of Electrical and Computer Engineering, Electromagnetic Compatibility Laboratory, University of Missouri-Rolla, Rolla, MO 65409 USA. He is now with Intel Corporation, Hillsboro, OR 97124 USA (e-mail: xiaoning@ieee.org).

- J. L. Drewniak is with the Department of Electrical and Computer Engineering, Electromagnetic Compatibility Laboratory, University of Missouri-Rolla, Rolla, MO 65409 USA (e-mail: drewniak@ece.umr.edu).

- J. Nadolny is with FCI Electronics, Etters, PA 17319-9769 USA (e-mail: jnadolny@fciconnect.com).

- D. M. Hockanson is with Sun Microsystems, Inc., Palo Alto, CA 94303-4900 USA (e-mail: david.hockanson@sun.com).

Publisher Item Identifier S 0018-9375(02)01440-0.

including signal designations, and the signal-return geometry is necessary for meeting EMI requirements in high-speed digital designs. A reliable experimental method is helpful in evaluating the EMI performance of connectors and developing design guidelines. Furthermore, numerical modeling of the problem can be used to support measurements, and aid in identifying and quantifying the radiation mechanisms. With the help of careful and experimentally verified numerical modeling, the measurement burden can be significantly alleviated. Numerical tools can also be used to conduct EMI studies and design discovery without the construction of numerous test boards. Another benefit of numerical modeling is that unmeasurable quantities may be obtained from the modeling.

Previous experimental work has been reported on the EMI performance of inter-PCB connectors. In [5], the radiated EMI was directly measured in a transverse electromagnetic (TEM) cell or anechoic chamber to show the effectiveness of different ground pin shielding patterns. The measurements were indicative of EMI, but required special measurement facilities. References [6]–[9] focused on transfer impedance measurements. In [10], six classical measurement methods for characterization of the transfer impedance measurement and shielding performance of board-to-backplane and backplane-to-cable connectors were investigated: 1) a triaxial cell; 2) a line-injection set-up; 3) a GTEM-cell; 4) TEM-cell; 5) a mode-stirred chamber (MSC); and 6) an anechoic chamber. References for each method can be found in [10]. While transfer impedance is particularly useful for shielded connectors that are mounted on an enclosure wall, it is more ambiguous as a measure of EMI comparison for open region geometries such as the interconnection of PCBs. Furthermore, managing measurement parasitics becomes challenging above approximately 500 MHz.

Two experimental techniques, based on measuring  $|S_{21}|$ , viz., common-mode current measurements and near-field probe measurements, were utilized in this study. The experimental techniques are described in Section II, and the suitability of both measurements as an indicator of EMI performance was investigated by comparing the measurements and the FDTD modeled results of some simple geometries. In Sections III and IV, the measurement techniques are applied to investigate the EMI performance of stripline-type inter-board connections for multi-PCB configurations. Both stacked-card configurations and module-on-backplane configurations are studied. The finite difference time domain (FDTD) method is used as the numerical tool in this study because of ease in analyzing multiple frequencies with a single time-domain simulation. Furthermore, it is well suited for rectilinear geometries. The

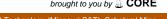

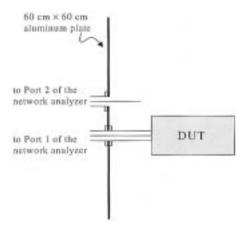

Fig. 1. Experimental set-up for the common-mode current measurement.

FDTD modeled results agree well with the common-mode current measurements for frequencies up to 1 GHz. The near-field measurements compared well with FDTD modeling for frequencies up to 3 GHz.

## II. EXPERIMENTAL METHODS

The experimental set-up for the common-mode current measurement is shown in Fig. 1. A two-port,  $|S_{21}|$  measurement was made using an HP8753D Network Analyzer. Low-loss cables were connected between the network analyzer and a  $60 \times 60$  cm<sup>2</sup> aluminum plate. The plate was used to isolate the device under test (DUT) and the measuring instruments to reduce the parasitic coupling between the connecting cables and the measuring instruments, thereby enhancing the repeatability and dynamic range of the measurement. Two SMA bulkhead-through connectors were mounted on the aluminum plate to provide the signal paths through the plate. A semi-rigid coaxial cable was attached to the DUT and connected to the bulkhead-through connector that is connected to Port 1. A Fischer 2000 clamp-on current probe was placed around the semi-rigid coaxial cable and connected to the bulkhead-through connector that was connected to Port 2. The signal was fed from Port 1 of the network analyzer, directed through the low-loss cable, the bulkhead-through connector mounted on the aluminum plate, the semi-rigid coaxial cable, and finally injected into the DUT. The induced common-mode current on the outer shield of the attached semi-rigid cable was picked up by the clamp-on current probe, and fed into Port 2 of the network analyzer. The measured  $|S_{21}|$  is related to the common-mode current induced on the attached coaxial cable, and is indicative of the EMI. A special calibration procedure using the standard short, open, load termination (SOLT) is performed to remove the frequency response of the probe from the measurement [2], where the  $|S_{21}|$  and the magnitude of the induced common-mode current on the attached cable are related by

$$\left|S_{21}^{\rm measured}\right| = \left|\frac{I_{CM} \cdot 50 \; \Omega}{V_s}\right|. \label{eq:S21_equation}$$

Since the common-mode current can be readily calculated in numerical modeling, this equation makes possible an absolute comparison between the measured data and the modeled results.

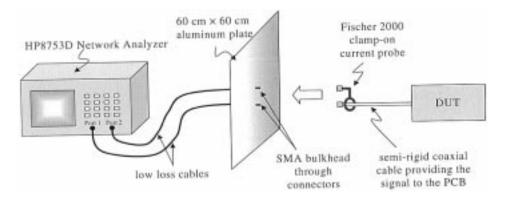

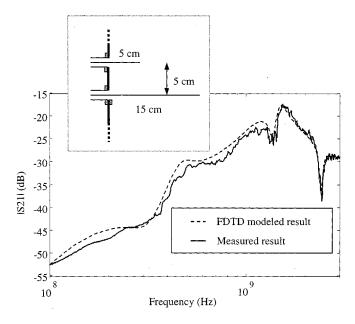

Fig. 2. Schematic of the coupled monopole antennas measurement.

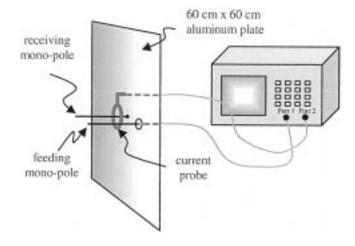

A simple test set-up using two monopole antennas, as shown in Fig. 2, was built to investigate the useful frequency range of this common-mode current measurement. Two wires with a diameter of 0.408 mm (20 mils) were used as the monopole antennas in the measurement. The feeding monopole was soldered to the center conductor of an M/A-COM flange mount jack receptacle that was mounted on the  $60 \times 60 \text{ cm}^2$  aluminum plate. The receiving monopole was soldered to a copper tape patch, which was attached to the aluminum plate. Both monopoles were 15 cm long, and separated by 5 cm. The induced current on the receiving monopole was then measured using the  $S_{21}$  procedure described above. The measured result is shown in Fig. 3, together with the FDTD modeled result. Discrepancies become prominent for frequencies greater than 1.5 GHz. The discrepancies are due in part to the presence of a large current probe in the proximity of the DUT, which is difficult to include in the numerical modeling.

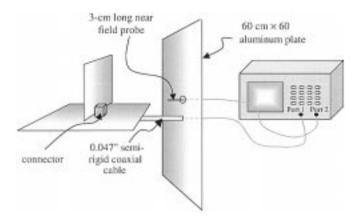

For high-speed digital circuits with subnanosecond rising and falling edges, the frequency range of concern extends beyond 1 GHz, and applications of the common-mode current measurement may be limited as stated above. For this reason, a near-field measurement method was developed to reduce the influence of measurement parasitics, and to extend the frequency range over which the numerical modeling results could be validated with measurements. The test set-up is shown in Fig. 4. The current probe used in the previous measurement approach is replaced by

Fig. 3. Modeled and measured results of the coupled monopoles shown in Fig. 2.

Fig. 4. Experimental set-up of the near-field measurement.

a short near-field monopole probe. The near field in the proximity of the DUT is picked up by the probe and fed into Port 2, and the  $|S_{21}|$  is measured. The probe is sufficiently small so that it will not load the circuit, however, the electric field picked up by the near-field probe also contains the frequency response of the probe. Nevertheless, this approach is a very repeatable method for relative studies and can be used to corroborate the numerical modeling. It can also be used for relative studies with production connectors. A simple structure was built to investigate the dynamic range of this near-field measurement technique. The driven antenna was a 15-cm long monopole, and the spacing between the monopole and the 5-cm long near-field probe was 5 cm. The measured and FDTD modeled  $|S_{21}|$  is shown in Fig. 5. The agreement is favorable for frequencies up to 3 GHz.

Both the common-mode current measurement and the near-field measurement are suitable for the EMI performance evaluation of prototype or production PCB designs. Generally, the common-mode current approach is more favorable for low-frequency measurements, since the parasitics of the current probe become prominent at high frequencies. By selecting appropriately specified current probes, the measurement technique can be applicable for frequencies in the kilohertz range. The near electric-field monopole sensor is more favorable for high-fre-

Fig. 5. Measured and FDTD modeled near-field of a 15-cm monopole picked up by a 5-cm probe.

quency measurements, since the signal picked up by the short probe may be too small at low frequencies due to the frequency response of the probe when driving a 50- $\Omega$  load (i.e., the network analyzer).

In the following two sections, both measurement techniques are applied to investigate the EMI performance of stripline-type inter-board connections for multi-PCB configurations. Both stacked-card configurations and module-on-backplane configurations are studied. A stacked-card configuration study is presented in Section III. The common-mode current measurement technique is used to validate the modeling results. Results using FDTD modeling to study the effects of the ground contacts in the connector are discussed in Section III as well. A module-on-backplane configuration is presented in Section IV. The near-field monopole-probe measurement technique is used to validate the modeled results. Results from FDTD modeling of the module-on-backplane configuration are then used to demonstrate the impact on radiation of signal designations through a connector.

# III. REFERENCE-PLANE CONTACTS IN STRIPLINE-TYPE CONNECTORS

Previous studies have shown the importance of the signal return geometries at the inter-board connection for EMI concerns [2], [3], [5], [11]. The EMI can be reduced significantly if the field containment at the connection is improved, and the appreciable impedance of the signal return geometry is minimized. This can be realized by reducing the spacing between the signal and signal return pins, using multiple signal return pins, or utilizing conducting planes as the signal return (stripline-type connection) [11]. In this section, a stripline-type connection is studied. The validity of the measurement technique and FDTD modeling in connector design and applications is demonstrated. Aspects that may be encountered in the design and application

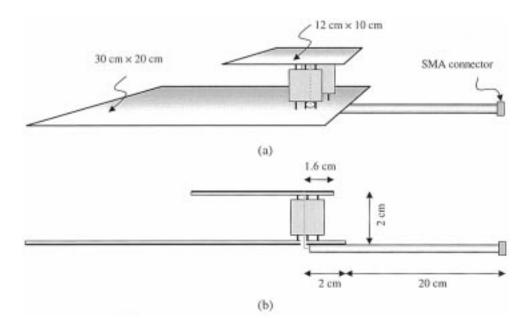

Fig. 6. Geometry of the stacked-card test fixture: (a) perspective view and (b) side view.

of this type of connector are investigated including the number and height profile of the reference plane contacts.

For a stripline-type connection, each signal pin row is sandwiched by two ground blades to achieve superior field containment at the connection, as illustrated in Fig. 6. Short conductors are attached to both ends of the ground blade to provide the connection of the blade to the PCB reference planes, and denoted as "ground contacts" herein. Adding the ground blades can increase the cost of the connector, but the improved signal return path and PCB reference plane connections can aid in meeting the requirements in circuit designs where EMI performance is critical, e.g., routing very high speed digital signals between PCBs. There can be an EMI improvement of 25-35 dB from a simple two-wire connection to a well designed stripline-type connection [11]. However, the advantage of this ground-blade approach may be compromised if the routing of the signal pin is not carefully considered. In production connectors, the signal and the signal-return pins are generally arranged in arrays. Different signal pins may provide different EMI performance due to their relative positions to the signal-return structures. Meanwhile, other design factors, such as the aspect ratio of the ground blades, the number of the ground contacts, may affect the overall EMI performance as well, and must be considered. These design and application issues are addressed in this section.

The stacked-card configuration shown in Fig. 6 was constructed and used as the test bed for this study. The size of the mother-board was  $30 \times 20 \, \mathrm{cm^2}$ , and that of the daughter-board was  $12 \times 10 \, \mathrm{cm^2}$ . The spacing between the two boards was 2 cm, and the offset of these two boards at the connection edge was 0.4 cm. A 0.085-in semi-rigid coaxial cable was attached to the ground plane of the mother-board at the center of the board edge, with the outer shield soldered to the ground plane along the entire contact length. The length of the cable section that extended beyond the PCB ground plane was 20 cm. A 24 AWG wire was used as the signal pin. One end of the signal pin penetrated the ground plane of the mother-board

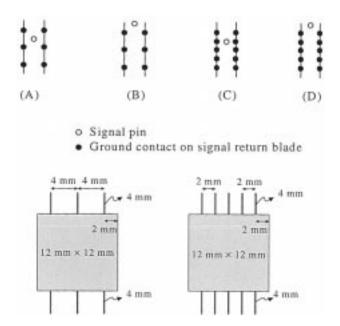

without electrically contacting it, and was soldered to the extended center conductor of the semi-rigid cable. The other end of the signal pin was soldered to the ground plane of the daughter-board. The connection point for the signal pin was 5 cm away from both 12-cm edges of the daughter-board, 10 cm away from both 30-cm edges of the mother-board, and 2 cm away from the 20-cm edge of the mother-board. No signal traces were present on either board so that the study focused on the inter-board connection itself. Four signal and signal return geometries with different signal pin designations, or different numbers of ground contacts were studied, and denoted as Cases A, B, C, and D, as illustrated in Fig. 7. The ground blade of Cases A and B has three ground contacts, and that of Cases C and D has five ground contacts. The signal is routed through the interior for Cases A and C, and through the edge for Cases B and D. A 2-mm pitch is standard in many connectors, and was used for the closely spaced ground contacts for Cases C and D.

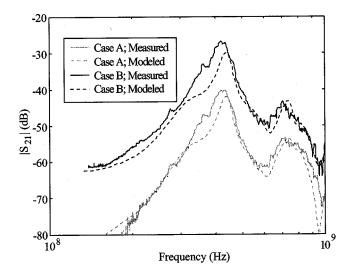

The common-mode current on the attached cable was measured and calculated from the FDTD modeling, and is an indicator of radiated emissions. The measured common-mode currents on the attached semi-rigid cable (using the measurement technique shown in Fig. 1) for inter-board connections Cases A and B are shown in Fig. 8, together with the FDTD modeled results. In the FDTD modeling, a uniform cell size of  $2 \times$  $2 \times 2 \text{ mm}^3$  was used. All of the PCB planes shown in Fig. 6 were modeled as perfect electric conductors (PECs). A thin wire algorithm was used to model the wire structures in the fixture [13]. Eight perfectly matched layers (PMLs) were placed at each boundary plane of the computational domain [14], and seven white-space layers were placed between the PML and the test fixture. The source applied in the modeling was a sinusoidally modulated Gaussian voltage source with a 50  $\Omega$  resistance in series. The dielectrics on the PCBs were omitted, since their thickness was negligible compared to the spacing between the two planes, and no traces were present on the planes. The  $60 \times 60 \,\mathrm{cm}^2$  aluminum plate shown in Fig. 1 was also included

Fig. 7. Schematic representation of four connector pin-outs and their corresponding ground-blade geometries: (A) interior signal routing, three ground contacts; (B) edge signal routing, three ground contacts; (C) interior signal routing, five ground contacts; and (D) edge signal routing, five ground contacts. The ground blade geometry for (A) and (B) is shown on the left, and that for (C) and (D) is shown on the right.

Fig. 8. Measured and FDTD modeled common-mode current on the attached semi-rigid cable for the stacked-card configuration with inter-board connections Cases A and B shown in Fig. 7.

in the modeling, and modeled as an infinite ground plane, i.e., the ground plane in the modeling was truncated at the outmost layer of the PML boundary, and the PEC boundary conditions were enforced on the plane that is extended through the white spaces and all the PML layers. The actual FDTD computational domain was then reduced since it was not necessary to generate a mesh for the  $60\times60\text{-cm}^2$  large plane.

The common-mode current on the cable for Case B is approximately 10–15 dB greater than that for Case A, indicating that the EMI performance of a signal routed through an edge row of the connector pins is considerably worse than a signal

Fig. 9. FDTD modeled common-mode current on the attached semi-rigid coaxial cable of the stacked-card configuration with inter-board connections shown in Fig. 7.

routed through an interior row. Case A has better field containment at the inter-board connection than Case B does, because the signal pin is better surrounded by the signal returns for Case A. In terms of the signal return impedance, Case A has a smaller signal return impedance, because most of the return current will take the parallel paths of the four adjacent ground contacts. For Case B, most of the return current will take the paths of only two adjacent ground contacts, with a relatively larger impedance in the signal return geometry. The inductance of the ground contacts dominates the signal return impedance since the inductance of the  $12 \times 12 \text{ mm}^2$  ground blade is negligible compared to the ground contacts each having a total length of 8 mm. Therefore, the signal return impedance of Case A is approximately half or less than that of Case B, which corroborates well with the approximately 10–15 dB difference of the induced common-mode current on the attached cable. A more accurate prediction of the EMI difference requires including the mutual inductance between different ground contacts and the signal pins in a rigorous equivalent circuit model, which is not considered herein. The agreement between the measured and modeled results are generally favorable over the studied frequency range, demonstrating that the FDTD method is suitable for modeling the EMI performance of inter-board connections. In the rest of this section, only the FDTD modeled results are presented for the connector design study.

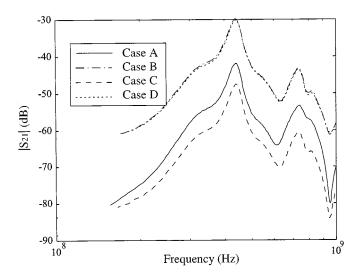

The FDTD-modeled common-mode current on the attached cable for Cases C and D is shown in Fig. 9. Modeled results for Cases A and B are also shown in the same figure for comparison. The common-mode current for Case C is approximately 15–20 dB less than that of Case D, which again indicates that the inner signal pin has better EMI performance than the outer pin does. The calculated common-mode current is almost the same for Cases B and D. In these two cases, the signals are routed through the outer row and most of the return current will then take the path provided by the two closest ground contacts. The additional ground contacts in Case D do not incur major changes of the signal return current distribution. Therefore, there is only a slight difference in the common-mode current for these two

Fig. 10. FDTD modeled common-mode current on the attached semi-rigid coaxial cable of the stacked-card configuration with different ground blades and different ground contact lengths.

cases. However, comparing Cases A and C, there is an approximately 4–6 dB reduction from three ground contacts to five ground contacts. For the cases of signal pin being routed through interior pin-rows, the additional ground contacts immediately next to the signal pin provide effective additional signal return paths, and improve the field containment at the connection, *viz.*, help to reduce the nonzero impedance of the signal return geometry. Therefore, adding additional ground contacts may help to improve the EMI performance of interior signal pin rows. However, this is a strong function of the 4-mm ground contact length, as will be discussed in the following paragraphs.

The fact that changing the number of the ground contacts affects the EMI performance also supports the concept of a nonzero impedance of the signal return geometry being dominated by the ground contacts for the connections shown in Fig. 7. Therefore, the EMI benefits of the stripline-type approach is compromised by the nonzero impedance of the discrete ground contacts, which are required in practice for the mounting of the connector on a PCB. Minimizing the length of the ground contacts is expected to be beneficial for EMI mitigation. FDTD modeling was then conducted to investigate the effect on EMI of the ground contact lengths. The ground blades shown in Fig. 7 were then replaced by  $12 \times 16 \text{ mm}^2$  ones, and the length of the ground contact was decreased from 4 mm to 2 mm, as shown in Fig. 10. Only the cases with interior signal routing (Cases A and C) were then studied.

The modeled common-mode current on the attached cable is shown in Fig. 10. The results for lower frequencies are omitted.

Fig. 11. Experimental set-up of the near-field measurement for a module-on-backplane configuration.

Fig. 10 shows that the length of the ground contact is a critical aspect of the EMI performance. When three ground contacts were used for each blade, the predicted improvement using a 2-mm ground contact length as opposed to 4 mm is approximately 15 dB. When five ground contacts were used, the predicted improvement is approximately 10 dB. The results shown in Fig. 10 also indicate that, when the length of the ground contact was 4 mm, the number of ground contacts significantly affects the common-mode current on the cable; though, when the length of the ground contact is 2 mm, there is negligible difference between the results with three and five ground contacts. This is because when the length of the ground contact is reduced to 2 mm, the nonzero impedance of the discrete ground contacts in parallel is no longer the only dominant factor of the impedance of the signal return. Consequently, reducing this part of the impedance has only a marginal effect of lowering the total impedance of the ground return, and, hence, lowering the common-mode current.

Generally, minimizing the ground contact length is beneficial for the EMI performance of the stripline-type connector. For multilayer PCB designs, keeping the reference plane immediately adjacent to the connector as the first entire plane helps to reduce the ground contact length. If the EMI effects of the ground contacts can be minimized, the additional ground contacts are then unnecessary, which not only reduces the via density of the board, but also reduces the manufacturing cost of the connector.

### IV. SIGNAL DESIGNATION IMPACT ON EMI PERFORMANCE IN STRIPLINE-TYPE CONNECTOR

In this section, the near-field measurement technique discussed in Section II is utilized together with FDTD modeling to investigate the EMI performance of a production module-on-backplane stripline-type connector for frequencies up to 3 GHz. The experimental setup of the near-field measurement is shown in Fig. 11. The dimensions of the mother-board and daughter-board were  $10\times10~{\rm cm^2}$ , and  $10\times6~{\rm cm^2}$ , respectively. A 0.047-in semi-rigid coaxial cable was attached to the ground plane of the mother-board at the center of the board edge, with the outer shield soldered to the ground plane along the entire contact length. The length of the portion of the

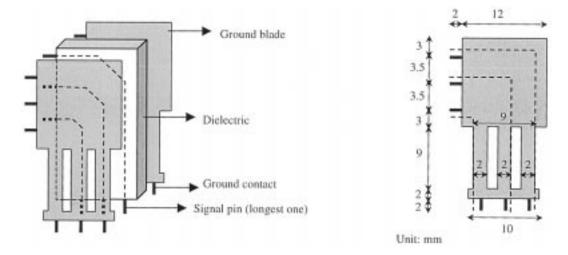

Fig. 12. Simplified schematic of one slice of the stripline-type connector and the dimensions of a ground blade (the spacing between the two ground blades of the connector is 2.5 mm).

feeding cable extended beyond the PCB edge to the aluminum plate was 3.5 cm. The signal pin of the connector penetrated through the ground plane of the mother-board without electrical contact, and was soldered to the extended center conductor of the semi-rigid cable. The daughter-board was mounted vertically in the middle of the mother-board, i.e., 5 mm apart from either side of the board edge. The ground planes of the mother-board and the daughter-board were connected through the signal return of the connector. No signal traces were present on either the mother-board or daughter-board. The near-field probe was 3 cm long.

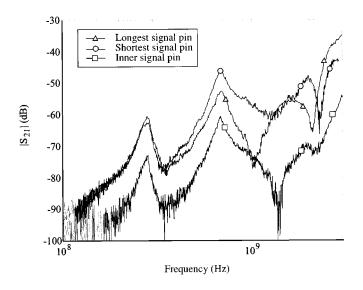

The production connector shown in Fig. 11 was a multipin connector with each row of pins sandwiched by two adjacent conductor blades. The connector was a standard 2-mm pitch connector. Each ground blade had three short contacts which were used for the connection between the ground blade and PCB reference plane. During this study, only a column of signal pins embedded in a dielectric, and the adjacent two ground blades were used and the rest of the connector assembly was removed for simplicity. A simplified schematic of one slice of this stripline-type connector is shown in Fig. 12. Only three representative signal pins are shown in the figure, the longest, the shortest, and an inner pin. Three near-field measurements were conducted to investigate the effects on EMI when the signal was routed through these three different signal pins shown in Fig. 12. For each measurement, the signal was fed from the center conductor of the attached semi-rigid cable, and then directed through one of the three signal pins and terminated on the daughter-board. All the ground contacts were soldered to the ground planes of the mother-board or daughter-board. In each case of study, all the unused pins were removed.

The measured  $|S_{21}|$  for the three different connector signal routing paths is shown in Fig. 13. The results show that the signal pin designation has a significant impact on the EMI performance of the connector. When the signal is routed through the inner pin, the resulting electric near field is much smaller than the other two cases. For this signal routing case, the field containment in the connector is much better than when the signal

Fig. 13. Measured  $|S_{21}|$  for the test set-up shown in Fig. 11. The connector was a slice of the stripline-type connector, with three different signal routing paths.

pin is routed through a pin on the edge. The conclusion is similar to that drawn in the previous section, but the studied frequencies are increased to 3 GHz. The shortest connector signal routing path results in a larger measured near-field as compared to the longest routing path for frequencies up to 2 GHz, although the shortest signal pin has a shorter signal and signal return path, which is usually thought to be beneficial for EMI performance. This may be a result of the connection point of the shortest signal pin to the daughter-board is closer to the bottom edge of the daughter-board than that of the longest signal pin (1 mm versus 10 mm), which results in stronger fringing fields at the connection area. The connecting point of the signal pin on the PCB may also be critical for the EMI performance, since it affects the excitation of the radiating conductors (PCB reference planes). Above 2 GHz, the longest signal path near-field exceeds that of the shortest signal path. The crossing curves and unexpected results for the shortest and longest signal paths demonstrate that at

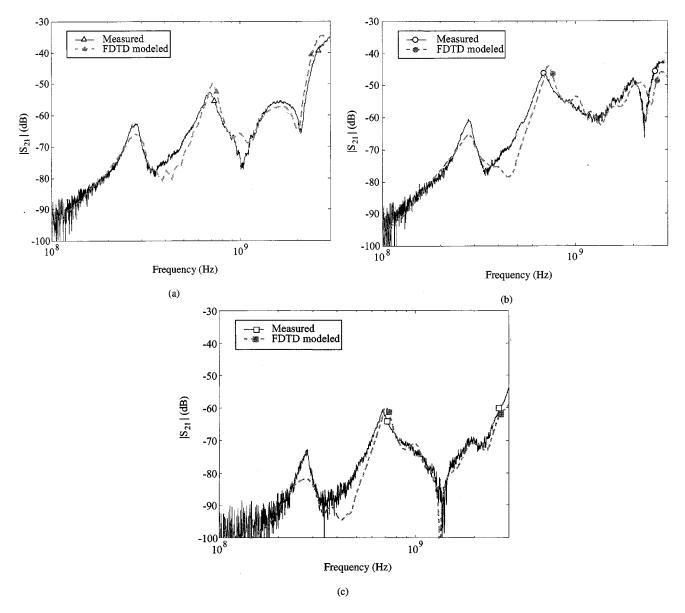

Fig. 14. Measured and FDTD modeled  $|S_{21}|$  for the cases with different connector routing paths: (a) longest signal path; (b) shortest signal path; and (c) inner signal path.

the high-frequencies of concern here, simple notions of minimal inductance and field containment are insufficient to adequately understand the problem physics and geometry features that impact the EMI performance of the connector. FDTD modeling was used to provide further information, and to support the unexpected measurement result.

The FDTD method with a uniform cell size of  $1.25\times0.5\times0.5$  mm<sup>3</sup> was then used to model the geometry shown in Fig. 11. The 3-cm near-field probe and the semi-rigid coaxial cable were modeled as thin wires, and the  $60\times0$ -cm<sup>2</sup> aluminum plate was modeled as an infinite ground plane. The mother-board and the daughter-board were modeled as perfect conductors. The cell size was sufficient for modeling all of the details of the simplified schematic shown in Fig. 12, where the ground blades of the connector were modeled as perfect conductors, and the ground contacts were modeled as thin wires. The two  $135^{\circ}$  bends of the signal pin were approximated by a right angle bend, as shown in the figure. A thin wire algorithm was used to

model all the other wire structures in the fixture. Eight PMLs were placed at each boundary plane of the computational domain, and seven white-space layers were placed between the PML and the test fixture. The source was a sinusoidally modulated Gaussian voltage source with a 50  $\Omega$  resistance in series. The comparisons between the measured and modeled results for the three different cases are shown in Fig. 14. The agreement is generally favorable over the studied frequency range, which indicates that the FDTD method is suitable for modeling the EMI performance of this production connector up to 3 GHz.

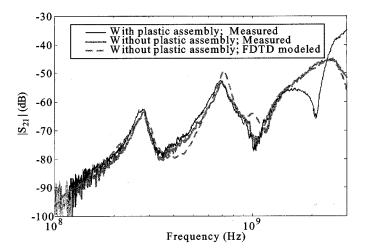

The effect of the dielectric material in the connector assembly was also investigated. The plastic assembly of the stripline geometry, which has an effective relative dielectric constant of approximately 3.0, was removed. The signal pin (the longest one) was replaced by a piece of AWG 24 wire with the same routing path. The measured  $|S_{21}|$  is compared to the measured result for the case with the dielectric assembly in Fig. 15, as well as the FDTD modeled result with no dielectric. The comparison be-

Fig. 15. Effect on near-field of the plastic connector assembly.

tween the two measured results indicates that the dielectric assembly has only marginal effects on the near-field for frequencies less than 1.5 GHz. However, as the frequency increases, transmission-line effects of the connector signal routing path are manifested. The null in the measured  $|S_{21}|$  at approximately 2 GHz for the case with the plastic assembly is actually due to a quarter-wavelength effect of the transmission line. Since the signal is shorted to the ground plane of the daughter-board, it looks like an open circuit at the feeding point and the total current fed into the PCB is a minimum. The FDTD modeled result agrees well with the measured result, which again supports the validity of the FDTD method for EMI performance evaluation of connectors.

#### V. SUMMARY AND CONCLUSIONS

Two measurement methods based on the common-mode current and the near electric-field were used together with FDTD modeling to evaluate the EMI performance of stripline-type connectors in multi-PCB configurations. Using ground blades in the signal return geometry is helpful for controlling EMI, but the performance may be compromised by the impedance associated with the ground contacts. It was shown that the ground-contact length should be minimized in the connector design. Furthemorer, in multilayer PCB designs, the reference plane of high-speed signals should be placed close to the connector so that the length of signal-return via can be reduced. If the length of the ground contacts can be minimized, an excessive number of ground contacts is unnecessary for EMI mitigation, which not only reduces the via density of the board, but also reduces the cost of the connector.

The signal pin designation also impacts the EMI performance of a connector. Routing the signal through the inner connector pin-rows is beneficial for EMI mitigation. Routing the signal on the outer pin rows significantly increases the radiated near electric-field. The implication for circuit design is that the highest speed signals should be routed on inner signal pin rows to achieve the best EMI performance.

Generally, both the common-mode current measurement technique and the near-field monopole approach are suitable for connector evaluation and modeling verification. The FDTD method is an appropriate modeling tool for the EMI performance study of inter-board connections. FDTD can be used for modeling the EMI performance of production stripline-type connectors for frequencies into the gigahertz range.

#### REFERENCES

- [1] D. M. Hockanson, J. L. Drewniak, T. H. Hubing, T. P. Van Doren, F. Sha, and M. J. Wilhelm,, "Investigation of fundamental EMI source mechanisms driving common-mode radiation from printed circuit boards with attached cables," *IEEE Trans. Electromagn. Compat.*, vol. 38, no. 4, pp. 557–565, 1996.

- [2] D. M. Hockanson, X. Ye, J. L. Drewniak, T. H. Hubing, T. P. Van Doren, and R. E. DuBroff, "FDTD and experimental investigation of EMI from stacked-card PCB configurations," *IEEE Trans. Electromagn. Compat.*, vol. 43, pp. 1–10, Feb. 2001.

- [3] X. Ye, J. Nadolny, J. L. Drewniak, T. H. Hubing, T. P. Van Doren, and R. E. DuBroff, "EMI associated with inter-board connection for module-on-backplane and stacked-card configurations," in *IEEE Int. Symp. Electromagnetic Compatibility*, 1999, pp. 797–802.

- [4] K. Li, M. A. Tassoudji, S. Y. Poh, M. Tsuk, R. T. Shin, and J. A. Kong, "FDTD analysis of electromagnetic radiation from modules-on-backplane configuration," *IEEE Trans. Electromagn. Compat.*, vol. 37, pp. 326–332, Aug. 1995.

- [5] L. K. C. Wong, "Backplane connector radiated emission and shielding effectiveness," in *IEEE Int. Symp. Electromagnetic Compatibility*, 1994, pp. 346–351.

- [6] B. Vanlandschoot, L. Martens, L. Van den Torren, and D. Morlion, "An improved triaxial cell for transfer impedance measurements on multipins backplane connectors," in *IEEE Int. Symp. Electromagnetic Com*patibility, 1997, pp. 141–144.

- [7] L. O. Hoeft and J. S. Hofstra, "Measured electromagnetic shielding performance of commonly used cables and connectors," *IEEE Trans. Elec*tromagn. Compat., vol. 30, pp. 260–275, Aug. 1988.

- [8] S. Dunwoody and E. VanderHeyden, "Transfer impedance testing of multiconductor shielded connectors of arbitrary cross section," in *IEEE Int. Symp. Electromagnetic Compatibility*, 1990, pp. 581–585.

- [9] L. O. Hoeft, J. L. Knighten, and M. Ahmad, "Measured surface transfer impedance of multipin micro-D subminiature and LFH connector assemblies at frequencies up to 1 GHz," in *IEEE Int. Symp. Electromagnetic Compatibility*, Seattle, WA, Aug. 1999, pp. 577–582.

- [10] L. Martens, A. Madou, B. Vanlandschoot, L. Kone, B. Demoulin, P. Sjoberg, A. Anton, L. Van den Torren, J. Van Koetsem, H. Hoffmann, and U. Schricker, "Shielding of backplane interconnection technology systems (EU SOBITS project)," in *IEEE Int. Symp. Electromagnetic Compatibility*, Denver, CO, Aug. 1998, pp. 818–822.

- [11] X. Ye, "Advances and applications of the finite difference time domain (FDTD) method and scattering parameter measurement techniques for electromagnetic compatibility in high-speed digital design," Ph.D. dissertation, Univ. Missouri, Rolla, MO, 2000.

- [12] D. M. Pozar, *Microwave Engineering*. New York: Wiley, 1998, ch. 3

- [13] A. Taflove, "The thin wire," in Computational Electrodynamics: The Finite-Difference Time-Domain Method. Norwood, MA: Artech House, 1995. ch. 10.

- [14] J. P. Berenger, "Perfectly matched layer for the absorption of electromagnetic waves," J. Comput. Phys., vol. 114, pp. 185–200, Oct. 1994.

**Xiaoning Ye** (S'98–M'01) was born in China in 1973. He received the B.S. and M.S. degrees in electronics engineering from Tsinghua University, Beijing, China, in 1995, and 1998 respectively, and the Ph.D. degree in electrical engineering from University of Missouri-Rolla in 2000.

Since 1997, he has studied and worked in the Electromagnetic Compatibility Laboratory at University of Missouri-Rolla, where his research and education have been supported by Dean's fellowship and assistantship. He joined Intel Corporation, Hillsboro, OR,

as a Senior EMI Engineer in 2001. His research interests include numerical and experimental study of electromagnetic compatibility and signal integrity problems, and microstrip patch antennas.

**James L. Drewniak** (S'85–M'90–SM'01) received the B.S. (highest honors), M.S., and Ph.D. degrees in electrical engineering from the University of Illinois at Urbana-Champaign in 1985, 1987, and 1991, respectively.

He joined the Electrical Engineering Department at the University of Missouri-Rolla in 1991, where he is part of the Electromagnetic Compatibility Laboratory. His research includes electromagnetic compatibility in high-speed digital and mixed signal designs, electronic packaging, and electromagnetic compati-

bility in power electronic based systems.

Dr. Drewniak is an Associate Editor of the IEEE Transactions on Electromagnetic Compatibility.

**Jim Nadolny** was born in Bridgeport, CT, on April 13, 1961. He received the B.S.E.E. degree from the University of Connecticut, Storrs, in 1984, and the M.S.E.E. degree from the University of New Mexico, Albuquerque, in 1992.

Before joining FCI Electronics, Etters, PA, in 1999, he had been with AMP, Honeywell, and General Electric. He has focused on EMI design and analysis at the system and component levels for 15 years and has recently been focused on multigigabit data transmission for the past several years. He has given many design seminars and provided technical training through the IEEE and at company conferences. His current interests include the signal integrity aspects of interconnection links.

**David M. Hockanson** (S'90–M'98) received the B.S. (honors), M.S., and Ph.D. degrees in electrical engineering from the University of Missouri-Rolla in 1992, 1994, and 1997, respectively.

He was with the Electromagnetic Compatibility Laboratory at the University of Missouri-Rolla, where he worked under a National Science Foundation Graduate Fellowship. He is currently with Sun Microsystems, Inc., Palo Alto, CA, where he is a Staff EMC Engineer. His research interests include circuit modeling of topical EMC issues, in particular, power structures and chip coupling.