## Missouri University of Science and Technology Scholars' Mine

**Electrical and Computer Engineering Faculty** Research & Creative Works

**Electrical and Computer Engineering**

01 Aug 1997

# Investigation of Split Groundplanes at the Connector for EMI Control

David M. Hockanson

James L. Drewniak Missouri University of Science and Technology, drewniak@mst.edu

Joe Nuebel

James C. Parker Jr.

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

## **Recommended Citation**

D. M. Hockanson et al., "Investigation of Split Groundplanes at the Connector for EMI Control," Proceedings of the IEEE International Symposium on Electromagnetic Compatibility (1997, Austin, TX), pp. 177-182, Institute of Electrical and Electronics Engineers (IEEE), Aug 1997. The definitive version is available at https://doi.org/10.1109/ISEMC.1997.667564

This Article - Conference proceedings is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# Investigation of Split Groundplanes at the Connector for EMI Control

David Hockanson, James L. Drewniak Electromagnetic Compatibility Laboratory Department of Electrical Engineering

University of Missouri–Rolla Rolla, MO 65409-0040 Joe Nuebel, James C. Parker, Jr.<sup>†</sup>

Electromagnetic Compatibility Group

Sun Microsystems, Inc.

2550 Garcia Avenue

Mountain View, CA 94043-1100

Abstract: EMI can often be reduced by selectively filtering various parts of a given system. One common method employed by designers is to split the groundplane near the chassis and route I/O lines over the split. The rationale is based on providing a large series impedance to common-mode currents on the I/O lines. In this manner, PCB designers hope to lower the level of noise currents contributing to radiation. This work studies the efficacy of the groundplane split as a deterrent for EMI associated with I/O lines being driven against other extended reference structures. A test-board was developed to analyze the impedance of the groundplane split with various configurations.

#### I. INTRODUCTION

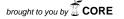

OW-frequency based design principles are often imple-I mented on PCBs to reduce high-frequency EMI. Unfortunately, geometries that can be modeled as lumped elements at low frequencies must be modeled with distributed elements or transmission lines at higher frequencies. One such design technique is a split groundplane at the connector. A split groundplane is often implemented on PCBs that have I/O lines routed to a remote device. Hypothetically, the groundplane split may reduce EMI by introducing a large series impedance in possible "noise" current conduction paths. Noise sources at the printedcircuit level are not well understood, although work is being done to characterize PCB noise sources [1], [2], [3]. Several possible noise sources are suggested herein to facilitate a discussion on the influence of the split groundplane. The first suggested EMI noise path of concern is shown in Figure 1. Multiple reference structures connected to the chassis at various locations result in conducting loops in the system. Magnetic fields that couple the loops generate parasitic currents. This may be a particularly difficult problem at low frequencies (below 500 MHz), because the reactance of the loop is small and higher levels of current may be conducted. The connector plate on a PCB is connected to the chassis. A low-impedance connection is desired between the connector plate and chassis, but may be difficult to achieve. A poor connection between the connector plate and the chassis may result in confining the current to certain regions. The "necking" of current results in a higher concentration of magnetic fields in this area. Consequently, the connection between the connector plate and the chassis may be modeled as an inductor. A potential difference between the connector plate and the chassis may drive the EMI antenna as shown in Figure 1. I/O lines decoupled or otherwise connected to the PCB

<sup>†</sup>James C. Parker, Jr. was with Sun Microsystems, and passed away in the Summer of 1996.

reference plane and the chassis may comprise a dipole-type EMI antenna

At low frequencies, splitting the groundplane near the connector plate effectively breaks the conducting loop by placing a high reactive impedance in series with the loop. Subscribing to a single-point ground in devices is expected to reduce the level of low-frequency current being conducted around the interior of the chassis. As an example, a typical groundplane split in a daughter-card may be modeled approximately as a 20 pFcapacitor. The inductance of the parasitic loop may be approximately 40 nH. Looking at the parasitic loop in Figure 1, 40 nH may seem low. However, most of the conductors are large conductors, not wires, and the value for the loop inductance extracted from the experimental data presented in Section III is less than 40 nH. At frequencies well below the series resonance at  $178 \ MHz$ , the capacitance of the split loads the loop. However, signal return lines that are routed over the split are often decoupled to the chassis island. The chassis island is the region connected to the chassis that has been isolated from the signal ground by the split. This raises the capacitance between the reference plane of the daughter-card and the chassis. Decoupling the signal return lines to the chassis island may lower the series resonance to tens of MHz, consequently lowering the efficacy of the split.

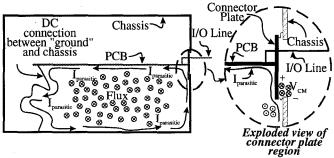

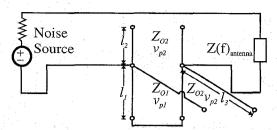

The role of the split in reducing EMI resulting from conducting loops in a chassis is not the focus of this study, but rather is discussed for completeness, because it is often indicated as the underlying reasoning for using a split groundplane for EMI control. The focus of this study is the role of the groundplane split in EMI from radiating I/O lines. In particular, the series impedance of the split for the common-mode path is investigated. Figure 2 suggests another way that noise coupled to an I/O line may result in radiation. Noise may be coupled to the line several ways, including capacitive, or inductive coupling. Noise may also result from a line being connected through a low impedance to a noisy power-bus when the signal line is driven high or low. If the line is decoupled to the reference plane of the PCB, the noise currents should be shunted to the reference and not radiate. Unfortunately, decoupling capacitors are not very useful beyond a few hundred megahertz [4]. The series inductance resulting from mechanically placing the capacitor typically dominates the element's behavior after several hundred megahertz. Therefore noise can be conducted to and radiated from an EMI antenna composed of the I/O line and the chassis. A split is often introduced in the groundplane near the connector plate.

In this paper, theory is developed to describe the high-frequency

Figure 1. Depiction of how conducting loops and poor connector plate connectivity may result in radiated fields. The connector plate region is exploded to show detail.

Figure 2. Schematic showing how noise coupled to an I/O line may radiate from a device. The schematic shows a split groundplane and depicts how noise currents may be conducted around the inside of the chassis, because of the relatively high impedance of the split.

impedance behavior of the groundplane split. Models are developed to facilitate a discussion of the benefits or hindrances of the split. An S-bus test-board was designed and built to analyze the split and determine the effect of the split on EMI. The results of the experimental studies are contained herein.

#### II. THEORY

The groundplane split is expected to reduce EMI associated with I/O lines being driven against the chassis by placing a large series impedance in the path of the noise current. However, placing a split in the PCB forces the noise currents to take a longer conducted path, and not necessarily a high-impedance displacement current path. Figure 2 shows how a noise current may return to its source along the inside of the chassis. The longer current path is a loop and can be modeled as an inductor at low frequencies, and the groundplane split can be modeled as a capacitor. The groundplane split at low frequencies may not appreciably reduce the level of the noise current, because the alternate current path below the PCB is not high impedance. Furthermore, if the EMI antenna resonance frequency is defined as the frequency at which the antenna reactance is zero, the introduction of the groundplane split may simply shift the resonance frequency, and not necessarily reduce the level of radiation. The radiated levels could be reduced if the resonance frequency were shifted to a frequency where the radiation resis-

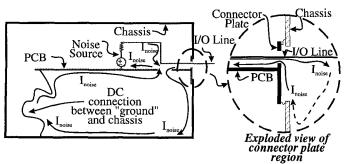

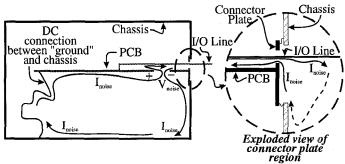

Figure 3. Schematic showing how a split groundplane may increase radiation if the power-bus is noisy with respect to the chassis.

tance was significantly higher than without the split. However, this is not a dependable design approach because cable lengths may not be standard, and the end-user may wish to change the cable. The split groundplane design will provide a high series impedance over a narrow bandwidth around the parallel resonance between  $L_{loop}$  and  $C_{split}$ . Beyond this resonance, the parallel circuit looks capacitive and begins to short.

The noise model shown in Figure 2 assumes the noise source is driving the I/O line relative to the reference plane. However, if the power-bus itself is at a different RF potential relative to the chassis, as shown in Figure 3, the groundplane split can exacerbate the noise problem. The noise source in Figure 3 may be a power-bus that has significant RF noise with respect to another reference structure in the chassis. Various connectors, reference planes, and the chassis provide a conduction path for noise currents to return to their source. Without connectivity between the PCB reference planes and the chassis near the connector plate, the I/O line (shown connected to the PCB reference plane in Figure 3) can be driven against the chassis where the I/O line exits. When the groundplane is continuous, the I/O line is at relatively the same potential as the chassis where the I/O line exits the system. Consequently, the EMI antenna terminals are effectively shorted, and EMI is reduced.

The high-frequency behavior of the split groundplane design is more complicated. The extended noise current path resulting from the split may be of significant electrical extent and must be treated as a shorted transmission line. The transmission-line model may be different for every device, adding to the difficulty of a generalized analysis. The transmission-line model is somewhat crude for modeling the loop. The loop is comprised of various planes and connectors that may have resonances other than those predicted by a simple transmission-line model. However, the transmission-line model should provide a reasonable approximation. The width of the slot in the groundplane is assumed small with respect to wavelength.

The groundplane split was treated as a lumped element capacitance in the preceding discussion. However, even on small daughter-cards the split length is on the order of  $10\ cm$ . Common S-bus cards are  $8\ cm$  wide. If the splits were completely embedded in FR-4 material, the splits would no longer be electrically small beyond a few hundred megahertz. Currents take the path of least impedance, therefore it is well accepted that the return current for a microstrip circuit will return directly under the trace, given a continuous groundplane. When the

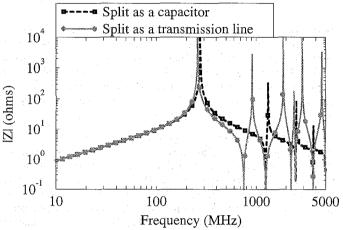

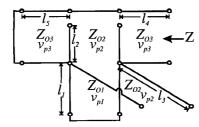

Figure 4. Circuit model depicting a noise source driving an I/O line over a split groundplane.  $L_{loop}$  and  $C_{split}$  have been replaced with transmissionline models.

Figure 5. Comparison of the magnitude of the impedance for the split modeled as a capacitor and the split modeled as two parallel transmission lines.

groundplane is split, displacement current will cross the split. However, if the split is electrically long, it will behave as a slotline transmission line. The electric-field distribution in the split is a function of frequency. Depending on the "mode" excited in the groundplane split, the impedance may vary between small and large values. The split must then be treated as a transmission line with input terminals where the trace crosses the split. Consequently, the high-frequency model for the groundplane split in parallel with the conducting loop consists of three transmission lines in parallel as shown in Figure 4. The transmission line of length  $l_1$  models the loop below the PCB shown in Figure 2, while the transmission lines of length  $l_2$  and  $l_3$ model the groundplane split on either side of the trace. For the complete equation that models the parallel transmissionline circuit, the reader is referred to [5]. The magnitude of the impedance is shown in Figure 5, and compared to the magnitude of the impedance with the split treated as a simple 20 pFcapacitor. The characteristic impedance of the split was assumed  $Z_{O2} = 25\Omega$ , and the phase velocity was assumed to be half the speed of light in a vacuum  $v_{p2} = 1.5 \times 10^{10} \frac{cm}{s}$ . The total length of the split was taken as 8 cm, with  $l_2 = 3 cm$  and  $l_3 = 5 cm$  to model a trace crossing a split just off center. The card width 8 cm was chosen to approximately model a standard S-bus daughter-card. The phase velocity was chosen to simulate a slotline completely embedded in FR-4 material with a relative dielectric constant  $\epsilon_r \approx 4$ . The characteristic impedance of the line was chosen as a realistic value for a slotline. The parameters for the transmission line of length  $l_1$ , which models the loop below the PCB, were approximated as:  $l_1=12~cm$ ,  $v_p=3.0\times 10^{10}\frac{cm}{s}$ , and  $Z_{O1}=35\Omega$ . The phase velocity was chosen because the loop is air filled, but the other parameters were chosen simply as realistic transmission-line parameters for the example. The results for the transmission-line modeled split correlate closely with the capacitor model up to a few hundred megahertz, as expected. The highly oscillatory behavior between low and high impedance at higher frequencies indicates the split may be of little benefit for EMI control. Depending on the noise source, a broadband high- or low-impedance may be necessary. However, according to the model, the ground-plane split results in both high- and low-impedances over narrow bandwidths.

#### III. EXPERIMENTAL RESULTS

Test-boards were developed to analyze the role of the groundplane split in EMI and determine the validity of the proposed models. The test-boards were S-bus daughter-cards. S-bus cards are frequently used by Sun Microsystems and therefore the test-boards may be analyzed in a wide range of high-speed machines. The test-boards were used in a Sparcstation 20 and an S1000 server with similar results.

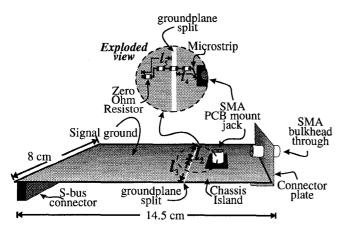

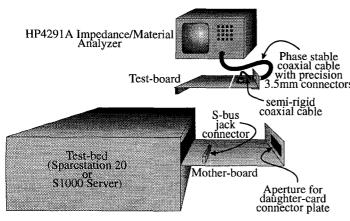

Two test-boards were built. The boards were identical except that one has a continuous groundplane and the other has a split groundplane. The boards were fitted with SMA PCB jacks to allow measurement at different locations. Figure 6 shows the basic design for the test-board with a groundplane split. For measuring the impedance of the groundplane split, the SMA PCB mount jack was connected to the SMA bulkhead through with a short 0.085" semi-rigid coaxial cable. The housing of the SMA jack was connected to the chassis island, and the centerconductor was routed over the split using zero ohm resistors. The impedance of the groundplane split was measured using a HP4291A Impedance/Material Analyzer (1 MHz - 1.8 GHz). The general setup configuration is shown in Figure 7. The impedance analyzer was calibrated and then compensated to the end of the attached semi-rigid cable. Consequently, the measurement reference plane was at the SMA PCB mount jack on the chassis island. No peripherals or power cables were connected to the test-bed during impedance measurements.

The configuration of the test board prohibits the direct measurement of the groundplane split. The impedance analyzer can be calibrated and compensated to the SMA PCB jack, however, the trace that crosses the gap and connects to the signal ground adds electrical length to the measurement path. The transmission-line model for this setup is shown in Figure 8. The transmission line of length  $l_1$  models the loop below the PCB as shown in Figure 4. The lines of length  $l_2$  and  $l_3$  model the groundplane split on either side of the trace. The transmission line of length  $l_4$  models the microstrip between the split and the calibrated reference plane, and the line of length  $l_5$  models the "stub" that is shorted to the PCB reference plane on the other side of the split. The parameters  $l_2, l_3, l_4$ , and  $l_5$  are shown in Figure 6. For the complete equation that models the parallel transmission-line circuit, the reader is referred to [5].

Some parameters can be determined empirically from the data,

Figure 6. Test-board layout showing the basic setup for taking measurements. The exploded region shows how the center conductor of the SMA jack was routed over the trace to the signal ground using microstrip traces and zero ohm resistors. The lengths designated by  $l_2, l_3, l_4$ , and  $l_5$  are the lengths of the transmission lines comprising the equivalent circuit model.

Figure 7. Schematic depicting the configuration used for taking impedance measurements.

Figure 8. Transmission line model for measuring the impedance of the groundplane split with the test-board.

Figure 9. Comparison of the magnitude of the impedance for the transmission-line model and experimental data for the continuous groundplane test-board.

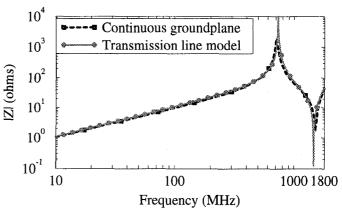

and some from the literature. Initially the continuous groundplane was analyzed to determine the exact lengths of  $l_4$  and  $l_5$ . The phase velocity and characteristic impedance for the PCB transmission lines (microstrip) were calculated to be  $v_{p3} =$  $\frac{3.0\times10^{10}}{\sqrt{3.0}}\frac{cm}{s}$ ,  $Z_{O3}=47\Omega$ , respectively, where  $\sqrt{3.0}$  is the effective relative dielectric constant for the microstrip geometry [6]. The length of the transmission-line "stub" where the microstrip is connected to the PCB ground was measured to be  $l_5 = 1.5 \ cm$ . Experimentally, a quarter-wave resonance was measured around 660 MHz, indicating that the length of the transmission line between the location of the groundplane split and the calibrated Freference plane must be  $l_4 = 4.8 cm$ . Figure 9 shows a comparison between the transmission line model and the experimental data for the continuous groundplane for two different cases of  $l_2$  and  $l_3$ . The results agree well, although at the resonances the magnitude of the impedance is quite different. This results from the loss in the conductors and zero ohm resistors of the test-board, as well as an imperfect termination to the transmission line.

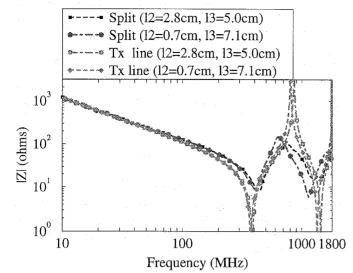

The parameters associated with the groundplane split transmission lines can be determined in a similar manner. The test-board with the split groundplane was connected to the impedance analyzer without being connected to the motherboard. Ferrite sleeves were used to isolate the test device from the test equipment. The equivalent circuit should be the same as in Figure 8 with the omission of the transmission line with a characteristic impedance  $Z_{O1}$ , which models the loop below the PCB in the chassis. The length of the open-terminated transmission lines can be measured approximately with a ruler on the test-board. The characteristic impedance and phase velocity of Lines 2 and 3 can be determined empirically to match the experimental results. Figure 10 shows a comparison between the transmission-line model and the experimental data for  $l_2 = 2.8 \ cm, l_3 = 5.0 \ cm$  and  $l_2 = 0.7 \ cm, l_3 = 7.1 \ cm$ (see Figure 6). The zero ohm resistors were approximately 2mm wide. The characteristic impedance and phase velocity for the open-terminated transmission lines were determined to be  $Z_{O2}=37\Omega,\ v_{p2}=\frac{3.0\times10^{10}}{\sqrt{1.2}}\frac{cm}{s}$ , respectively, where  $\epsilon_r\approx 1.2$ . The phase velocity was chosen by matching the approximate resonance frequencies of the data with the resonance frequen-

Figure 10. Comparison of the magnitude of the impedance for the transmission-line model and experimental data for the split groundplane not installed in the mother-board. The impedance was measured at two locations,  $l_2 = 2.8 \text{ cm}, l_3 = 5.0 \text{ cm}$  and  $l_2 = 0.7 \text{ cm}, l_3 = 7.1 \text{ cm}$  (see Figure 6).

cies of the slotline model. The characteristic impedance  $Z_{O2}$  was found by matching the model impedance and the experimental impedance results at 10 MHz, and solving for  $Z_{O2}$ .

The discrepancies at the extrema indicate some shortcomings of the transmission-line model. The magnitudes of the impedance at the extrema do not match well, because the loss in the conductors and the terminations are not incorporated into the transmission-line model. The loss in the conductors will result in a higher impedance at the zeros. At the poles, several parameters influence the value of the impedance. The transmissionline models use perfect shorts and opens to model the split, loop, and microstrip terminations. On the PCB current necking results in higher density magnetic-fields (inductance), and open circuits have fringing electric-fields (capacitance). The groundplane split is a slotline transmission line. The slotline is embedded in FR-4 material surrounded by air, therefore the characteristic impedance is a function of frequency [7]. The phase velocity and characteristic impedance determined for the slotlines empirically were chosen because they gave the best fit for a constant value. Despite the deficiencies, the model describes the relevant physics associated with the groundplane split, and shows fair agreement when compared to the experimental results.

The first resonance shown in Figure 10 is a series LC resonance. The loop consisting of the microstrip crossing the groundplane split and terminating on the signal ground is in series with the split, which at lower frequencies should look capacitive. The resonances beyond 350 MHz, however, result from transmission line resonances. If the slot were modeled as a simple capacitor over the observed bandwidth, moving the location where the trace crosses the groundplane split would result in no change in the resonance frequencies. However, the experimental results show a shift in the resonance frequencies, as predicted by the

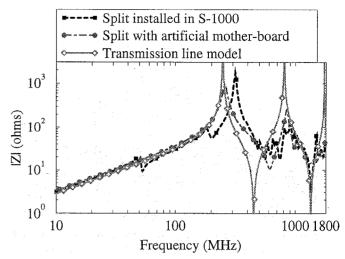

Figure 11. Comparison of the magnitude of the impedance for the transmission-line model, experimental data for the split groundplane installed in the S1000, and experimental data with the artificial mother-board.

transmission line model.

The split groundplane card was installed in the S1000, and the impedance was measured with the impedance analyzer. The parameters for the final unknown transmission line were matched empirically, and determined to be  $Z_{O1} = 137\Omega$ ,  $v_{p1} = 3.0 \times 10^{10} \frac{cm}{s}$ , and  $l_1 = 6.0$  cm. The phase velocity was chosen because the loop (or transmission line) beneath the PCB in the chassis was air filled. The length  $l_1$  was chosen to approximately match the transmission-line resonances with the resonances found in the experimental data, and the characteristic impedance  $Z_{O1}$  was determined by equating the impedance for the model and the experimental results at 10 MHz, and solving for  $Z_{O1}$ . Figure 11 shows the comparisons for the split groundplane test-board installed in the S1000. The transmission-line model shows similar impedance oscillations compared to the experimental data, although the location of the first resonance is significantly displaced. This is a result of the discrepancies between the simple transmission-line model for the loop and the actual properties of the loop. An artificial "mother-board" was constructed to verify that the resonances were a result of the transmission-line nature of the system, and not dependent on the chassis or lumped elements in the test-bed. The artificial mother-board was created by soldering four inch wide copper tape to four via pads on top of the board that were connected to the reference planes of the test-board. The vias were located adjacent and parallel to the top of the S-bus connector. The copper tape was wrapped around the bottom of the test-board and brought back up to the top of the card under the chassis connector plate. The copper tape was then connected to the chassis-island using the conductive adhesive backing of the copper tape. The results for the magnitude of the impedance for the artificial mother-board are shown in Figure 11. The test-board was not installed in the mother-board or the chassis for the impedance measurement. The experimental results for the artificial mother-board and the test-board installed in the S1000 show fair agreement. The smaller oscillations in the ex-

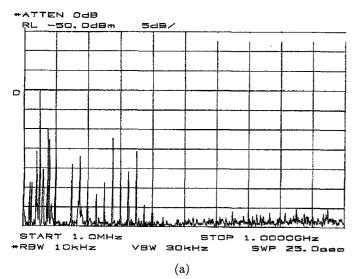

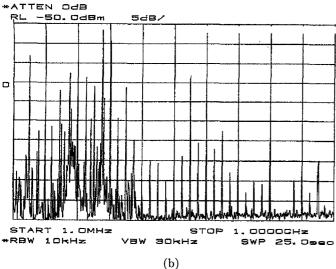

Figure 12. Radiated fields for the test-card installed in a S1000 with (a) the continuous groundplane test-card, and (b) the split groundplane test-card.

perimental data with the test-board installed in the S1000 may be a result of other parasitics in the S1000 not modeled, such as cavity resonances or coupling to other circuitry.

The previous tests were designed to analyze the impedance of the groundplane split and determine if the transmission-line model could adequately describe the split groundplane system. However, the model focuses on the impedance of the groundplane split. One experiment was done to explore whether the groundplane split reduces radiated energy or not. The test-board was installed in the S1000 with an I/O line connected to  $V_{CC}$ . A 1 m section of 24 AWG copper wire was connected to the I/O line, and power was supplied to the S1000. No cables other than the I/O line and the power cable were connected to the S1000. The system was setup in a shielded chamber and the radiated fields were measured with a horizontally polarized EMCO log-periodic dipole array (200 MHz-1 GHz) connected to an HP8563E Spectrum Analyzer (9 kHz-1 GHz). No ac-

tive circuitry was on the daughter-card, although a 25 MHz clock is routed through the S-bus connector from the mother-board to the top of the daughter-card. The clock trace on the daughter-card was 2 cm long and unterminated, and was not in proximity with the I/O line connected to  $V_{CC}$ . The results are shown in Figure 12 for the configuration with the continuous groundplane test-board and the split groundplane test-board. The split groundplane test-board resulted in significantly higher levels of radiation over a large bandwidth.

#### IV. CONCLUSION

Designers often use a split groundplane technique to isolate PCB reference planes (signal groundplanes) from "quiet" grounds. The rationale underlying the approach is typically based on increasing the impedance in the common-mode path. This investigation focused on the impedance of the split groundplane. A test-board was designed and the series impedance provided by the groundplane split was analyzed. A transmission-line equivalent circuit was developed to model the groundplane split. The transmission-line model was found to have fair agreement up to 1.8 GHz, which was the limit of the test equipment. The transmission-line model presented gave sufficient results for predicting the high-frequency dependence of the groundplane split. At high-frequencies the groundplane split impedance oscillates between high and low values. Consequently, the groundplane split can not be used to provide a strictly high- or low-impedance over a large bandwidth. The radiated fields for a continuous groundplane and a split groundplane were measured for one particular type of I/O line. The radiated fields for the split groundplane were significantly higher over the measured bandwidth.

### REFERENCES

- D. M. Hockanson, J. L. Drewniak, T. H. Hubing, T. P. Van Doren, Fei Sha, and M. Wilhelm, "Investigation of fundamental EMI source mechanisms driving common-mode radiation from printed circuit boards with attached cables", IEEE Transactions on Electromagnetic Compatibility, pp. 557-566, November 1996.

- [2] M. Radojicic and G. Costache, "A model to predict radiated emissions from electronic circuits", in *IEEE International* Symposium on Electromagnetic Compatibility, Cherry Hill, NJ, 1991, IEEE Electromagnetic Compatibility Society, pp. 54–57.

- [3] J. R. Bergervoet, "EMC measurements and models connecting the system level with the module level", *Phillips Journal of Research*, vol. 48, pp. 63–80, 1994.

- [4] T. H. Hubing, J. L. Drewniak, T. P. Van Doren, and D. M. Hockanson, "Power bus decoupling on multilayer printed circuit boards", *IEEE Transactions on Electromagnetic Com*patibility, pp. 155-166, May 1995.

- [5] D. M. Hockanson and J. Nuebel, "Report on the efficacy of split groundplanes as an EMI deterrent", Tech. Rep. TR97-1-020, University of Missouri-Rolla EMC Lab, February 1997.

- [6] D. M. Pozar, Microwave Engineering, Addison-Wesley Publishing Company, Inc., Reading, Massachusetts, 1990.

- [7] K. C. Gupta, R. Garg, I. Bahl, and P. Bhartia, Microstrip Lines and Slotlines, Artech House, Boston, Massachusetts, second edition, 1996.