Missouri University of Science and Technology Scholars' Mine

Mechanical and Aerospace Engineering Faculty Research & Creative Works

Mechanical and Aerospace Engineering

01 Sep 2008

# Reducing Computational Time Delay in Digital Current-Mode Controllers for Dc-dc Converters

Kai-tak Wan Missouri University of Science and Technology

Mehdi Ferdowsi Missouri University of Science and Technology, ferdowsi@mst.edu

Follow this and additional works at: https://scholarsmine.mst.edu/mec\_aereng\_facwork

🔮 Part of the Electrical and Computer Engineering Commons

# **Recommended Citation**

K. Wan and M. Ferdowsi, "Reducing Computational Time Delay in Digital Current-Mode Controllers for Dcdc Converters," *Proceedings of the IEEE 30th International Telecommunications Energy Conference, 2008,* Institute of Electrical and Electronics Engineers (IEEE), Sep 2008. The definitive version is available at https://doi.org/10.1109/INTLEC.2008.4664114

This Article - Conference proceedings is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Mechanical and Aerospace Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# **Reducing Computational Time Delay in Digital Current-Mode Controllers for Dc-Dc Converters**

Kai Wan and Mehdi Ferdowsi, *Member*, *IEEE* Missouri University of Science and Technology, Rolla, MO, USA <u>kwzm7@mst.edu</u> and <u>ferdowsi@mst.edu</u>

Abstract—A new method to improve the performance of digital current-mode controllers used in dc-dc power conversion is introduced. The proposed scheme is based on a simple prediction method which offers more time for DSP calculations than its conventional counterparts. Therefore, there will be less DSP computational time delay, which results in faster dynamic response and more accuracy and stability in power electronic converters. Principles of operation of the proposed prediction method as well as its application to several digital control techniques are presented.

#### I. INTRODUCTION

Digital control of dc-dc converters has had a substantial development over the past few years [1-18]. Compared with analog techniques, digital control techniques offer a number of advantages including programmability, higher flexibility, fewer components, and less sensitivity to noise. These advantages make digital control methods become a viable solution to meet the requirements for voltage- and/or current-mode control techniques.

Several digital current-mode control techniques have recently been reported in the literature including current programming [1], estimative [2], predictive [3], deadbeat [4-7], and digital [8, 9]. Although, different names have been adopted to present these methods, it can be proven that most of them are based on the deadbeat control theory [10]. All of these methods try to make the peak, average, or valley value of the inductor current track a reference signal. These conventional digital control methods have several limitations. For instance the methods introduced in [1, 2, 8, 9] assume that the digital signal processor (DSP) is fast enough to calculate the required duty ratio while the switch is conducting and before its conduction time is over (less then one switching cycle). Methods introduced in [3, 4] assume that the reference current is almost constant; based on which an extra switching period of time delay is introduced in order to provide the DSP more calculation time.

In this paper, a prediction method for the reference current is introduced. Based on the proposed prediction technique, the DSP starts the calculations for the duty ratio in advance and before the beginning of the related switching cycle. This improved method allows more calculation time for the DSP without imposing any extra time delay. The dynamic response of the proposed method is very fast. In Section II, several conventional digital control methods are compared. The proposed prediction approach is discussed in Section III, where it is applied to the conventional digital control schemes. Simulation results comparing the performance of a conventional digital control before and after the application of the proposed predictive method are presented in Section IV. Finally, Section V draws conclusions and presents an overall evaluation of the proposed method.

#### II. CONVENTIONAL DIGITAL CURRENT-MODE CONTROL METHODS

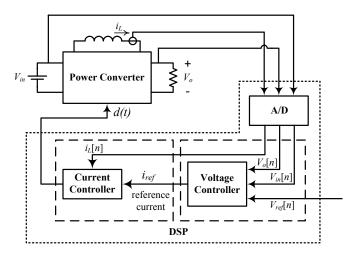

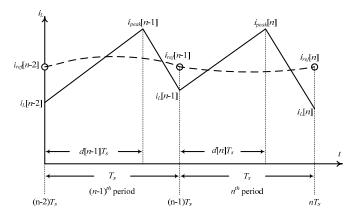

Fig. 1 depicts the block diagram of a digital current-mode controller implemented using a DSP. Using samples of the inductor current and input and output voltages, the DSP tries to satisfy the control objective by finding the right value for the duty ratio. In current-mode control, the objective is to force the peak, average, or valley value of the inductor current to follow reference current  $i_{ref}$ . In most applications, the reference current itself is obtained from a voltage compensator. In this paper, without loss of generality, the buck converter is used to discuss the proposed method. Typical inductor current waveform of a buck converter operating in continuous conduction mode is shown in Fig. 2.

Table I compares the main characteristics of the most common digital current-mode control approaches [10]

Fig. 1. Block diagram of a digital current-mode controller.

## 978-1-4244-2056-8/08/\$25.00 ©2008 IEEE

| Conventional current-<br>mode control method | Control objective                                               | Control equation                                                                                                                  | DSP processing time limit (in switching cycles) |

|----------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Valley [1]                                   | $i_L[n] = i_{ref}[n-1]$                                         | $d[n] = \frac{L}{V_{in}T_s} (i_{ref}[n-1] - i_L[n-1]) + \frac{V_o}{V_{in}}$                                                       | Less than one                                   |

| Average [2]                                  | $\frac{1}{T_s} \int_{(n-1)T_s}^{nT_s} i_L(t) dt = i_{ref}[n-1]$ | $d[n] = \frac{L}{V_{in}T_s} (i_{ref}[n-1] - \frac{T_sV_o}{2V_{in}} \cdot \frac{V_{in} - V_o}{L} - i_L[n-1]) + \frac{V_o}{V_{in}}$ | Less than one                                   |

including valley current control [1] and average current control [2]. In most of these control methods, it is assumed that reference current  $i_{ref}$  is fairly constant. Input and output voltages are slowly varying signals and can be considered constant during one switching period. Therefore one can write

$$V_o[n] \approx V_o[n-1]$$

and  $V_{in}[n] \approx V_{in}[n-1]$ . (1)

Hence, for the sake of simplicity in the following equations, input and output voltages are not shown as sampled signals even though they actually are.

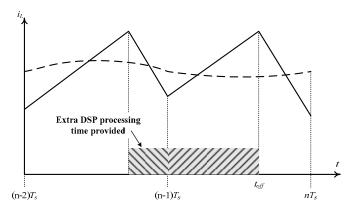

As it can be observed from Fig. 2 and Table I, in conventional valley and average digital current-mode control methods, samples of inductor current  $i_L[n-1]$  and reference current  $i_{ref}[n-1]$  are obtained at the beginning of the switching period. Using these control methods, DSP should calculate the required duty ratio before the time at which the conduction of the switch is over. In these cases, DSP processing time limit is less than one switching cycle, which is not long enough. The DSP processing time provided by conventional digital control methods is shown in Fig. 3.

## III. PREDICTIVE TECHNIQUE TO IMPROVE THE CONVENTIONAL DIGITAL CONTROL TECHNIQUES

In order to provide more calculation time for the DSP, one would devise prediction methods for  $i_L[n-1]$  and  $i_{ref}[n-1]$ . In such a case, the DSP does not have to wait until the beginning of the switching cycle to sample  $i_L[n-1]$  and  $i_{ref}[n-1]$ . These two signals will be predicted during the previous switching cycle right after the switch is turned off and DSP is free. The extra DSP processing time provided by the proposed digital control method is shown in Fig. 4.

## A. Proposed method to predict $i_L[n-1]$

The final value of the inductor current in each period can be described as a function of the initial value of the inductor current, positive and negative slopes, and the duration of the switch on- and off-times. Using Fig. 2, one could describe  $i_L[n-1]$  as a function of previous samples that are already available in the DSP. In other words,

$$i_{L}[n-1] = i_{L}[n-2] + \frac{(V_{in} - V_{o})d[n-1]T_{s}}{L} - \frac{V_{o}(1 - d[n-1])T_{s}}{L}$$

(2)

Where,  $T_s$  is the switching period and L is the inductor value. Equation (2) can be simplified as

Fig. 2. Actual and reference inductor current waveforms (in this figure average current-mode control is considered).

Fig. 3. DSP processing time provided by conventional digital control methods.

Fig. 4. Extra DSP processing time provided by the proposed method.

$$i_{L}[n-1] = i_{L}[n-2] + \frac{V_{in}d[n-1]T_{s}}{L} - \frac{V_{o}T_{s}}{L}$$

(3)

It is worth mentioning that all the required samples on the right-hand side of (3) are already available in the DSP after the switch is turned off in the previous switching cycle. Equation (3) is used to predict  $i_L[n-1]$ .

#### B. Proposed method to predict $i_{ref}[n-1]$

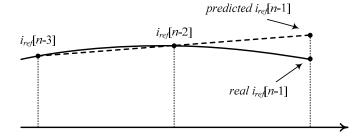

Previous samples of  $i_{ref}$  are used to predict  $i_{ref}[n-1]$ . Using a slope prediction approach, one can describe  $i_{ref}[n-1]$  as

$$i_{ref}[n-1] = i_{ref}[n-2] + (i_{ref}[n-2] - i_{ref}[n-3])$$

=  $2i_{ref}[n-2] - i_{ref}[n-3]$  (4)

Comparison between the predicted  $i_{ref}$  and real  $i_{ref}$  is shown in Fig. 5. It is worth mentioning that in most cases  $i_{ref}$  is the output of a voltage compensator; therefore, it does not have high frequency components.

For instance, by replacing the predicted values for  $i_L[n-1]$  and  $i_{ref}[n-1]$  (equations (3) and (4)), the improved equation for the conventional valley control (see Table I) will be

$$d[n] = \frac{L}{V_{in}T_s} (2i_{ref}[n-2] - i_{ref}[n-3] - i_L[n-2]) - d[n-1] + 2\frac{V_o}{V_{in}}$$

(5)

Table II depicts the control equations obtained by using the proposed predictive method. Comparison between the control equations of Tables I and II reveals that the proposed method does not impose any extra calculation time even though the related equations seem to be longer. The advantage here is that by using the proposed prediction method, additional calculation time will be provided to the DSP (compare last columns of Tables I and II).

#### **IV. SIMULATION RESULTS**

In order to study the dynamic performance of the proposed prediction method, a conventional digital average currentmode controller and its modified predictive counterpart are simulated and compared. The parameters of the buck converter are input voltage:  $V_{in} = 6 \text{ V}$ ; inductor value:  $L = 108 \text{ }\mu\text{H}$ ; capacitor value:  $C = 92 \text{ }\mu\text{F}$ ; switching frequency:  $f_s = 100 \text{ kHz}$ ; and load resistance:  $R = 3 \Omega$ .

Fig. 5. Comparison between the predicted  $i_{ref}$  and real  $i_{ref}$ .

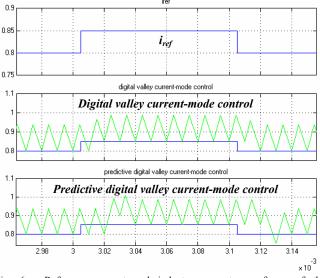

Fig. 6. Reference current and inductor current waveforms of the conventional digital valley current-mode controller and that of the proposed predictive digital valley current-mode controller when reference current has step changes.

Reference current and inductor current waveforms of the conventional digital valley current-mode controller and that of the proposed predictive digital valley current-mode controller, when reference current has step changes, are shown in Fig. 6. It can be observed that the proposed prediction scheme almost has the same performance as the conventional one. However, in the predictive approach, additional time is provided for DSP calculations. Therefore, the predictive average current-mode control can be used at higher switching frequency applications.

| PROPOSED DIGITAL CURRENT-MODE CONTROL METHODS |                  |  |  |  |  |

|-----------------------------------------------|------------------|--|--|--|--|

| ontrol objective                              | Control equation |  |  |  |  |

TABLE II

| Proposed current control method | Control objective                                               | Control equation                                                                                                                                             | DSP processing time limit<br>(in switching cycles) |

|---------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Predictive valley               | $i_L[n] = i_{ref}[n-1]$                                         | $d[n] = \frac{L}{V_{in}T_s} (2i_{ref}[n-2] - i_{ref}[n-3] - i_L[n-2]) - d[n-1] + 2\frac{V_o}{V_{in}}$                                                        | One                                                |

| Predictive<br>average           | $\frac{1}{T_s} \int_{(n-1)T_s}^{nT_s} i_L(t) dt = i_{ref}[n-1]$ | $d[n] = \frac{L}{V_{in}T_s} (2i_{ref}[n-2] - i_{ref}[n-3] - i_L[n-2] - \frac{T_sV_o}{2V_{in}} \cdot \frac{V_{in} - V_o}{L})$ $-d[n-1] + 2\frac{V_o}{V_{in}}$ | One                                                |

# V. CONCLUSIONS

A prediction technique which makes DSP utilization more practical in the realization of digital current-mode controllers is introduced in this paper. Due to the fact that the DSP does not have enough time to perform all the required calculations, conventional digital control methods reviewed in this paper do not perform very well when the switching frequency is high. Using the proposed prediction method, the DSP will have longer processing time. The control equations of two control methods modified by the improved prediction algorithm are presented in this paper. The simulation result shows that the proposed predictive digital controller performs as well as conventional digital current-mode control methods.

#### REFERENCES

- P. Shanker and J. M. S. Kim, "A new current programming technique using predictive control," in *Proc. IEEE International Telecommunications Energy Conference*, Nov. 1994, pp. 428-434.

- [2] M. Ferdowsi, "An estimative current mode controller for dc-dc converters operating in continuous conduction mode," *in Proc. APEC*, Mar. 2006, pp. 19-23.

- [3] J. Chen, A. Prodic, R. W. Erickson, and D. Maksimovic, "Predictive digital current programmed control," *IEEE Trans. Power Electronics*, vol. 18, no. 1, pp. 411-419, Jan. 2003.

- [4] S. Bibian and J. Hua, "High performance predictive dead-beat digital controller for DC power supplies," *IEEE Trans. Power Electronics*, vol. 17, no. 3, pp. 420-427, May 2002.

- [5] S. Bibian and J. Hua, "Time delay compensation of digital control for DC switch mode power supplies using prediction techniques," *IEEE Trans. Power Electronics*, vol. 15, no. 5, pp. 835-842, Sep. 2000.

- [6] S. Bibian and J. Hua, "A simple prediction technique for the compensation of digital control time delay in DC switch mode power supplies," in *Proc. IEEE Applied Power Electronics Conference and Exposition*, Mar. 1999, pp. 994-1000.

- [7] S. Bibian and J. Hua, "Digital control with improved performance for boost power factor correction circuits," in *Proc. IEEE Applied Power Electronics Conference and Exposition*, Mar. 2001, pp. 137-143.

- [8] S. Chattopadhyay and S. Das, "A digital current-mode control technique for DC–DC converters," *IEEE Trans. Power Electronics*, vol. 21, no. 6, pp. 1718-1726, Nov. 2006.

- [9] S. Chattopadhyay and S. Das, "A digital current mode control technique for DC-DC converters," in *Proc. IEEE Applied Power Electronics Conference and Exposition*, Mar. 2005, pp. 885-891.

- [10] K. Wan, J. Liao, and M. Ferdowsi, "Control methods in dc-dc power conversion – a comparative study," in *Proc. IEEE Power Electronics Specialists Conference*, Jun. 2007, pp. 921-926.

- [11] C. C. Fang and E. H. Abed, "Sampled-data modeling and analysis of the power stage of PWM dc-dc converters," *Technical Research Report*, 1999.

- [12] G. C. Verghese, C. A. Bruzos, and K. N. Mahabir, "Averaged and sampled-data models for current mode control: a re-examination," in *Proc. IEEE Power Electronics Specialists Conference*, 1989.

- [13] F. Huliehel and S. Ben-Yaakov, "Low-frequency sampled-data models of switched mode DC-DC converters power electronics," *IEEE Trans. Power Electronics*, vol. 6, no. 1, pp. 55-61, Jan. 1991.

- [14] C. C. Fang and E. H. Abed, "Sampled-data modeling and analysis of closed-loop PWM DC-DC converters," in *Proc. IEEE Int. Symp. Circuits and Systems*, May 30-Jun. 2, 1999, pp. 110-115.

- [15] G. C. Verghese, M. E. Elbuluk, and J. G. Kassakian, "A general approach to sampled-data modeling for power electronics circuit," *IEEE Trans. Power electronics systems*, pp. 45-55, 1986.

- [16] A. Brown and R. D. Middlebrook, "Sampled data modeling of switching regulators," in *Proc. IEEE Power Electronics Specialists Conference*, 1981, pp. 349-369.

- [17] J. Weigold and M. Braun, "Robust predictive dead-beat controller for buck converters," in *Proc. IEEE Int. Power Electronics and Motion Control*, Aug. 2006, pp. 951-956.

- [18] O. Kukrer and H. Komurcugil, "Deadbeat control method for singlephase UPS inverters with compensation of computation delay," in *Proc. IEE Electric Power Applications*, Jan. 1999, pp. 123-128.