# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Summer 2015

# Reliability and security in low power circuits and systems

Hui Geng

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Computer Engineering Commons

**Department: Electrical and Computer Engineering**

#### **Recommended Citation**

Geng, Hui, "Reliability and security in low power circuits and systems" (2015). Doctoral Dissertations. 2648.

https://scholarsmine.mst.edu/doctoral\_dissertations/2648

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# RELIABILITY AND SECURITY IN LOW POWER CIRCUITS AND SYSTEMS

by

# **HUI GENG**

# A DISSERTATION

Presented to the Faculty of the Graduate School of the MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

DOCTOR OF PHILOSOPHY

in

**COMPUTER ENGINEERING**

2015

Approved by

Dr. Yiyu Shi, Advisor Dr. Daryl G. Beetner Dr. Minsu Choi Dr. Jun Fan Dr. Boping Wu

#### ABSTRACT

With the massive deployment of mobile devices in sensitive areas such as healthcare and defense, hardware reliability and security have become hot research topics in recent years. These topics, although different in definition, are usually correlated. This dissertation offers an in-depth treatment on enhancing the reliability and security of low power circuits and systems. The first part of the dissertation deals with the reliability of sub-threshold designs, which use supply voltage lower than the threshold voltage (V<sub>th</sub>) of transistors to reduce power. The exponential relationship between delay and V<sub>th</sub> significantly jeopardizes their reliability due to process variation induced timing violations. In order to address this problem, this dissertation proposes a novel selective body biasing scheme. In the first work, the selective body biasing problem is formulated as a linearly constrained statistical optimization model, and the adaptive filtering concept is borrowed from the signal processing community to develop an efficient solution. However, since the adaptive filtering algorithm lacks theoretical justification and guaranteed convergence rate, in the second work, a new approach based on semi-infinite programming with incremental hypercubic sampling is proposed, which demonstrates better solution quality with shorter runtime. The second work deals with the security of low power crypto-processors, equipped with Random Dynamic Voltage Scaling (RDVS), in the presence of Correlation Power Analysis (CPA) attacks. This dissertation firstly demonstrates that the resistance of RDVS to CPA can be undermined by lowering power supply voltage. Then, an alarm circuit is proposed to resist this attack. However, the alarm circuit will lead to potential denial-of-service due to noise-triggered false alarms. A non-zero sum game model is then formulated and the Nash Equilibria is analyzed.

#### **ACKNOWLEDGMENTS**

I would like to thank Dr. Yiyu Shi, my advisor and the chairman of my doctoral committee. The present work would not have been completed without his great advice and insightful guidance. It has been a pleasure working in his research group.

I would like to express my sincere gratitude to the remainder of my doctoral committee. Dr. Daryl G. Beetner and I had very fruitful discussion about the reliability of sub-threshold design, and Dr. Minsu Choi gave a lot useful suggestions to the security work in RDVS system. Dr. Jun Fan and Dr. Boping Wu have taken time to review my work and provided useful outside perspectives.

I would like to thank my parents, Jiansheng Geng and Guizhen Yu for their continuous encouragement and support. I thank my husband, Jianming Liu, for his great love, and our sweet little girl, Anya Geng Liu, who gives me a lot fun after the hard work.

# TABLE OF CONTENTS

| 3.3. PROPOSED IHCS ALGORITHM                                                                           | 38   |

|--------------------------------------------------------------------------------------------------------|------|

| 3.4. EXPERIMENTAL RESULTS                                                                              | 46   |

| 3.5. CONCLUSIONS                                                                                       | 51   |

| 4. PART II: ON RANDOM DYNAMIC VOLTAGE SCALING IN CORRELATION POWER ANALYSIS: A GAME-THEORETIC APPROACE | I 52 |

| 4.1. INTRODUCTION                                                                                      | 52   |

| 4.2. PRELIMINARIES                                                                                     | 54   |

| 4.2.1. Cryptographic System and CPA                                                                    | 56   |

| 4.2.2. Design Description.                                                                             | 56   |

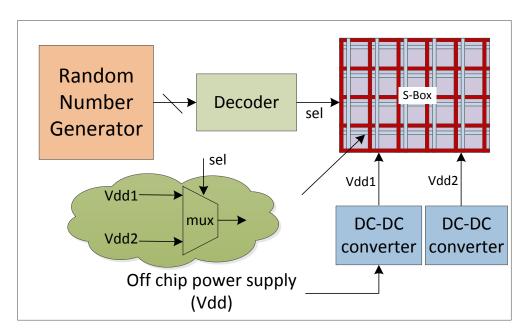

| 4.2.2.1 RDVS System                                                                                    | 57   |

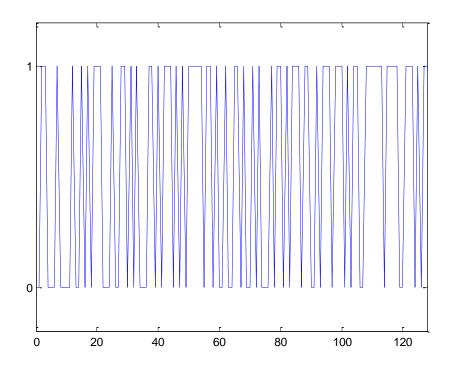

| 4.2.2.2 Random number generator                                                                        | 57   |

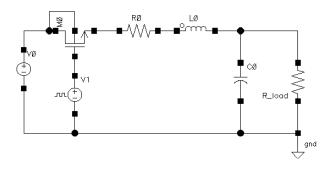

| 4.2.2.3 DC-DC converter.                                                                               | 58   |

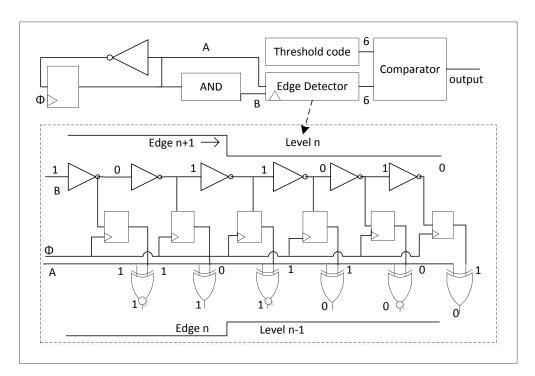

| 4.2.2.4 Power supply voltage monitor.                                                                  | 60   |

| 4.3. GAME MODEL AND ANALYSIS                                                                           | 60   |

| 4.4. NUMERICAL RESULTS                                                                                 | 67   |

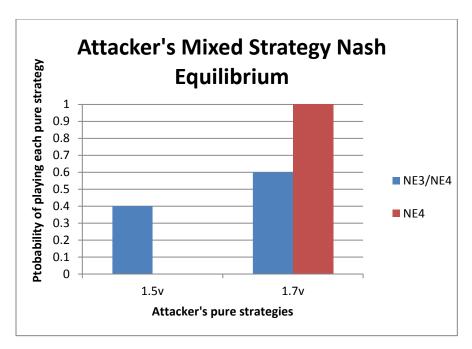

| 4.4.1. Mixed Nash Equilibrium Analysis.                                                                | 69   |

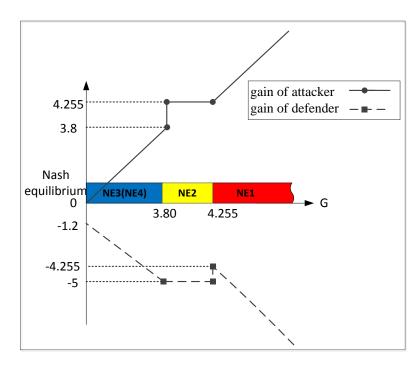

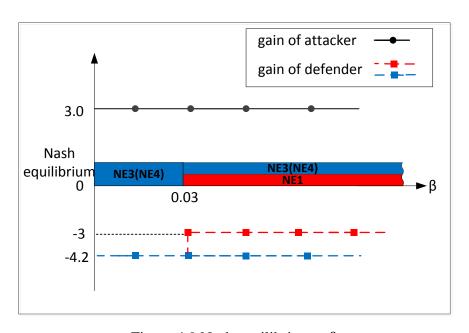

| 4.4.2. Effect of Parameters on Nash Equilibrium                                                        | 70   |

| 4.5. CONCLUSION                                                                                        | 74   |

| 5. SUMMARY AND FUTURE WORK                                                                             | 75   |

| 5.1. SUMMARY OF CONTRIBUTIONS                                                                          | 75   |

| 5.2. FUTURE WORK                                                                                       | 76   |

| BIBLIOGRAPHY                                                                                           | 78   |

| VITA                                                                                                   | 84   |

# LIST OF ILLUSTRATIONS

| Figure                                                                                                                                                                        | Page |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1. Normalized path delay and critical path distribution                                                                                                                     | 7    |

| 2.2. Network of T0.                                                                                                                                                           | 13   |

| 2.3. Adaptive filitering framework overview                                                                                                                                   | 16   |

| 2.4. Network of T0.                                                                                                                                                           | 16   |

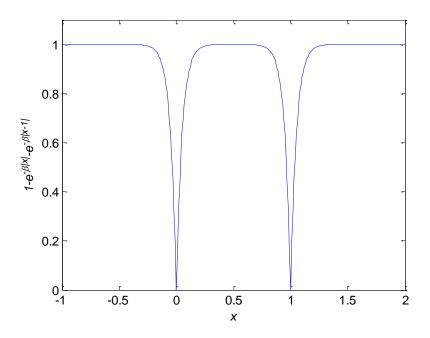

| 2.5 The continuous approximated function of the new 10,1 norm counting both non-zero and non-one entries, which outputs 1 when the input is neither 0 nor 1.                  | 21   |

| 2.6 The plot of the binary attractor, which is the negative gradient direction of new 10,1 norm, imposes an attraction to zero and one on the coefficients near zero and one. | 25   |

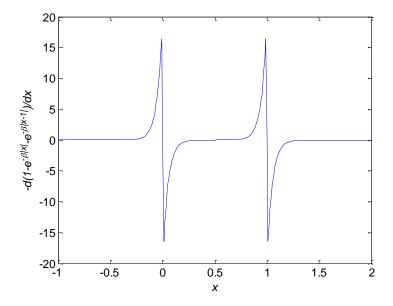

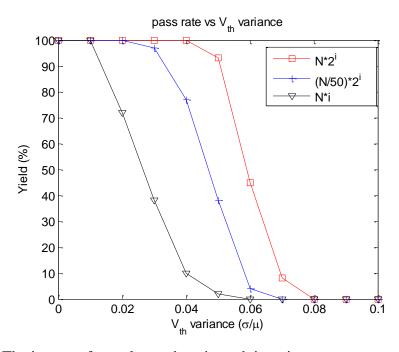

| 2.7 Pass rate v.s. V <sub>th</sub> variance comparison among different methods for T2                                                                                         | 29   |

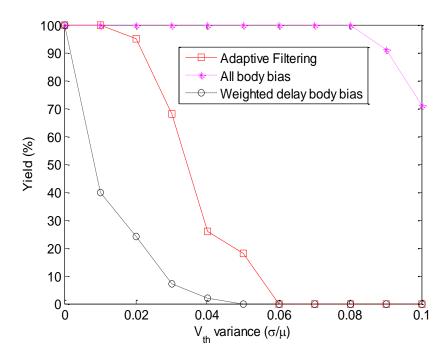

| 2.8 Pass rate and the percentage of gates selected v.s. iteration number for design T2 with 10% V <sub>th</sub> variance                                                      | 29   |

| 2.9 The impact of representative path selection on pass rate at different $V_{th}$ variance for design T2.                                                                    | 31   |

| 2.10 The impact of r on runtime for design T5                                                                                                                                 | 32   |

| 2.11 The impact of r on pass rate for design T5.                                                                                                                              | 32   |

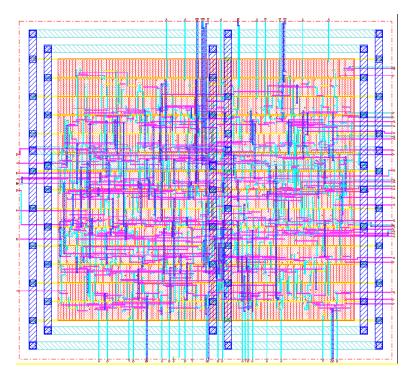

| 2.12 Layout of T2 without body biasing                                                                                                                                        | 33   |

| 2.13 Layout of T2 with body biasing gates selected by APA-BA-PP                                                                                                               | 33   |

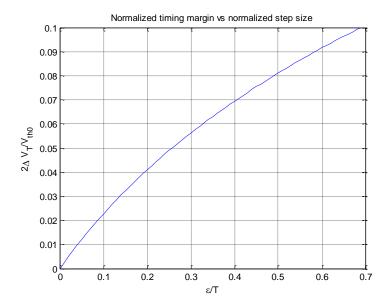

| 3.1 Relation between the step size $2\Delta V_T/V_{th0,\mu}$ and the normalized time margin $\varepsilon/T$                                                                   | · 43 |

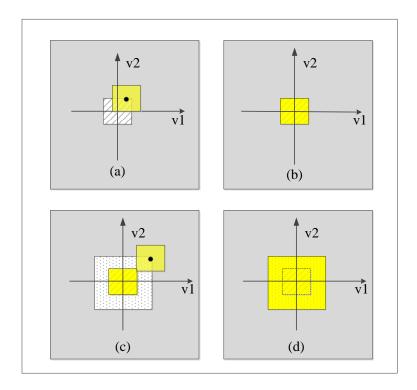

| 3.2 A two-dimension example of proposed IHCS algorithm workflow                                                                                                               | 46   |

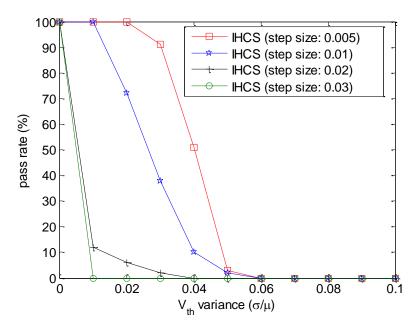

| 3.3 The impact of step size on pass rate at different $V_{th}$ variance for design T2                                                                                         | 49   |

| 3.4 The impact of sample numbers in each iteration on pass rate at different $V_{th}$ variance for design T2.                                                                 | 50   |

| 3.5 Layout of design T2 with body biasing.                                                                                                                                    | 50   |

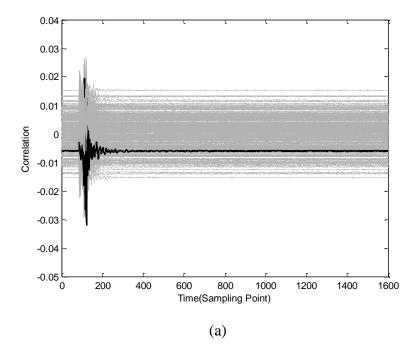

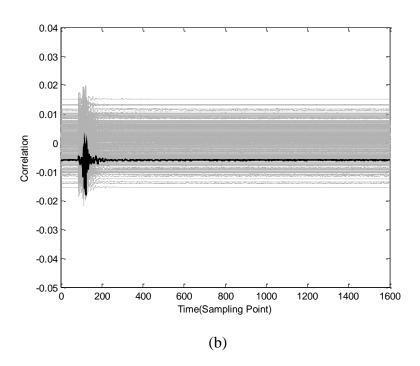

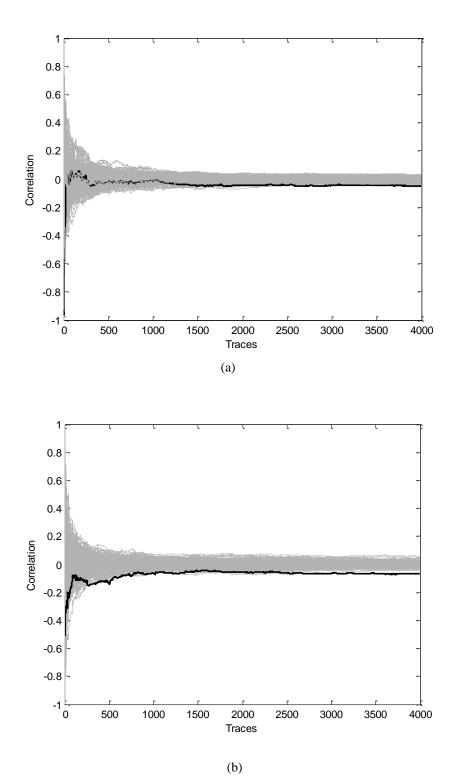

| 4.1 CPA result with Temporal DVS                                                                                                                                              | 55   |

| 4.2 System diagram of RDVS S-Box.                                                                                                                                             | 57   |

| 4.3 Part of the random number generator cycles of LSFR.                                                                                                                       | 58   |

| 4.4 DC-DC converter                                                                                                                                                           | 59   |

| 4.5 Block diagram of the VPM and edge detector                                                                                                                                | 61   |

| 4.6 Number of traces needed for successful CPA attack                                                                                                                         | 62   |

| 4.7 Attacker's mixed strategy Nash equilibrium. | 70 |

|-------------------------------------------------|----|

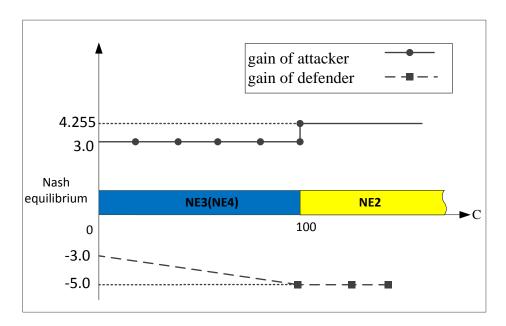

| 4.8 Nash equilibria v.s. G                      | 71 |

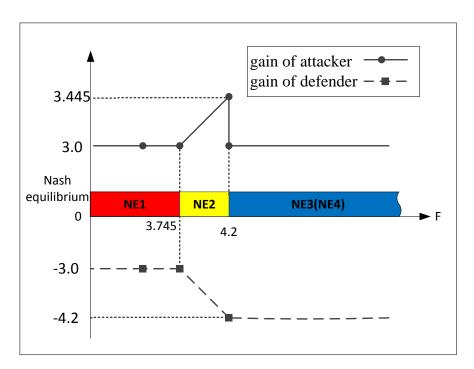

| 4.9 Nash equilibria v.s. β.                     | 71 |

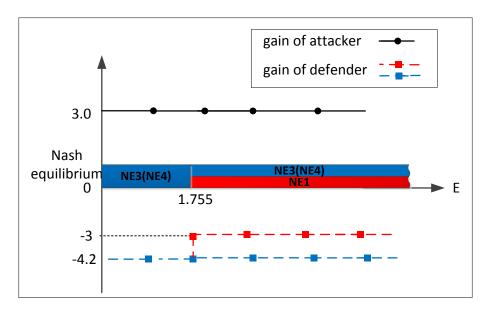

| 4.10 Nash equilibria v.s. E.                    | 72 |

| 4.11 Nash equilibria v.s. F.                    | 73 |

| 4.12 Nash equilibria v.s. C.                    | 73 |

# LIST OF TABLES

| Table                                                                      | Page |

|----------------------------------------------------------------------------|------|

| 2.1 Paths of T0.                                                           | 14   |

| 2.2 Summary of five 65nm sub-threshold designs                             | 27   |

| 2.3 Comparison of pass rate among different approach                       | 28   |

| 2.4 The runtime of SVD, QR and APA-BA-PP v.s. gate number for design T1-T6 | 31   |

| 3.1 Parameters of 65nm library                                             | 39   |

| 3.2 Summary of six 65 nm sub-threshold designs                             | 47   |

| 3.3 Comparison of pass rate among different approach                       | 48   |

| 3.4 The runtime of APA-BA-PP and IHCS for designs T1-T6                    | 48   |

| 4.1 Normal form of the game                                                | 66   |

| 4.2 Rank of secret key in CPA analysis to DVS S-box                        | 68   |

| 4.3 Value of parameters                                                    | 68   |

## **NOMENCLATURE**

Description Symbol **Delay Factor** η  $C_s$ Switching Load Capacitance  $\varphi_{s}$ **Surface Potential**  $V_{dd}$ Supply Voltage **Body Biasing Coefficient** γ  $V_{th}$ Threshold Voltage  $V_{T}$ Thermal Voltage Sub-threshold Swing Parameter ρ  $V_{SB}$ **Body Biasing Voltage** Threshold Voltage for V<sub>SB</sub>=0  $V_{th0}$ Gate Delay without  $V_{th}$  Variation and body biasing t t' Gate Delay with V<sub>th</sub> Variation Gate Delay with V<sub>th</sub> Variation and body biasing t" Matrix with connection information of circuit A T Target Delay of Circuit **Decision Vector** X ζ **Small Positive Number** b Dealy Improvement Vector Gate Power p Gate Power with body biasing  $P_{b}$  $\mathbf{I}_{\mathbf{N}}$ **Unit Vector** Step Size of Adaptive Filtering μ

Lagrange Multiplier

Positive Regularization Parameter

λ

$\delta$

#### 1. INTRODUCTION

With the massive deployment of mobile devices in sensitive areas such as healthcare and defense, hardware reliability and security have become hot research topics in recent years. These two topics, although different in definition, are usually correlated. This dissertation offers an in-depth treatment on enhancing the reliability and security of low power circuits and systems.

## 1.1. RELIABILITY

Both fabrication-time and run-time effects impact the reliability of integrated circuits (ICs). With the shrinking of feature size in complementary metal-oxide semiconductor (CMOS) technology, the fabrication-induced process variation, which may cause timing failure and impact the performance of circuits significantly, poses a major challenge for reliability of modern IC [62][63]. There are two different types of process variation, die-to-die variation and within-die variation. The die-to-die variation, resulting from wafer-to-wafer, impacts all transistors and interconnects on a die equally, and just effects the chip performance like frequency, leakage current etc. [64]. Conversely, the within die variations induces different electrical characteristics to different devices and interconnects within the same die.

Different approaches have been proposed to improve the reliability modern ICs in super-threshold designs, like Statistical Static Timing Analysis (SSTA) [65] and body biasing compensation technology [66], etc. However, there are few works on the subthreshold designs, and this dissertation focuses on the effect of within die variation on sub-threshold designs. In fact, the effect of process variation on timing is extremely serious for sub-threshold design due to the exponential relationship between delay and  $V_{th}$ . Therefore, the first part of this dissertation focuses on solving timing problem caused by process variation in sub-threshold designs.

# 1.2. SECURITY

Mobile phones and computers are already the most common and basic communication tools now, and attacks to phones and computers keep increasing recently.

Considering that the phones and computers are able to access sensitive user data like bank information and photos etc., people are having higher and higher security requirements to these devices. In order to improve the security of electrical devices, both the security of software and hardware should be considered, and this dissertation focuses on the improvement of hardware security.

Side-channel attack (SCA) is a very popular hardware attack method. SCA explores the secret information by measuring the emitted outputs from physical devices, which includes execution timing, power consumptions, electromagnetic leaks, and even thermal/acoustic emanations [60]. Published SCAs include simple power analysis (SPA), differential power analysis (DPA), correlation power analysis (CPA), collision attack [61] and leakage power analysis (LPA), etc. Among them, DPA and CPA are the most popular and effective ones, which have been reviewed by numerous researchers on various crypto-systems [60].

Both DPA and CPA are power analysis attack methods, and the attackers measure the dynamic power consumption, which is dissipated during the transistors switching. The same input plaintext always results in the same power trace with a given key, thus, attackers can aggregate the small deviations between the power traces to identify the correct key. To address this issue, random dynamic voltage scaling (RDVS) has been proposed in the literature, which is demonstrated to be effective against DPA and CPA [48][49]. However, the resistance of RDVS to CPA can be undermined through lowering off-chip power supply voltage, and the second part of this dissertation focuses on addressing this problem in RDVS cryptosystem.

## 1.3. WORK SUMMARY

This dissertation consists of three projects.

The selective body biasing problem for post-silicon tuning in sub-threshold designs is proposed and solved with adaptive filtering algorithm in Section 2, in which, the selective body biasing problem is formulated mathematically as an integer programming problem with a statistical linear inequality constraint. In order to address this problem, the concept of adaptive filtering was borrowed from the signal processing community. A novel algorithm with binary attractors and power penalty was proposed to

efficiently solve it. The experiments were based on a set of industrial designs with a 65 nm sub-threshold library. The pass rate is defined as the percentage of Monte Carlo samples without timing violations out of the 10K samples. Results show that, compared with a seemingly more intuitive approach, this approach can improve the pass rate by 57% on average with similar standby power and the same number of body biasing gates. This approach can reduce the standby power on average by 84%, with a 20% pass rate loss as compared to the approach that biases all of the gates.

Section 3 focuses on developing a more efficient algorithm to solve the proposed selective body biasing problem, which is formulated alternatively as a linear semi-infinite programming (LSIP) problem. In addition, the structure of the problem, associated with the physical meaning of the design, can lead to a novel Incremental Hypercubic Sampling (IHCS) algorithm. The algorithm solves the LSIP problem through a number of finite mixed-integer linear programming, and many nice properties of the algorithm are obtained through rigid mathematical derivations.

Though RDVS technology is a very efficient method to improve the resistance of cryptosystem against SCA, it is demonstrated that the resistance can be undermined by providing lower off-chip power supply voltage in Section 4. In order to address this issue, the following method is proposed in this dissertation. The off-chip power supply voltage will be monitored, and an alarm could be triggered to protect valued information once the power supply voltage is lower than the expected voltage (threshold voltage). However, considering both maintenance cost and the environment noise on power supply voltage, this problem is formulated as a non-zero sum game model, and the attacker and the circuit supplier (defender) are the players of this game. The analysis of the Nash equilibrium in this game shed light on the choice of the optimal threshold voltage, which is based on parameters of cryptosystem including the value of information, denial-of-service cost, etc.

Finally, Section 5 discusses the contribution of this dissertation and suggestions of future works.

# 2. PART 1: SELECTIVE BODY BIASING FOR POST-SILICON TUNING OF SUB-THRESHOLD DESIGNS: AN ADAPTIVE FILTERING

## 2.1. LITERATURE REVIEW

Power consumption has become an important design consideration for modern circuits, which is particularly true for energy constrained applications (e.g., battery-powered systems and wide-area surveillance) [1-4]. Sub-threshold designs (in which transistors work in a weak-inversion region under lower-than-threshold supply voltages) have emerged as a compelling solution for low power circuits and systems. The power consumption of sub-threshold circuits is expected to be within a range of 1pJ/instruction [4].

Despite significant power reductions, sub-threshold designs are subject to several challenges. The most critical challenge faced is related to predictability in the sub-threshold regime, where the  $V_{th}$  variation is the dominant variation source. The threshold variation is typically induced by random dopant fluctuations (RDFs). The placement and number of dopant atoms in the device channel cause random shifts in  $V_{th}$  [3, 4]. The RDF may increase path delays dramatically given the exponential relationship between  $V_{th}$  and the drive current in the sub-threshold designs. Gate delay variations can be as high as 300% of the nominal values [4]. Meanwhile, the  $V_{th}$  variation created by the RDF for each gate is purely random. Thus, the critical paths in different chips of the same design are likely to be completely different after the fabrication is complete. Therefore, obtaining a timing closure at the design time is extremely difficult. The post-silicon or runtime tuning techniques are imperative.

Body biasing is one of the most effective tuning techniques currently available. This technique uses body effect to modulate the  $V_{th}$  of transistors, and thus changes the circuit's power and performance. A total of three different types of body biasing technologies can be used: forward body biasing (FBB), reverse body biasing (RBB), and bidirectional adaptive body biasing (ABB). Forward body biasing is typically used to speed up the circuit during the active mode. RBB is an effective technique that can be used to decrease the leakage power in standby mode. Finally, adaptive body biasing can be adjusted into either FBB or RBB at the cost of control and measurement circuitry [7]. However, many existing works on body biasing assumed super-threshold designs either

explicitly or implicitly [7-11] [27-29], and they cannot be extended directly to the subthreshold regime, primarily as a result of the exponential dependency of delay on the purely random  $V_{th}$  variation. The details are discussed in Section II.

Bo Zhai [4] derived a statistical model of the sub-threshold circuit delay and proposed the reduction of energy consumption by optimizing the pipeline's depth. However, it assumes that path delays are independent random variables with lognormal distributions, and that the maximum of two lognormal random variables is still lognormal. Although the gate delays are independent, the path delays are possibly dependent because different paths may share gates.

Bo Liu, etc. in [6] were the first to examine the possibility of body biasing in subthreshold designs. They suggested that both gate resizing and a fuzzy logic controller could be used to reduce the effect of process variation. However, the additional fuzzy logic controller involves extra dynamic power. In addition, in that approach body biasing is applied to all of the gates. That introduces large power and area overhead.

Nearly all of the body biasing studies conducted [6-11] assumed the presence of multiple body biasing voltage domains. These domains increase not only the routing but also the control complexity, which makes these schemes hard to be employed in large-volume commercial production. Multiple body biasing schemes also suffer from less latch-up immunity, less threshold voltage controllability, more substrate noise vulnerability and less gate oxide reliability. Considering the relative importance of reliability and cost, it is more practical to explore a scheme that uses only one body biasing voltage domain, preferably with binary control decision, i.e., whether a single body biasing voltage should be applied or not.

Towards this end, this dissertation puts forward a novel body biasing scheme for sub-threshold designs which tries to find a number of selective gates for body biasing so that the timing violation caused by random  $V_{th}$  variation is eliminated statistically with minimum standby power overhead. This scheme applies the same FBB voltage to all of the selected transistors so that the design cost can be reduced. The proposed algorithm is an offline algorithm, which selects the set of gates for body biasing at design-time. During post-silicon tuning, the biasing voltage is simply applied to the gates selected.

Simply assuming the worst case for all the gates will not be an option here, as the timing benefit brought by body biasing for a single gate in the sub-threshold regime can barely cancel its own delay increment in the worst-case scenario. Accordingly, for worst-case scenario, all the gates have to be selected as body biasing gates. On the other hand, the probability that all the gates are in the worst-case corner at the same time is extremely low. It is thus meaningful to explore an alternative statistical solution.

The remainder of this section is organized as follows. Both the background and motivation behind this study are summarized in Section 2.2. The timing model and problem formulation are introduced in Section 2.3. Section 2.4 presents the proposed adaptive filtering algorithm. Experimental results are presented in Section 2.5 and concluding remarks are given in Section 2.6.

#### 2.2. BACKGROUND AND MOTIVATION

The biggest challenge in sub-threshold designs is the unpredictability brought by the exponential dependence of delay variation on purely random threshold voltage variations.

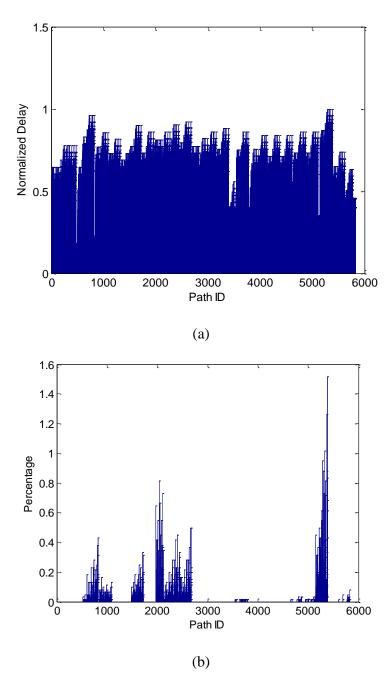

A 65 nm industrial sub-threshold design was used as an example to illustrate this challenge. The normalized path delay, without variation, is given in Figure 2.1 (a). This design was processed through timing optimization, and the critical path ID was 5436. Meanwhile, 10K Monte Carlo simulations were run for  $\sigma/\mu = 10\%$  V<sub>th</sub> variation. The percentage that each path can become critical was calculated as in Figure 2.1 (b).

The highest possibility at which a path can become critical is approximately 1.46%, which means that many other paths may become critical. Accordingly, it is no longer possible to design for timing closure based on a selected number of critical paths, and post-silicon tuning is imperative to address the problem.

A number of researchers have proposed the use of body biasing for post-silicon tuning, but for super-threshold designs [7-11] [27-29]. Most used ABB technology, which can improve the performance of slow modules to fix the timing problem. It can also reduce the leakage power of fast modules. Additional circuitry is, however, needed for either runtime monitoring or voltage adjustments, increasing the area over-head.

Figure 2.1. Normalized path delay and critical path distribution: (a) normalized path delay without  $V_{th}$  variation, and (b) critical path distribution with  $V_{th}$  variation in a 65 nm sub-threshold design

A test chip with an on-chip body biasing generator was implemented to demonstrate the effectiveness of bidirectional ABB [7]. Critical paths were replicated as part of an ABB control circuit to generate one or multiply body biasing voltages. However, it assumes that a small set of critical paths can be identified. This assumption is incorrect for sub-threshold designs, as illustrated in Figure 2.1.

A lookup table based ABB scheme was proposed to control multiple functional blocks on a single chip independently. Different body biasing voltages were stored in a look-up table. Sensors were used to detect the temperature variation, and then suitable body biasing voltages were obtained for corresponding blocks [10]. One disadvantage associated with this method is the significant area overhead of additional circuitry. Another is the large number of delay and leakage measurements required to obtain the final solution. Though the authors tried to decrease the requirement of delay and leakage samples by using a polynomial timing model, it only worked for super-threshold designs and could not be extended to the sub-threshold region.

A joint co-optimization workflow was proposed to minimize the leakage power, under a given delay constraint, at a given yield in [27]. It included design-time gate-level sizing and post-silicon ABB adaptation. A robust adjustable linear program algorithm was given to solve the problem. Extending this solution to a sub-threshold design is difficult, because this optimization problem requires a linearized delay model (which is difficult to obtain in the sub-threshold region). In contrast, for multiple optimal body biasing voltages, additional body biasing voltage generators are required to implement the biasing voltages. This not only further increases the area overhead to the body biasing gate area and routing cost, but also suffers from less latch-up immunity, less threshold voltage controllability, more vulnerable to substrate noise and less gate oxide reliability.

One of the most common problems associated with ABB is the large area overhead when body biasing is provided to all of the gates. Considering multiple body biasing voltages are needed in ABB, almost all the ABB related papers use clustering methods to solve this problem. However, most cluster technologies are based on blocks that utilize the spatial correlation of process parameters. [9] [28] proposed the use of variability-aware technique to cluster gates using distributions and correlations of gate delays. This technique assumes that the relationship between the delay and the variation

source is linear. It also assumes that the variations at different gates are spatially correlated. Neither of these, however, hold true in sub-threshold designs.

Several researchers have tried to provide body biasing to part of gates to decrease area overhead. [8] tried to minimize the standby power by selecting a subset of rows from a row-based standard cell layout. Body biasing was applied to those selected rows that contained the most timing critical gates. The timing constraints, however, were deterministic. This does not fit the strong log-normal random variations in sub-threshold designs.

To sum up, most of the previous papers on body biasing only work for superthreshold. They either assume a small set of critical paths, or utilize a linearized delay model and spatially variation information which do not hold in sub-threshold designs. Meanwhile, there exists huge routing area and standby power overhead for multiple body biasing voltages which prohibits them from being used in practical industrial application.

In order to address the above issues, this paper proposes to only apply one postsilicon body biasing voltage to a limited number of selected gates in order to optimize the standby power overhead. Both the reduced routing area cost and improved reliability are preferable in practice, because only one body biasing voltage is utilized.

#### 2.3. MODELING AND PROBLEM FORMULATION

As mentioned in the introduction section, in order to reduce as much standby power overhead as possible for sub-threshold designs, a minimal set of gates needs to be identified. Thus, the timing violations can be statistically eliminated by providing body biasing to this set. The following is divided into three subsections. The timing model is defined in the first section, and the problem is formulated mathematically in the second. The third subsection contains an example that illustrates this formulation.

**2.3.1. Models and Assumptions.** As will be shown later, a large number of delay samples under the random  $V_{th}$  variation is needed to train the adaptive algorithm to be proposed. The time-consuming Monte Carlo simulation is not a viable option here. An analytic delay model that is less accurate but much more efficient is thus used.

The gate delay is assumed to follow the sub-threshold statistical model [4-5] [12-13]:

$$t_{d} = \frac{1}{2} \eta C_{s} V_{dd} \frac{1}{I_{s0}} e^{-\frac{V_{dd}}{\rho V_{T}}} e^{\frac{V_{th}}{\rho V_{T}}} = \tau e^{\frac{V_{th}}{\rho V_{T}}}, \tag{2.1}$$

where  $\eta$  is the delay factor and  $C_s$  is the switching load capacitance.  $V_{dd}$  is the supply voltage and  $V_{th}$  is the threshold voltage.  $V_T$  is the thermal voltage and  $\rho$  is the sub—threshold swing parameter. The constant  $\tau$  can be obtained by using HSPICE to measure the gate delay at typical  $V_{th}$ .

In addition, the threshold with body biasing can be calculated based on the equation

$$V_{th} = V_{th0} + \gamma (\sqrt{|-2\varphi_s + V_{SB}|} - \sqrt{|-2\varphi_s|}), \tag{2.2}$$

where  $\gamma$  (the body biasing coefficient) and  $\varphi_s$  (the surface potential) are obtained from the technology library [12].  $V_{SB}$  is the body biasing voltage, and  $V_{th0}$  (the threshold voltage for  $V_{SB}=0$ ) is a random variable due to the process variation.

The following assumptions are also made to hold for sub-threshold designs:

- The routing of body biasing nets has a minimal impact on signal nets, and thus, signal net's wire delay remains constant.

- Most of paths in the sub-threshold design can become critical paths. This is due to purely random  $V_{th}$  variation and the exponential relationship between delay and  $V_{th}$  variation. The example given in Section 2.2 (Figure 2.1 (b)) was used to demonstrate this assumption.

- Only one body-biasing domain will be used (i.e., all of the gates selected for body biasing will use the same body voltage, and only one user-specified biasing voltage is available). This assumption is made to significantly reduce the hardware cost associated with body biasing.

The last two assumptions make this work unique. The system to be identified is sparse (considering a very limited number of gates) and binary; there are only two controlling options for each gate: using body biasing or not. This permits the formulation of the problem in a very interesting way as given below.

**2.3.2. Problem Formulation.** Without loss of generality, only combinational logic is considered in the following discussion, because for sequential logic, the combinational logic can be checked between each pair of the registers separately.

For a design with a total of N gates and M paths, a matrix  $\mathbf{A}$  with M rows and N columns is defined to represent the circuit connection in which each row stands for a path and each column stands for a gate. If a gate  $G_n$  appears in path  $P_m$ , the element at m-th row and n-th column of the matrix  $\mathbf{A}$  (i.e.  $\mathbf{A}_{m,n}$ ) will be set to 1, otherwise it is set to 0. Three  $N \times I$  vectors are defined as  $\mathbf{t}$ ,  $\mathbf{t}'$ , and  $\mathbf{t}''$ , in which each element stands for a gate's t, t' and t'' delay in different scenarios:

- t is the gate delay without  $V_{th}$  variation or body biasing,

- t' is the gate delay with only  $V_{th}$  variation,.

- t'' is the gate delay with both  $V_{th}$  variation and body biasing.

Thus, t is the ideal gate delay with no process variation and t' is the gate delay sample with random normal distributed  $V_{th}$  variation that may cause timing violations. In theory, since  $V_{th}$  could deviate from its nominal value in each direction, t' may be either longer or smaller than t. In order to address the possible timing violation, some gates will be selected for body biasing, and their gate delay after body biasing is t''.

With the definitions above, when there are no variations or body biasing, the maximum delay, T for this circuit could be obtained by

$$T = \max(\mathbf{At}). \tag{2.3}$$

The circuit is assumed to have passed the timing sign-off when there is no process variation. Accordingly, this delay T will be taken as the target of the post-silicon body biasing tuning. The delay matrix  $\mathbf{A}_{\mathfrak{t}'}$  ( $M \times N$ ) when there is  $V_{th}$  variation can be calculated as

$$\mathbf{A}_{t'} = \mathbf{A}diag\left\{\mathbf{t}'\right\},\tag{2.4}$$

where  $diag\{\mathbf{t}'\}$  is a  $N \times N$  diagonal matrix with diagonal vector  $\mathbf{t}'$ . Similarly, the delay matrix  $\mathbf{A}_{t''}(M \times N)$  when there are both  $V_{th}$  variation and body biasing is

$$\mathbf{A}_{t''} = \mathbf{A}diag\left\{\mathbf{t}''\right\}. \tag{2.5}$$

Therefore, when body biasing is applied, the delay improvement matrix  $\mathbf{A}_{n}$ .  $(M \times N)$  is

$$\mathbf{A}_{t'} = \mathbf{A}_{t'} - \mathbf{A}_{t''} = \mathbf{A} diag\{\mathbf{t'} - \mathbf{t''}\}. \tag{2.6}$$

The overall required delay improvement vector  $\mathbf{b}$  ( $M \times 1$ ) required to fulfill the target delay is

$$\mathbf{b} = \mathbf{A}\mathbf{t}' - T\mathbf{I}_{M},\tag{2.7}$$

where  $I_M$  is a unit vector  $(M \times 1)$ .

A decision vector  $\mathbf{x}$  ( $N \times 1$ ) is defined, in which each element represents the decision of body biasing control on that gate, i.e., 1 means applying body biasing to that gate and 0 means no body biasing. The proper  $\mathbf{x}$  must be chosen to ensure the overall delay improvement for every path is larger than the required delay improvement, thereby fulfilling the timing constraint,

$$\operatorname{prob}\left\{\mathbf{A}_{tt}\mathbf{x} \geq \mathbf{b}\right\} > 1 - \zeta,\tag{2.8}$$

where  $\zeta$  is a small positive number and  $\mathbf{A}_{n} \mathbf{x} \ge \mathbf{b}$  represents a component-wise inequality (i.e.,  $\mathbf{a}_{m,n} \mathbf{x} \ge b_m, m = 1...M$ , where  $\mathbf{a}_{m,n}$  is the  $m^{th}$  row of  $\mathbf{A}_{tt}$ , and  $b_m$  is the  $m^{th}$  element of  $\mathbf{b}$ ).

When the delay is modelled in a statistical way, this is a robust linear programming problem which could be considered in a statistical framework [15]. However, due to the fact that the delay is log-normal and the paths are not independent with each other, it is not tractable since the joint distribution is very difficult to obtain. Therefore, the approach in [15] cannot be used, and (2.8) can be further converted to a minimization problem using the logarithmic barrier function and solve it using adaptive filtering based algorithm later in Section 2.3.

Additional two  $I \times N$  vectors are defined as  $\mathbf{p}$ , and  $\mathbf{p}_b$ , in which each element stands for  $G_n$  gate's power  $p_n$  without body biasing, and power  $p_{b,n}$  with body biasing. Therefore, for  $\mathbf{x}$ , the total power P will be

$$P = \mathbf{p}_b \mathbf{x} + \mathbf{p} (\mathbf{I}_N - \mathbf{x})$$

=  $\mathbf{p} \mathbf{I}_N + (\mathbf{p}_b - \mathbf{p}) \mathbf{x}$ , (2.9)

where  $\mathbf{I}_N$  is a unit vector  $(N \times 1)$ .

In order to decrease the power, it is proposed to solve the following optimization problem

min

$$(\mathbf{p}_b - \mathbf{p})\mathbf{x}$$

subject to  $\operatorname{prob}\{\mathbf{A}_u, \mathbf{x} \ge \mathbf{b}\} > 1 - \zeta.$  (2.10)

where  $(\mathbf{p}_b - \mathbf{p})\mathbf{x}$  is used as the optimization target. Considering that  $\mathbf{pI}_N$  is constant, it is the same as  $\mathbf{pI}_N + (\mathbf{p}_b - \mathbf{p})\mathbf{x}$ . It should be noted that the integer set in (2.10) is non-convex and the coefficients of the constraint are statistical. Accordingly, the problem is NP hard. A novel adaptive filtering algorithm will be proposed to solve it below. Before that, an example to illustrate the above modeling process is first given in sub-section 2.2.3 as below.

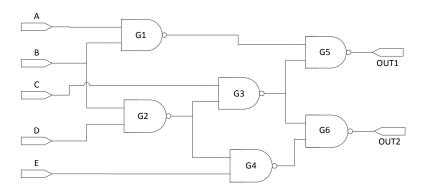

**2.3.3. An Example.** Taking the circuit T0 as an example, there are a total of six 2-input NAND gates identified by number G1 - G6 respectively in network T0, shown in Figure 2.2. There are 11 paths in total. If the same worst-case gate delay is used for any path going through a gate (regardless of the input pin difference), the path number can be further reduced to 7, as shown in Table 2.1.

Figure 2.2. Network of T0.

| Path ID | <b>Gates In The Path</b> |

|---------|--------------------------|

| P1      | G1,G5                    |

| P2      | G2,G3,G5                 |

| Р3      | G2,G3,G6                 |

| P4      | G2,G4,G6                 |

| P5      | G3,G5                    |

| P6      | G3,G6                    |

| P7      | G4,G6                    |

Table 2.1 Paths of T0.

According to TABLE I, the matrix **A** of T0 is

P7

$$\mathbf{A} = \begin{bmatrix} 1 & 0 & 0 & 0 & 1 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 \\ 0 & 1 & 1 & 0 & 0 & 1 \\ 0 & 1 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 0 & 1 & 0 \\ 0 & 0 & 1 & 0 & 0 & 1 \\ 0 & 0 & 0 & 1 & 0 & 1 \end{bmatrix}. \tag{2.11}$$

And the **t** vector  $(6 \times 1)$  can be express as

$$\mathbf{t} = \begin{bmatrix} t_1 & t_2 & t_3 & t_4 & t_5 & t_6 \end{bmatrix}^T, \tag{2.12}$$

where  $t_n$  (n=1,2,...,6) is the gate delay without process variation or body biasing for gate number n. Considering the longest path includes 3 NAND gates, the target delay T is

$$T = \max \left( \mathbf{At} \right)$$

$$= \max \{ t_2 + t_3 + t_5, t_2 + t_3 + t_6, t_2 + t_4 + t_6 \}.$$

(2.13)

The  $\mathbf{t'}$  and  $\mathbf{t''}$  vector could be obtained similarly, in which  $t_n$  and  $t_n$  means the t' delay with process variation only and t" the delay with both process variation and body biasing for gate number n. The delay improvement matrix  $\mathbf{A}_{n'}$  (7×6) of T0 can then be expressed as

$$\begin{bmatrix} t'_{1}-t''_{1} & 0 & 0 & 0 & t'_{5}-t''_{5} & 0 \\ 0 & t'_{2}-t''_{2} & t'_{3}-t''_{3} & 0 & t'_{5}-t''_{5} & 0 \\ 0 & t'_{2}-t''_{2} & t'_{3}-t''_{3} & 0 & 0 & t'_{6}-t''_{6} \\ 0 & t'_{2}-t''_{2} & 0 & t'_{4}-t''_{4} & 0 & t'_{6}-t''_{6} \\ 0 & 0 & t'_{3}-t''_{3} & 0 & t'_{5}-t''_{5} & 0 \\ 0 & 0 & t'_{3}-t''_{3} & 0 & 0 & t'_{7}-t''_{7} \\ 0 & 0 & 0 & t'_{4}-t''_{4} & 0 & t'_{7}-t''_{7} \end{bmatrix}.$$

$$(2.14)$$

Then the required delay improvement vector  $\mathbf{b}$  (7×1) is

$$\mathbf{b} = [t'_1 + t'_5 - T \quad t'_2 + t'_3 + t'_5 - T \quad t'_2 + t'_3 + t'_6 - T t'_2 + t'_4 + t'_6 - T \quad t'_3 + t'_5 - T \quad t'_3 + t'_6 - T \quad t'_4 + t'_6 - T]^T.$$

(2.15)

Note that both t' and t'' for each gate are independent lognormal random variables since the  $V_{th}$  variations follow independent Gaussian distributions.

## 2.4. ALGORITHM

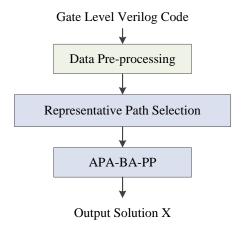

In this section, a novel adaptive filtering based framework is proposed to solve the problem formulated in (2.10), along with its complexity analysis. The framework overview is illustrated in Figure 2.3, which includes three steps: data pre-processing, representative path selection, and APA-BA-PP.

The pre-processing step is based on the gate level Verilog file. Both path and gate information are extracted first. The sub-threshold timing model is then built through HSPICE simulation. The matrices and vectors are prepared last as described in Section 2.2.

A representative path selection stage is employed because the path number can have an exponential relationship with the gate number. It selects a set of representative paths, the number of which does not exceed the number of gates. The details are described in Section 2.3.1.

Finally, the APA-BA-PP algorithm actually selects the gates for body biasing and is the most important part of the framework. The details are described in Section 2.3.2.

Figure 2.3. Adaptive filitering framework overview

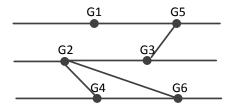

**2.4.1. Representative Path Selection.** This step suppresses the potentially huge path number. A similar approach as described in [14] [26] is employed. To illustrate the idea, circuit T0 is used again as an example. Its 7 paths are expressed in the graph in Figure 2.4. Based on this graph, the delay of path P2:  $G2 \rightarrow G3 \rightarrow G5$  and P4:  $G2 \rightarrow G4 \rightarrow G6$  can be rewritten accurately as the linear combination of the remaining paths. For example, P2 = P5 + P3 - P6, therefore, P2 can be well represented by P5, P3, and P6.

Figure 2.4. Network of T0.

In general, the representative path selection algorithm can find r paths, the linear combination of which can represent the delay of other paths. This will reduce the dimension of  $\mathbf{A}$  to  $r \times N$ , in which  $r = rank(\mathbf{A})$ . Since  $rank(\mathbf{A})$  will not exceed its

column number which in turn is equal to the gate number, the number of representative paths selected will not exceed the gate number. The details are as follows.

To select these representative paths, singular value decomposition (SVD) is performed on matrix  $\bf A$  firstly,

$$\mathbf{A} = \mathbf{U}\Delta\mathbf{V}^T, \tag{2.16}$$

and then apply QR decomposition using column pivoting on  $\mathbf{U}_r$ , which is a sub-matrix formed by the first r columns of  $\mathbf{U}$

$$\mathbf{U}_{r}^{T}\mathbf{P}_{r} = \mathbf{Q}\mathbf{R}.\tag{2.17}$$

The matrices  $\mathbf{Q}$  and  $\mathbf{R}$  are found during the procedure and help identify the output permutation matrix  $\mathbf{P}_r$ . After obtaining  $\mathbf{P}_r$ , to identify the r representative paths,  $\mathbf{P}_r^T \mathbf{A}$  is computed and the sub-matrix formed by the first r rows is taken as  $\mathbf{A}_r$  which in turn corresponds to r paths.

It should be noted that considering the delay is modelled as log-normal distribution, it is not guaranteed that the other non-presentative paths can also satisfy the timing constraints. Even for the representative paths, it is not guaranteed that they can satisfy the delay constraints for every possible sample of the log-normal distributions. However, the use of representative paths is still helpful to conquer the complexity issue and to highlight the essential circuit structure information.

The SVD and QR decomposition in this algorithm are only a one-time cost for each design. Sophisticated algorithms are available for solving these procedures. Furthermore, because matrix **A** is very sparse, the runtime of SVD could be further reduced through exploiting this sparsity. The analysis of the computation complexity will be detailed in Section 2.3.3.

**2.4.2. APA-BA-PP Algorithm.** After reducing **A** to  $\mathbf{A}_r$ , the formulation in (2.10) can be simplified as:

$$min \qquad (\mathbf{p}_b - \mathbf{p})\mathbf{x} \tag{2.18}$$

subject to

$$\operatorname{prob}\left\{\mathbf{A}_{t}, \mathbf{x} \ge \mathbf{b}\right\} > 1 - \zeta,$$

(2.19)

$$\mathbf{x} \in \{0,1\},\ m = 1...r.$$

(2.20)

The formulated problem in (2.18)-(2.20) contains three parts: the inequality timing requirement (2.19), the integer set constraint (2.20) and the minimization target of power cost (2.18). In this subsection, a novel algorithm is proposed to solve this problem: the inequality timing constraint (2.19) is first transformed to a logarithmic barrier optimization target; the power minimization target (2.18) is then added in the cost function as power penalty, and the integer set constraint (2.20) converted as the binary attractor in the cost function. The details will be elaborated below.

At first, in order to handle the inequality constraint, the logarithmic barrier function [14] is utilized to convert the inequality constraint to the following unconstrained optimization

$$min -log \sum_{m=1}^{r} (\mathbf{a}_{m,t}^{T} \mathbf{x} - b_{m}). (2.21)$$

This problem is still challenging as the coefficients are all statistical. Towards this, the adaptive filtering concept could be borrowed from the signal processing community to aid in developing a novel algorithm to solve it.

Considering that the delay improvement matrix  $\mathbf{A}_{u'}$  and the required delay improvement vector  $\mathbf{b}$  are all lognormal distributions, following the way [15] handles the impulse noise, a constraint on the update of the adaptive filter coefficients is added:

min

$$-\log \sum_{m=1}^{r} (\mathbf{a}_{m,n'}^{T}(k)\mathbf{x}(k) - b_{m}(k))$$

subject to  $\|\mathbf{x}(k) - \mathbf{x}(k-1)\|_{2}^{2} \le \mu^{2}$ , (2.22)

where k is the sampling time index for the different random lognormal distributions, and  $\mu$  is a parameter ensuring that  $\mathbf{x}(k)$  and  $\mathbf{x}(k-1)$  does not change dramatically. This can also be viewed as the minimum disturbance constraint. The variable  $\mu$  controls the convergence level of the algorithm and it should be as small as possible. The a-posterior error is

$$\varepsilon_m(k) = b_m(k) - \mathbf{a}_{m,t'}^T(k)\mathbf{x}(k), m = 1...r.$$

(2.23)

Considering that the optimization target in (2.22) is convex, the method of Lagrange multipliers could be used, and the unconstrained cost function of (2.22) can be obtained as

$$J(\mathbf{x}(k)) = -\log \sum_{m=1}^{r} (-\varepsilon_{m}(k)) + \lambda \left[ \|\mathbf{x}(k) - \mathbf{x}(k-1)\|_{2}^{2} - \mu^{2} \right],$$

(2.24)

where  $\lambda$  is the Lagrange multiplier. The derivative of the cost function with respect to the vector  $\mathbf{x}(\mathbf{k})$  is

$$\frac{\partial J(\mathbf{x}(k))}{\partial \mathbf{x}(k)} = \frac{\mathbf{A}_{n}^{T}(k)\mathbf{I}}{\sum_{m=1}^{r} (-\varepsilon_{m}(k))} + 2\lambda \left[\mathbf{x}(k) - \mathbf{x}(k-1)\right].$$

(2.25)

Setting the derivative to zero, (2.26) is gotten as

$$\mathbf{x}(k) = \mathbf{x}(k-1) + \frac{1}{2\lambda} \frac{\mathbf{A}_{tt}^{T}(k)\mathbf{I}}{\sum_{m=1}^{r} \left(-\varepsilon_{m}(k)\right)}.$$

(2.26)

Substituting (2.26) into the constraint (2.22), (2.27) is obtained

$$\frac{1}{2\lambda} = \frac{\mu \sum_{m=1}^{r} \left(-\varepsilon_m(k)\right)}{\sqrt{\mathbf{I}^T \mathbf{A}_{tt'}(k) \mathbf{A}_{tt'}^T(k) \mathbf{I}}}.$$

(2.27)

Substituting (2.27) into (2.26), the constant  $\sum_{m=1}^{r} (-\varepsilon_m(k))$  can be canceled, and the update equation for the **x** vector is:

$$\mathbf{x}(k) = \mathbf{x}(k-1) + \frac{\mu \mathbf{A}_{n'}^{T}(k)\mathbf{I}}{\sqrt{\mathbf{I}^{T} \mathbf{A}_{n'}(k) \mathbf{A}_{n'}^{T}(k)\mathbf{I}}}.$$

(2.28)

In practice, a small positive regularization parameter  $\delta$  is added in the denominator of the second term to prevent the divide-by-zero problem. The update equation is then

$$\mathbf{x}(k) = \mathbf{x}(k-1) + \mu \frac{\mathbf{A}_{tt'}^{T}(k)\mathbf{I}}{\sqrt{\mathbf{I}^{T}\mathbf{A}_{tt'}(k)\mathbf{A}_{tt'}^{T}(k)\mathbf{I} + \delta}}.$$

(2.29)

Next, consider the integer constraint, which is non-convex and NP hard. In order to conquer the NP-hard integer set problem, the idea of the zero-point attractor in [16] is extended to a binary attractor. First, the concept of the  $l_0$  norm, that counts the number of non-zero entries, is introduced.

Considering that  $l_0$  norm is a Non-Polynomial (NP) hard problem, it is generally approximated by a continuous function. A popular approximation [17] is

$$\|\mathbf{x}(k)\|_{0} \approx \sum_{n=0}^{N} \left(1 - e^{-\beta|x_{n}(k)|}\right),$$

(2.30)

where the two sides of (2.30) are strictly equal when the parameter  $\beta$  approaches infinity. Here, it is extended to involve both 0 and 1 as below

$$\|\mathbf{x}(k)\|_{0,1} \approx \sum_{n=0}^{N} \left(1 - e^{-\beta|x_n(k)|} - e^{-\beta|x_n(k)-1|}\right). \tag{2.31}$$

To illustrate how (2.31) works, the function  $1-e^{-\beta|x_n(k)|}-e^{-\beta|x_n(k)-1|}$  is plotted in Figure 2.5. It is clear that it outputs 1 if the input is neither 0 nor 1, which is also the number of non-zero and none-one entries. The motivation behind the binary attractor is that the following target

$$min \quad \|\mathbf{x}(k)\|_{2} \tag{2.32}$$

minimizes the total number of non-zero and non-one entries, which requires the optimal solution to belong to the  $\{0,1\}$  integer space. Considering the power minimization target too, the proposed cost function in (2.21) can be rewritten as

$$-\log \sum_{m=1}^{r} (\mathbf{a}_{m,tt'}^{T}(k)\mathbf{x}(k) - b_{m}(k)) + \varphi(\mathbf{p}_{b} - \mathbf{p})\mathbf{x}(k-1) + \kappa \|\mathbf{x}(k)\|_{0.1},$$

(2.33)

where  $\varphi(\mathbf{p}_b - \mathbf{p})\mathbf{x}(k-1)$  is the power penalty term,  $\varphi > 0$  is a step-size factor of the power penalty, and  $\kappa > 0$  is the strength for binary attractor.

Figure 2.5 The continuous approximated function of the new 10,1 norm counting both non-zero and non-one entries, which outputs 1 when the input is neither 0 nor 1.

Therefore, by minimizing (2.33), the update of the adaptive filtering should be modified to:

$$\mathbf{x}(k) = \mathbf{x}(k-1) + \mu \frac{\mathbf{A}_{u'}^{T}(k)\mathbf{I}}{\sqrt{\mathbf{I}^{T}\mathbf{A}_{u'}(k)\mathbf{A}_{u'}^{T}(k)\mathbf{I} + \delta}}$$

$$-\varphi(\mathbf{p}_{b} - \mathbf{p}) - \kappa \nabla \|\mathbf{x}(k)\|_{0,1},$$

(2.34)

where  $\nabla \|\mathbf{x}(k)\|_{0,1}$  is the gradient with respect to  $\mathbf{x}(k)$ . Note that the current form of (2.34) cannot be implemented in practice, since the term depends on  $\mathbf{x}(k)$ , the exact a priori value of which is not known. Since the additional constraint  $\|\mathbf{x}(k)-\mathbf{x}(k-1)\|_2^2 \leq \mu^2$  is applied in (2.22), it is reasonable to assume  $\|\mathbf{x}(k)\|_{0,1} \approx \|\mathbf{x}(k-1)\|_{0,1}$ ,  $\nabla \|\mathbf{x}(k)\|_{0,1} \approx \nabla \|\mathbf{x}(k-1)\|_{0,1}$ . Therefore, the update of the adaptive filtering should be modified to:

$$\mathbf{x}(k) = \mathbf{x}(k-1) + \mu \frac{\mathbf{A}_{n'}^{T}(k)\mathbf{I}}{\sqrt{\mathbf{I}^{T}\mathbf{A}_{n'}(k)\mathbf{A}_{n'}^{T}(k)\mathbf{I} + \delta}}$$

$$-\varphi(\mathbf{p}_{b} - \mathbf{p}) - \kappa \nabla \|\mathbf{x}(k-1)\|_{0.1}.$$

(2.35)

Substituting (2.31) into (2.35), the final update of the adaptive filtering is:

$$\mathbf{x}(k) = \mathbf{x}(k-1) + \mu \frac{\mathbf{A}_{tt'}^{T}(k)\mathbf{I}}{\sqrt{\mathbf{I}^{T}\mathbf{A}_{tt'}(k)\mathbf{A}_{tt'}^{T}(k)\mathbf{I} + \delta}} - \varphi(\mathbf{p}_{b} - \mathbf{p}) - \kappa \beta \operatorname{sgn}(\mathbf{x}(k-1)) \otimes e^{-\beta|\mathbf{x}(k-1)|} - \kappa \beta \operatorname{sgn}(\mathbf{x}(k-1) - \mathbf{I}) \otimes e^{-\beta|\mathbf{x}(k-1) - \mathbf{I}|},$$

(2.36)

where  $\otimes$  is the component-wise multiplication, **I** is a unit vector, and  $sgn(\cdot)$  is component-wise sign function defined as

$$\operatorname{sgn}(x) = \begin{cases} \frac{x}{|x|}, & x \neq 0; \\ 0, & elsewhere. \end{cases}$$

(2.37)

The algorithm described by (2.36) is denoted as affine projection algorithm with binary attractor and power penalty (APA-BA-PP). The final algorithm is shown in Algorithm 1.

The interpretation of the proposed adaptive algorithm is presented as follows. The adaptive filtering algorithm sequentially updates its filter coefficients along the negative gradient direction for each input  $\mathbf{A}_{n'}(k)$  with log-normal distribution, and can be expressed as

$$\mathbf{x}_{new} = \mathbf{x}_{prev} + \text{gradient correction} + \text{power penalty}$$

+ binary attraction (2.38)

## Algorithm 1: APA-BA-PP

a. Initialization:

$$\delta, \mu_0, \varphi_0, \kappa_0, \eta$$

$$k = 0, \mathbf{x}_0 = \begin{bmatrix} 0,0,...,0 \end{bmatrix}^T$$

- b. Load  $\mathbf{A}, \mathbf{p}, \mathbf{p}_b$  and  $r = rank(\mathbf{A})$

- c. Perform SVD decomposition on  $\mathbf{A} = \mathbf{U}\Delta\mathbf{V}^T$

- d. Perform QR with column pivoting on matrix  $\mathbf{U}_r$  composed by the first r columns of  $\mathbf{U} \cdot \mathbf{U}_r^T \mathbf{P}_r = \mathbf{Q} \mathbf{R}$ , where  $\mathbf{P}_r$  is permutation matrix.

- e. Take  $\mathbf{A}_r$  to be the sub-matrix formed by the first r row of  $\mathbf{P}_r^T \mathbf{A}$ .

- f. Calculate delay  $\mathbf{t}$  and  $T = \max(\mathbf{A}\mathbf{t})$

- g. Loop: while k < K

- h. Calculate random delay t' and t", and

$$\mathbf{A}_{t'} = \mathbf{A}diag\left\{\mathbf{t'}\right\}, \mathbf{A}_{t''} = \mathbf{A}_r diag\left\{\mathbf{t''}\right\}$$

$$\mathbf{A}_{tt'} = \mathbf{A}_{t'} - \mathbf{A}_{tt'} = \mathbf{A}_r diag\left\{\mathbf{t'} - \mathbf{t''}\right\}$$

$$\mathbf{b} = \mathbf{A}_r \mathbf{t'} - T\mathbf{I}$$

i. Calculate step-size

$$\mu_k = \eta \mu_{k-1}, \varphi_k = \eta \varphi_{k-1}, \kappa_k = \eta \kappa_{k-1}$$

i. Update the filter

$$\mathbf{x}_{k} = \mathbf{x}_{k-1} + \mu_{k} \frac{\mathbf{A}_{n}^{T} \mathbf{I}}{\sqrt{\mathbf{I}^{T} \mathbf{A}_{n} \cdot \mathbf{A}_{n}^{T} \mathbf{I} + \delta}}$$

$$-\varphi_{k} (\mathbf{p}_{b} - \mathbf{p}) - \kappa_{k} \beta \operatorname{sgn}(\mathbf{x}_{k-1}) \otimes e^{-\beta |\mathbf{x}_{k-1}|}$$

$$-\kappa_{k} \beta \operatorname{sgn}(\mathbf{x}_{k-1} - \mathbf{I}) \otimes e^{-\beta |\mathbf{x}_{k-1} - \mathbf{I}|}$$

k. k = k + 1

For the first term of gradient correction, according to the definition of matrix  $\mathbf{A}_{tt'}$ ,  $\mathbf{A}_{tt'}^T(k)\mathbf{I}$  is the summation of delay improvement of each gate over all the representative paths at timing index k, and after normalization, this information is used to select the gate. At each iteration, the algorithm adopts the body biasing assignment according to a

single case of variation. Different samples in subsequent iterations may cause the assignment solution to move in different directions, and a move in one iteration may deteriorate the timing yield of previous samples. However the assignment solution will move towards the direction that moderates most of the variations, in the long run. It is reasonable that the gates with accumulated higher overall delay improvement over different samples of the random distribution tend to be critical and this works in a similar way of sorting the gates based on their statistical summations of delay improvement contribution.

The second term, power penalty, is a constant negative vector based on the extra power cost for each gate if it is selected to apply body bias. This power penalty is used to suppress the gates with higher power cost to be selected.

Finally, the third term, binary attraction, imposes an attraction to zero and one on the coefficients near zero and one. To further illustrate the impact of the binary attractor, it is plotted in Figure 2.6. After each iteration, a filter weight will increase a little when it is less than zero, or decrease a little when it is larger than zero. Meanwhile, the filter weight less than one will increase a little and decrease a little if larger than one. Therefore, the binary attractor will attract the non-zero and non-one weights around zero and one. The range of attraction depends on the parameter  $\beta$ . In the adaptation, the gate with lower delay improvement contribution (near zero) in the past indicates a higher possibility of remaining not selected, and the one with higher contribution (near one) tends to remain selected. According to Figure 2.6., the closer it is to zero and one, the greater the attraction intensity is. In conclusion, the binary attractor could smooth and remove the effect of abrupt delay variation due to exponential delay relationship.

According to the above analysis, it is clear that the step-size  $\varphi$  and  $\kappa$  determine the performance of the proposed algorithm. In order to further improve the performance, a simple variable step-size strategy is used in which the step-sizes are reduced by a constant factor [18]. This is because when more and more samples are accumulated in the sorting, the resulting rank should become more stable, therefore the power penalty and binary attractor can gradually be removed. More complicated variable step-size algorithm could be studied in the future [18]. Assume the algorithm runs for K iterations in which K

Figure 2.6 The plot of the binary attractor, which is the negative gradient direction of new 10,1 norm, imposes an attraction to zero and one on the coefficients near zero and one.

is a user-specified number. The larger K is, the more gates will be selected, the impact of K on the pass rate and gate selection will be shown later.

To sum up, the proposed APA-BA-PP algorithm can sort the gates based on their statistical contributions to overall delay improvement considering both the standby power cost and the binary decision rule. In practice, in order to further regulate the right-hand side of (2.36), a sigmoidal function could be applied [25], and the final gate set should be selected according to the final ranking of the solution based on the balance between the pass rate requirement and the tolerance of standby power. However, it should be noted that the rigid convergence analysis of the proposed algorithm is still open for future work. In practice, the algorithm could be enforced to stop after a maximum number of iterations K are achieved (in experiments of this dissertation K = 5000). Experimental results show that such a heuristic can provide solutions with reasonably good quality.

**2.4.3. Complexity Analysis.** This section is concluded with the complexity analysis of this APA-BA-PP algorithm. SVD decomposition is done to path matrix A ( $M \times N$ ), where M is the number of paths and N is the number of gates. This APA-BA-PP algorithm deals with the combinational circuits between registers, similarly to those in the timing analysis. For modern designs with millions of gates, the number of gates would still be in the range of thousands.

For most designs,  $\mathbf{A}$  is usually very sparse. Therefore, this sparse property can be utilized to significantly decrease the runtime of SVD. For example, the randomized SVD [30] [33] runs very fast on large scale sparse matrix. According to reference [30], the complexity of randomized schemes SVD could achieve O(MNlog(r)), where  $\mathbf{r}$  is number of representative paths, which ideally should be the rank of the matrix  $\mathbf{A}$ . For extremely large number of paths, the runtime could be further decreased through using smaller  $\mathbf{r}$  than the real rank of  $\mathbf{A}$  at the cost of slight accuracy loss, as will be shown in the experimental results.

The complexity of QR with column pivoting on matrix  $\mathbf{U}_r$  with size  $M \times r$  is  $O\left((M + rlog_f(r))r^2\right)$ , f > 1 [31], which is also linear w.r.t. the path number. Yet compared with SVD decomposition, it is well known that QR has a much smaller affine. Therefore, the runtime of QR is also acceptable.

Finally, for the proposed APA-BA-PP algorithm, matrix operations are involved with complexity O(Nr) in each iteration. Accordingly, the total complexity is O(KNr), where K is the total iteration number.

#### 2.5. EXPERIMENT RESULTS

The path extraction was implemented in Python and the remaining parts were implemented in C++. Eigen 3.0 library was used for the QR decomposition [18], and redsvd package was used for SVD [19]. Simulations are performed based on five 65 nm industrial sub-threshold designs as listed in Table 2.2, which includes the path number, gate number along with the rank of matrix **A** (the number of representative paths) for each design. The supply voltage is 200 mV, and the body biasing voltage V<sub>BS</sub> is set to 400 mV for PMOS and 400 mV for NMOS. The body biasing voltage is selected so that

when all the gates are biased, 100% pass rate can be achieved for  $V_{th}$  variance less than 8%. All pass rates reported in this section were obtained through 10K Monte Carlo simulations. In each simulation, it works only if all the paths satisfy the target delay, otherwise it fails. The pass rate is the ratio of the number of working simulations to the total number of simulations. The experiments were conducted on a workstation equipped with quad-core 2.4 GHz CPU and 96 GB RAM.

The proposed adaptive algorithm is compared with two intuitive methods. The first one "all body biasing" applies body biasing to all the gates in the design. The second one "weighted delay" selects body biasing gates based on the descending order of the weighted delay of each gate. The weighted delay of a gate is defined as the product of the number of paths going through a gate and its corresponding delay improvement when body biasing is applied. This metric evaluates the overall importance of a gate in timing. For a fair comparison, the same number of gates are selected for the weighted delay method and the proposed adaptive filtering method.

Table 2.2 Summary of five 65nm sub-threshold designs

| Design | Gate<br>number | Path<br>number | Rank |

|--------|----------------|----------------|------|

| T1     | 168            | 75,383         | 122  |

| T2     | 496            | 5830           | 248  |

| Т3     | 546            | 916,719        | 311  |

| T4     | 892            | 729,045        | 460  |

| T5     | 1,269          | 462,140        | 379  |

| Т6     | 3,513          | 685,908        | -    |

The pass rate and standby power are compared among the three methods in the six designs for different  $V_{th}$  variations ( $\sigma/\mu$ ), and the results are shown in Table 2.3. Different  $V_{th}$  variations are used to report meaningful pass rates as the designs are of different sizes. For the adaptive filtering method and the weighted delay method, the percentage of gates selected for body biasing is also reported. The number of iterations used in the adaptive filtering method is between 5,000 and 6,000. According to the results in this table, compared with the all body biasing method which always achieves 100% pass rate ,

the adaptive filtering method reduces the standby power by 86% at the cost of 20% pass rate loss on average. On the other hand, compared with the weighted delay method, the adaptive filtering method increases the pass rate by up to 57% with the similar standby power. Also, the number of gates selected for body biasing only constitutes a small percentage of the total gates, which verifies the sparsity assumption in Section 2.4.

Design T2 is then used to study the relationship between pass rate and  $V_{th}$  variation for the three methods shown in Figure 2.7. The adaptive filtering approach is stopped after 6,000 iterations. 97 out of 496 gates are selected by the adaptive filtering approach and the weighted delay approach. As expected, the proposed adaptive filtering method outperforms the weighted delay method significantly. But it is worse compared with the all body biasing method, which is the cost paid to achieve the significant standby power reduction. Note that the performance difference between APA-BA-PP and "All body bias" can be further reduced by choosing more selected gates as studied later in Figure 2.8.

Table 2.3 Comparison of pass rate among different approach

|        | Pass rate |                     |                   | Standby Power (µW) |                     |                   | Selected Gate<br>Percentage |                              |

|--------|-----------|---------------------|-------------------|--------------------|---------------------|-------------------|-----------------------------|------------------------------|

| Design | σ/μ       | All body<br>biasing | Weighted<br>delay | APA-<br>BA-PP      | All body<br>biasing | Weighted<br>delay | APA-<br>BA-PP               | APA-BA-PP/<br>Weighted delay |

| T1     | 0.04      | 100%                | 0%                | 80%                | 0.35                | 0.09              | 0.10                        | 25.60%                       |

| T2     | 0.03      | 100%                | 8%                | 70%                | 0.86                | 0.17              | 0.15                        | 18.71%                       |

| Т3     | 0.06      | 100%                | 11%               | 78%                | 1.08                | 0.24              | 0.23                        | 19.60%                       |

| T4     | 0.04      | 100%                | 10%               | 96%                | 1.70                | 0.31              | 0.30                        | 17.26%                       |

| T5     | 0.07      | 100%                | 56%               | 84%                | 2.25                | 0.27              | 0.27                        | 10.87%                       |

| Т6     | 0.04      | 100%                | 12%               | 65%                | 6.35                | 1.64              | 1.61                        | 20.00%                       |

Figure 2.7 Pass rate v.s.  $V_{th}$  variance comparison among different methods for T2.

Figure 2.8 Pass rate and the percentage of gates selected v.s. iteration number for design T2 with 10%  $V_{th}$  variance

The same design is used again to demonstrate the relationship between the pass rate/percentage of the total gates selected and the iteration number for the adaptive filtering method. The results are depicted in Figure 2.8 for 10%  $V_{th}$  variance. As mentioned earlier, the selected gate number will increase in each iteration to achieve higher pass rate. This can be clearly observed in the figure. Interestingly, when the iteration number increases over 6,000, a sharp increase in pass rate can be observed. Therefore, it is necessary to try different numbers of iterations, and choose the most cost-efficient size for the target gate set.

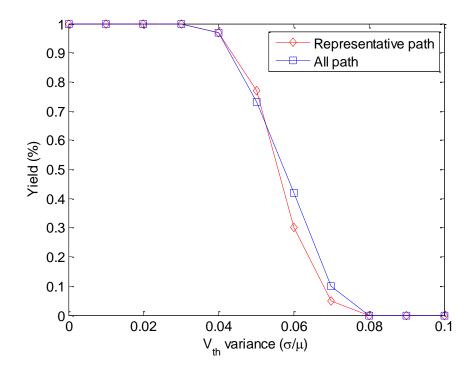

Still using the same design, the impact from the representative path selection step is studied. The pass rates from the adaptive filtering method with and without this step are compared for different  $V_{th}$  variance, and the results are shown in Figure 2.9. From the figure it can be seen that using representative paths can result in slightly lower pass rate for the same  $V_{th}$  variation. But it results in drastic runtime reduction by reducing the exponential path number to linear w.r.t. the gate number.

As mentioned in Section 2.3.3, the proposed algorithm deals with the combinational circuits between registers, and for modern designs with millions of gates, the number of gates will be in the range of thousands. In order to demonstrate the scalability of the proposed scheme, the runtime of SVD, QR and APA-BA-PP are separately reported for different cases in Table 2.4. It verifies that even for the largest design T6 with 3,513 gates, the runtime is still acceptable.

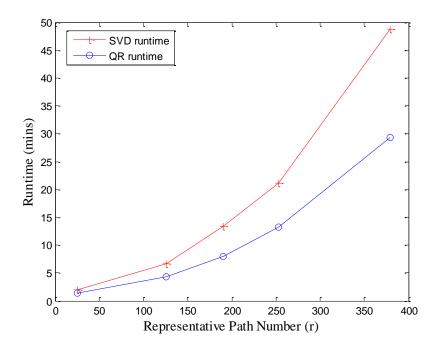

Meanwhile, the impact of the number of representative paths r on the runtime and the quality of the solution is very interesting. T5 is used here as an example, and the runtimes of SVD and QR w.r.t. different r are shown in Figure 2.10. It is clear that the runtime could be significantly decreased with smaller r. On the other hand, the impact of r on pass rate is presented in Figure 2.11, which verifies that the pass rate loss could be slight for r reduced from 379 (full rank) to 127 (10% of the gate number).

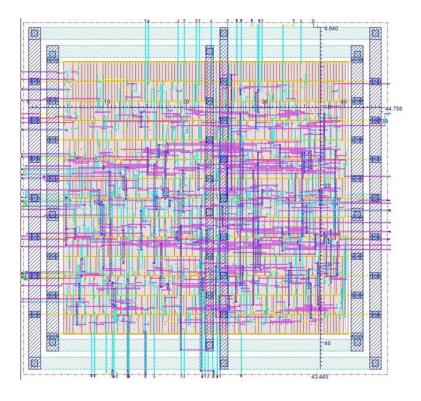

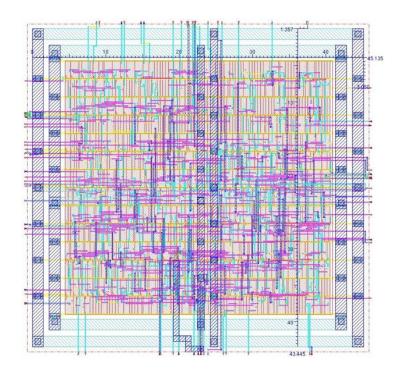

Finally, using Cadence encounter, the core layout of T2 is finished to study the area overhead of the proposed algorithm. The layout without body biasing is given in Figure 2.12, and layout with selected body biasing is compared in Figure 2.13. Based on the proposed APA-BA-PP, 97 out of 496 gates are selected in T2, and the total area overhead is 0.8% compared with the original design without body biasing, which is really

small (the size is labeled in the layout). Considering that the area overhead is from both biasing gates and routing, the wire length overhead is also given to show the contribution of different parts. The total wire length is 3,387 um for the design without body biasing, and 3,447 um for the design with body biasing, a 2% overhead.

Figure 2.9 The impact of representative path selection on pass rate at different  $V_{th}$  variance for design T2.

Table 2.4 The runtime of SVD, QR and APA-BA-PP v.s. gate number for design T1-T6

| Desig |     | Runtime (mins) |        |               |  |  |

|-------|-----|----------------|--------|---------------|--|--|

| n     | r   | SVD            | QR     | APA-BA-<br>PP |  |  |

| T1    | 122 | 0.91           | 0.58   | 7.23          |  |  |

| T2    | 248 | 0.34           | 0.15   | 17.72         |  |  |

| Т3    | 311 | 65.37          | 40.28  | 34.99         |  |  |

| T4    | 460 | 111.72         | 63.35  | 47.01         |  |  |

| T5    | 254 | 21.18          | 13.19  | 75.04         |  |  |

| T6    | 702 | 228.05         | 129.52 | 140.01        |  |  |

Figure 2.10 The impact of r on runtime for design T5.

Figure 2.11 The impact of r on pass rate for design T5.

Figure 2.12 Layout of T2 without body biasing.

Figure 2.13 Layout of T2 with body biasing gates selected by APA-BA-PP

# 2.6. CONCLUSION

In this project, the problem of body biasing for sub-threshold designs with one body biasing voltage domain and one body biasing voltage level is formulated firstly. It is demonstrated that the problem can be modeled as a linearly constrained statistical sparse optimization problem, and the adaptive filtering concept from the signal processing community is borrowed to develop an efficient algorithm to solve it. Experimental results on industrial designs using 65nm sub-threshold library suggest that compared with the weighted delay approach, the proposed approach can improve the pass rate by 57% on average with similar standby power and the same number of body biasing gates. Compared with the approach to bias all the gates, the proposed approach can reduce the standby power by 84% on average with 20% pass rate loss.

# 3. PART I: SELECTIVE BODY BIASING FOR POST-SILICON TUNING OF SUB-THRESHOLD DESIGNS: A SEMI-INFINITE PROGRAMMING APPROACH WITH INCREMENTAL HYPERCUBIC SAMPLING

#### 3.1. BACKGROUND AND MOTIVATION

A practical selective body biasing scheme, with only one body biasing voltage domain to fix the timing violation, is proposed in Section 2. However, though the formulated problem used uncertain constraints with probability distribution, the proposed adaptive algorithm does not explicitly prioritize the constraints with larger probability (i.e., constraints that are more likely to occur). In addition, the power optimization was achieved with power penalty heuristic, and the integer constraints in the formulation were conquered by the binary attractor heuristic. These heuristics lack theoretical justification and have no guaranteed convergence rate. All these issues will significantly degrade the performance of the algorithm.

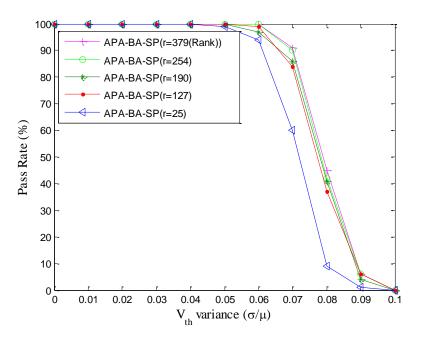

The interesting fact is noticed that the problem of selective body biasing with single biasing voltage domain can be formulated alternatively as a linear semi-infinite programming (LSIP) problem. In addition, the structure of the problem, associated with the physical meaning of the design, can lead to a novel Incremental Hypercubic Sampling (IHCS) algorithm. The algorithm solves the LSIP problem through a number of finite mixed-integer linear programming. Finally, many nice properties of the algorithm is demonstrated through rigid mathematical derivations. Experimental results on industrial designs using 65nm sub-threshold library demonstrate that, compared with the state-of-art adaptive filtering approach in Section 2, the IHCS approach can improve the pass rate by up to 7.3x with a speed up to 4.1x, using the same number of body biasing gates with about the same power consumption.

The remainder of this section is organized as follows: Section 3.2 gives the new LSIP problem formulation. The proposed IHCS algorithm is presented in Section 3.3. The experimental results are demonstrated in Section 3.4 and concluding remarks are given in Section 3.5.

### 3.2. PROBLEM FORMULATION

In this section, an alternative formulation for the problem of selective body biasi-

-ng with only one biasing voltage domain is shown, which will lead to a novel and efficient algorithm.

This section is started by defining the notations necessary for the discussion. Following the delay model in Section 2, all gates are simplified as a simple pull-up or pull-down transistor or appropriate driving strength, and only the worst case falling and rising time is considered. The gate delay is given here again in the following (3.1) for convenience, which is exponential with a single Gaussian distributed random variable  $V_{th}$ .

$$t_{d} = \frac{1}{2} \eta C_{s} V_{dd} \frac{1}{I_{r0}} e^{-\frac{V_{dd}}{\rho V_{T}}} e^{\frac{V_{th}}{\rho V_{T}}} = \tau e^{\frac{V_{th}}{\rho V_{T}}}, \tag{3.1}$$

where  $\eta$  is the delay factor and  $C_s$  is the switching load capacitance.  $V_{dd}$  is the supply voltage and  $V_{th}$  is the threshold voltage.  $V_T$  is the thermal voltage and  $\rho$  is the subthreshold swing parameter. The constant  $\tau$  can be obtained by using HSPICE to measure the gate delay at typical  $V_{th}$ .

The threshold with body biasing can be calculated as

$$V_{th} = V_{th0} + \gamma (\sqrt{|-2\varphi_s + V_{SB}|} - \sqrt{|-2\varphi_s|}), \tag{3.2}$$

where both  $\gamma$  (the body biasing coefficient) and  $\varphi_s$  (the surface potential) are obtained from the technology library [12].  $V_{SB}$  is the body biasing voltage, and  $V_{th0}$  (the threshold voltage for  $V_{SB}=0$ ) is a random variable due to the process variation.