## Missouri University of Science and Technology Scholars' Mine

**Electrical and Computer Engineering Faculty** Research & Creative Works

**Electrical and Computer Engineering**

01 Oct 2000

# DC Power Bus Design with FDTD Modeling Including a Dispersive Media

Xiaoning Ye

Jun Fan

Missouri University of Science and Technology, jfan@mst.edu

Marina Koledintseva

Missouri University of Science and Technology, marinak@mst.edu

James L. Drewniak

Missouri University of Science and Technology, drewniak@mst.edu

Follow this and additional works at: https://scholarsmine.mst.edu/ele\_comeng\_facwork

Part of the Electrical and Computer Engineering Commons

### **Recommended Citation**

X. Ye et al., "DC Power Bus Design with FDTD Modeling Including a Dispersive Media," Proceedings of the IEEE 9th Topical Meeting on Electrical Performance of Electronic Packaging (2000, Scottsdale, AZ), pp. 55-58, Institute of Electrical and Electronics Engineers (IEEE), Oct 2000.

The definitive version is available at https://doi.org/10.1109/EPEP.2000.895492

This Article - Conference proceedings is brought to you for free and open access by Scholars' Mine. It has been accepted for inclusion in Electrical and Computer Engineering Faculty Research & Creative Works by an authorized administrator of Scholars' Mine. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# DC Power Bus Design with FDTD Modeling Including a Dispersive Media

Xiaoning Ye, Jun Fan, Marina Koledintseva, and James L. Drewniak

Electromagnetic Compatibility Laboratory

Department of Electrical and Computer Engineering

University of Missouri - Rolla, Rolla, MO 65409

Phone: 573-3414099 Fax: 573-3414532

Email: xiaoning@ieee.org

## Abstract

DC power-bus modeling in high-speed digital design using the FDTD method is reported herein. The dispersive media is approximated by a Debye model to account for the loss. A wide band frequency response (100 MHz - 5 GHz) is obtained through a single FDTD simulation. Favorable agreement is achieved between the modeled and measured results for a typical DC power-bus structure with multiple SMT decoupling capacitors mounted on the board. The FDTD tool is then applied to investigate the effects of local decoupling on a DC power-bus. The modeled results agree with the results from another modeling tool, the CEMPIE (a circuit extraction approach based on a mixed-potential integral equation formulation) method.

#### I. Introduction

A DC power-bus structure in a multi-layer printed circuit board (PCB), which employs multiple planes as DC power and ground, is a common scenario in high-speed digital circuits. Surface-mount technology (SMT) decoupling capacitors are often placed in proximity to high speed switching devices to mitigate simultaneous switching noise, and reduce the RF noise propagation on the power plane [1], [2]. A reliable power-bus model is a powerful tool that can be integrated into the design procedure to provide design insight, and can be used for developing design guidelines. Several methods have been applied to power bus modeling. The simplest one is the lumped element model, which considers the power bus as a parallel-plane capacitor, and works well at frequencies below board resonance frequencies [1]. For higher frequencies, an appropriate method utilizes the wire-antenna and radial transmission-line modeling to take into account the distributed behavior of the power bus [3]. Traditional full-wave numerical solvers include the finite element method (FEM) [4], and finite-difference-time-domain (FDTD) [5]. Another class of modeling approaches are extracted equivalent-circuit models, in particular, partial element equivalent circuit (PEEC) method [6], and a circuit extraction based on a mixed-potential integral equation (CEMPIE) method [7]. The FDTD and the CEMPIE methods are used in this study.

In Section II, a sample board is modeled using the FDTD method. It is a two-layer structure with a power plane and a ground plane, and sixteen SMT decoupling capacitors are placed uniformly on the board. In the next section, the FDTD method is applied to investigate the effect of local decoupling on DC power-bus design. The modeled results are compared with the results obtained from the CEMPIE method.

#### II. FDTD modeling of a sample board with dispersive media

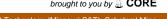

A sample two-layer board was built to mimic a simple two-layer DC power-bus structure as shown in Fig. 1. The board was a 150 mm × 200 mm double-sided PCB, and the dielectric was 1.65-mm (65- mil.) FR4 material. Sixteen decoupling capacitors were uniformly distributed over the board. One end of each decoupling capacitor was soldered directly to the top plane, while the other end was connected to the bottom plane by a short piece of AWG 24 wire. Two test ports were built on the board using semi-rigid coaxial cables. The outer shield of these cables was soldered to the ground plane with a 360-degree connection, and the center conductors were extended through the thickness of the board and soldered to the power plane. A two-port measurement was conducted using an HP 8753D network analyzer. Prior to the measurement, a full-path two-port calibration was performed to remove the effects of the semi-rigid coaxial cables and set the reference plane of the measurement at the ground plane of the test board.

To model this particular board, the traditional frequency-domain methods (MoM, FEM, PEEC, CEMPIE, etc.) are suitable candidates, as well as the FDTD technique. However, for more complex designs of PCB's, e.g., boards with a significant number of SMT capacitors, or boards with segmented power or ground planes, the unknowns for traditional

frequency-domain methods may increase significantly. The FDTD method has the advantage of allowing for more complicated layouts to be modeled without increasing the computational domain or burden. In addition, extending the method to three or more layer structures is straightforward. Another advantage is that broad-band spectrum is often preferred for power-bus design studies, and this can be done with one FDTD simulation.

Fig. 1. Schematics of the test board - side view and top view. All dimensions are in mm.

The sample board was modeled with the FDTD method using a uniform mesh size of  $l \text{ mm} \times l \text{ mm} \times 0.055 \text{ mm} (x, y, z)$ . A sinusoidally modulated Gaussian 50  $\Omega$  voltage source was used in the simulation. The power plane and the ground plane were modeled as perfect electric conductors (PECs) of zero thickness. Eight perfectly matched layers (PML) were placed at each boundary plane of the computational domain, and seven white-space layers were placed between the PML and the test board. Each SMT decoupling capacitor was modeled by an ideal capacitor in series with an effective series resistor. The nominal capacitance used was 9 nF and the resistance was  $130 \text{ m}\Omega$ . These values were determined by an impedance measurement on one SMT component using an HP 4291A impedance/material analyzer. By including the leading wires of the capacitor in the modeling, the parasitic inductance of the SMT capacitor interconnect was taken into account. The algorithm for incorporating a capacitor or a resistor sub-cell in the FDTD modeling can be found in [9].

The dielectric loss has a dominant effect on the Q value of the PCB at higher frequencies, and it was necessary to include it in the numerical modeling. A simple FDTD approach describes the frequency dependence of the media by a constant real value of effective conductivity, which can only model the dielectric loss within a rather narrow frequency range. Multiple simulations are required to generate the results of a wide bandwidth, which is time-consuming. An approach using recursive convolution of constitutive parameters in the time domain and corresponding field components for linear isotropic frequency-dependent complex permittivity was applied [8]. The behavior of the FR-4 material (in the frequency range of 100 MHz to 5 GHz) was approximated using the Debye model [10]:

$$\varepsilon_r = \varepsilon_{\infty} + \frac{\varepsilon_s - \varepsilon_{\infty}}{1 + j\omega\tau_r} - \frac{j\sigma_e}{\omega\varepsilon_0},$$

where  $\mathcal{E}_{\infty}$  is the "optic" dielectric constant,  $\mathcal{E}_s$  is the "static" dielectric constant,  $\mathcal{T}_r$  is the relaxation time, and  $\mathcal{G}_e$  is conductivity of the dielectric. The Debye parameters were determined by setting the loss tangent as 0.022 at 500 MHz and 0.025 at 5 GHz, which yields good agreement of loss tangent between the result from the Debye model and that from measurements for the frequency range of interest.

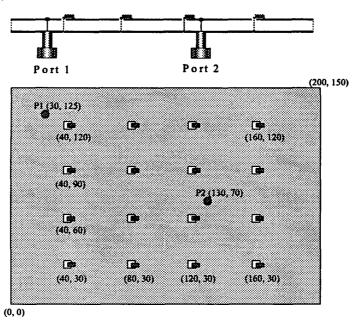

The FDTD method described above was then applied to model the test board shown in Fig. 1. The modeled and measured results ( $|S_{11}|$  and  $|S_{21}|$ ) are shown in Fig. 2. Good agreement was achieved in a wide bandwidth from 100 MHz to 5 GHz by a single FDTD simulation.

Fig. 2. Measured and FDTD modeled  $|S_{11}|$  and  $|S_{21}|$  of the test board.

#### III. Application of the numerical modeling

At high frequencies, the parasitic self inductance of the decoupling capacitor dominates the electrical performance, and the capacitor itself can not provide a low impedance path for bypassing of the noise current on the power-bus. However, a decoupling capacitor placed close to an IC can be tightly coupled to the power pins of the IC as a result of mutual inductance between the vias of the IC and the decoupling capacitor. This mutual inductance works as a current divider over a wide frequency range, and it reduces the power-bus noise magnitude. This effect of locally placed decoupling capacitors was investigated using both FDTD and the CEMPIE method. A more detailed study on quantifying the decoupling capacitor location can be found in [11].

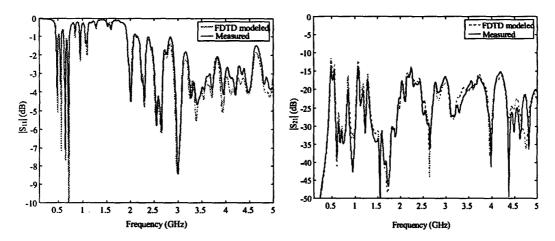

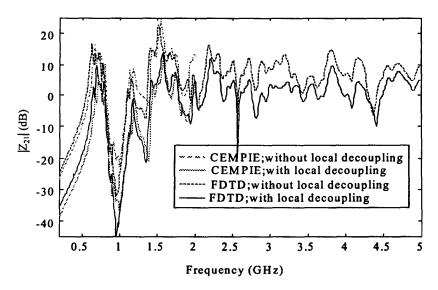

A 152.4 mm  $\times$  228.6 mm (6"  $\times$  9") two-layer PCB with 1.118-mm (44-mil.) FR4 dielectric shown in Fig. 3 was the power-bus structure studied herein. There were 39 global decoupling capacitors with an individual value of  $0.01\mu$ F uniformly distributed on the board. The spacing between any two adjacent capacitors was 25.4 mm (1"). Either zero or four local decoupling capacitors were added adjacent to Port 1. The spacing between these local decoupling capacitors and Port 1 was 2.54 mm (0.1"). The  $|Z_{21}|$  between Port 1 and Port 2 was modeled. A higher  $Z_{21}$  magnitude means that more noise can be transferred from the source to Port 2. Fig. 4 shows both the FDTD and CEMPIE modeled results. The comparison shows that the local decoupling does exhibit lower magnitudes by 5-10 dB than the case without local decoupling over the entire frequency range. The agreements between the CEMPIE results (only calculated up to 2 GHz) and the FDTD results are generally good.

Fig. 3. Modeling structure for local decoupling study.

Fig. 4. Modeled results for the structure shown in Fig. 3 with and without local decoupling capacitors.

#### IV. Conclusions

The FDTD method taking into account the dispersive nature of FR-4 is capable of modeling the wide-band response of a typical DC power bus structure. The dielectric is approximated by a Debye material. Favorable agreement is achieved between the modeled and measured results, demonstrating the effectiveness and application of the FDTD method in DC power-bus design. The FDTD tool applied to investigate the effects of local decoupling in DC power-bus yields good agreement with an independent method, CEMPIE modeled results. The FDTD method is a powerful full-wave power-bus modeling tool. It can be used as an alternative cost-effective approach for hardware trial-and-error measurements. Various what-if scenarios can be easily and rapidly performed using this modeling approach.

#### V. References:

- [1] T. H. Hubing, J. L. Drewniak, T. P. Van Doren, and D. M. Hockanson, "Power bus decoupling on multilayer printed circuit boards," *IEEE Trans. Electromagn. Compat.*, vol. 37, pp. 155-166, May 1995.

- [2] C. R. Paul, "Effectiveness of multiple decoupling capacitors," *IEEE Trans. Electromagn. Compat.*, vol. 34, pp. 130-133, May 1992.

- [3] J. C. Jr. Parker, "Via coupling within parallel rectangular planes", *IEEE Trans. Electromagn. Compat.*, vol. 39, pp. 17-23, Feb. 1997.

- [4] X. D. Cai, G. L. Costache, R. Laroussi, and R. Crawhall, "Numerical extraction of partial inductance of package reference (power/ground) planes," *IEEE int. Symp. Electromagn. Compat.*, pp. 12-15, Atlanta, GA, August 1995.

- [5] W. D. Beckaer and R. Mittra, "FDTD modeling of noise in computer package," *IEEE Multi-Chip Module Conf.*, Santa Clara, CA, pp. 123-127, March 1993.

- [6] A. E. Ruehli, "Equivalent circuit models for three-dimensional multiconductor systems," *IEEE Trans. Microwave Theory Tech.*, vol. 22, pp. 216-221, March 1974.

- [7] H. Shi, J. Fan, J. L. Drewniak, T. H. Hubing, and T. P. Van Doren, "Modeling multilayered PCB power-bus designs using an MPIE based circuit extraction technique," *IEEE int. Symp. Electromagn. Compat.*, pp. 647-651, Denver, CO, August 1998.

- [8] K.Kunz and R.Luebbers, The Finite Difference Time Domain Method for Electromagnetics. CRC Press, Inc., 1993.

- [9] M. Piket-May, A. Taflove, and J. Baron, "FDTD modeling of digital signal propagation in 3-D circuits with passive and active loads", *IEEE Trans. Micro. Theory Tech.*, vol. 42, pp. 1514-1523, August 1994.

- [10] D. D. Pollock, Physical Properties of Materials for Engineers, 2nd edition, CRC press, 1993, Ch 12.

- [11] J. Fan, J. L. Knighten, A. Orlandi, N. W. Smith, and J. L. Drewniak, "Quantifying decoupling capacitor location," IEEE Int. Symp. Electromagn. Compat., Washington DC, August 2000.