## Scholars' Mine

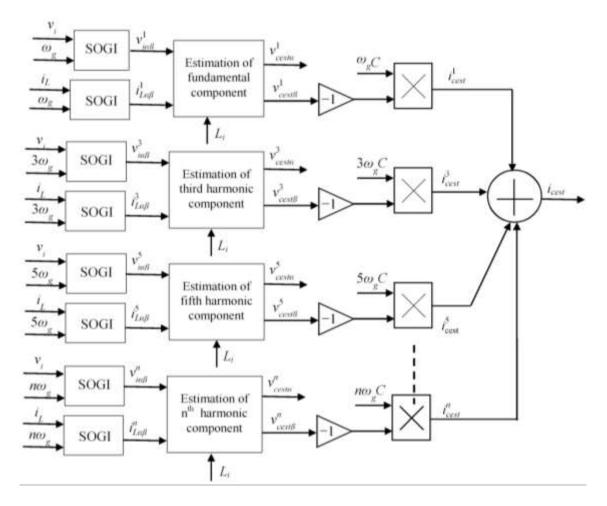

**Doctoral Dissertations**

Student Theses and Dissertations

Fall 2017

# Advanced control architectures for grid connected and standalone converter systems

Subhajyoti Mukherjee

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electrical and Computer Engineering Commons Department: Electrical and Computer Engineering

## **Recommended Citation**

Mukherjee, Subhajyoti, "Advanced control architectures for grid connected and standalone converter systems" (2017). *Doctoral Dissertations*. 2627. https://scholarsmine.mst.edu/doctoral\_dissertations/2627

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# ADVANCED CONTROL ARCHITECTURES FOR GRID CONNECTED AND STANDALONE CONVERTER SYSTEMS

by

## SUBHAJYOTI MUKHERJEE

## A DISSERTATION

Presented to the Faculty of the Graduate School of the

## MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

## **DOCTOR OF PHILOSOPHY**

in

## ELECTRICAL ENGINEERING

2017

Approved by

Mehdi Ferdowsi, Co-Advisor Pourya Shamsi, Co-Advisor Jonathan Kimball Hamidreza Modares Ali Rownaghi

© 2017

## Subhajyoti Mukherjee

All Rights Reserved

## PUBLICATION DISSERTATION OPTION

This dissertation consists of the following five journal articles:

Paper I – Pages 10-47, "Control of a single-phase standalone inverter without an output voltage sensor," *IEEE Trans. Power Electron.*, vol. 32, no. 7, pp. 5601–5612, July. 2017.

Paper II – Pages 48-85, "Grid voltage estimation and current control of singlephase grid-connected converter without grid voltage sensor," *IEEE Trans. Power Electron.*, early access article.

Paper III – Pages 86-110, "Indirect grid current control of an *LCL* filter based grid connected converter," *IEEE Journal Emerging and Selected Topics in Power Electron*. (to be submitted)

Paper IV – Pages 111-141, "Model Reference Adaptive Control Based Estimation of Equivalent Resistance and Reactance in Grid-Connected Inverters," *IEEE Trans. Energy Conv.*, early access article.

Paper V – Pages 142-173, "Power-angle Synchronization with Fault Ride-through Capability for Low Voltage Grids," *IEEE Trans. Energy Conv.* (under review, passed major review phase)

## ABSTRACT

This dissertation proposes new control algorithms dedicated towards improving the reliability, computational burden and stability in grid-connected and stand-alone based power electronic converter systems applicable for ac microgrids.

Two voltage sensorless control architectures, one for stand-alone applications and the other for grid-connected application are established in this thesis. The output voltage of a standalone single-phase inverter is controlled directly by controlling the output filter capacitor current without using a dedicated output voltage sensor. A method to estimate the output filter capacitance is also presented. For the grid connected converter, a novel closed loop estimation is presented to estimate the grid voltage. In addition to the estimation of the grid voltage, the proposed method also generates the unit vectors and frequency information similar to a conventional phase-locked loop structure. The voltage sensorless algorithm is then extended to *LCL* filter based grid connected converters thereby proposing a new indirect method of controlling the grid current.

Furthermore, addressing the stability issues in current-controlled grid tied converters, this dissertation also analyzes the power angle synchronization control of grid-tied bidirectional converters for low voltage grids. The power flow equations for the low voltage grid are analyzed and compensators are designed to ensure the decoupled control of active and reactive power. It is demonstrated that the proposed compensators are immune to grid fluctuations and ensure stable operation controlling the desired power flow to and from the grid.

Detailed plant modeling, controller design, simulation and experimental results are presented for all of the proposed schemes.

## ACKNOWLEDGMENTS

I would like to thank Dr. Mehdi Ferdowsi and Dr. Pourya Shamsi for giving me the opportunity to work in their research group. I would like to acknowledge the financial and technical support they have given to me during my doctoral studies. I would also like to thank Dr. Jonathan W. Kimball, Dr. Hamidreza Modares, and Dr. Ali Rownaghi for being my committee members and for their valuable inputs.

I would like to thank my lab-mates and friends in Missouri University of Science and Technology, Rolla, for providing help and support during the course of my doctoral studies at S&T.

## **TABLE OF CONTENTS**

| Page                                                                                                     |

|----------------------------------------------------------------------------------------------------------|

| PUBLICATION DISSERTATION OPTIONiii                                                                       |

| ABSTRACTiv                                                                                               |

| ACKNOWLEDGMENTS v                                                                                        |

| LIST OF ILLUSTRATIONS x                                                                                  |

| LIST OF TABLES xviii                                                                                     |

| SECTION                                                                                                  |

| 1. INTRODUCTION 1                                                                                        |

| 1.1. REVIEW OF EXISTING CONTROL ARCHITECTURES FOR STAND-<br>ALONE AND GRID-CONNECTED CONVERTER SYSTEMS 1 |

| 1.2. RESEARCH CONTRIBUTION                                                                               |

| PAPER                                                                                                    |

| I. CONTROL OF A SINGLE-PHASE STANDALONE INVERTER WITHOUT AN<br>OUTPUT VOLTAGE SENSOR                     |

| ABSTRACT                                                                                                 |

| 1. INTRODUCTION                                                                                          |

| 2. CONTROL ARCHITECTURE                                                                                  |

| 2.1. Review of the Conventional Voltage Control Method                                                   |

| 2.2. Proposed Control Scheme                                                                             |

| 2.3. Estimation of Output Filter Capacitor                                                               |

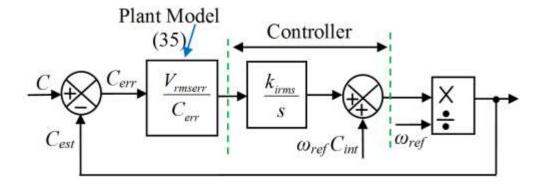

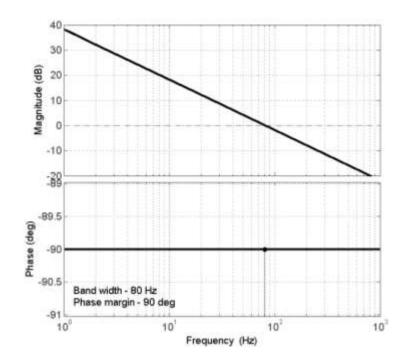

| 3. DESIGN GUIDELINES FOR THE RMS CONTROLLER AND<br>SENSITIVITY ANALYSIS                                                      | 27 |

|------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1. Modeling the RMS Control Loop                                                                                           | 27 |

| 3.2. Parameter Sensitivity Analysis                                                                                          | 29 |

| 4. RESULTS AND DISCUSSIONS                                                                                                   | 33 |

| 4.1. Simulation Studies                                                                                                      | 33 |

| 4.2. Experimental Verification                                                                                               | 35 |

| 5. CONCLUSION                                                                                                                | 42 |

| APPENDIX                                                                                                                     | 42 |

| REFERENCES                                                                                                                   | 45 |

| II. GRID VOLTAGE ESTIMATION AND CURRENT CONTROL OF A SINGLE<br>PHASE GRID CONNECTED CONVERTER WITHOUT GRID VOLTAGE<br>SENSOR | 48 |

| ABSTRACT                                                                                                                     | 48 |

| 1. INTRODUCTION                                                                                                              | 48 |

| 2. CONTROL ARCHITECTURE                                                                                                      | 52 |

| 2.1. Proposed Estimation of the Grid Voltage and Unit Vector Generation<br>Without a Voltage Sensor                          | 52 |

| 2.2. System Modeling and Guidelines for Controller Parameter Selection                                                       | 62 |

| 3. EFFECT OF THE DEAD-TIME AND PARAMETER SENSITIVITY<br>ANALYSIS                                                             | 66 |

| 3.1. Modeling the Dead-Time                                                                                                  | 66 |

| 3.2. Parameter Sensitivity Analysis                                                                                          | 69 |

| 4. RESULTS AND DISCUSSIONS                                                                                                   | 73 |

| 5. CONCLUSION                                                                                                                | 79 |

| APPENDIX                                                                                                                       | 79  |

|--------------------------------------------------------------------------------------------------------------------------------|-----|

| REFERENCES                                                                                                                     | 81  |

| III. INDIRECT GRID CURRENT CONTROL of an <i>LCL</i> BASED GRID<br>CONNECTED CONVERTER                                          | 86  |

| ABSTRACT                                                                                                                       | 86  |

| 1. INTRODUCTION                                                                                                                | 86  |

| 2. CONTROL ARCHITECTURE                                                                                                        | 90  |

| 2.1. Estimation of the Filter Capacitor Voltage                                                                                | 91  |

| 2.2. Estimation of the Filter Capacitor Current and Proposed Control Structure                                                 | 95  |

| 3. RESULTS                                                                                                                     | 100 |

| 4. CONCLUSION                                                                                                                  | 103 |

| APPENDIX                                                                                                                       | 105 |

| REFERENCES                                                                                                                     | 107 |

| IV. MODEL REFERENCE ADAPTIVE CONTROL BASED ESTIMATION OF<br>EQUIVALENT RESISTANCE AND REACTANCE IN GRID-CONNECTED<br>CONVERTER | 111 |

| ABSTRACT                                                                                                                       | 111 |

| 1. INTRODUCTION                                                                                                                | 111 |

| 2. CONTROL ARCHITECTURE                                                                                                        | 115 |

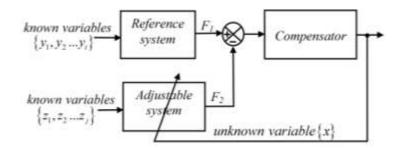

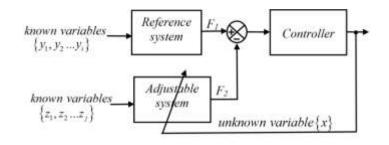

| 2.1. Concept of Model Reference Adaptive Control (MRAC)                                                                        | 115 |

| 2.2. Application of the MRAC Approach for Estimating the Equivalent<br>Resistance and Reactance in a Grid-Connected Inverter   | 115 |

| 3. STABILITY ANALYSIS OF THE PROPOSED MRAC METHOD                                                                              | 120 |

| 3.1. Global Stability                                                                                                          | 120 |

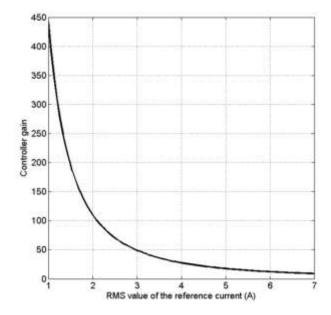

| 3.2. System Modeling and Controller Parameter Selection                                                                   | 122 |

|---------------------------------------------------------------------------------------------------------------------------|-----|

| 4. RESULTS AND DISCUSSIONS                                                                                                | 128 |

| 5. CONCLUSION                                                                                                             | 136 |

| APPENDIX                                                                                                                  | 136 |

| REFERENCES                                                                                                                | 138 |

| V. POWER-ANGLE SYNCHRONIZATION FOR GRID CONNECTED<br>CONVERTER WITH FAULT RIDE-THROUGH CAPABILITY FOR<br>LOW VOLTAGE GRID | 142 |

| ABSTRACT                                                                                                                  | 142 |

| 1. INTRODUCTION                                                                                                           | 142 |

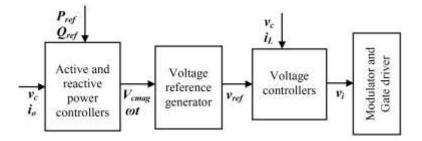

| 2. POWER FLOW EQUATIONS AND SYSTEM MODELING FOR LOW<br>VOLTAGE GRIDS                                                      | 146 |

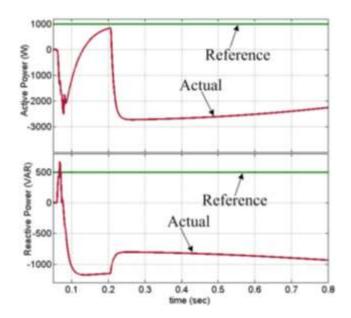

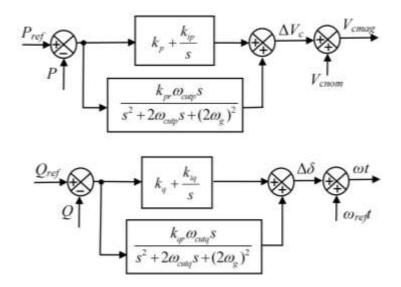

| 3. CONTROLLER STRUCTURE                                                                                                   | 154 |

| 3.1. Active and Reactive Power Compensators                                                                               | 154 |

| 3.2. Start-up Procedure                                                                                                   | 158 |

| 3.3. Voltage Controller                                                                                                   | 160 |

| 4. RESULTS AND DISCUSSIONS                                                                                                | 163 |

| 5. CONCLUSION                                                                                                             | 169 |

| REFERENCES                                                                                                                | 170 |

| SECTION                                                                                                                   |     |

| 2. CONCLUSION                                                                                                             | 174 |

| BIBLIOGRAPHY                                                                                                              | 177 |

| VITA                                                                                                                      | 179 |

## LIST OF ILLUSTRATIONS

| Page |

|------|

|------|

| Figure 1.1. Current controlled architecture for single-phase grid-connected converter                                 |

|-----------------------------------------------------------------------------------------------------------------------|

| Figure 1.2. Direct grid current control architecture for <i>LCL</i> filter based grid-connected converter             |

| Figure 1.3. Multi-loop current control architecture for <i>LCL</i> filter based single-phase grid-connected converter |

| Figure 1.4. Conventional two-loop architecture for single-phase stand-alone converter                                 |

| PAPER I                                                                                                               |

| Figure 1. Circuit of a single-phase standalone inverter                                                               |

| Figure 2. The conventional voltage control structure with capacitor curent feedback                                   |

| Figure 3. Overall block diagram of the proposed control scheme                                                        |

| Figure 4. The current control loop with the corresponding plant                                                       |

| Figure 5. Closed loop equivalent representation of the controller structure                                           |

| Figure 6. Open loop frequency response of the current controller and plant 22                                         |

| Figure 7. Closed loop frequency response of the current controller and plant                                          |

| Figure 8. Frequency response of the output impedance                                                                  |

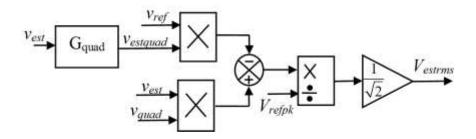

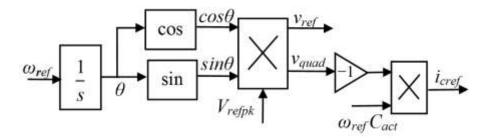

| Figure 9. Computation of the rms value of the estimated filter capacitance                                            |

| Figure 10. Generation of the reference value of the filter capacitor current                                          |

| Figure 11. | Closed loop representation of the RMS control loop for estimating<br>the output filter capacitance                                                             | 8 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 12. | Open loop frequency response of the rms voltage controller and plant                                                                                           | 9 |

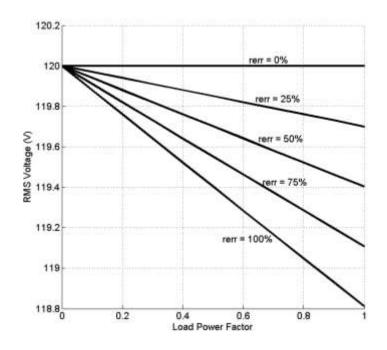

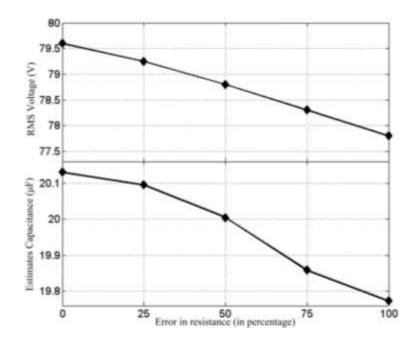

| Figure 13. | Theoretical rms output voltage with error in the assumed resistance<br>at different load power factor                                                          | 1 |

| Figure 14. | Simulated rms output voltage with error in the assumed resistance<br>at different load power factor                                                            | 2 |

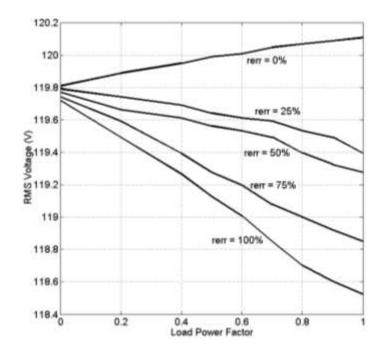

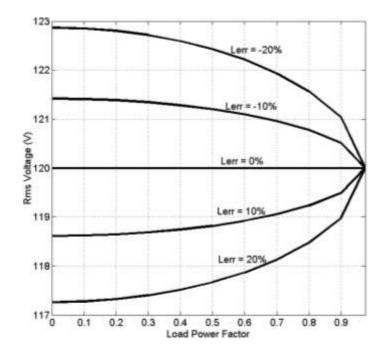

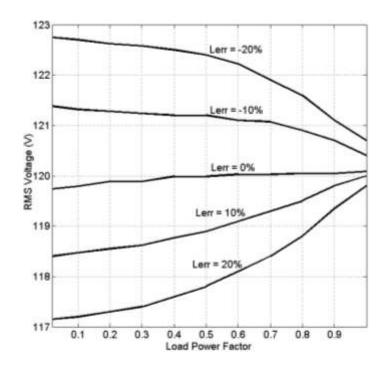

| Figure 15. | Theoretical rms output voltage with error in the assumed inductance<br>at different load power factor                                                          | 2 |

| Figure 16. | Simulated rms output voltage with error in the assumed inductance<br>at different load power factor                                                            | 3 |

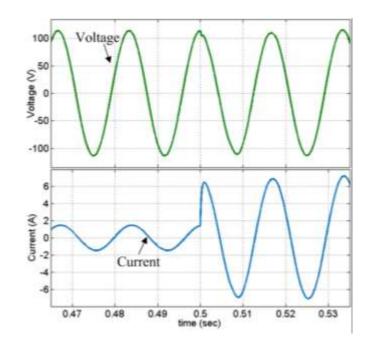

| Figure 17. | Simulated voltage and load current waveforms during change<br>in linear load                                                                                   | 4 |

| Figure 18. | Simulated voltage and load current waveforms during change<br>in nonlinear load                                                                                | 4 |

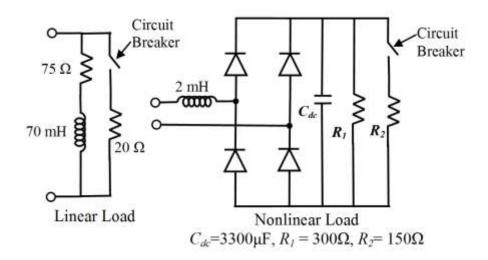

| Figure 19. | Configuration of the linear and nonlinear loads used for the experimental study                                                                                | 5 |

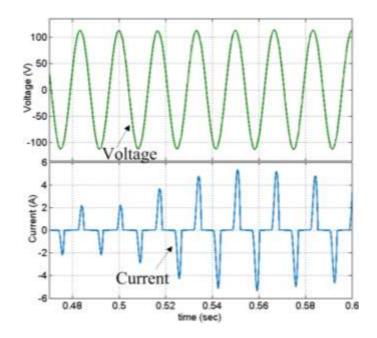

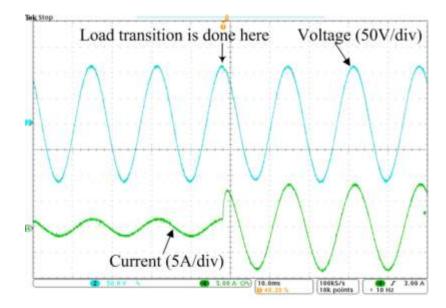

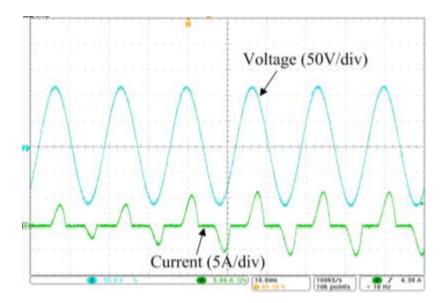

| Figure 20. | Output voltage and load current waveforms during change in<br>linear load                                                                                      | 7 |

| Figure 21. | Output voltage and load current waveforms during change in nonlinear load                                                                                      | 7 |

| Figure 22. | Output voltage under nonlinear load with proposed control scheme (top) and conventional voltage control scheme (bottom)                                        | 8 |

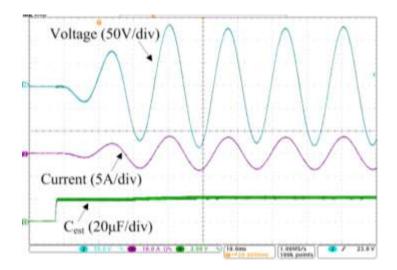

| Figure 23. | Output voltage, load current and estimated filter capacitance<br>during startup                                                                                | 8 |

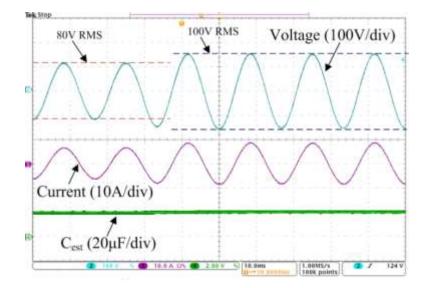

| Figure 24. | Output voltage, load current and estimated filter capacitance<br>during a change in reference from 80 V rms to 100 V rms                                       | 9 |

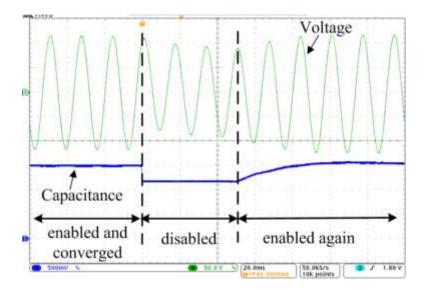

| Figure 25. | Output voltage and estimated filter capacitance with rms controller disabled for 3 cycles and enabled again (Voltage : 50 V/div, Capacitor : $6.67 \mu$ F/div) | 9 |

| Figure 26. The actual rms voltage and estimated capacitance for different $r_{err}$ (%) at unity power factor operation.                                       | 41 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 27. The actual rms voltage and estimated capacitance for different $L_{err}$ (%) at under highly inductive load (load power factor 0.1)                 | 41 |

| PAPER II                                                                                                                                                       |    |

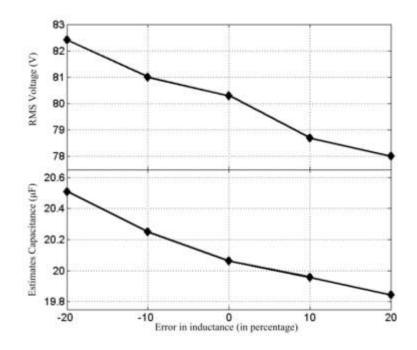

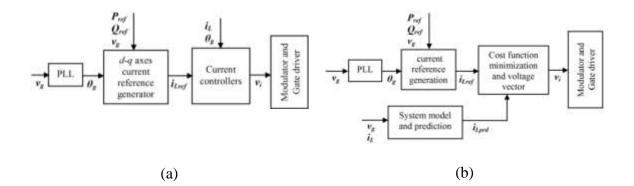

| Figure 1. Control structure for (a) current controlled VSC,<br>(b) VSC controlled by MPC                                                                       | 49 |

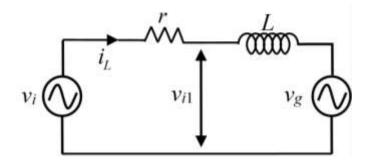

| Figure 2. A single-phase grid connected inverter                                                                                                               | 53 |

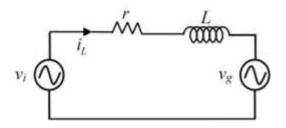

| Figure 3. Single line equivalent diagram of the circuit in Figure 1                                                                                            | 53 |

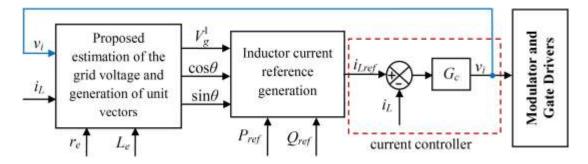

| Figure 4. Overall control block diagram                                                                                                                        | 53 |

| Figure 5. Basic structure of an MRAC system                                                                                                                    | 54 |

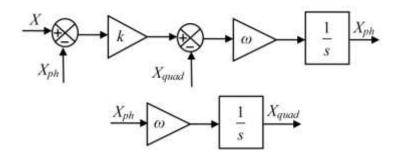

| Figure 6. The SOGI structure                                                                                                                                   | 55 |

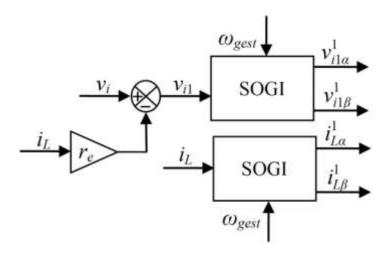

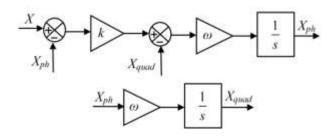

| Figure 7. Generation of the in-phase ( $\alpha$ ) and quadrature ( $\beta$ ) components                                                                        | 56 |

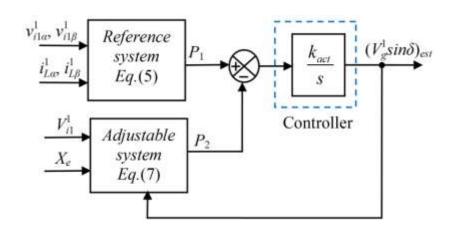

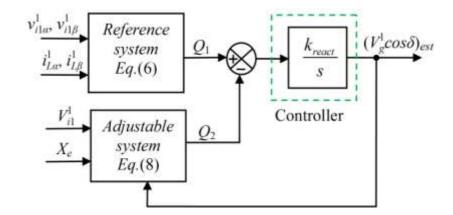

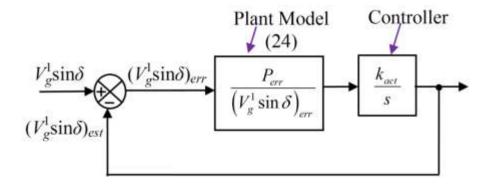

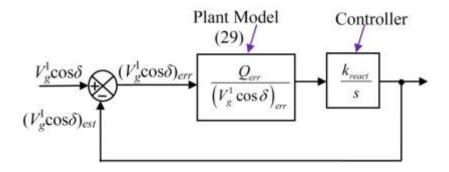

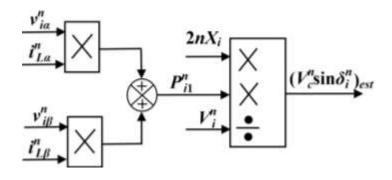

| Figure 8. MRAC structure to estimate $V_g^1 \sin \delta$                                                                                                       | 57 |

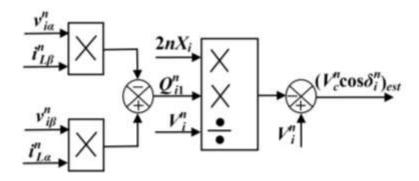

| Figure 9. MRAC structure to estimate $V_g^1 \cos \delta$                                                                                                       | 57 |

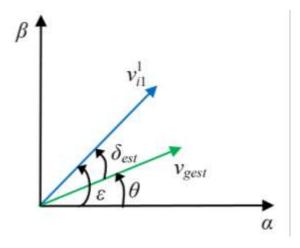

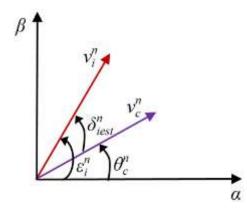

| Figure 10. Representation of the different voltage vectors in the $\alpha$ - $\beta$ frame of reference                                                        | 59 |

| Figure 11. Loop gain of the current controller and plant                                                                                                       | 62 |

| Figure 12. Closed loop representation of the MRAC structure<br>for estimating $V_g^1 \sin \delta$                                                              | 64 |

| Figure 13. Closed loop representation of the MRAC structure<br>for estimating $V_g^1 \cos \delta$                                                              | 66 |

| Figure 14. Open loop frequency response of the controller and plant estimating $V_g^1 \sin \delta$                                                             | 66 |

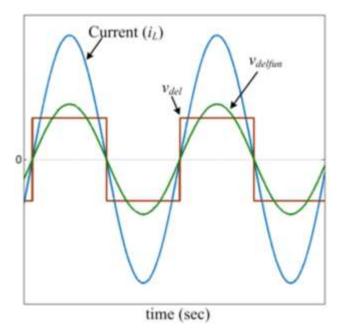

| Figure 15. Qualitative representation of the inductor current $(i_L)$ , voltage drop due to dead time $(v_{del})$ and its fundamental component $(v_{delfun})$ | 68 |

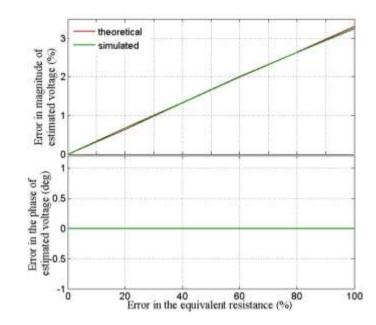

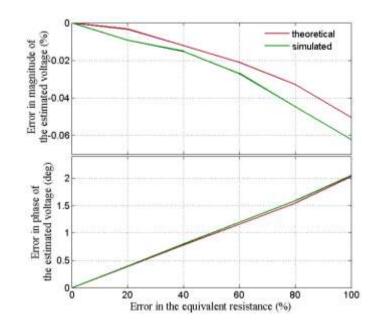

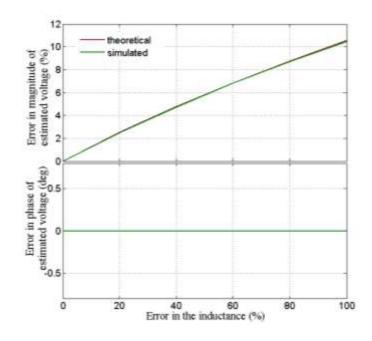

| Figure 16. | Error in the magnitude and phase of the estimated voltage with<br>variation in the resistance when supplying rated active power                                               | 71 |

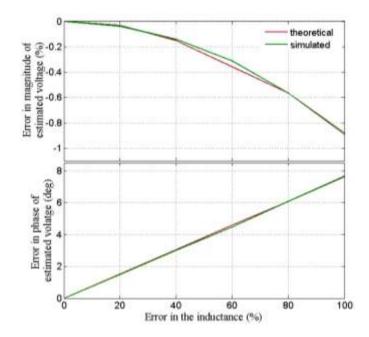

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 17. | Error in the magnitude and phase of the estimated voltage with variation in the inductance when supplying rated active power                                                  | 71 |

| Figure 18. | Error in the magnitude and phase of the estimated voltage with variation in the resistance when supplying rated reactive power                                                | 72 |

| Figure 19. | Error in the magnitude and phase of the estimated voltage with<br>variation in the inductance when supplying rated reactive power                                             | 72 |

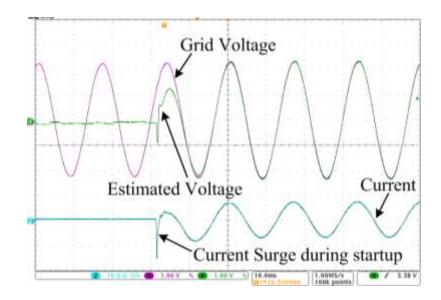

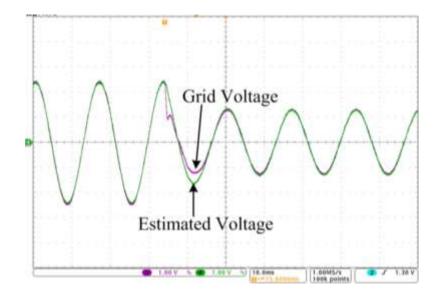

| Figure 20. | The estimated voltage during startup (Voltage scale: 50V/div)                                                                                                                 | 74 |

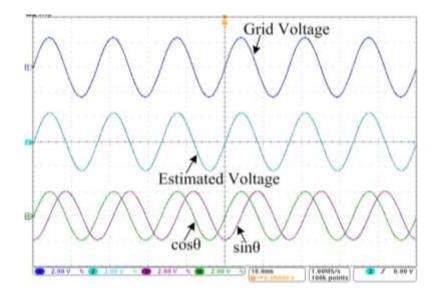

| Figure 21. | Estimated voltage and unit vectors under pure sinusoidal grid voltage (Voltage scale: 100V/div)                                                                               | 74 |

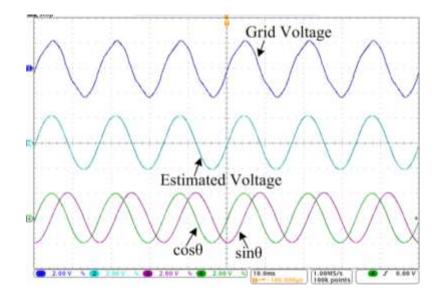

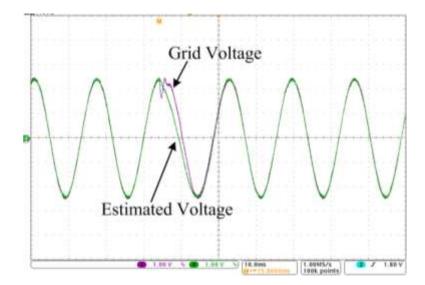

| Figure 22. | Estimated voltage and unit vectors under highly distorted grid voltage (Voltage scale: 100V/div)                                                                              | 75 |

| Figure 23. | The estimated voltage during a decrease in the grid voltage by 50% (Voltage scale: 50V/div)                                                                                   | 75 |

| Figure 24. | The estimated voltage during a change in the phase of grid voltage by 45 degrees (Voltage scale: 50V/div)                                                                     | 76 |

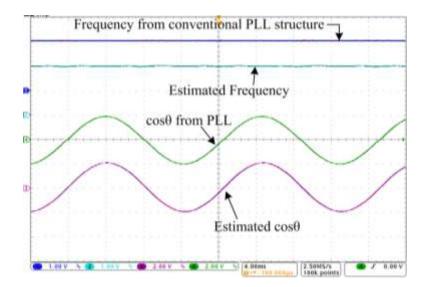

| Figure 25. | Comparison of the estimated frequency from the proposed<br>scheme with the frequency generated from SOGI PLL<br>structure. (Freq scale: 30 Hz/div)                            | 76 |

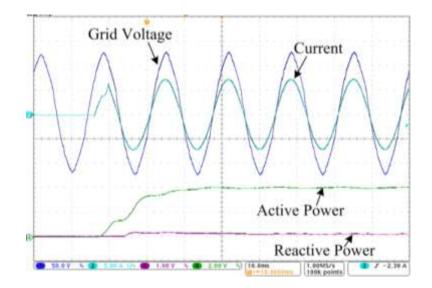

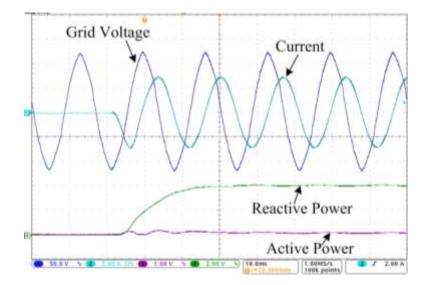

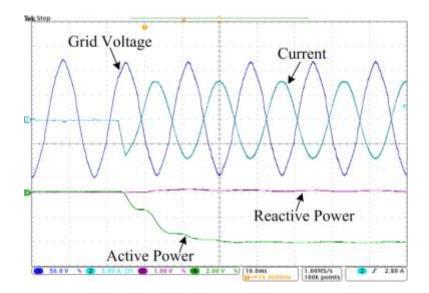

| Figure 26. | Grid voltage, current, active and reactive power when<br>delivering rated active power (Active Power: 200W/div,<br>Reactive Power: 200VAR/div).                               | 77 |

| Figure 27. | Grid voltage, current, active and reactive power when<br>delivering rated reactive power (Active Power: 200W/div,<br>Reactive Power: 200VAR/div)                              | 78 |

| Figure 28. | Grid voltage, current, active and reactive power when<br>delivering rated active power in rectifier mode of<br>operation (Active Power: 200W/div, Reactive Power: 200VAR/div) | 78 |

| rigule 20. | delivering rated active power in rectifier mode of                                                                                                                            | 78 |

## PAPER III

| Figure 1. | A single-phase grid connected inverter with <i>LCL</i> filter                                                                                                                           | 88       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

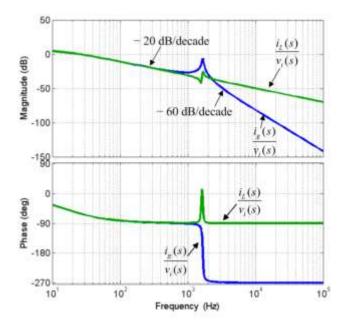

| Figure 2. | The frequency response of $\frac{i_L(s)}{v_i(s)}$ and $\frac{i_g(s)}{v_i(s)}$                                                                                                           | 88       |

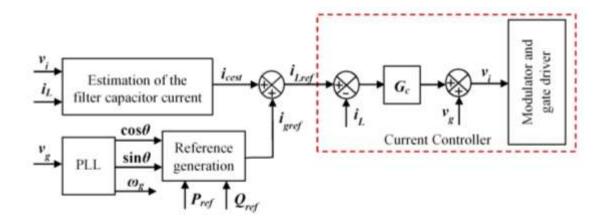

| Figure 3. | Overall block diagram of the proposed control scheme                                                                                                                                    | 90       |

| Figure 4. | Equivalent circuit representation from the converter bridge to the filter capacitor of the circuit in Figure 1                                                                          | 91       |

| Figure 5. | Proposed closed loop estimation structure to estimate $V_c^n \sin \delta_{in}$                                                                                                          | 92       |

| Figure 6. | Proposed closed loop estimation structure to estimate $V_c^n \cos \delta_{in}$                                                                                                          | 93       |

| Figure 7. | Representation of the different voltage vector in the $\beta$ frame of reference                                                                                                        | α-<br>94 |

| Figure 8. | Estimation of the filter capacitor current                                                                                                                                              | 96       |

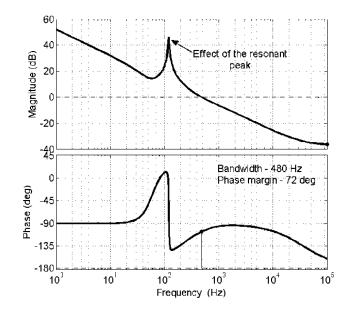

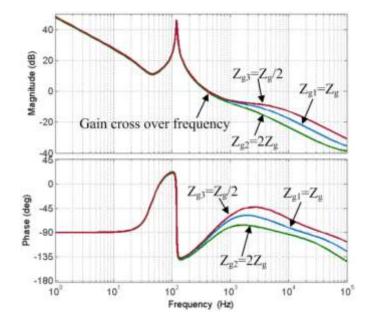

| Figure 9. | Loop gain plot of the current controller and plant                                                                                                                                      | 99       |

| Figure 10 | ). Frequency response showing the effect of the filter capacitor current on the grid current                                                                                            | 99       |

| Figure 11 | . Frequency response of the output admittance                                                                                                                                           | 100      |

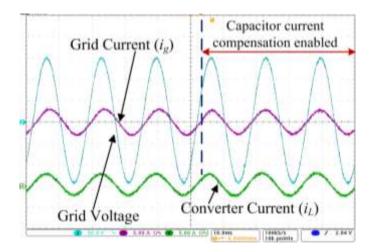

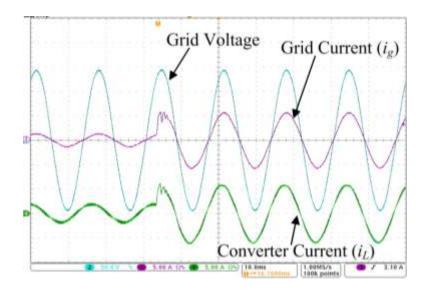

| Figure 12 | 2. Grid voltage, grid current and converter current with and<br>without the proposed capacitor current compensation<br>under normal grid conditions                                     | 102      |

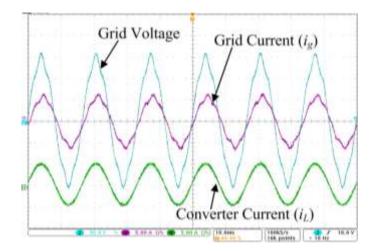

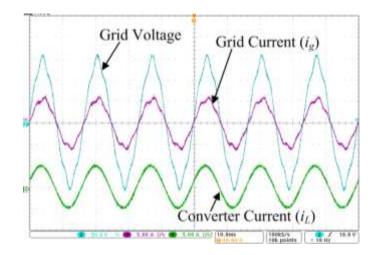

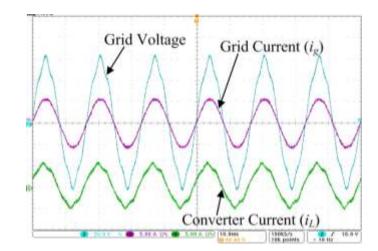

| Figure 13 | 3. Grid voltage, grid current and converter current without compensation of the capacitor current under distorted grid conditions                                                       | 102      |

| Figure 14 | <ol> <li>Grid voltage, grid current and converter current with<br/>proposed compensation of the capacitor current<br/>(only the fundamental) under distorted grid conditions</li> </ol> | 103      |

| Figure 15 | 5. Grid voltage, grid current and converter current with<br>proposed compensation of the fundamental and harmonic<br>capacitor current under distorted grid conditions                  | 103      |

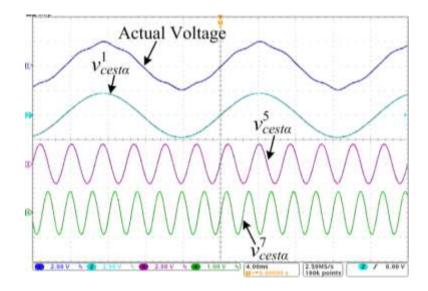

| Figure 16. The actual capacitor voltage, estimated fundamental $(v_{cesta}^1)$ ,<br>fifth harmonic $(v_{cesta}^5)$ and seventh harmonic $(v_{cesta}^7)$ components                           | 104 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

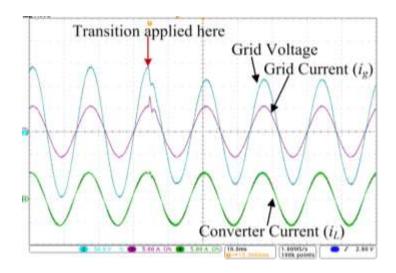

| Figure 17. Grid voltage, grid current and converter current during a transition from 0.25 p.u to 1 p.u of active power                                                                       | 104 |

| Figure 18. Grid voltage, grid current and converter current during a transition of 20% in the grid voltage                                                                                   | 105 |

| PAPER IV                                                                                                                                                                                     |     |

| Figure 1. Control structure for of a grid-tied inverter using (a) current controlled architecture and (b) MPC                                                                                | 112 |

| Figure 2. Basic structure of an MRAC system                                                                                                                                                  | 114 |

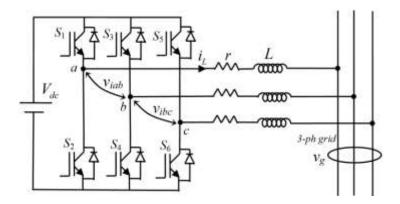

| Figure 3. A 3-phase grid connected inverter                                                                                                                                                  | 114 |

| Figure 4. Per-phase equivalent circuit of the grid connected inverter in Figure 3                                                                                                            | 114 |

| Figure 5. The SOGI structure                                                                                                                                                                 | 117 |

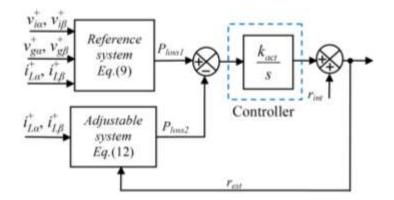

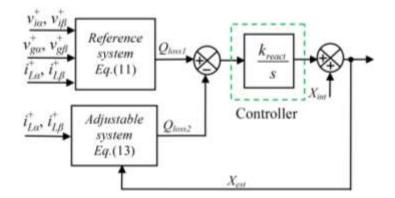

| Figure 6. MRAC structure to estimate the equivalent resistance                                                                                                                               | 117 |

| Figure 7. MRAC structure to estimate the equivalent reactance                                                                                                                                | 118 |

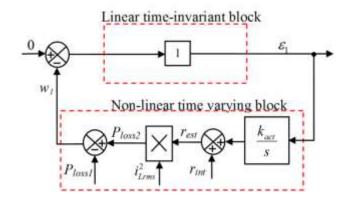

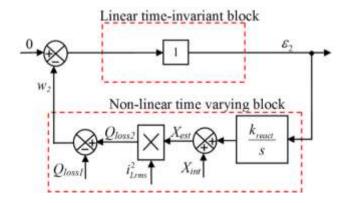

| Figure 8. Equivalent structure of the MRAS in Figure 6                                                                                                                                       | 122 |

| Figure 9. Equivalent structure of the MRAS in Figure 7                                                                                                                                       | 122 |

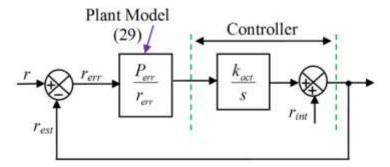

| Figure 10. Closed loop representation of the MRAS for estimating the resistance                                                                                                              | 124 |

| Figure 11. Closed loop representation of the MRAS for<br>estimating the inductive impedance                                                                                                  | 125 |

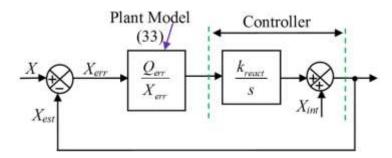

| Figure 12. Frequency response of the controller and plant estimating the resistance                                                                                                          | 126 |

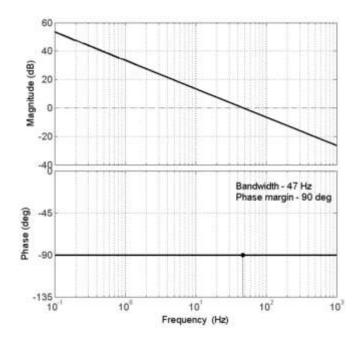

| Figure 13. Frequency response of the controller and plant estimating<br>the resistance delivering half the rated power with and<br>without the adaptive change in controller gain as in (34) | 127 |

| Figure 14. Variation in the controller gain with change in the reference current                                                                                                             | 128 |

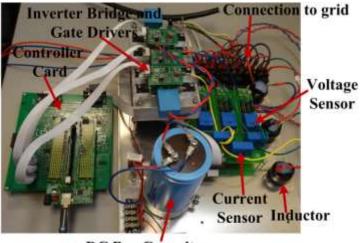

| Figure 15. Picture of the hardware setup                                                                                                                                                                                                                                                    | .30 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

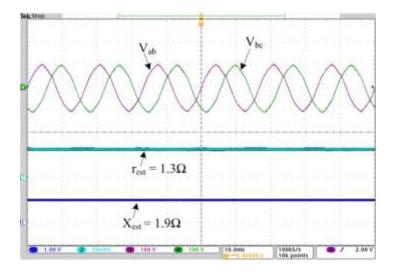

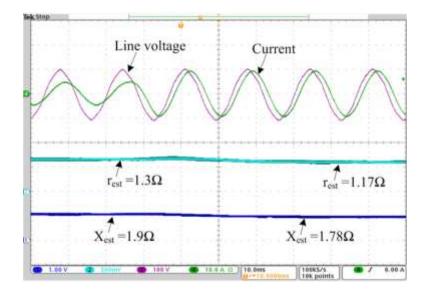

| Figure 16. Estimated resistance and reactance under balanced grid voltage $(r_{est} : 1 \ \Omega/\text{div}, X_{est} : 2 \ \Omega/\text{div})1$                                                                                                                                             | .30 |

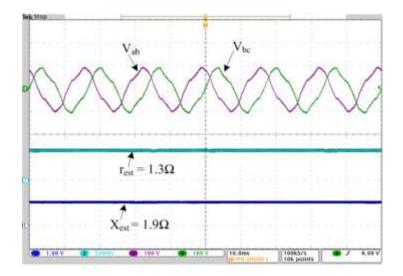

| Figure 17. Estimated resistance and reactance under unbalanced and distorted grid voltage ( $r_{est}$ : 1 $\Omega$ /div, $X_{est}$ : 2 $\Omega$ /div)                                                                                                                                       | 31  |

| Figure 18. Line voltage and current waveform during transition from $P = 375$ W to $P = 750$ W ( $r_{est} : 1 \Omega/\text{div}, X_{est} : 2 \Omega/\text{div}$ )                                                                                                                           | .33 |

| Figure 19. Line voltage and current waveform during transition from $Q = 375$ VAR to $Q = 750$ VAR ( $r_{est} : 1 \Omega/\text{div}, X_{est} : 2 \Omega/\text{div}$ )                                                                                                                       | .33 |

| Figure 20. Line voltage, current, estimated resistance and estimated reactance during an addition of 0.85 $\Omega$ ( $r_{est}$ : 1 $\Omega$ /div, $X_{est}$ : 2 $\Omega$ /div) 1                                                                                                            | .34 |

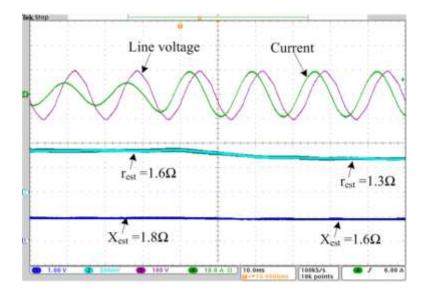

| <ul> <li>Figure 21. Reference and actual <i>d</i>-axis current in current controlled grid connected converter (a) Response exhibiting overshoot,</li> <li>(b) Overdamped response exhibiting long settling time,</li> <li>(c) Response with optimally tuned controller parameters</li></ul> | .35 |

| PAPER V                                                                                                                                                                                                                                                                                     |     |

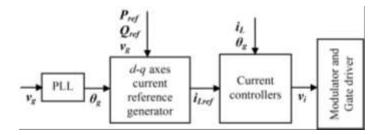

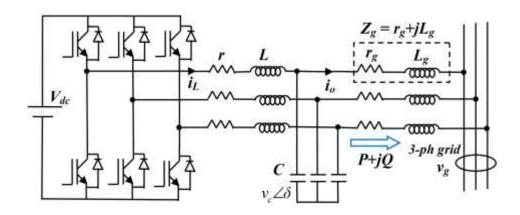

| Figure 1. Control structure for current controlled VSC                                                                                                                                                                                                                                      | .43 |

| Figure 2. Control structure for voltage controlled grid connected VSC 14                                                                                                                                                                                                                    | .43 |

| Figure 3. 3-phase grid-connected VSC                                                                                                                                                                                                                                                        | 46  |

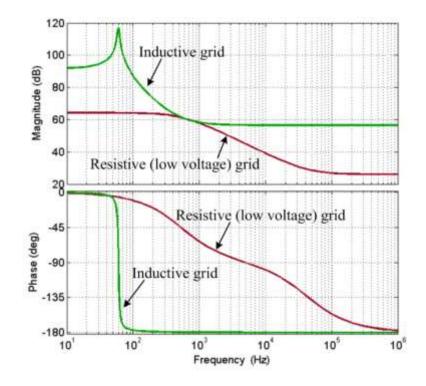

| Figure 4. Performance of the power-angle synchronization controller of high voltage (inductive) grids [20] when applied to low voltage grids 14                                                                                                                                             | .48 |

| Figure 5. Comparison of the frequency response of the small signal model<br>in (5) and (24)                                                                                                                                                                                                 | .53 |

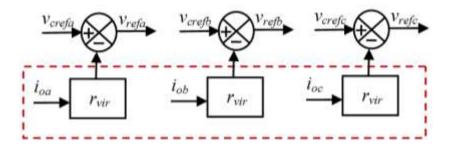

| Figure 6. Implementing the virtual resistance for better decoupling<br>between active and reactive power                                                                                                                                                                                    | .53 |

| Figure 7. Proposed control structure of the active and reactive power compensators                                                                                                                                                                                                          | 55  |

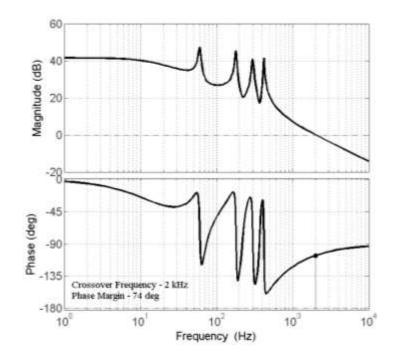

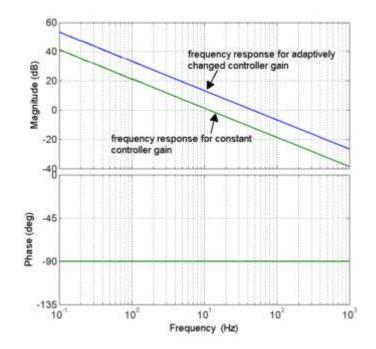

| Figure 8. Bode plot of the active power controller and plant when consuming rated active power                                                                                                                                                                                              | 57  |

|            | Bode plot of the reactive power controller and plant generating<br>load angle reference when consuming rated active power                                                                                                     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 10. | Bode plot of the active power controller and plant for different grid impedance                                                                                                                                               |

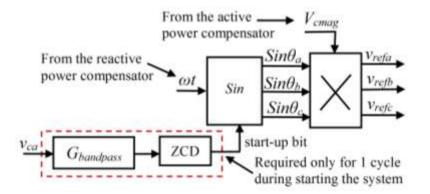

| Figure 11. | 3-phase voltage reference generation with the start-up circuit                                                                                                                                                                |

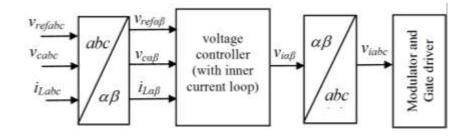

| Figure 12. | Inner voltage controller structure                                                                                                                                                                                            |

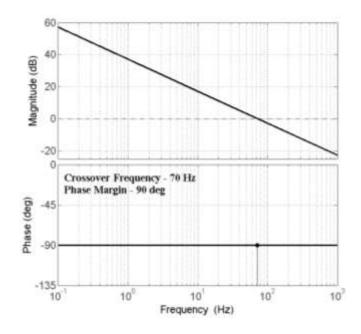

| Figure 13. | $\alpha$ -axis voltage controller with inner current loop                                                                                                                                                                     |

| Figure 14. | Frequency response of the loop gain of the voltage controller<br>and plant                                                                                                                                                    |

| Figure 15. | Picture of the hardware setup                                                                                                                                                                                                 |

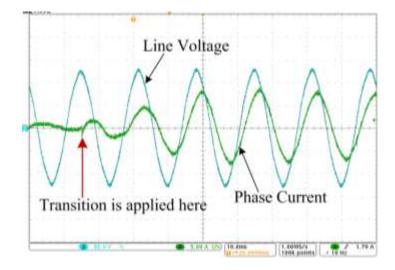

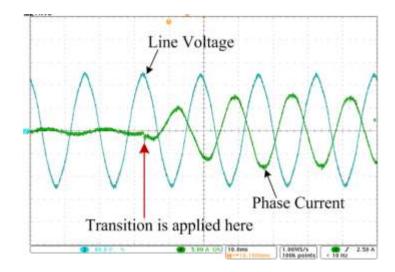

| Figure 16. | Line voltage and current waveform during transition from $P = 0$ W to $P = 1$ kW (Voltage: 80 V/div, Current: 5 A/div)                                                                                                        |

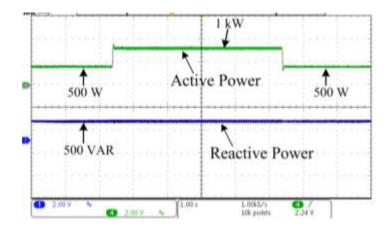

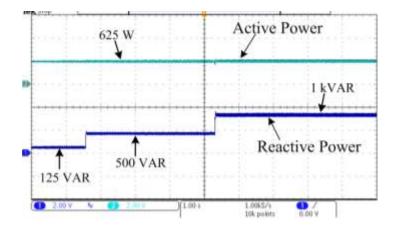

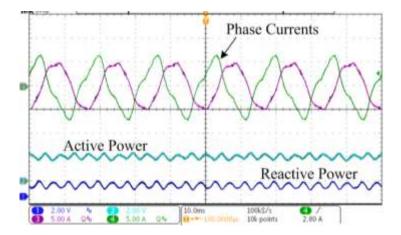

| Figure 17. | Change in active power with reactive power kept constant.<br>(Active Power: 625 W/div, Reactive Power: 625 VAR/div)165                                                                                                        |

| Figure 18. | Change in reactive power with active power kept constant.<br>(Active Power: 625 W/div, Reactive Power: 625 VAR/div)165                                                                                                        |

| Figure 19. | Line voltage and current waveform during transition from $P = 0$ W to $P = -1$ kW (Voltage: 80 V/div, Current: 5 A/div)                                                                                                       |

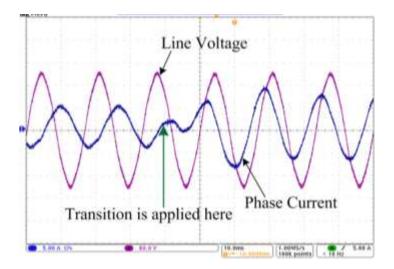

| Figure 20. | Line voltage and phase current during transition from $Q = 0.8$ kVAR to $Q = -1$ kVAR (Voltage: 80 V/div, Current: 5 A/div) 166                                                                                               |

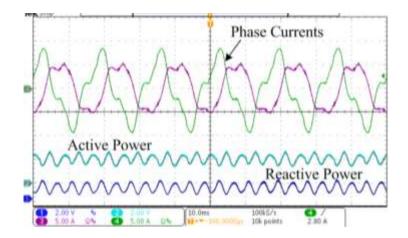

| Figure 21. | Line currents and power delivered during a 30% sag in voltage.<br>(Active Power: 0.8 kW/div, Reactive Power: 0.8 kVAR/div)                                                                                                    |

| Figure 22. | Line currents and power delivered during a 50% sag in voltage<br>(Active Power: 0.8 kW/div, Reactive Power: 0.8 kVAR/div)                                                                                                     |

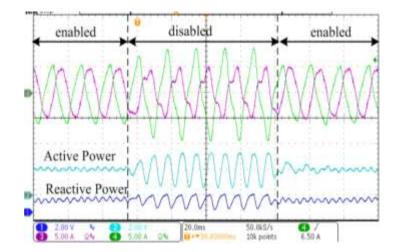

| Figure 23. | Line Currents, active and reactive power waveforms with the resonant portion of the active and reactive power compensators disabled for 5 cycles and enabled again (Active Power : 0.8 kW/div, Reactive Power : 0.8 kVAR/div) |

## LIST OF TABLES

|                                                              | Page |

|--------------------------------------------------------------|------|

| PAPER I                                                      |      |

| Table 1. System Parameters                                   | 21   |

| Table 2. Controller Parameters                               | 22   |

| PAPER II                                                     |      |

| Table 1. System and Current Controller Parameters            | 61   |

| PAPER III                                                    |      |

| Table 1. System Parameters                                   | 89   |

| Table 2. Controller Parameters                               | 98   |

| PAPER IV                                                     |      |

| Table 1. System and Controller Parameters                    | 128  |

| Table 2. Hardware Components                                 | 129  |

| Table 3. Estimated Values of Resistance and Reactance        | 132  |

| PAPER V                                                      |      |

| Table 1. Parameters of the Power Controllers                 | 158  |

| Table 2. System Parameters and Voltage Controller Parameters | 162  |

| Table 3. Hardware Components                                 | 162  |

## **1. INTRODUCTION**

## 1.1. REVIEW OF EXISTING CONTROL ARCHITECTURES FOR STAND-ALONE AND GRID-CONNECTED CONVERTER SYSTEMS

The single-phase and three-phase voltage source converter is the most commonly used power electronics converter for utility level stand-alone or grid-connected distributed generation units. With the focus on reducing emission due to power production by fossil fuels, renewable energy gained immense importance over the past few decades. Renewable energy being abundantly available with no cost, it can serve as an alternative for power production. Various renewable resources present offer their own advantages and disadvantages. The most commonly used renewable power sources are the wind energy and solar energy. Extraction of power from wind energy requires high initial cost for setting up of the wind power plant i.e. the wind turbine along with its mechanical and electrical control system for optimal usage. On the other hand solar energy requires the panels to be setup over along with its electrical and mechanical systems which also involve high initial cost. However, from the perspective of maintenance solar power plants are comparatively easier to maintain from the mechanical perspective as replacement of a wind turbine would involve replacing an old wind turbine with a newer one. On the contrary maintenance of solar power plants is easier from the mechanical perspective. However, it might get challenging to locate the exact point of problem in a solar power plant as generally mechanical failure of a solar panel is seldom observed. Despite all these advantages and disadvantages, due to the inherent intermittent nature of renewable power resources it becomes immensely challenging to connect these

sources to the grid/local load directly. The latter issue enabled researchers to come up with interfacing power converter topologies for successful grid integration of renewable power resources. A DC-AC converter serves as the interface for the renewable power source to connect to the grid. Pointing out some drawbacks in the existing control architecture, advanced control technique to successfully integrate renewable resources with the grid is the main focus of this thesis.

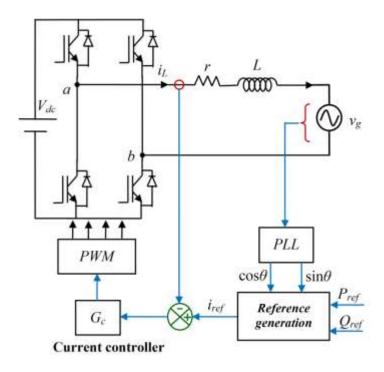

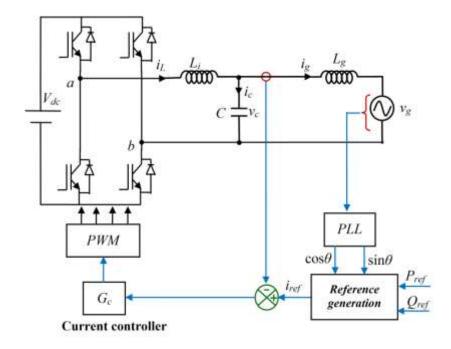

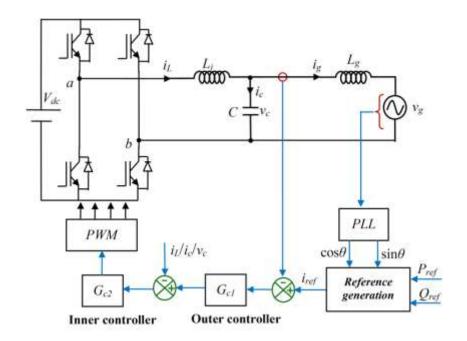

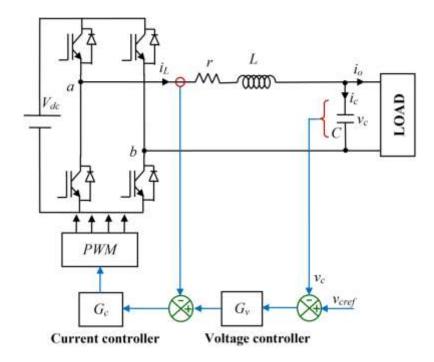

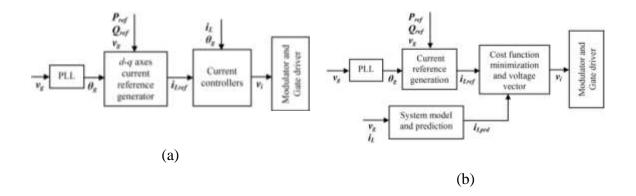

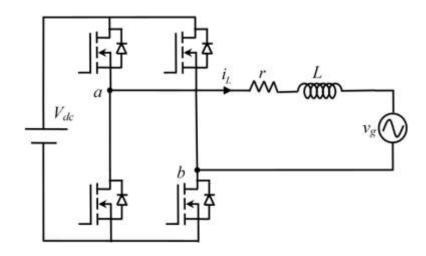

For grid-connected applications, the goal is to control the active and reactive power supplied to and from the grid. Since, the grid voltage is (generally) not dictated by the converter, this is achieved by controlling the current supplied by the converter to the grid. This control approach is known as the current control architecture [1]-[3], and is immensely popular due to its inherent simplicity and decoupled nature. Typical implementation with a L and LCL filters are shown in Figure 1.1 - Figure 1.3. The control scheme requires the accurate phase information of the fundamental component of the grid voltage. This information is obtained from a phase locked loop (PLL) which has the grid voltage as its input and generates the frequency and phase information (in the form of unit vectors) as its outputs. On the contrary, for stand-alone applications (see Figure 1.4) the goal is to control the output voltage. The output voltage requirement at the utility level is dictated as in [4] which clearly specifies the voltage rms to be within  $\pm 5\%$  of the nominal voltage. General requirements necessitate a control architecture which needs to ensure a negligible steady-state error in the output voltage, a minimum total harmonic distortion (THD) under nonlinear loads, and a fast response during load transients. The popularly used control architecture to achieve these is the two-loop control [5], [6], with an inner current and outer voltage loop as shown in Figure 1.4.

Figure 1.1. Current controlled architecture for single-phase grid-connected converter.

Figure 1.2. Direct grid current control architecture for *LCL* filter based single-phase gridconnected converter.

Figure 1.3. Multi-loop current control architecture for *LCL* filter based single-phase gridconnected converter.

Figure 1.4. Conventional two-loop architecture for single-phase stand-alone converter.

The performances of the conventional control architectures have reported satisfactory performance. However, the following drawbacks are noted in the existing control architectures. The power electronic converter (stand-alone or grid connected) is crucial for utility applications. Hence it is important to ensure its reliable operation. As discussed above, it can be identified that the voltage and current sensors are extremely crucial in the control architecture and the smooth functioning of the converter. However, sensors are prone to failure. In situations where any sensor fails, the dedicated control system for the converter will be jeopardized and in worst case this may cause disconnection and complete shutdown of the corresponding power converter. So, for increased reliability, there is a need to look for possible sensorless control algorithms. A sensorless algorithm may act as a suitable backup and take over once a sensor failure is identified. From protection point of view, removing the current sensors is not advisable. However, possible sensorless control algorithms can be ventured to replace the voltage sensor. A sensorless algorithm also saves space and cost. This results in a more compact design.

The *LCL* filter based grid connected converter has reported excellent grid current quality. However, the controller itself is challenging to design. Direct control of the grid current implies designing a controller for a third order system. This is not straight forward and generally involves a complex controller structure [7]. Multiple control loops have also been proposed for *LCL* based grid connected converters, [8]-[15], for stability and resonance damping at the cost of increased sensors. In general, the grid side current is chosen as the variable for the outer loop while the inner loop variable is chosen as the capacitor current [8], [11], [12], or the converter current [13] or the filter capacitor voltage

[14], [15]. However design of a multi-loop control structure is not trivial and requires detailed mathematical analysis [8], [11]. Compared to controlling the grid current, control of the converter side current is simple. Hence, alternative approaches to control the grid current by controlling the converter side current can be ventured. Additionally, accurate and optimized controller design depends on knowledge of accurate plant parameters. The plant parameters change depending on the operating conditions, temperature and ageing. So an online estimation of the plant parameters can be done to get an accurate plant model and tune the control parameters accordingly.

Finally, the popularly used current controlled architecture for grid connected converters are reporting stability problems in weak grid conditions with multiple converters connected in parallel. The loss of stability is mainly due to unmodelled and simplified PLL dynamics [16]-[20]. While research is still being carried on to mathematically model the issue, there is a parallel need to come up with alternate control algorithms which eliminate the PLL structure but still retain the advantages of the current control architecture.

#### **1.2. RESEARCH CONTRIBUTION**

Addressing the above problems, this dissertation proposes the following solutions for grid connected and stand-alone converter systems. Some of the solutions are proposed for single-phase systems. However, they are equally applicable to corresponding threephase architectures.

A methodology to control the output voltage of a standalone single-phase inverter without using a dedicated output voltage sensor (addressed in Paper I). The proposed control architecture aims to control the output voltage by controlling the output filter capacitor current. In addition to eliminating the voltage sensor, the proposed control method achieved better total harmonic distortion (THD) in the output voltage compared to existing conventional control methods. The plant modeling and controller design for the proposed control technique are presented. The proposed method depends on having the value of the output filter capacitance. A method to estimate the output filter capacitance is also presented. Dependence of the system parameters on the proposed control is studied. Rigorous analysis is done to show that the proposed sensorless scheme ensures the output voltage is within specified regulations at utility level.

For grid connected applications, it is important to know the phase and frequency of the grid voltage. This dissertation (Paper II) presents an estimation algorithm to estimate the grid voltage and control a single-phase grid connected converter without a dedicated grid voltage sensor. The main focus is given to current controlled architectures which need phase locked loops (PLL) for their operation. The grid voltage estimation method is proposed based on the active and reactive power delivered by the converter to the grid. In addition to the estimation of the grid voltage, the proposed method also generates the unit vectors and frequency information similar to a conventional PLL structure. The effect of circuit non idealities and parameter variations are considered and analyzed in details, thereby establishing their effects on the proposed estimation scheme. The proposed estimation algorithm is equally applicable for three phase grid connected systems. The proposed estimation method is then applied to LCL based grid connected converter to develop an indirect grid current control algorithm (Paper III). The new control algorithm of LCL based grid connected converter system uses the same number of sensors as a conventional direct grid current control algorithm (one current and one

voltage sensor). However, compared to the direct grid current control, the proposed control structure is simple in design as it controls the converter side current which follows an equivalent first order system. Fundamental and harmonic components of the filter capacitor voltage are estimated and the corresponding filter capacitor currents are computed from these estimated values. The fundamental and harmonic filter capacitor currents are then compensated from the converter side thereby indirectly controlling the grid current.

Addressing the issue of parameter variations, this dissertation proposes an online estimation based on model reference adaptive control (MRAC) approach in obtaining an accurate model of a grid connected inverter system. Active and reactive power based MRAC approaches are used to estimate the equivalent resistance and reactance between the inverter and the grid. Detailed stability analysis of the MRAC approach is presented. The system models for the MRAC controller design are derived and guidelines on the controller parameters selection are proposed.

Addressing the stability issue in conventional current controlled grid connected converter systems, this dissertation analyzes the power angle synchronization control of a grid-tied bidirectional dc-ac converter is investigated for low voltage grids (Paper V). The concept of power angle synchronization based control is to replace the current controlled architecture with voltage controlled architecture. In other words, the active and reactive power delivered to and from the grid is now controlled by controlling the voltage at the output of the converter. The power flow equations for the low voltage grid are analyzed and compensators are designed to ensure the decoupled control of active and reactive power. The proposed control system operates without the need for a phase locked loop during balanced and unbalanced grid conditions. The proposed power angle synchronization shows stable start-up, steady state and transient state operation during balanced grid conditions ensuring the desired power flow to and from the grid. It is also demonstrated that the compensators are immune to grid fluctuations and to a large extent can cater grid unbalanced conditions.

#### PAPER

## I. CONTROL OF A SINGLE-PHASE STANDALONE INVERTER WITHOUT AN OUTPUT VOLTAGE SENSOR

#### ABSTRACT

This paper analyzes the possibility of controlling the output voltage of a standalone single-phase inverter by directly controlling the output filter capacitor current without using a dedicated output voltage sensor. The plant modeling and controller design are presented. The proposed method depends on having the value of the output filter capacitance. A method to estimate the output filter capacitance is also presented. Rigorous analysis is done to show that the proposed sensorless scheme is largely insensitive to parameter variations and ensure the output voltage is within specified regulations at utility level. It is also demonstrated in the paper that compared to the conventional voltage control scheme the proposed control scheme ensures an improved total harmonic distortion (THD) of the output voltage waveform. Experimental results presented validate the proposed scheme.

## **1. INTRODUCTION**

The single-phase voltage source inverter is the most widely used power electronic converter for utility level standalone distributed generation units. The output voltage requirement at the utility level is dictated as in [1] which clearly specifies the voltage rms to be within  $\pm 5\%$  of the nominal voltage. General requirements necessitate a control

architecture which needs to ensure a negligible steady-state error in the output voltage, a minimum total harmonic distortion (THD) under nonlinear loads, and a fast response during load transients. Thus the control of such inverters has become a topic of interest among researchers. Unlike a three-phase inverter, a single-phase inverter cannot be directly controlled in the synchronous frame of reference. Authors of [2], [3] proposed to do so by creating a fictitious quadrature axis. Though the modeling and control of the inverter becomes simple in the fictitious synchronous frame of reference, the conversion itself involves additional computations and inherently introduces delay in the system. Furthermore, additional controllers as shown in [4] are necessary to maintain the output voltage under nonlinear loads. Over the past years, several nonlinear, adaptive, hysteresis, repetitive and geometric based control structures have been proposed for controlling single-phase inverter systems [5]-[15]. However, each of these interesting control structures have their limitations namely modeling complexities, detailed mathematical derivations, unsatisfactory performances under nonlinear loads, parameter sensitivity etc. Among the proposed control structures for single-phase inverters in the literature, the proportional resonant (PR) controller is arguably the most popular. The PR controller in a stationary frame of reference is the equivalent counterpart of the proportional integral (PI) controller in the synchronous frame of reference. Initially proposed in [20], the PR controller has been successfully implemented to track linear and nonlinear currents in current controlled grid connected converters [16]-[18]. It has also been applied to standalone converters to control their output voltage [5], [21]. The controller has reported excellent steady state error tracking under linear loads. However, as shown in [19], the controller has stability issues under nonlinear loads. This is primarily because with the

addition of resonant peaks at the dominant harmonic frequencies, namely third, fifth and seventh, the phase margin of the control loop deteriorates. The system stability thereby puts a limit on the resonant gains at higher harmonic frequencies, thereby requiring additional measures to improve the phase margin and reduce the voltage THD under nonlinear loads [19].

All the previous control architectures discussed for single-phase inverters use an output voltage sensor. In this paper, we take a novel step by eliminating the output voltage sensor and investigate the possibility of controlling a standalone inverter without the voltage sensor. Sensorless control has been proposed for grid connected converter systems where the power flow between the converter and the grid is controlled without the need of dedicated grid voltage sensors [22]–[24]. However, to the best knowledge of the authors, sensorless voltage control approaches have not been discussed for standalone inverters in the literature. With a regulated dc bus voltage, faults in single-phase inverter systems are generally caused by overcurrents. Hence, eliminating the output voltage sensor does not compromise the system protection. In fact, the elimination of the voltage sensor saves cost and space. Additional circuitry and wiring requirements are also reduced. The inverter may have to operate in an environment where it is subjected to high temperature, electromagnetic interference (EMI), and noises. In such conditions, sensors are prone to errors and physical damage. One such example is the hybrid power train where the power electronics converters have to operate under high temperature, noise and vibrations. A damaged or inaccurate sensor will jeopardize the entire system. A sensorless control scheme thus adds to the reliability of the overall system. It acts a backup during sensor failure thereby preventing complete shutdown of the system.

However, it must be ensured that the output voltage meets the desired specifications for utility applications [1]. Addressing this issue, the control methodology presented in this paper ensures that the output voltage is within the prescribed limits. The approach aims to control the output voltage by directly controlling the output capacitor current. An estimation of the output filter capacitance, required for this purpose is also discussed. It is demonstrated that the proposed control scheme ensures better THD of the output voltage under nonlinear loads compared to the conventional voltage control approach. A thorough analysis is done to show that such estimation along with the proposed control structure is largely immune to parameter fluctuations.

The rest of the paper is arranged as follows. The proposed control scheme is presented in Section 2. This section also includes the estimation of the output voltage and the output filter capacitance prediction. The modeling of the rms voltage control loop and the sensitivity of the output voltage to the parameter variations is shown in Section 3. The results are discussed in Section 4, while the conclusion presented in Section 5.

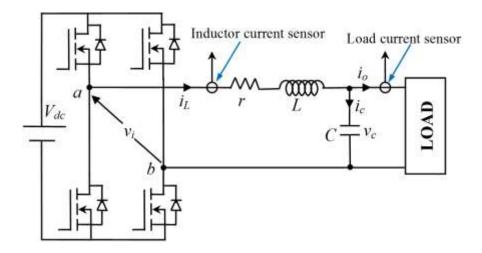

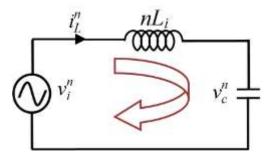

Figure 1. Circuit of a single-phase standalone inverter.

## **2. CONTROL ARCHITECTURE**

The schematic of a standalone inverter is shown in Figure 1. In the figure, L is the filter inductance, r is the resistance representing the ohmic loss of the switches and the filter inductor, C is the filter capacitance,  $i_L$  is the filter inductor current,  $i_o$  is the load current,  $i_c$  is the capacitor current,  $v_c$  is the output voltage of the converter, and  $v_i$  is the output voltage of the bridge. The filter inductor and load current are measured. However, unlike conventional voltage control methods the output voltage is not measured for the proposed sensorless control scheme.

## 2.1 Review of the Conventional Voltage Control Method

The inductor current and output capacitor voltage dynamics for the circuit as shown in Figure 1 are given as

$$L\frac{di_L}{dt} + ri_L = v_i - v_c \tag{1}$$

$$C\frac{dv_c}{dt} = i_L - i_o \tag{2}$$

The inductor current, output capacitor current, and load current are related as

$$i_L = i_o + i_c \tag{3}$$

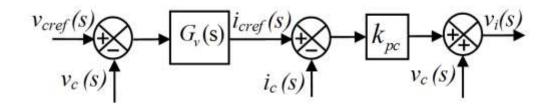

The multi loop structure with an outer voltage loop and an inner current loop [21] is generally used as the controller structure. The control structure introduces output impedance dependent on the load current. It has been reported that the choice of the capacitor current feedback in the inner current loop ensures much lower output impedance compared to the inductor current feedback approach [21]. The controller structure is presented in Figure 2. The output voltage feedforward is also added to the control loop. With such a control structure, the open loop gain is given as [21]

$$G(s) = \frac{k_{pc}G_{v}(s)}{s^{2}LC + (r+k_{pc})sC}$$

(4)

where  $G_v(s)$  is the voltage compensator and  $k_{pc}$  the proportional gain of the inner current loop. The system represented by (4) is a second order system. With an increase in the controller gain, especially at the higher harmonic frequencies, the phase margin of the system deteriorates. So there is a tradeoff between achieving a high bandwidth and stability in the open loop gain represented by (4). Often phase lead compensators are needed to improve the phase margin as reported in [19].

Figure 2. The conventional voltage control structure with capacitor current feedback.

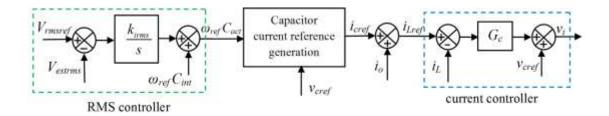

Figure 3. Overall block diagram of the proposed control scheme.

Figure 4. The current control loop with the corresponding plant.

#### 2.2 Proposed Control Scheme

The overall block diagram of the proposed control scheme is shown in Figure 3. The control structure has three distinct parts, the voltage RMS controller, the filter capacitor current reference generator, and a current controller. Each of the section is sequentially described in details. The output voltage of a single-phase inverter can be controlled by controlling the capacitor current. To produce the desired output voltage vcref, an inductor current reference can be set as

$$i_{Lref} = i_o + i_{cref} \tag{5}$$

where,

$$i_{cref} = C \frac{dv_{cref}}{dt} \tag{6}$$

It is worth mentioning that metallized polypropylene film capacitors are the most common choice as filter capacitors. These capacitors have negligible equivalent series resistance (ESR). On the basis of this knowledge, the resistive drop across the output capacitor has been ignored in (6). It can be seen from (1) that inductor current  $i_L$  can be controlled by  $v_i$ , the output of the bridge, while the dynamics of output voltage  $v_c$  can be controlled by controlling inductor current  $i_L$ . Thus output voltage  $v_c$  can be indirectly controlled by controlling  $v_i$ . A properly designed controller will ensure that the output of the bridge ( $v_i$ ) is able to maintain the inductor current at its desired reference  $i_{Lref}$  (as in (5)) thereby ensuring that capacitor current  $i_c$  is maintained at  $i_{cref}$  as given in (6). This in turn will ensure that the output voltage is maintained at the desired reference value  $v_{cref}$ . However, it should be noted that an accurate knowledge of the value of the output filter capacitor is needed in (6). The rms voltage controller in Figure 3 gives an estimation of the filter capacitor which is used to calculate the capacitor reference current (as in (6)). The capacitor reference current generator in Figure 3 basically implements (6). The estimation of the capacitor and capacitor reference current generation will be addressed in details in the next section. Capacitor reference current icref is added to the load current to generate reference inductor current  $i_{Lref}$  as in (5). A well-designed current controller ensures that the actual inductor current  $i_L$  tracks  $i_{Lref}$ . The current controller structure is represented as

$$v_i(s) = (i_{Lref}(s) - i_L(s))G_c(s) + v_{cref}(s)$$

(7)

where  $G_c(s)$  represents the current controller. Generally output voltage  $v_c$  is treated as a disturbance input in (1) and is used as the feedforward term in (7) [21]. However, as a voltage sensor is not being used,  $v_c$  is not available. So  $v_{cref}$  is used as the feedforward term. The control structure is shown in Figure 4.

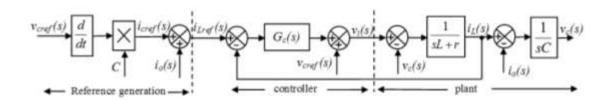

The design of the controller needs the knowledge of the plant model. In other words, the open loop gain of the plant and controller must be known. The loop gain of the proposed control structure is derived next. Taking the Laplace transform of (2), (3), (5) and (6) and using them in (7) leads to

$$v_{i}(s) = (sCG_{c}(s) + 1)v_{cref}(s) - sCG_{c}(s)v_{c}(s)$$

(8)

Also, in the Laplace domain (1) and (2) can be combined as

$$(s^{2}LC + srC + 1)v_{c}(s) + (sL + r)i_{o}(s) = v_{i}(s)$$

(9)

Substituting  $v_i(s)$  from (8) in (9) results in

$$\left(s^{2}LC + s(r + G_{c}(s))C + 1\right)v_{c}(s) = \left(sCG_{c}(s) + 1\right)v_{cref}(s) - \left(sL + r\right)i_{o}(s)$$

(10)

or,

$$v_c(s) = \frac{sCG_c(s)+1}{s^2LC+s(r+G_c(s))C+1}v_{cref}(s) - \frac{sL+r}{s^2LC+s(r+G_c(s))C+1}\dot{i}_o(s)$$

(11)

which can be rearranged in the standard form as

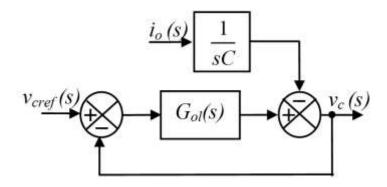

$$v_{c}(s) = \frac{\frac{sCG_{c}(s)+1}{sC(sL+r)}}{1+\frac{sCG_{c}(s)+1}{sC(sL+r)}} v_{cref}(s) - \frac{\frac{1}{sC}}{1+\frac{sCG_{c}(s)+1}{sC(sL+r)}} \dot{i}_{o}(s)$$

(12)

The block diagram representation of (12) is shown in Figure 5. The load current  $i_o$  is generally treated as an disturbance input. From (12), treating  $i_o$  as a disturbance input, the transfer function relating  $v_c$  and  $v_{cref}$  need sto be found. This transfer function will serve as the closed loop gain. The closed loop gain is obtained as

$$\frac{v_{c}(s)}{v_{cref}(s)} = G_{cl}(s) = \frac{\frac{sCG_{c}(s) + 1}{sC(sL + r)}}{1 + \frac{sCG_{c}(s) + 1}{sC(sL + r)}}$$

(13)

Equation (13) is in the standard form. The open loop gain is found by inspection of (13). From (13), the open loop gain is obtained as

$$G_{ol}(s) = \frac{sCG_c(s) + 1}{sC(sL + r)}$$

(14)

Figure 5. Closed loop equivalent representation of the controller structure.

The controller parameters will be selected based on the open loop gain in (14). Again, open loop gain  $G_{ol}(s)$  can be simplified as

$$G_{ol}(s) = \frac{1}{sC(sL+r)} + \frac{G_c(s)}{sL+r}$$

(15)

or,

$$G_{ol}(s) = G_1(s) + G_2(s)$$

(16)

where,

$$G_1(s) = \frac{1}{sC(sL+r)}$$

and  $G_2(s) = \frac{G_c(s)}{sL+r}$

It can be observed from (15) and (16) that the open loop gain at low frequencies is primarily dictated by  $G_1(s)$ . However, as frequency increases the influence of  $G_1(s)$ decreases. So at higher frequencies the open loop gain is dictated by  $G_2(s)$ . Hence it can be asserted that the system bandwidth and response to harmonic frequencies can be controlled by  $G_c(s)$ . It should also be noted that similar to the voltage control architecture [19], [21], output impedance  $Z_o(s)$  is also introduced in this case. From (12),  $Z_o(s)$  can be found as

$$\frac{v_c(s)}{i_o(s)} = Z_o(s) = \frac{sL + r}{s^2 LC + s(r + G_c(s))C + 1}$$

(17)

From (3) and (5) it is worth noting that

$$i_{Lref} - i_L = i_{cref} - i_c \tag{18}$$

So, unlike in voltage control structures, it can be concluded that the choice of the inductor current or the capacitor current as the control variable makes no difference to the performance of the control loop for the proposed scheme.

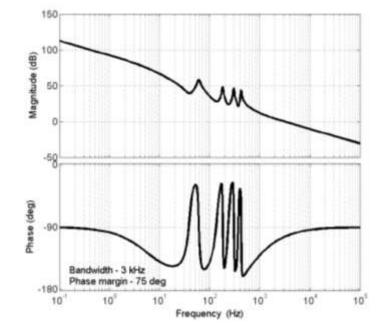

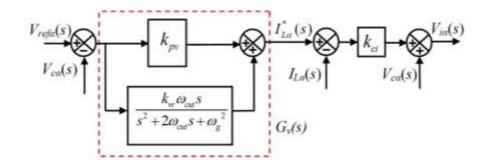

Since a single-phase system is expected to produce a sinusoidal output, a PR controller with the resonant peak at the fundamental frequency is sufficient as the current controller. However, since any standalone system must have the capability to cater nonlinear loads, the controller is augmented with resonant peaks at dominant harmonic frequencies, namely the third, fifth and seventh harmonic frequencies. Incorporating the additional resonant peaks, the controller structure is given as

$$G_{c}(s) = k_{p} + \sum_{n=1,3,5,7} \frac{k_{m}\omega_{cutn}s}{s^{2} + 2\omega_{cutn}s + (n\omega_{o})^{2}}$$

(19)

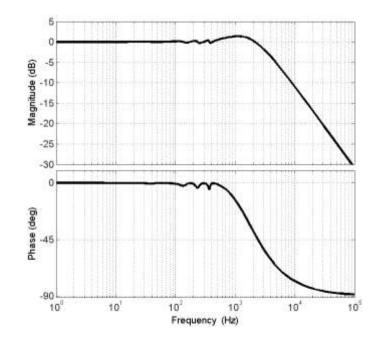

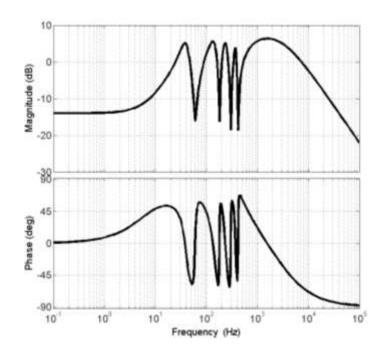

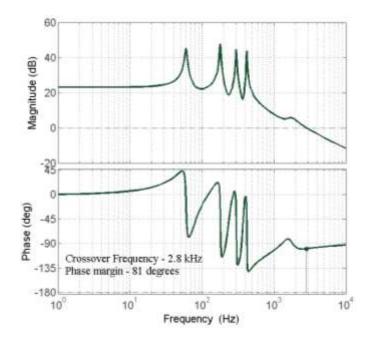

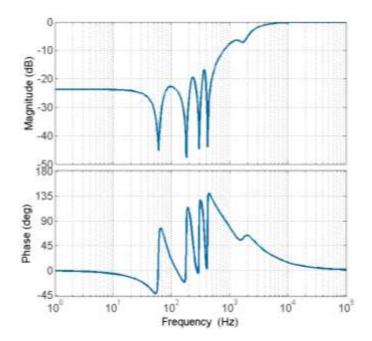

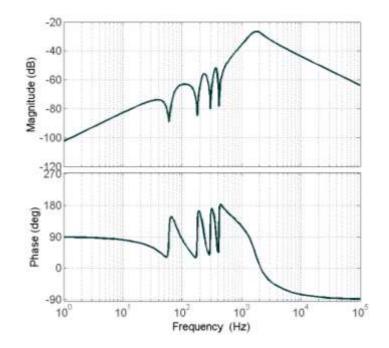

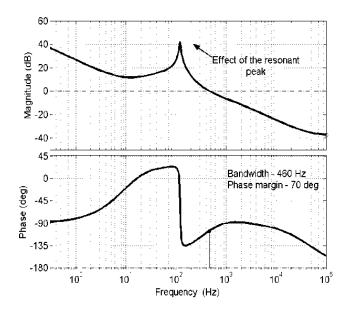

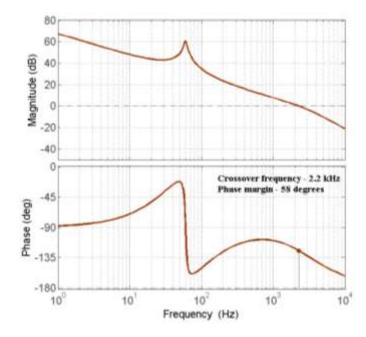

In (19),  $k_p$  is the proportional gain,  $k_m$  and  $\omega_{cutn}$  are the resonant gain and cut off frequency at the  $n^{\text{th}}$  harmonic frequency. The proportional gain and resonant gains are chosen such that the bandwidth is about 3 kHz, while the gain at the fundamental and compensated harmonic frequencies is at least 40 dB. It should be noted that since the open loop system has a first order behavior, the phase margin at 3 kHz is sufficiently high (about 75 degrees). Such high phase margin and bandwidth cannot be simultaneously achieved with the conventional voltage control architecture. The different components used for the circuit in Figure 1 are listed in Table 1. It should be noted that in Table 1, *r* is taken as the summation of the winding resistance of the inductor and twice the on state resistance of each switch ( $r = r_{dc}+2R_{ds}$ ). With the controller parameters represented in Table 2, the open loop frequency response of the plant and the controller is shown in Figure 6. The corresponding close loop response is shown in Figure 7. For the chosen controller parameters, the output impedance  $Z_o$  is shown in Figure 8. It can be seen that the output impedance is very low at the fundamental and compensated harmonic frequencies. The effect of the delay introduced due to the sampling, computation and PWM update was not considered in the controller design. The delay adds an additional phase lag to the system [4]. Hence it is important to verify that the phase lag does not make the closed loop system unstable. The phase lag introduced due to the delay is approximated as

$$\phi_{del} = -tan^{-1}(\omega T_{del}) \tag{20}$$

For a switching frequency of 20 kHz, a double sample and update scheme in one switching cycle gives  $T_{del}$  of 25 micro seconds. Using (20), the phase lag at the cross over frequency of 3 kHz, is computed as 25 degrees. Hence the phase margin at the crossover frequency of 3 kHz decreases from 75 degrees to 50 degrees. This phase margin is still sufficient to ensure the stable operation of the closed loop system.

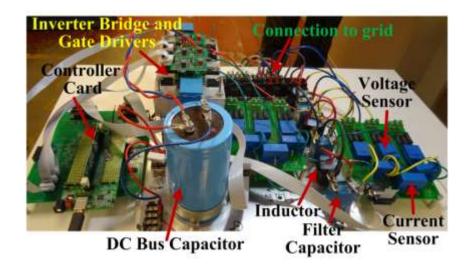

Table 1. System Parameters.

| Part                         | Manufacturer            | Specifications                                        |

|------------------------------|-------------------------|-------------------------------------------------------|

| Inductor( <i>L</i> )         | Hammond (195G20)        | $L=5$ mH, $r_{dc} = 40$ m $\Omega$                    |

| Capacitor ( <i>C</i> )       | Epcos (B33364A5206J050) | 20 µF, 440 V                                          |

| Switches $(S_1-S_4)$         | Infineon (IPP600N25N3)  | $V_{ds}$ =250 V, $I_d$ =25 A, $R_{ds}$ =80 m $\Omega$ |

| Dc bus capacitor             | Epcos (B43704B5338M)    | 450 V, 3300 μF                                        |

| Loss resistance ( <i>r</i> ) | _                       | $r_{dc}+2R_{ds}=0.2 \ \Omega$                         |

| $k_p (V/A)$               | 80    |

|---------------------------|-------|

| $k_{r1}$ (V/Asec)         | 2,000 |

| $k_{r3}(V/Asec)$          | 2,500 |

| $k_{r5}(V/Asec)$          | 3,000 |

| $k_{r7}(V/Asec)$          | 4,000 |

| $\omega_{cut1}$ (rad/sec) | 10    |

| $\omega_{cut3}$ (rad/sec) | 20    |

| $\omega_{cut5}$ (rad/sec) | 30    |

| $\omega_{cut7}$ (rad/sec) | 40    |

Table 2. Controller Parameters.

Figure 6. Open loop frequency response of the current controller and plant.

Figure 7. Closed loop frequency response of the current controller and plant.

Figure 8. Frequency response of the output impedance.

#### **2.3 Estimation of the Output Filter Capacitance**

It can be seen from (6) that the value of  $i_{cref}$  is dependent on the value of output capacitance *C*. An inaccurate estimate of *C* will cause the output voltage to deviate from the desired reference value. An output voltage rms control loop is proposed to get an estimate of the filter capacitance (see Figure 3). To get the rms value of the output voltage, an estimation of the output voltage is needed. The output voltage estimation is done using the concept of virtual flux [22], [23]. The virtual flux is computed as

$$\psi_{vir} = \int \left( v_i - r_e i_L \right) - L_e i_L \tag{21}$$

where  $r_e$  and  $L_e$  are the assumed value of the resistance and inductance of the filter inductor. A pure integrator has dc drift problems. Hence the integration in (21) is generally performed by a low pass filter. However, low pass filtering

is always associated with phase lag and attenuation in the gain. A better alternative is to use the filter

$$G_{fil} = \frac{k\omega_{cut}}{s^2 + k\omega_{cut}s + \omega_{ref}^2}$$

(22)

The filter as shown in (22) is generally used for positive and negative sequence separation [25], [26] and has been used for virtual flux generation in [22]. The virtual flux is multiplied by  $\omega_{ref}$  to generate the signal vest which is passed through an orthogonal signal generator (OSG) to generate the signal  $v_{estquad}$ . The OSG is realized using an all pass filter (APF) given as

$$G_{quad} = \frac{\omega_{ref} - s}{\omega_{ref} + s}$$

(23)

Thus if  $v_{ref} = V_{rekpk}\cos\theta$ , then  $v_{est} = V_{estpk}\sin\theta_1$  and vestquad =  $-V_{estpk}\cos\theta_1$ . With the knowledge of vest and  $v_{estquad}$ , an instantaneous computation of the rms of the estimated voltage can be done. To do so, an operation similar to the scalar product between the reference and estimated voltage is performed. The operation is represented as

$$\langle v_{ref}, v_{est} \rangle = v_{quad} v_{est} - v_{ref} v_{estquad}$$

(24)

$$\langle v_{ref}, v_{est} \rangle = V_{refpk} V_{estpk} \cos \delta_{err} \tag{25}$$

Where,  $v_{quad} = V_{refpk} \sin\theta$ ,  $V_{refpk}$  is the peak value of the reference voltage,  $V_{estpk}$  is the peak value of the estimated voltage and  $\delta_{err}$  is the angle between them. The phase shift between the two voltages occurs if actual resistance r and inductance L in the circuit deviate from the assumed resistance  $r_e$  and inductance  $L_e$  respectively. However considering the phase shift to be small  $\cos\delta_{err} \approx 1$ . So (25) can be written as

$$\langle v_{ref}, v_{est} \rangle = V_{refpk} V_{estpk} \tag{26}$$

or,

$$V_{estpk} = \frac{\langle v_{ref}, v_{est} \rangle}{V_{refpk}}$$

(27)