# Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

2015

# On-die sensors for transient events

Mihir Vimal Suchak

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons

Department:

#### **Recommended Citation**

Suchak, Mihir Vimal, "On-die sensors for transient events" (2015). Masters Theses. 7698. https://scholarsmine.mst.edu/masters\_theses/7698

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

## **ON-DIE SENSORS FOR TRANSIENT EVENTS**

by

## MIHIR VIMAL SUCHAK

## **A THESIS**

Presented to the Faculty of the Graduate School of the

MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2015

Approved by

Daryl G. Beetner, Advisor David J. Pommerenke Yiyu Shi

#### **ABSTRACT**

Failures caused by transient electromagnetic events like Electrostatic Discharge (ESD) are a major concern for embedded systems. The component often failing is an integrated circuit (IC). Determining which IC is affected in a multi-device system is a challenging task. Debugging errors often requires sophisticated lab setups which require intentionally disturbing and probing various parts of the system which might not be easily accessible. Opening the system and adding probes may change its response to the transient event, which further compounds the problem.

On-die transient event sensors were developed that require relatively little area on die, making them inexpensive, they consume negligible static current, and do not interfere with normal operation of the IC. These circuits can be used to determine the pin involved and the level of the event in the event of a transient event affecting the IC, thus allowing the user to debug system-level transient events without modifying the system.

The circuit and detection scheme design has been completed and verified in simulations with Cadence Virtuoso environment. Simulations accounted for the impact of the ESD protection circuits, parasitics from the I/O pin, package and I/O ring, and included a model of an ESD gun to test the circuit's response to an ESD pulse as specified in IEC 61000-4-2. Multiple detection schemes are proposed. The final detection scheme consists of an event detector and a level sensor. The event detector latches on the presence of an event at a pad, to determine on which pin an event occurred. The level sensor generates current proportional to the level of the event. This current is converted to a voltage and digitized at the A/D converter to be read by the microprocessor. Detection scheme shows good performance in simulations when checked against process variations and different kind of events.

### **ACKNOWLEDGEMENTS**

I would like to sincerely thank my graduate advisor, Dr. Daryl G. Beetner, for his expert guidance in my research work and invaluable support throughout my graduate degree. I thank Dr. David Pommerenke for his knowledgeable advice and guidance in my work. I am also grateful to Dr. Yiyu Shi for serving as a member of my thesis committee and his expert advice for the improvements on my work. I also thank the research group at "Electromagnetic Compatibility Laboratory" at Missouri S&T, for providing me with great knowledge and environment for growth during my graduate career. I would also like to thank Richard Moseley and Dr. Michael Stockinger from Freescale Semiconductor for guiding my research work.

I thank my parents, brother and entire family for their unconditional love and support throughout my education. I also extend warm thanks to all my friends for encouragement and guidance. I finally thank God, almighty for making all this possible.

# TABLE OF CONTENTS

|                                       | Page |

|---------------------------------------|------|

| ABSTRACT                              | iii  |

| ACKNOWLEDGEMENTS                      | iv   |

| LIST OF FIGURES                       | viii |

| 1 INTRODUCTION                        | 1    |

| 1.1 BACKGROUND                        | 2    |

| 1.2 METHODOLOGY                       | 4    |

| 2 INTIAL DESIGNS                      | 5    |

| 2.1 OUT-OF-RANGE VOLTAGE DETECTORS    | 5    |

| 2.1.1 Concept and Schematics          | 5    |

| 2.1.2 Simulation Models               | 11   |

| 2.1.3 Simulation Results and Analysis | 13   |

| 2.1.3.1 Increasing size of M5         | 26   |

| 2.1.3.2 Current-source load inverter  | 27   |

| 2.2 OSCILLATORS                       | 32   |

| 2.2.1 Concepts and Schematics         | 33   |

| 2.2.1.1 Self-triggered oscillator     | 33   |

| 2.2.1.2 Windowed oscillator           | 33   |

| 2.2.1.3 RC-based oscillator           | 34   |

| 2.2.2 Simulation Models                               | 35  |

|-------------------------------------------------------|-----|

| 2.2.3 Simulation Results and Analysis                 | 37  |

| 2.2.3.1 Self-triggered oscillator                     | 37  |

| 2.2.3.2 Windowed oscillator                           | 39  |

| 2.2.3.3 RC-based oscillator                           | 49  |

| 2.2.4 Limitations                                     | 51  |

| 3 CENTRALIZED A/D BASED DETECTION METHODS             | 57  |

| 3.1 INSTANTANEOUS DETECTION                           | 57  |

| 3.1.1 Concept                                         | 58  |

| 3.1.2 Detection Scheme                                | 59  |

| 3.1.3 Need of Repeaters in I/O Pad Ring               | 63  |

| 3.1.4 Simulation Models                               | 67  |

| 3.1.5 Simulation Results and Drawbacks                | 68  |

| 3.2 "SAMPLE AND HOLD" METHOD                          | 76  |

| 3.2.1 Concept Derivation from Instantaneous Detectors | 76  |

| 3.2.2 Simulation Models                               | 83  |

| 3.2.3 Simulation Results and Analysis                 | 83  |

| 3.2.4 Implementation Details                          | 103 |

| 3.2.4.1 N-well and p-well biasing circuits            | 103 |

| 3.2.4.2 Snapback current limiting resistors               | )6 |

|-----------------------------------------------------------|----|

| 3.2.4.3 Different p-wells and n-wells                     | )6 |

| 3.2.4.4 Reset and reset_b                                 | )7 |

| 3.2.4.5 Level shifters                                    | )8 |

| 3.2.4.6 Padrst_mv and close signals                       | )9 |

| 3.3 FUTURE WORK: TEST PLAN FOR SAMPLE AND HOLD METHOD. 11 | 0  |

| 3.3.1 Transient Sources                                   | 12 |

| 3.3.2 Test Board                                          | 13 |

| 3.3.3 Measurements                                        | 5  |

| 3.3.4 Event Indication Thresholds                         | 6  |

| 3.3.5 Level Readouts                                      | 8  |

| 3.3.6 Hold Time                                           | 23 |

| 3.3.7 ESD Gun Tests                                       | 25 |

| 4 FILTERING/INTEGRATION FOR DETAILED EVENT ANALYSIS 12    | 26 |

| 4.1 FILTERING                                             | 26 |

| 4.2 INTEGRATION                                           | 27 |

| 5 CONCLUSIONS                                             | 29 |

| BIBLIOGRAPHY13                                            | 31 |

| VITA                                                      | 33 |

# LIST OF FIGURES

|              | Page                                                                                                                           |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-1.  | ESD protection at I/O pads and "Driving FET" M16                                                                               |

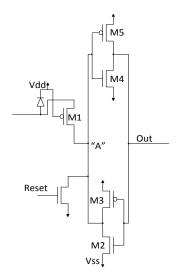

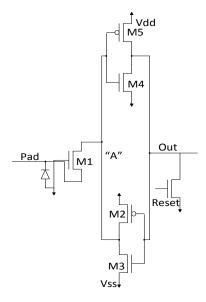

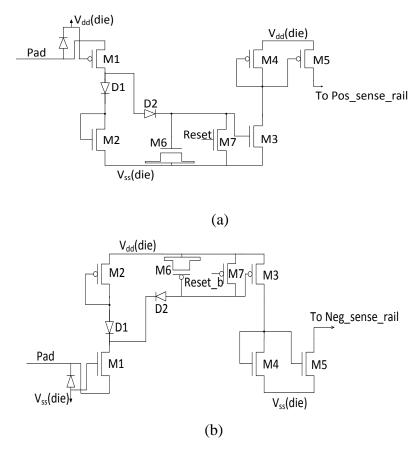

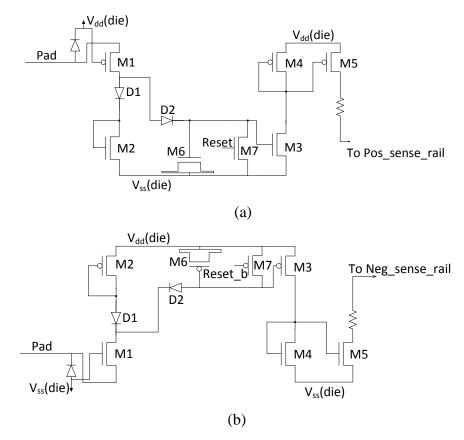

| Figure 2-2.  | Positive event indicator                                                                                                       |

| Figure 2-3.  | Negative event indicator9                                                                                                      |

| Figure 2-4.  | Positive event indicator with reset functionality10                                                                            |

| Figure 2-5.  | Negative event indicator with reset functionality10                                                                            |

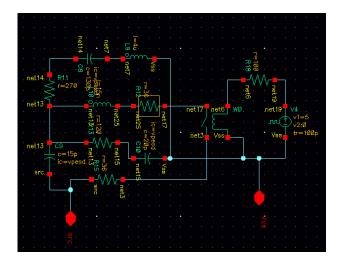

| Figure 2-6.  | ESD gun model in Cadence Virtuoso used to generate IEC-6100-4-2 type pulses                                                    |

| Figure 2-7.  | Pin parasitic model in Cadence Virtuoso                                                                                        |

| Figure 2-8.  | Complete simulation model formed in Cadence Virtuoso for testing different circuits                                            |

| Figure 2-9.  | General simulation model for any test circuit                                                                                  |

| Figure 2-10. | Positive event detector used for simulations                                                                                   |

| Figure 2-11. | Response of positive detector to 700V ESD event                                                                                |

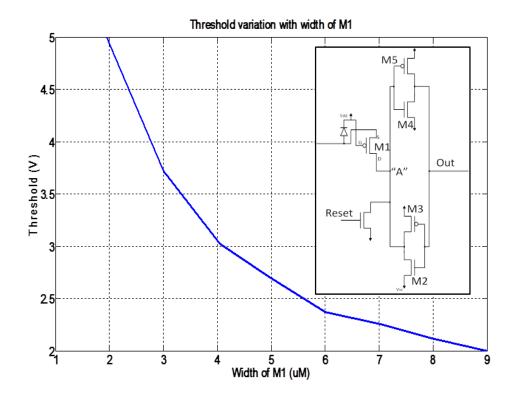

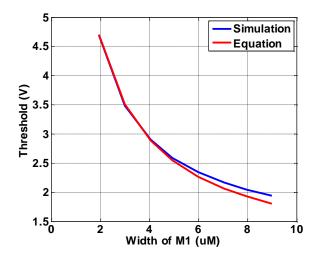

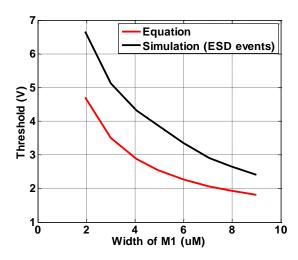

| Figure 2-12. | Threshold variation for positive event detector as width of M1 is varied16                                                     |

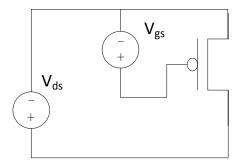

| Figure 2-13. | Simulation schematic for getting characteristic curves for the PFET18                                                          |

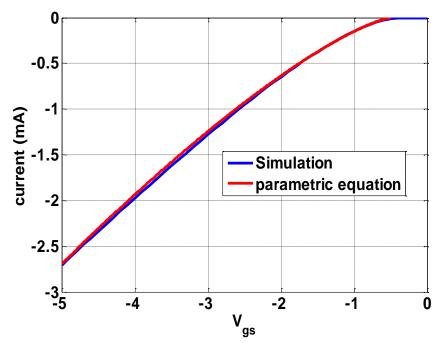

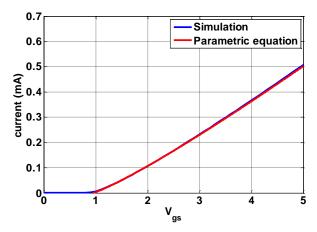

| Figure 2-14. | Comparison of Vgs-Idrain curve from simulations and parametric equation for 9u/0.6u PFET                                       |

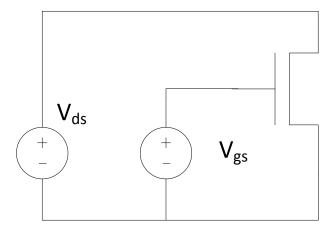

| Figure 2-15. | Simulation schematic for getting V-I curves for the NFET                                                                       |

| Figure 2-16. | NFET drain current comparison in saturation region with equation and simulation results for 1.5u/0.6u NFET                     |

| Figure 2-17. | Comparison for NFET V <sub>ds</sub> Vs I <sub>drain</sub> curve and approximations from Alpha-power model                      |

| Figure 2-18. | Response of positive event detector to slow event with 300 ns rise time while Vdd(die) and Vss(die) are held at a constant 5 V |

| Figure 2-19. | Comparison of thresholds for positive indicators from simulations and Alpha-power law when Vdd(die)-Vss(die)=constant          |

| Figure 2-20. | Comparison of thresholds for positive event indicators from simulations and Alpha power law when Vdd(die)-Vss(die) is not constant23               |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-21. | Negative event indicator24                                                                                                                         |

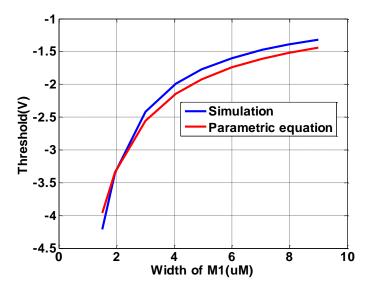

| Figure 2-22. | Comparison of thresholds for negative event indicators from simulations and Alpha power law when Vdd(die)-Vss(die)=constant25                      |

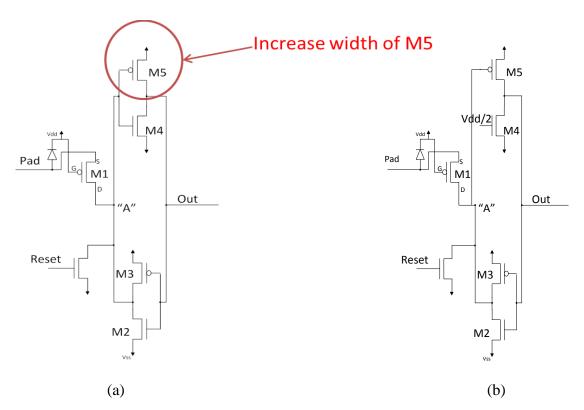

| Figure 2-23. | Methods to achieve proportionality between switching threshold of M4-M5 inverter and Vdd(die)26                                                    |

| Figure 2-24. | Comparison between positive event thresholds for slow and ESD events when M5=6u wide                                                               |

| Figure 2-25. | Comparison between positive event thresholds for slow and ESD events when M5=20u wide                                                              |

| Figure 2-26. | Positive event indicator with M4-M5 inverter with current source load29                                                                            |

| Figure 2-27. | Comparison of positive event indicator thresholds for slow and ESD events for M4-M5 inverter having M4 as current source load30                    |

| Figure 2-28. | Positive event indicator with M4 as current source load and optimizations to have minimal static current consumption31                             |

| Figure 2-29. | Comparison of thresholds for slow and ESD events                                                                                                   |

| Figure 2-30. | Self-triggered oscillator for measuring energy in a transient event34                                                                              |

| Figure 2-31. | Windowed oscillator for measuring voltage of transient events35                                                                                    |

| Figure 2-32. | The RC-based oscillator stores the maximum pad voltage on a capacitor and then counts the number of oscillations while the capacitor is discharged |

| Figure 2-33. | General simulation model for testing different circuits36                                                                                          |

| Figure 2-34. | Simulation setup for self-triggered oscillator                                                                                                     |

| Figure 2-35. | Response of self-triggered oscillator to slow events with Vdd(die)-Vss(die) = constant                                                             |

| Figure 2-36. | Response of self-triggered oscillator with Vdd(die)-Vss(die)=constant39                                                                            |

| Figure 2-37. | Comparison of output counts for self-triggered oscillator for slow rise/fall time and for positive ESD events when Vdd(die)-Vss(die)=constant40    |

| Figure 2-38. | Response of self-triggered oscillator during a slow event when Vdd(die)-Vss(die) is not constant            |

|--------------|-------------------------------------------------------------------------------------------------------------|

| Figure 2-39. | Response of self-triggered oscillator during an ESD event when Vdd(die)-Vss(die) is not constant            |

| Figure 2-40. | Comparison of output counts for cases with and without Vdd(die)-Vss(die)=constant41                         |

| Figure 2-41. | Windowed oscillator level sensor                                                                            |

| Figure 2-42. | Implementation of the out-of-range voltage detector                                                         |

| Figure 2-43. | Implementation of delay line                                                                                |

| Figure 2-44. | The delay line has a 115ns delay from input to output                                                       |

| Figure 2-45. | XOR gate implementation                                                                                     |

| Figure 2-46. | Oscillator implementation                                                                                   |

| Figure 2-47. | Variation of ocillator output frequency with the control voltage45                                          |

| Figure 2-48. | Response of windowed oscillator to slow event when Vdd(die)-Vss(die)=constant46                             |

| Figure 2-49. | Response of windowed oscillator to ESD events when Vdd(die)-Vss(die)=constant                               |

| Figure 2-50. | Comparison of output counts of windowed oscillator for slow and ESD events while Vdd(die)-Vss(die)=constant |

| •            | Comparison of windowed oscillator output counts with and without having Vdd(die)-Vss(die)=constant49        |

| Figure 2-52. | Basic concept for determining peak level of the event using the RC-based oscillator                         |

| Figure 2-53. | Response of RC-based oscillator to slow transient events                                                    |

| Figure 2-54. | Response of RC-based oscillator to ESD event53                                                              |

| Figure 2-55. | Comparison of output counts for RC-based oscillator for slow and ESD events                                 |

| Figure 2-56. | Comparison of output counts for cases with and without Vdd(die)-Vss(die)=constant for RC-based oscillator   |

| Figure 2-57. | Comparison of output counts for RC-based oscillator for slow and ESD evemts when Vdd(die)-Vss(die) =constant | .55 |

|--------------|--------------------------------------------------------------------------------------------------------------|-----|

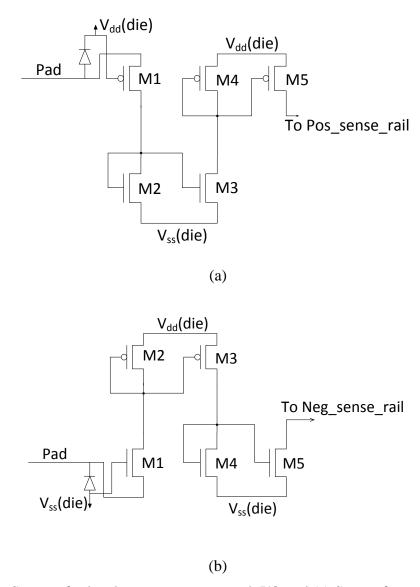

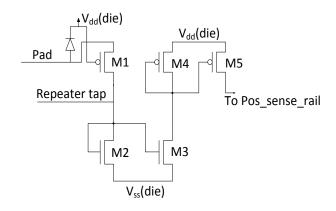

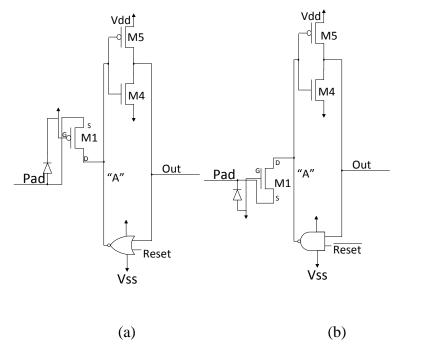

| Figure 3-1.  | ESD protection diodes on I/O pad and PFET connected across positive event diode                              |     |

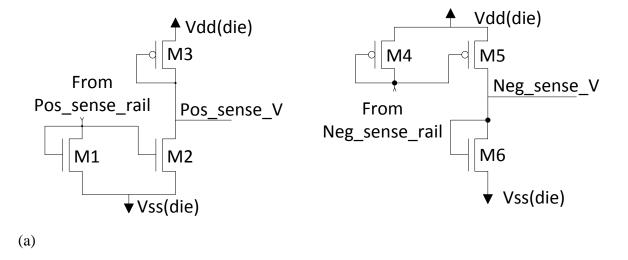

| Figure 3-2.  | Event indicators based on out-of-range voltage detector                                                      | .60 |

| Figure 3-3.  | Sensors for level measurement at each I/O pad                                                                | .61 |

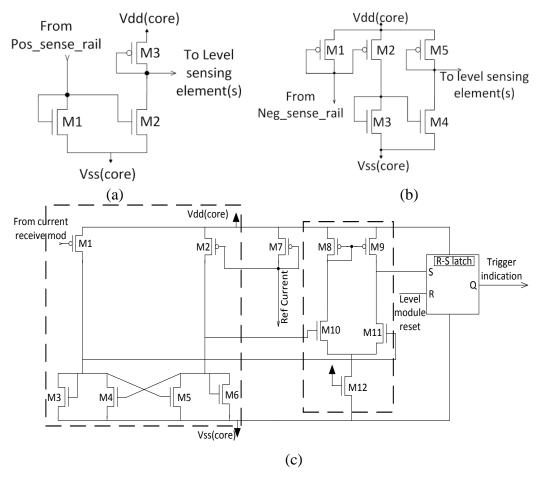

| Figure 3-4.  | Parts of level detection module                                                                              | .62 |

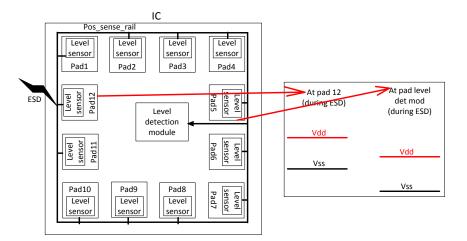

| Figure 3-5.  | Scenario of positive ESD event and behavior of local PDN at different points on IC                           | .64 |

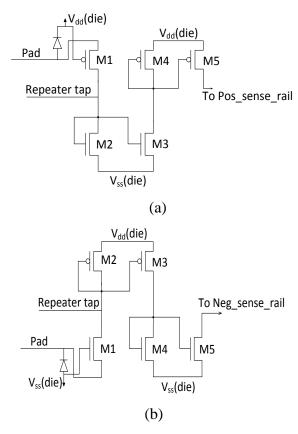

| Figure 3-6.  | Modified level sensors                                                                                       | .65 |

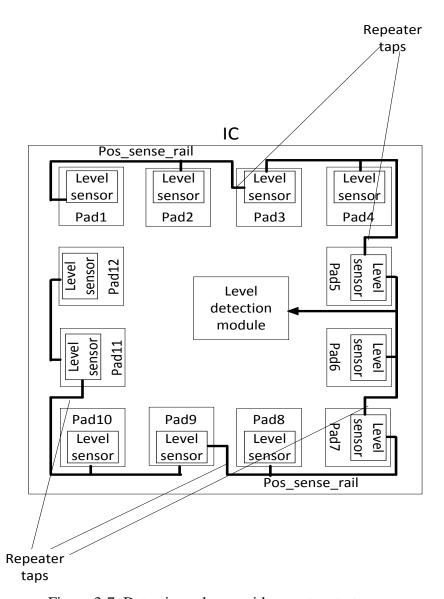

| Figure 3-7.  | Detection scheme with repeater strategy                                                                      | .66 |

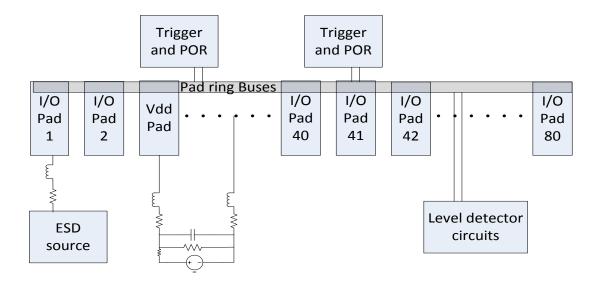

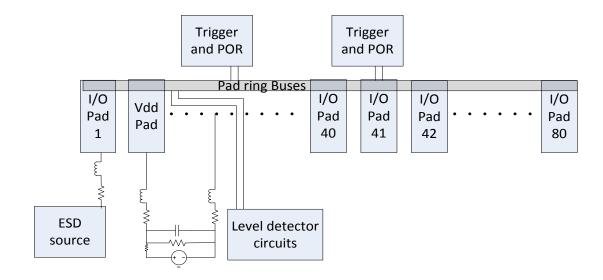

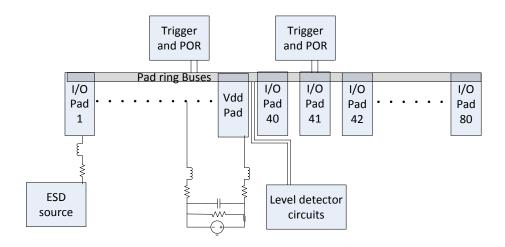

| Figure 3-8.  | Full simulation model                                                                                        | .68 |

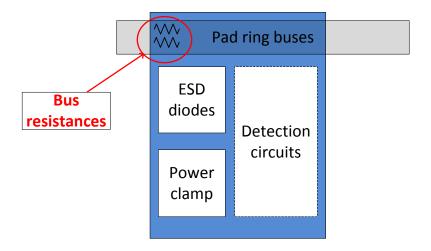

| Figure 3-9.  | I/O pad contents in the simulation model                                                                     | .68 |

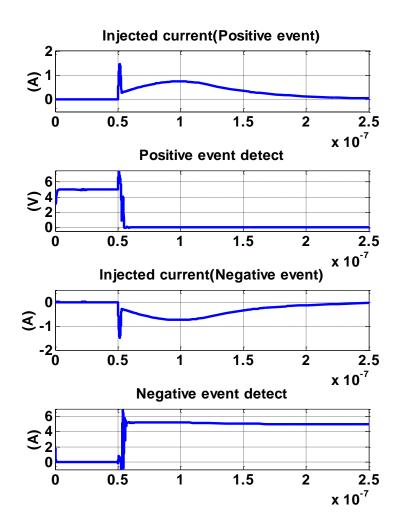

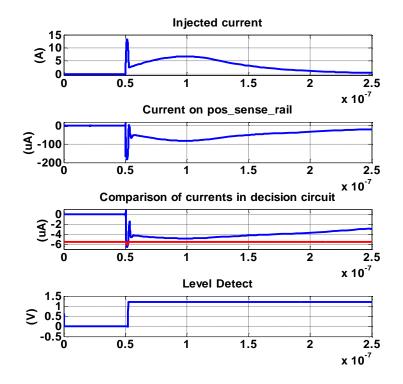

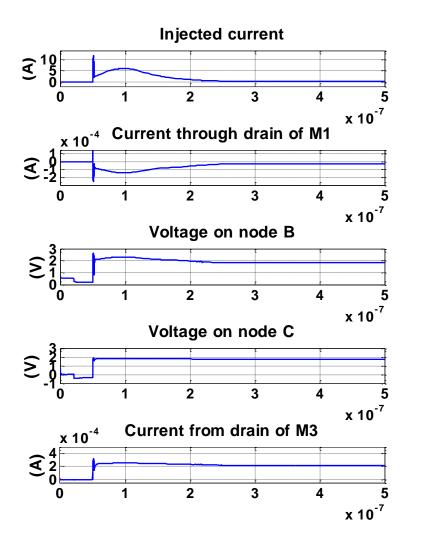

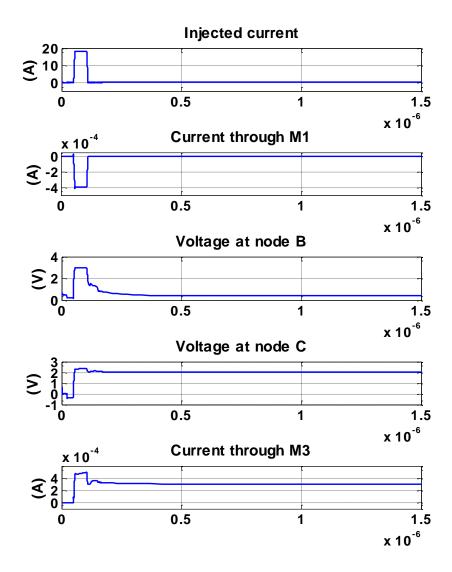

| Figure 3-10. | Detection signals for positive and negative 500 V ESD events                                                 | .69 |

| Figure 3-11. | Initial tests of level sensors placed zapped pad, level detector, and Vdd pad next to one another            | .70 |

| Figure 3-12. | Positive event level sensor schematic                                                                        | .71 |

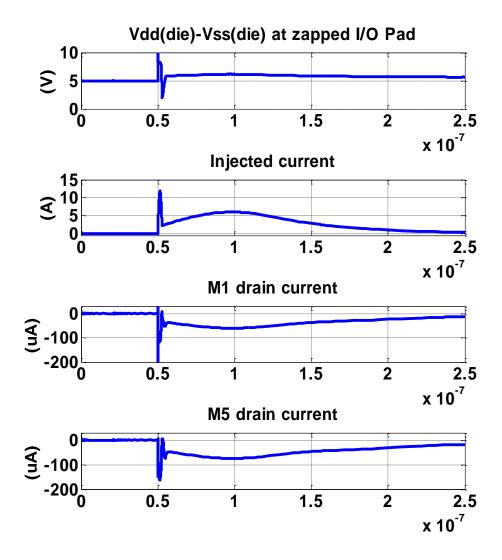

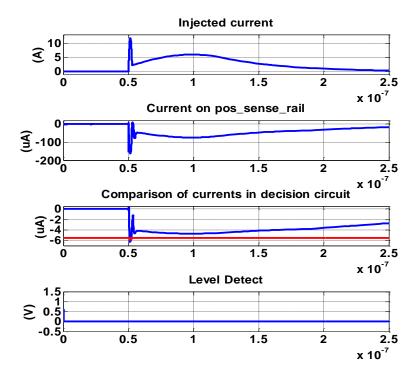

| Figure 3-13. | Response of level sensor to a 4 kV ESD event                                                                 | .72 |

| Figure 3-14. | Response of level detector module to a 4 kV ESD event                                                        | .73 |

| Figure 3-15. | Response of level detector module to a 4.5 kV ESD event                                                      | .73 |

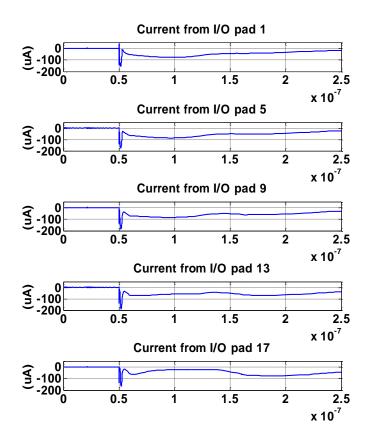

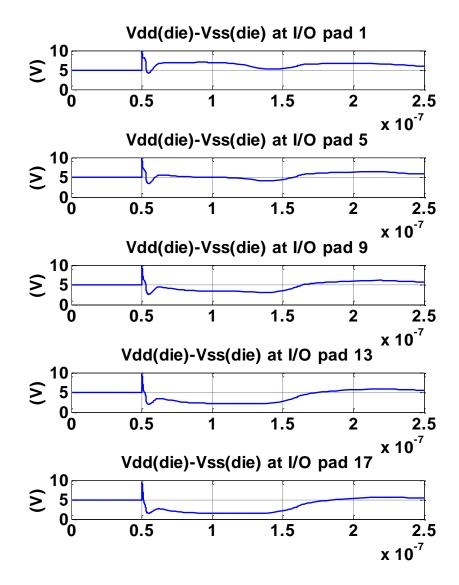

| Figure 3-16. | Simulation model when the zapped I/O pad was 40 pads away from Vdd and the level detector circuits           | .74 |

| Figure 3-17. | Currents at output of repeaters during a 4 kV ESD event                                                      | .74 |

| Figure 3-18. | Vdd(die)- Vss(die) at the repeater locations during an ESD event                                             | .75 |

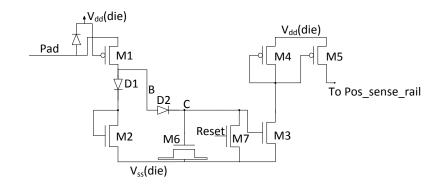

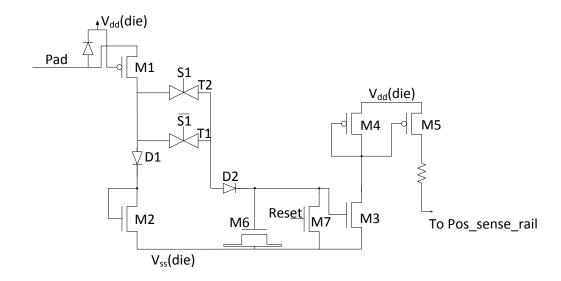

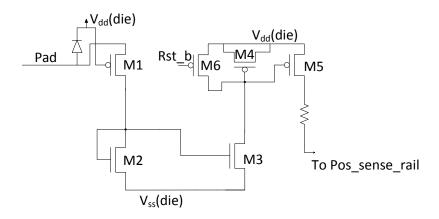

| Figure 3-19. | Sample and hold level sensors                                                                                | .77 |

| Figure 3-20. | Current to voltage converter circuits                                                                        | .79 |

| Figure 3-21. | Event indicators                                                                                             | .79 |

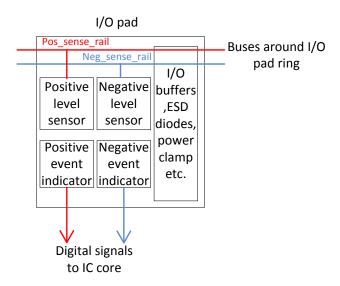

| Figure 3-22.                                                     | Circuit components in I/O pad for sample and hold detection scheme80                               |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Figure 3-23.                                                     | I/O pad ring for sample and hold detection scheme81                                                |

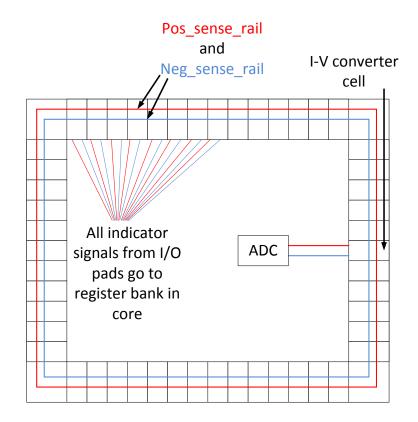

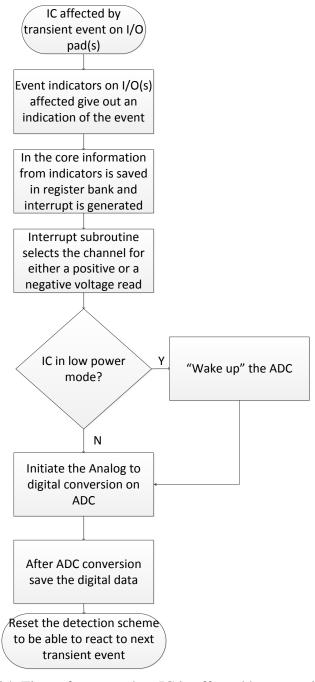

| Figure 3-24.                                                     | Flow of events when IC is affected by a transient event                                            |

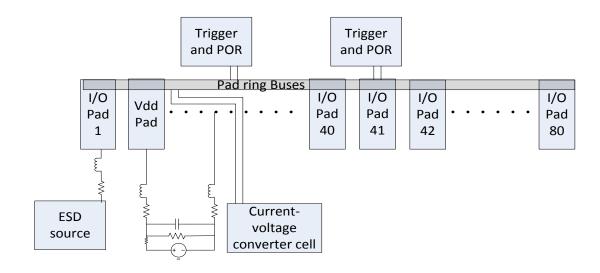

| Figure 3-25.                                                     | Simulation setup for testing sample and hold detection scheme83                                    |

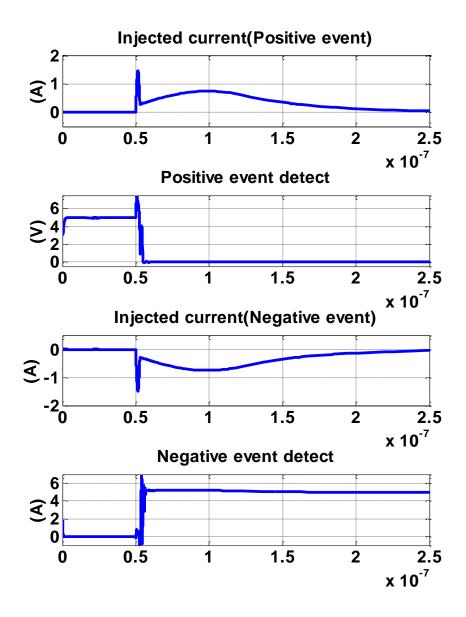

| Figure 3-26.                                                     | Positive and negative events injected on I/O pad and detected by the respective indicators         |

| Figure 3-27.                                                     | Simulation of event indicators with slow events to get quantitative measure of switching threshold |

| Figure 3-28.                                                     | Switching threshold of positive event indicator in terms of injected current                       |

| Figure 3-29.                                                     | Switching threshold of positive event indicator in terms of pad voltage relative to Vdd            |

| Figure 3-30.                                                     | Switching threshold of negative event indicator in terms of injected current                       |

| Figure 3-31.                                                     | Switching threshold of negative event indicator in terms of pad voltage                            |

|                                                                  | relative to Vdd                                                                                    |

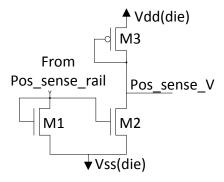

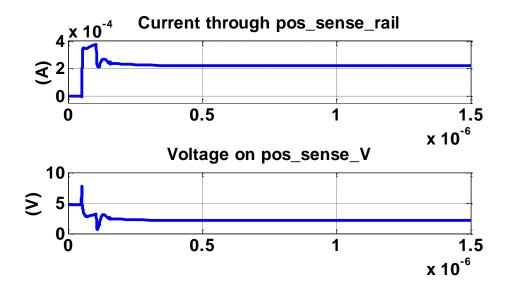

| Figure 3-32.                                                     | Positive event level sensor                                                                        |

|                                                                  |                                                                                                    |

| Figure 3-33.                                                     | Positive event level sensor                                                                        |

| Figure 3-33. Figure 3-34.                                        | Positive event level sensor                                                                        |

| Figure 3-33. Figure 3-34. Figure 3-35.                           | Positive event level sensor                                                                        |

| Figure 3-33. Figure 3-34. Figure 3-35. Figure 3-36.              | Positive event level sensor                                                                        |

| Figure 3-33. Figure 3-34. Figure 3-35. Figure 3-36. Figure 3-37. | Positive event level sensor                                                                        |

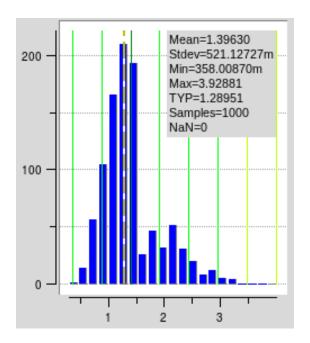

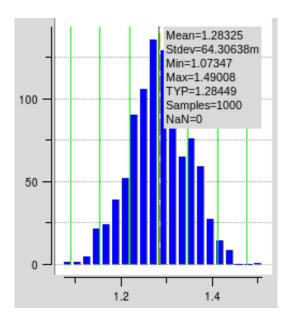

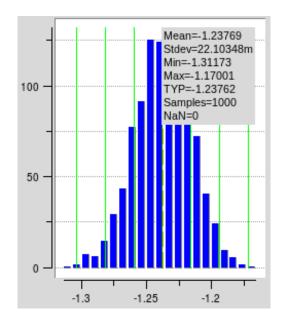

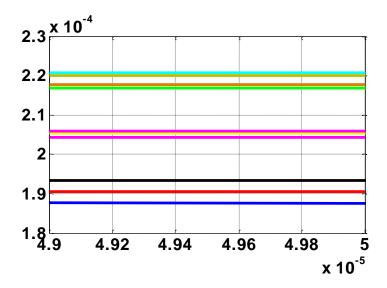

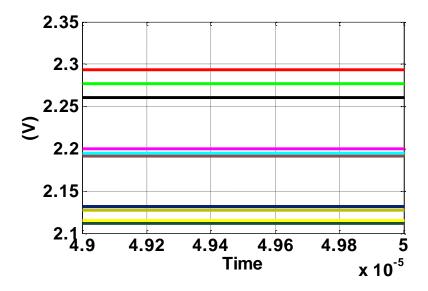

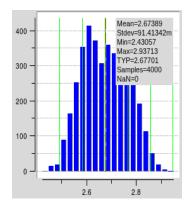

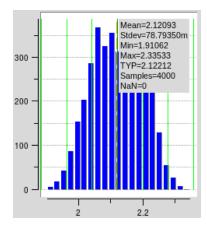

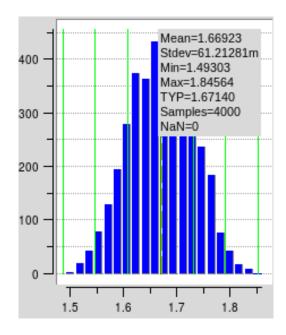

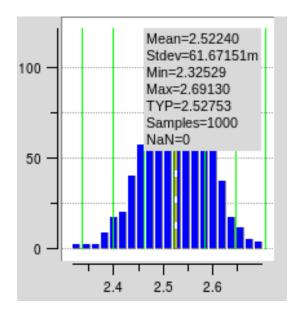

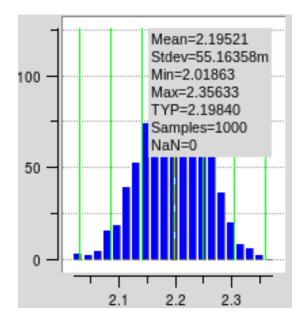

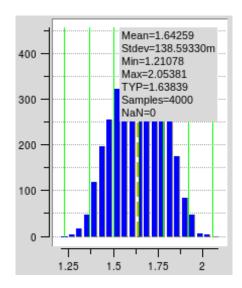

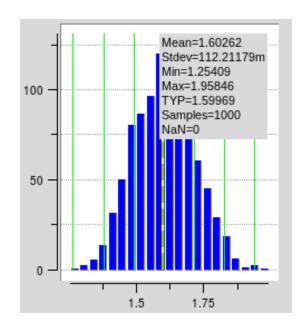

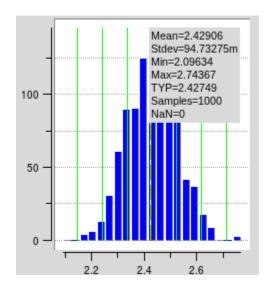

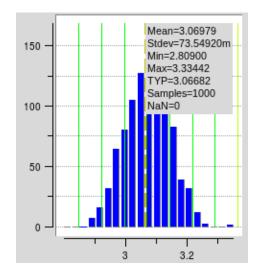

| Figure 3-40. | Monte Carlo simulation results for output voltage variations from detector and converter due to process variations as well as rise time and pulse width variations of 12 A peak events |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

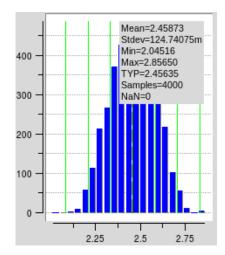

| Figure 3-41. | Monte Carlo simulation results for output voltage variations from detector and converter due to process variations as well as rise time and pulse width variations of 18 A peak events |

| Figure 3-42. | Monte Carlo simulation results for output voltage variations from detector and converter due to process variations as well as rise time and pulse width variations of 2kV ESD events   |

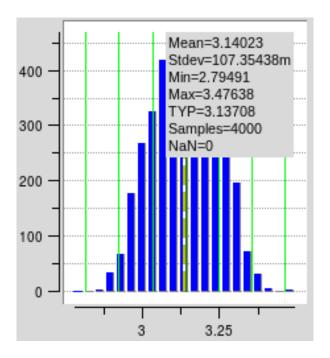

| Figure 3-43. | Monte Carlo simulation results for output voltage variations from detector and converter due to process variations as well as rise time and pulse width variations of 4kV ESD events   |

| Figure 3-44. | Monte Carlo simulation results for output voltage variations from detector and converter due to process variations as well as rise time and pulse width variations of 6kV ESD events   |

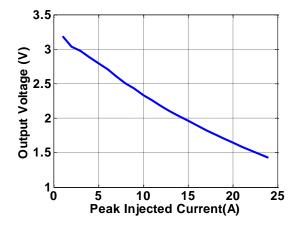

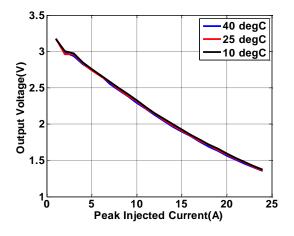

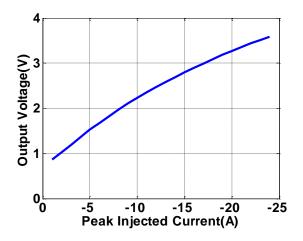

| Figure 3-45. | Output voltage for positive events as injected peak current is varied97                                                                                                                |

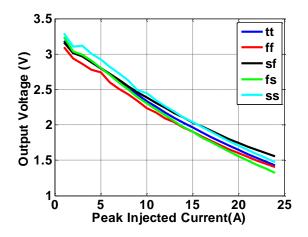

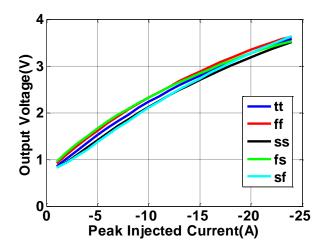

| Figure 3-46. | Output voltage curve variation with process corners98                                                                                                                                  |

| Figure 3-47. | Output voltage curve variation with testing lab temperature98                                                                                                                          |

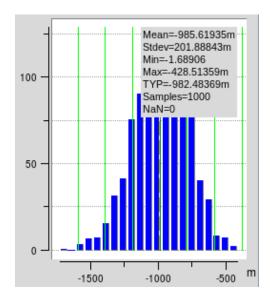

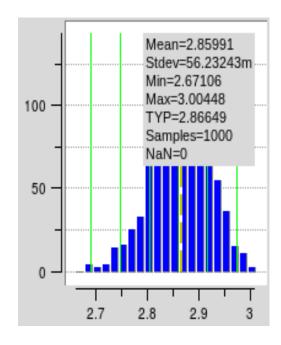

| Figure 3-48. | Monte Carlo simulation results for output voltage variations due to process variations as well as rise time and pulse width variations of -6 A peak events                             |

| Figure 3-49. | Monte Carlo simulation results for output voltage variations due to process variations as well as rise time and pulse width variations of -12 A peak events                            |

| Figure 3-50. | Monte Carlo simulation results for output voltage variations due to process variations as well as rise time and pulse width variations of -18 A peak events                            |

| Figure 3-51. | Monte Carlo simulation results for output voltage variations due to process variations as well as rise time and pulse width variations of -2 kV ESD events                             |

| Figure 3-52. | Monte Carlo simulation results for output voltage variations due to process variations as well as rise time and pulse width variations of -4 kV ESD events                             |

| Figure 3-53. | Monte Carlo simulation results for output voltage variations due to process variations as well as rise time and pulse width variations of -6 kV ESD events |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-54. | Output voltage for negative events as injected peak current is varied102                                                                                   |

| Figure 3-55. | Negative events output voltage curve variation for with process corners.102                                                                                |

| Figure 3-56. | Negative events output voltage curve variation for with lab temperature 103                                                                                |

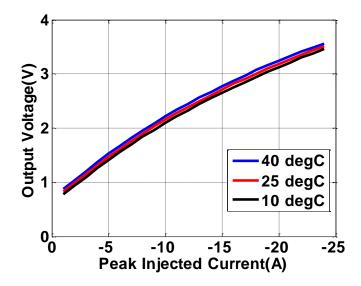

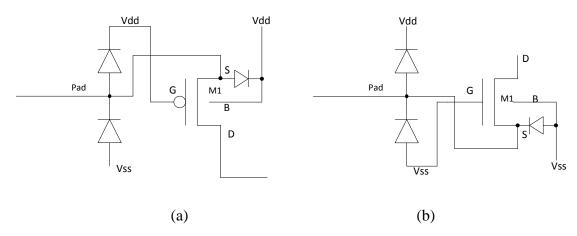

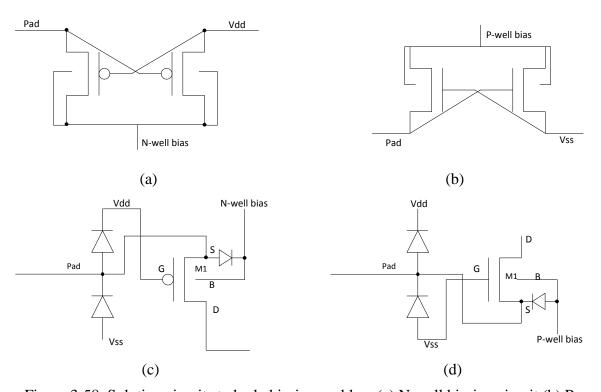

| Figure 3-57. | Parasitic diodes between body and substrate for PFETs and NFETs connected to I/O pads                                                                      |

| Figure 3-58. | Solution circuits to body biasing problem                                                                                                                  |

| Figure 3-59. | Level sensors with current limiting resistor                                                                                                               |

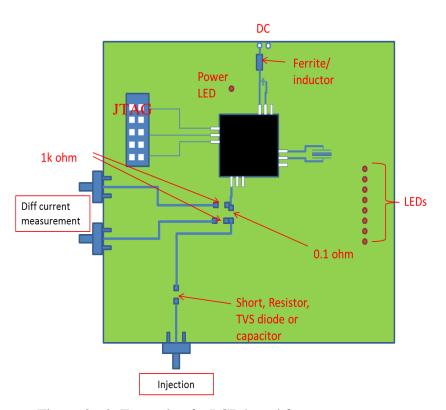

| Figure 3-60. | Example of a PCB board for measurement setup113                                                                                                            |

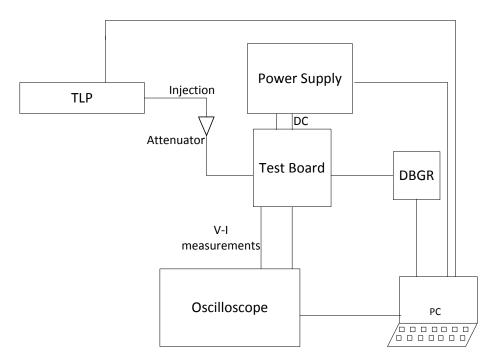

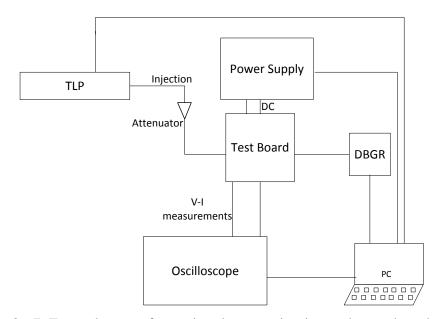

| Figure 3-61. | Example setup for testing detector circuits on test board                                                                                                  |

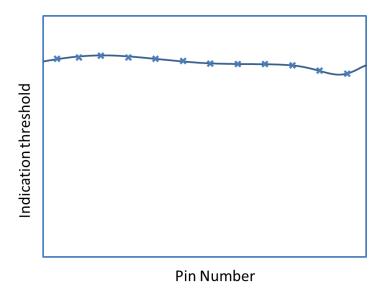

| Figure 3-62. | Example pin number to indication threshold map119                                                                                                          |

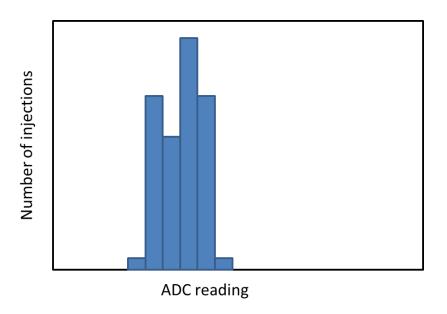

| Figure 3-63. | Example histogram created for a particular level of injection on a particular test pin                                                                     |

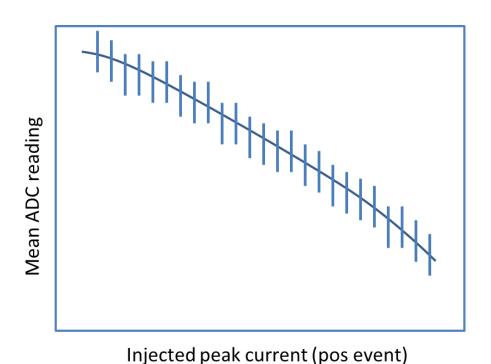

| Figure 3-64. | Example plot of ADC reading vs injected peak current with error bars included                                                                              |

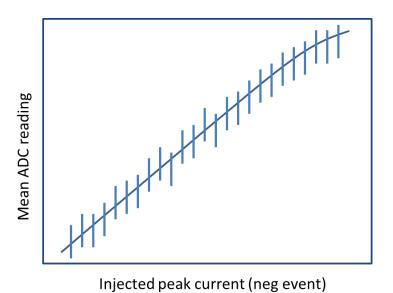

| Figure 3-65. | Example plot of ADC reading vs injected peak currents with error bars included                                                                             |

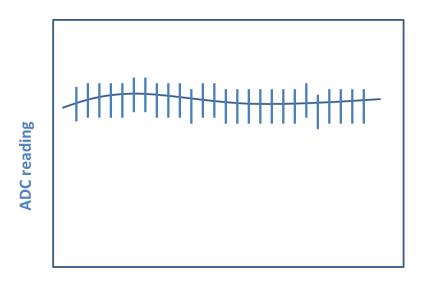

| Figure 3-66. | Example ADC reading vs pin number map created for a particular level of injection                                                                          |

| Figure 3-67. | Example setup for testing detector circuits on the test board124                                                                                           |

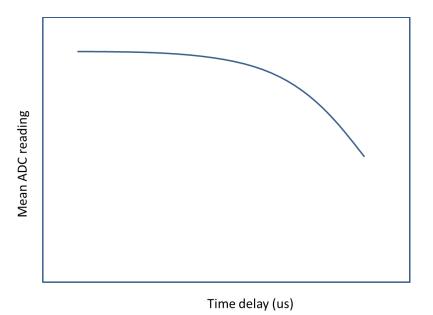

| Figure 3-68. | Example ADC reading vs time delay plot created for a particular level of injection on a particular test pin                                                |

| Figure 4-1.  | Positive event level sensor with filtering                                                                                                                 |

| Figure 4-2.  | Positive event level sensor with integration                                                                                                               |

### 1 INTRODUCTION

Immunity to transient events like ESD is a growing concern for electromagnetic compatibility (EMC) engineers in industry today. Isolating the component responsible for the error and debugging the error is a time intensive process which is becoming increasingly difficult with the shrinking size of embedded systems. This report presents the design of a set of circuits that can be implemented on-die to determine the I/O pin/pad affected by the transient event as well as approximate the level of transient event affecting the IC. The circuit was built to be relatively inexpensive (i.e. consume little area) and consume negligible static power. Such a detection scheme can allow: determination of specific (on-die) failure points and levels, reduced testing and debugging time and cost for both the IC manufacturer and customers, identification of the path taken by transient events on a system level, ESD protection circuit characterization, in-application event capture, error mitigation through defensive programming in response to an event, and prediction of IC lifespan and maintenance intervals based on the number and size of transient events encountered.

Section 1.1 discusses general need of a transient event detection scheme on ICs and previous work done on this. Section 1.2 describes technical details of research and simulation methods used throughout the project. Some designs developed in early part of the project are discussed in Section 2. These designs have few known shortcomings, discussed at the end of Section 2. To overcome shortcomings of circuits in Section 2, improved designs were developed which are discussed in Section 3.

#### 1.1 BACKGROUND

The increasing in complexity of circuits on an integrated circuit (IC), the decreasing size of transistors, and the decreasing supply voltage and associated noise margins makes the ICs increasingly susceptible to failures from transient events like electrostatic discharge (ESD) [1]. Typical problems include temporary disruption of the IC, semi-permanent failures that can be solved by resetting the IC or re-powering the IC, and permanent failures like transistor burnout due to latch-up, leading to lower production yields, lower product reliability and higher manufacturing cost.

ICs are generally equipped with ESD protection which is designed to route the current away from I/O transistors to power rails and out of the IC. These circuits are solely designed for preventing damage to the IC and give no direct information to the user about a transient event and how it affects the IC. If a system with multiple ICs is affected by an ESD event it is often difficult to isolate which IC caused the system to fail. The debugging procedure might require special setups and measurements to determine which IC was affected and how was it affected, so that necessary steps can be taken to protect against future failures. These measurements can be time consuming and expensive and, in some systems, impossible to perform since the presence of the test equipment itself modifies the system's response to the transient event.

The idea behind the work presented here is to enable the IC itself to record information about the transient disturbance. Few techniques exist in the literature for providing a similar measurement. Methods were suggested in [2] to determine the presence of an electromagnetic-induced error using software which monitors critical registers in a programmable IC. This method, though elegant, only gives information

about particular soft-errors and depends upon the software to work perfectly to give out an error indication. The software method gives limited information to help in root cause analysis of the ESD disturbance.

Some techniques for reporting the presence of a transient disturbance of the power supply have also been reported. For example the technique presented in [3][4] monitors the power distribution network (PDN) for noise and gives an indication of an irregular supply. The peak noise level can be saved using a sample and hold circuit. In [5], a voltage monitor circuit is developed which stores the peak voltage of the event on a capacitor, which is later measured externally through a pin on the IC. Circuits in [6][7] measure the level of the voltage disturbance on the PDN to approximate the level of the transient event.

All these circuits give information regarding some aspect of the transient event but do not give information about which I/O pins were affected by a particular event. They also provide very limited information about the level of disturbance entering the IC. The sensors designed in the following report are intended to give both pieces of information. There is no need for the user to measure anything. The measurements are made on-die. Software only has to be built to read the information and use it. Since the information is easily obtainable in software, corrective measures can also be taken to defend against soft-errors caused by a transient event in the field – for example, by performing a memory check or restoring the code to a known safe state after the event has occurred. The circuits developed here were designed to give consistent readings for a variety of transient events. The level of the reading does not depend upon the rise time or

duration of the transient disturbance seen by the IC, only the peak value of the input voltage.

### 1.2 METHODOLOGY

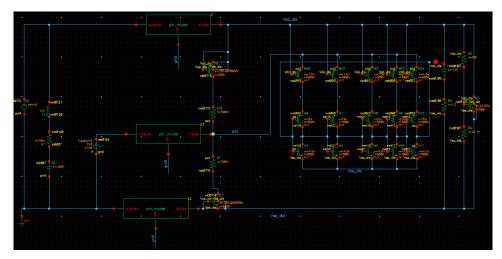

The transient event sensors were developed using a simulate and verify approach. Simulations were done in Cadence Virtuoso custom IC design software. Models used for simulations were chosen so as to approximate actual IC and test hardware as closely as possible. Models include approximations of PCB components, pin and package parasitics, on-die ESD protection circuits, load on the IC, on-die decoupling capacitors and as ESD gun model which is used to inject I/O pads with ESD events in order to test the working of the detector circuits. During the initial phase of the project, a publicly available technology library (AMI06 from NCSU) was used for design and proof of concept simulations. This technology library was used for "Initial designs" in Section 2. Later designs, discussed in Section 3, used a 90 nm technology from Freescale that will be used in a future test IC. Since a test IC will be developed from this work and much of the technology library is available for this technology, the simulations include technology and IC specific models of ESD protection structures. These simulations provide a comprehensive idea of how these circuits will perform in the final implementation.

#### 2 INTIAL DESIGNS

During the development of the measurement scheme for transient events, several detection and measurement strategies were explored which did not make it to the final test IC. These initial designs are discussed in the following section. Section 2.1 describes out-of-range voltage detectors which can measure transient events based on voltages on I/O pads. The measurement of the event is based on the voltage on an I/O pad going above or below the power supply voltage. Section 2.2 discusses oscillators for measuring the level of transient events. The number of output oscillations depends upon the level of the transient event. Counting the number of oscillations can be used to determine the level of the transient events. At the end of Sections 2.1 and 2.2 some known or foreseen issues are discussed. The circuits ultimately making it to the hardware testing phase, described in Section 3, were developed, in part, to get around these known issues.

### 2.1 OUT-OF-RANGE VOLTAGE DETECTORS

When an I/O pad is affected by an ESD event, the voltage on the I/O pad either goes higher than Vdd and current is injected into the pad (positive event) or the voltage on the pad goes below Vss and current is drawn from the pad (negative event). Detectors in this section are designed to react to such abnormal voltages on the I/O pad.

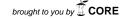

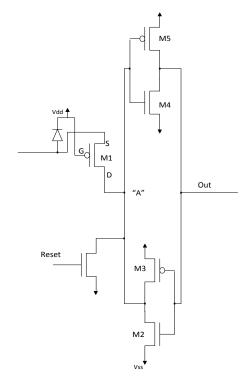

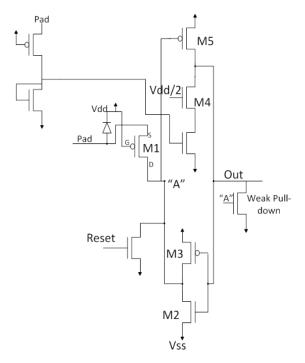

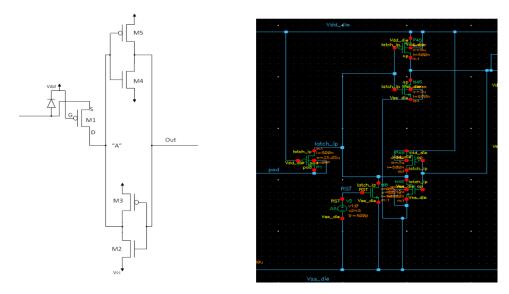

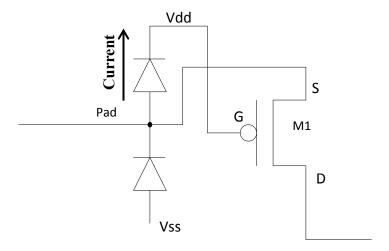

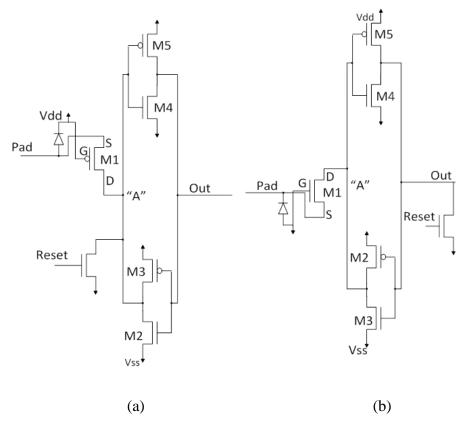

**2.1.1** Concept and Schematics. Transistor M1 in Fig. 2-1 performs the essential detection of an overvoltage event. During a positive transient event the I/O pad voltage goes higher than the Vdd voltage and current flows through the ESD protection diode. If the voltage drop from the pad to Vdd is above a threshold voltage, the P-channel

MOSFET (PFET – transistor M1) between the I/O pad and Vdd net will be turned on, thus supplying current to the FET drain.

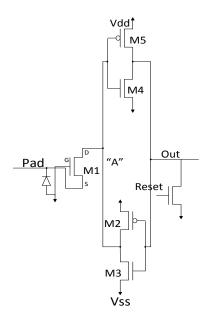

Figure 2-1. ESD protection at I/O pads and "Driving FET" M1

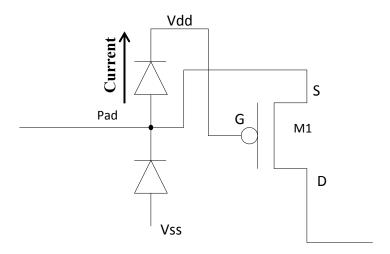

Transistor M1drives a latch circuit as shown in Fig. 2-2. The current driven by M1 is directly related to the voltage across the diode (i.e.  $V_{GS}$ ), which is directly related to the current through the ESD protection diode. Accordingly, the node connected to the drain of M1 is being pulled up towards Vdd. This node will remain high only during the event, while current flows through the diode. The passing of this event can be saved in a latch and read out later.

Transistor M1 has to pull the node "A" high when M2 is "on" and weakly pulls down the node. The amount of current required to flip the latch depends on the pull-down strength of M2 compared to the pull-up strength of M1. By varying the size of M1 and M2, as well as the switching threshold of the inverter formed by M4 and M5, the

threshold of the latch can be controlled. This theory can be explained mathematically as shown below in equation (2.1).

Figure 2-2. Positive event indicator

At the point where the latch switches state, node "A" has to reach the switching threshold of inverter M4-M5. This voltage will be called V<sub>"A",sw</sub>. Since only M1 and M2 drive node "A", their drain currents are equal. At the switching point, M1 will be in saturation and M2 will be in linear mode. Equating the drain currents of M1 and M2 gives:

$$k'_{p} \left(\frac{W}{L}\right)_{M1} \left[ \left(V_{dd} - V_{pad} - V_{t,p}\right) V_{dsat} - \frac{V_{dsat}^{2}}{2} \right] = k'_{n} \left(\frac{W}{L}\right)_{M2} \left[ \left(V_{op} - V_{ss} - V_{t,n}\right) \left(V_{A''} - V_{ss}\right) - \frac{\left(V_{A''} - V_{ss}\right)^{2}}{2} \right]$$

(2.1)

where  $k'_p$  and  $k'_n$  are the process trans-conductance for the PFET and NFET, respectively,  $(W/L)_{M1}$  and  $(W/L)_{M2}$  are the width to length ratios of M1 and M2, respectively,  $V_{pad}$  is the voltage at the pad,  $V_{"A"}$  is the voltage at node "A", and  $V_{t,p}$  and  $V_{t,p}$  are the threshold voltages for the PFET and NFET, respectively.

Solving (2-1), the latch switching voltage at the pad,  $V_{pad,sw}$ , where  $V_{"A"}$  reaches  $V_{"A",sw}$  is given by:

$$-V_{pad} = V_{t,p} + \frac{V_{dsat}}{2} - V_{dd} + \left\{ \frac{k'_{n}}{k'_{p}} \left( \frac{W}{L} \right)_{M2} \left( \frac{L}{W} \right)_{M1} \frac{1}{V_{dsat}} \left[ \left( V_{op} - V_{ss} - V_{t,n} \right) \left( V_{"A",sw} - V_{ss} \right) - \frac{\left( V_{"A",sw} - V_{ss} \right)^{2}}{2} \right] \right\}$$

(2.2)

The parameters on the right hand side of the equation, except  $(W/L)_{M2}$  and  $(L/W)_{M1}$ , are process parameters which are constants. Hence, the pad voltage at which the latch triggers can be controlled by changing the widths and lengths of M1 and M2.

Detecting the presence of the event can be done by creating a relatively low trigger voltage. The level of the event can be determined using multiple instances of such circuits with different trigger thresholds (e.g. one for 1 V above Vdd, one for 2 V above Vdd, etc.). The level of the ESD event can be estimated from which of the latches were triggered.

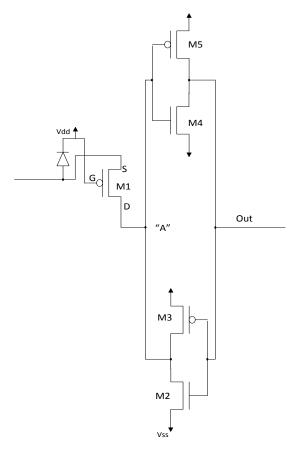

A similar circuit can be built for negative events, as shown in Fig. 2-3. In this case the pad voltage drops below  $V_{\rm ss}$ .

Figure 2-3. Negative event indicator

The corresponding equation for switching threshold of the negative event indicator in Fig. 2-3 is:

$$-V_{pad} = V_{t,n} + \frac{V_{dsat}}{2} - V_{ss} + \left\{ \frac{k'_{p}}{k'_{n}} \left( \frac{W}{L} \right)_{M2} \left( \frac{L}{W} \right)_{M1} \frac{1}{V_{dsat}} \left[ \left( V_{op} - V_{dd} - V_{t,p} \right) \left( V_{A'',sw} - V_{dd} \right) - \frac{\left( V_{A'',sw} - V_{dd} \right)^{2}}{2} \right] \right\}$$

(2.3)

A reset transistor should be added to these latches as shown in Fig. 2-4 and Fig. 2-5 to ensure the correct state of the latch at power-up and to allow detection of multiple events.

Figure 2-4. Positive event indicator with reset functionality

Figure 2-5. Negative event indicator with reset functionality

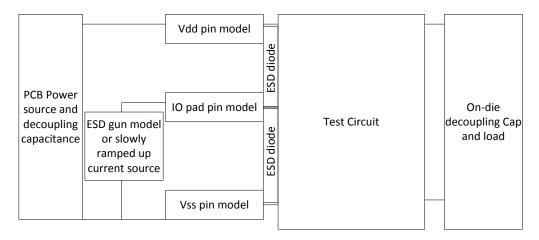

2.1.2 Simulation Models. A simulation model was constructed to provide a realistic representation of the voltage and current that would be experienced at the pad and across the on-die PDN during a transient event. Initial simulations excluded the PDN bus resistances and the characteristics of the on-die power clamps. These circuit elements, though important, were not required to test the basic functionality of this circuit.

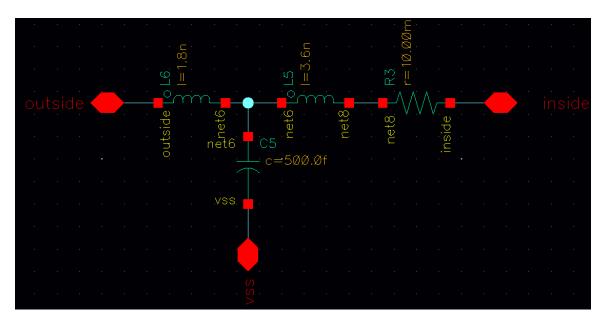

The ESD gun model use to inject the test circuit with ESD events is shown in Fig. 2-6. This model is similar to one developed in [8]. This circuit gives a good approximation of IEC-61000-4-2 ESD pulse. IO pin and pad parasitics are approximated using a lumped element model as shown in Fig. 2-7. The approximation includes bondwire and pin inductance, the capacitance of pins to ground, and the series resistance of the pin. This model is based on the package model developed from measurements of a Freescale microcontroller in [9]. The entire IC model used in the initial simulations is shown in Fig. 2-8.

Figure 2-6. ESD gun model in Cadence Virtuoso used to generate IEC-6100-4-2 type pulses

Figure 2-7. Pin parasitic model in Cadence Virtuoso

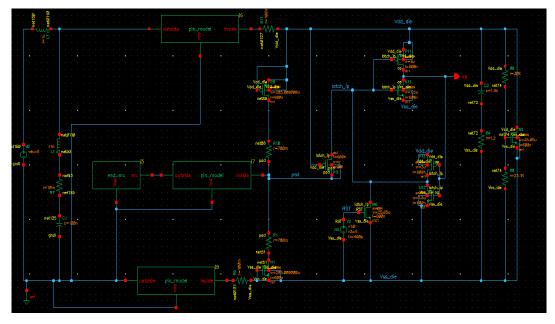

Figure 2-8. Complete simulation model formed in Cadence Virtuoso for testing different circuits

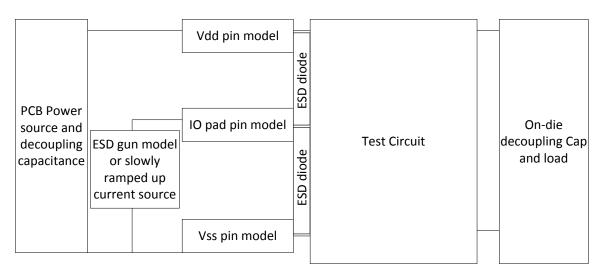

The simulation model is described in a block diagram in Fig. 2-9. The parts of the simulation, starting from the left, are: the on-board 5 V supply, decoupling capacitance

100 nF, ESD protection diodes, test circuit and finally, on the right, the on die decoupling capacitance and a current load approximating the IC current consumption. The behavior of PDN voltages is different on-board than on-die due to the pin parasitics. In this paper, discussions of Vdd/Vss refer to the Vdd/Vss on die since those are the supplies affecting the circuit under study.

Figure 2-9. General simulation model for any test circuit

## 2.1.3 Simulation Results and Analysis. The positive event detector, shown in

Fig. 2-10, was tested first. The size of the transistors was:

M1: 9 um/0.6 um M2: 1.5 um/0.6 um M3: 3 um/0.6 um M4: 1.5 um/0.6 um M5: 6 um/0.6 um

(Note: Sizes are specified as width/length.)

Figure 2-10. Positive event detector used for simulations

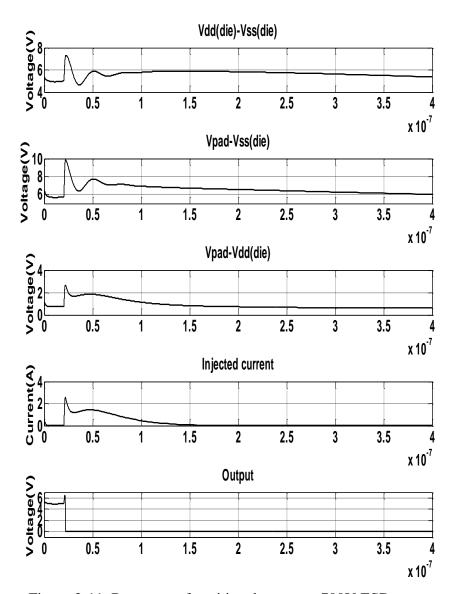

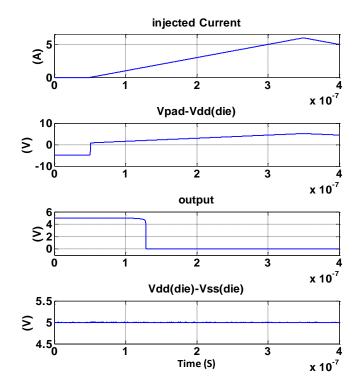

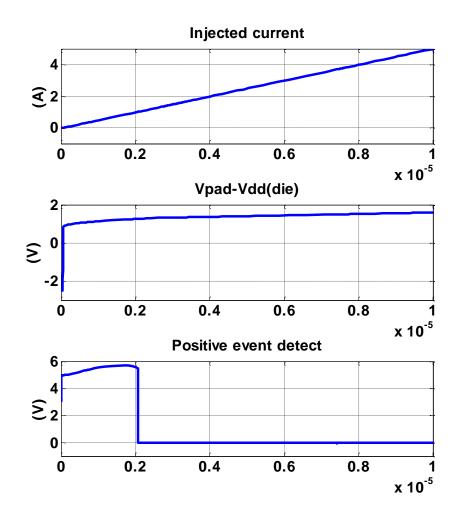

Figure 2-11 shows an example simulation when the I/O pad was injected with a 700 V event (i.e. the ESD gun capacitor was charged to 700 V before discharge). A 700 V event injects about 2.5A of current into the IO pad. Event capture is successful since the output of the detector switches from a high (5 V) to a low (0 V) when the ESD event disturbs the I/O pad. The PDN on the IC, depicted by Vdd\_die and Vss\_die, is disturbed momentarily during the ESD event due to current routed from the I/O pad to Vdd\_die through the ESD diodes. Whether the device triggers depends on the peak voltage on the pad with respect to Vdd on die (Vdd\_die). For this configuration, the threshold for triggering was found to be about 2 V. So long as the peak pad voltage is 2 V or more above Vdd\_die, the event should be latched by the detector.

Figure 2-11. Response of positive detector to 700V ESD event

The trigger threshold is determined by the relative sizes of the transistors. Figure 2-12 shows the trigger threshold when the width of M1 was varied from 2 to 9 u. The trigger voltage varies from 5 to 2 V. Thus, it may be possible to measure the level of the ESD event using a group of such circuits and observing which of them triggered.

Figure 2-12. Threshold variation for positive event detector as width of M1 is varied

The trigger threshold can be determined analytically from the configuration of the detector. As described before, the equation governing the trigger of the positive event detector is:

$$-V_{pad} = V_{t,p} + \frac{V_{dsat}}{2} - V_{dd} + \left\{ \frac{k'_{n}}{k'_{p}} \left( \frac{W}{L} \right)_{M2} \left( \frac{L}{W} \right)_{M1} \frac{1}{V_{dsat}} \left[ \left( V_{op} - V_{ss} - V_{t,n} \right) \left( V_{"A",sw} - V_{ss} \right) - \frac{\left( V_{"A",sw} - V_{ss} \right)^{2}}{2} \right] \right\}$$

(2.4)

This equation is derived using a simple MOSFET algebraic model suggested by Shichman and Hodges [10]. This model is based on curve fitting and is insufficient to predict the behavior for modern processes [11]. Modern models like BSIM models take into account variation of parameters with bias and temperature and the interdependence

among various parameters. Using such models here makes prediction of thresholds more complicated than needed.

A simpler model called the Alpha-power model introduced in [11] gives a set of parametric equations which are simple to use. Since curve fitting is done for this particular application, parameters and behavior of equations have more reliability. The Alpha-power law equations are as follows:

$$I_{Drain} = 0 \qquad \qquad \left( V_{gs} \leq V_{th} : cutoff \right)$$

$$= \left( I'_{Drain} / V'_{Drain} \right) V_{ds} \qquad \left( V_{ds} < V'_{Drain} : Linear \, \text{Re gion} \right)$$

$$= \left( I'_{Drain} \right) \qquad \left( V_{ds} \geq V'_{Drain} : Saturation \right)$$

$$(2.5)$$

where:

$$I'_{Drain} = W * K(V_{gs} - V_t)^{\alpha}$$

$$V'_{Drain} = P_v (V_{gs} - V_t)^{\alpha/2}$$

where W is width of the MOSFET, and the length is factored into "K" since length is assumed to be constant. The parameters  $V_{th}$ , K,  $P_v$  and  $\alpha$  are found from curve fitting to V-I curves of MOSFETs in simulation.

Following the earlier development, the equation for threshold for the positive event detector using the alpha power law is:

$$V_{pad,sw} = \left| V_{t,M1} \right| + \left( \frac{K_{M2} * W_{M2}}{K_{M1} * W_{M1} * P_{v,M2}} \left( \left| V_{dd} \right| - \left| V_{t,M2} \right| \right)^{\alpha_{M2}/2} * \left( V_{"A",sw} \right) \right)^{1/\alpha_{M1}}$$

(2.6)

where V<sub>"A",sw</sub> is the voltage at node "A" at which inverter M4-M5 switches, found to be 2.9 V for the sizes of M4 and M5 used in simulations.

To match theoretical triggers to those found experimentally, the parameter values for the MOSFETs had to be found through simulation. Since M1 is assumed to be in

saturation mode when the latch triggers, simulations were performed with M1 in saturation. The simulation schematic is shown in Fig. 2-13.

Figure 2-13. Simulation schematic for getting characteristic curves for the PFET

$V_{ds}$  was kept to -10 V while  $V_{gs}$  was swept from 0 to -5 V. Since  $V_{ds} > V_{gs} - V_t$  the FET would be in saturation for the entire sweep. Parameter values were determined to match the resulting curve with the following equation:

$$(I_{Drain}) = W * K(V_{gs} - V_t)^{\alpha}$$

$$(2.7)$$

The resulting parameters were: Vt= -0.5 V,  $\alpha$  = 1.315 and K = 41.4022 A/m for a W=9 um PFET. The measured and simulated V<sub>gs</sub> Vs I<sub>drain</sub> curve is shown in Fig. 2-14.

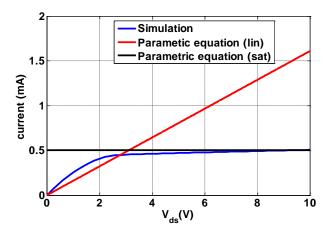

Simulations for M2 (the NFET) were done for a W=1.5 um FET. The simulation schematic is shown in Fig. 2-15. The FET was simulated with  $V_{ds}=10$  V while sweeping  $V_{gs}$  from 0-5 V. The parameters found from curve fitting are:  $V_t$ = 0.95 V,  $\alpha$  = 1.1469 and K = 67.35 A/m. Figure 2-16 shows the comparison between the simulated and calculated I-V curve.

Figure 2-14. Comparison of Vgs-Idrain curve from simulations and parametric equation for 9u/0.6u PFET

Figure 2-15. Simulation schematic for getting V-I curves for the NFET

Figure 2-16. NFET drain current comparison in saturation region with equation and simulation results for 1.5u/0.6u NFET

The simulation above gives the value of Idrain during saturation. The values for I'drain and V'drain for linear operation are also needed. The equations for linear operation of the FET are:

$$(I_{Drain}) = (I'_{Drain}/V'_{Drain})V_{ds}$$

$$I'_{Drain} = W * K(V_{gs} - V_{t})^{\alpha}$$

$$V'_{Drain} = P_{v}(V_{gs} - V_{t})^{\alpha/2}$$

$$(2.8)$$

The parameter left to be found is  $P_v$ . Simulations and curve fitting for Vds sweep from 0-10 V while keeping Vgs= 5 V gave  $P_v$ = 1.4. The resulting curves are shown in Fig. 2-17. Notice how curve is fitted for linear region. This is done to have a close approximation around Vds = 3 V since that is the region this FET will be in during triggering. Similar curve fitting was performed to find  $P_v$  for PFETs, which was found to be 1.4.

New simulations were performed to find thresholds while slowly varying the pad voltage. Thresholds for various combinations of M1 and M2 sizes were found while injecting a triangular "pulse" with very slow rise time into the IO pad. The slowly

varying input was used to avoid bandwidth being a factor in the results since static conditions are assumed in the analytic equations. A 5 V DC source was connected between Vdd(die) and Vss(die) since this voltage is assumed in the equations. An example simulation result is shown in Fig. 2-18.

Figure 2-17. Comparison for NFET  $V_{ds}$  Vs  $I_{drain}$  curve and approximations from Alphapower model

The thresholds for various sizes of M1 were found by recording the Pad- $V_{dd}$ (die) voltages which made the circuit trigger. Corresponding thresholds were also found by solving the equation:

$$V_{pad,sw} - V_{dd} = \left| V_{t,M1} \right| + \left( \frac{K_{M2} * W_{M2}}{K_{M1} * W_{M1} * P_{v,M2}} \left( \left| V_{dd} \right| - \left| V_{t,M2} \right| \right)^{\alpha_{M2}/2} * \left( V_{"A",sw} \right) \right)^{1/\alpha_{M1}}$$

(2.9)

Both the results are plotted together in Fig. 2-19. The predicted and measured thresholds match to within about 0.2 V.

Figure 2-18. Response of positive event detector to slow event with 300 ns rise time while Vdd(die) and Vss(die) are held at a constant 5 V

Figure 2-19. Comparison of thresholds for positive indicators from simulations and Alpha-power law when Vdd(die)-Vss(die)=constant

If Vdd(die) is not held constant with respect to Vss(die) during the ESD event, then the match is not as good as is shown in Fig. 2-20. This mismatch happens because the change in Vdd during the event changes the threshold of the M4-M5 inverter and this changes the  $V_{A^n,sw}$  term in the equations. This issue will be addressed later in the discussion.

Figure 2-20. Comparison of thresholds for positive event indicators from simulations and Alpha power law when Vdd(die)-Vss(die) is not constant

A similar analysis was done for the negative event detectors, like the one shown in Fig. 2-21. Simulations were done with a slowly ramped current injected into the pin, while the power supply voltages were held constant with respect to each other. The thresholds were recorded during these simulations.

The equation for the trigger of a negative event detector is similar to that for a positive detector:

$$-V_{pad,sw} = |V_{t,M1}| + \left(\frac{K_{M2} * W_{M2}}{K_{M1} * W_{M1} * P_{v,M2}} \left( |V_{dd}| - |V_{t,M2}| \right)^{\alpha_{M2}/2} * \left( |V_{"A",sw} - V_{dd}| \right) \right)^{1/\alpha_{M1}}$$

(2.10)

A comparison of the calculated and simulated thresholds is shown in Fig. 2-22. When the power supply voltage is held constant, the theoretical and simulated values of trigger voltage match within less than 0.2 V.

Figure 2-21. Negative event indicator

When Vdd is not noisy the thresholds of the out-of-range voltage detectors can be predicted well. Vdd will not be constant, however, for real application. The ESD events will cause significant changes in the power supply voltage (Vdd-Vss). This disturbance depends on the rise time and duration of the ESD event, which can have a wide range of rise times and durations when they affect a pin of an IC. This uncertainty in power supply voltage causes the thresholds for the detector circuits to be dependent on the type of the

event, since dependence of voltage at node "A" is different compared to dependence of M4-M5 inverter threshold on power supply.

Figure 2-22. Comparison of thresholds for negative event indicators from simulations and Alpha power law when Vdd(die)-Vss(die)=constant

During switching of the latch in positive event detector (refer Fig. 2-10), M2 can be assumed as a pull-down resistor of value R while M1, which is in saturation, can be assumed to be to be a voltage controlled current source of current say I, hence voltage at node "A" can be given by equation 2.11

$$V_{A''} = V_{ss} + I * R (2.11)$$

Since, the latch switches when  $V_{,"A"}$  reaches switching threshold of M4-M5  $(V_{,"A"},sw)$ , if the threshold for M4-M5 could be made proportional to power supply  $(V_{ss})$  in this case), in a similar manner to  $V_{,"A"}$ , then the detector thresholds would become almost

independent from type of ESD events. This independence is required if the detector is to be used like an A/D converter.

Methods suggested to achieve desired proportionality between Vdd and M4-M5 inverter threshold (referred to as V<sub>A</sub>, sw from now on) are shown in Fig. 2-23. One possibility is to make M4 very wide. Another is to make is to make the M4-M5 inverter a current-source-load inverter. Each of these options will be discussed in detail below.

Figure 2-23. Methods to achieve proportionality between switching threshold of M4-M5 inverter and Vdd(die) (a) Increase width of M5 to be much larger compared to that of M4 (b) Make M4-M5 a current source load inverter

**2.1.3.1 Increasing size of M5.** The equation for the switching threshold of M4-M5 inverter is given as [12]:

$$k'_{M4} * V_{dsat,M4} (V_{"A",sw} - V_{ss} - V_{t,M4} - \frac{V_{dsat,M4}}{2}) + k'_{M5} * V_{dsat,M5} (V_{"A",sw} - V_{dd} - V_{t,M5} - \frac{V_{dsat,M5}}{2}) = 0$$

Giving

$$V_{A'',sw} = C + \frac{r}{r+1} \left( V_{dd} - V_{ss} + V_{t,M5} + \frac{V_{dsat,M5}}{2} \right)$$

(2.12)

where:

$$r = \frac{k'_{M5} * V_{dsat,M5}}{k'_{M4} * V_{dsat,M4}} = \frac{v_{sat,M5} * W_{M5}}{v_{sat,M4} * W_{M4}},$$

the term "C" is independent of Vdd, and  $W_{M5}$  and  $W_{M4}$  are channel widths of M5 and M4 respectively. If  $W_{M5} >> W_{M4}$  then  $(r/r+1) \rightarrow 1$  which will allow  $V_{A,sw}$  to change directly with  $V_{dd\ o}r\ V_{ss}$ .

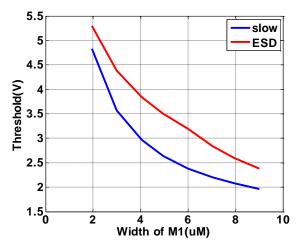

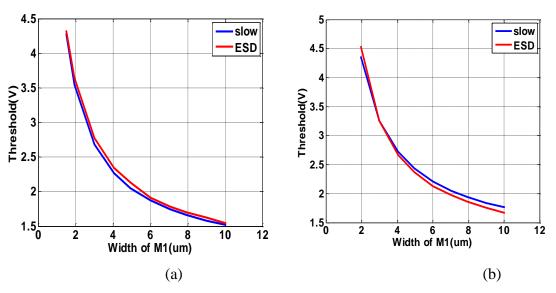

Simulated results for positive event thresholds are shown in Fig. 2-24 and 2-25. For Fig. 2-24, the sizes of the FETs were:

M1: 9 um/0.6 um M2: 1.5 um/0.6 um M3: 3 um/0.6 um M4: 1.5 um/0.6 um M5: 6 um/0.6 um

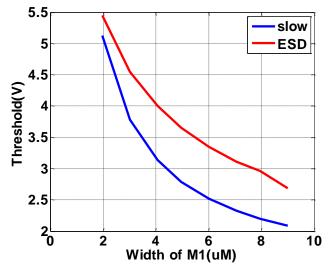

As discussed before, thresholds were found for both slow events and ESD events and compared. The difference between the thresholds for a slow and fast event in Fig. 2-24 was up to about 0.87 V when M5 was 6 um wide. Figure 2-25 shows the results when M5 was 20 um wide. Surprisingly, changing the size of M5 did not give the expected improvement in the threshold match for slow and fast events, the difference in thresholds of slow and ESD events is still up to 0.86 V.

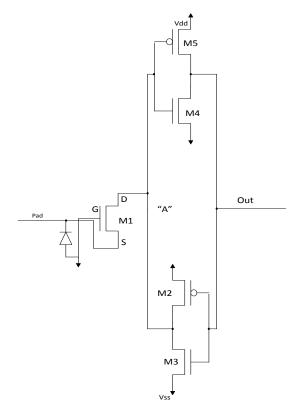

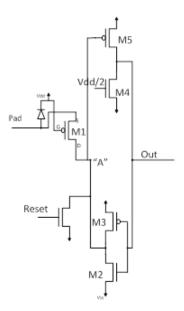

**2.1.3.2 Current-source load inverter.** In this configuration, the M4-M5 inverter is converted to a current-source load inverter with M4 held in saturation with a gate-to-source voltage  $V_{gs}=V_{dd}/2$ , as shown in Fig. 2-26. The gate voltage of M4 is specifically set to follow changes in Vdd.

Figure 2-24. Comparison between positive event thresholds for slow and ESD events when M5=6u wide

Figure 2-25. Comparison between positive event thresholds for slow and ESD events when M5=20u wide

At the point of switching,  $V_{^{\prime\prime}A^{\prime\prime}}=V_{out.}$  and both M5 and M4 are in saturation. Equating currents in M5 and M4:

$$K'_{M5}*(\frac{W}{L})_{M5}*(V_{"A",sw}-V_{dd}-V_{t,M5})^{2} = K'_{M4}*(\frac{W}{L})_{M4}*(\frac{V_{dd}-V_{ss}}{2}-V_{ss}-V_{t,M4})^{2}$$

$$\sqrt{\frac{K'_{M4}*(\frac{W}{L})_{M4}}{K'_{M5}*(\frac{W}{L})_{M5}}}*(\frac{V_{dd}}{2}-\frac{3V_{ss}}{2}-V_{t,M4})+C=V_{"A",sw}}$$

(2.13)

$K'_{M4}$  is roughly twice of  $K'_{M5}$ , if  $L_{M4}$ = $L_{M5}$  then WM4 and WM5 can be selected such that  $V_{A'',sw}$  changes directly with power supply. For example if linearity with  $V_{dd}$  has to be achieved then setting  $W_{M4}$ = $2*W_{M5}$  gives relation as shown by equation 2.14. The resulting match between the thresholds for slow and fast events is shown in Fig. 2-27. The match in this case is within less than 100 mV.

Figure 2-26. Positive event indicator with M4-M5 inverter with current source load

$$V_{A'',sw} = 2*\left(\frac{V_{dd}}{2} - V_{t,M4}\right) + C$$

$$V_{A'',sw} = V_{dd} + (2*V_{t,M4}) + C$$

(2.14)

Note that theoretically the gate bias of M4 has to be kept at  $V_{dd}/2$  and M4 width should be double to that of M5 but practically these conditions overpower M5 and circuit is always latched. For this reason gate bias of M4 is reduced from  $V_{dd}/2$  to  $(1.5/5)*V_{dd}$  and its size changed to accommodate change in gate bias. Simulations for results shown in Fig. 2-27 include these modifications.

Figure 2-27. Comparison of positive event indicator thresholds for slow and ESD events for M4-M5 inverter having M4 as current source load

One possible issue with the circuit is that M4-M5 always consumes current – at least until an event is detected and the output is low. For some applications this static current might be acceptable and others not. To minimize static current, it is possible to only turn on the M4 during testing conditions, when static current is acceptable, and turn it off otherwise, for example by controlling the gate voltage at M4. Another possibility is to turn M4 on using a sensor circuit, like the one in Fig. 2-28. A second detector is added

which will turn on only during the transient event. This inverter will turn on the M4/M5 inverter and allow it to detect the event. Only one such "detector" is needed for all latches at a pad, so does not add significant cost/complexity to the design. Since M4 will be turned off after the event has passed, an additional weak pull-down is added to the output keep the output latched after the event has passed.

Figure 2-28. Positive event indicator with M4 as current source load and optimizations to have minimal static current consumption

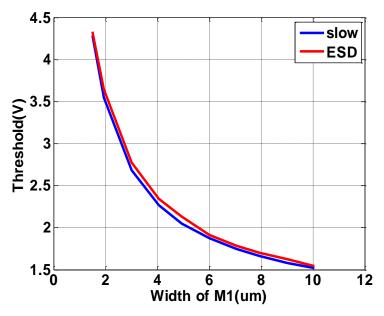

Figure 2-29 shows comparison of thresholds for slow and ESD events (Figure 2-29(a) for current source load inverter configuration, Fig. 2-29(b) for modified version of the configuration as shown in Fig. 2-28). Comparing the results of Fig. 2-29(b) with Fig. 2-29(a), results with non-modified current-source load inverter configuration, notice that not only the thresholds for both slow and ESD events change by themselves (less than

9%) but also the match between slow and ESD events changes. For un-modified circuit the thresholds for slow and ESD events were less than 0.1 V apart throughout, while with modifications they are at 0.2 V maximum difference. Note that this result can be improved by changing size of M4 as needed, but with 0.5 um technology only this level of tuning could be achieved.

Figure 2-29. Comparison of thresholds for slow and ESD events with (a) current source load inverter configuration (b) modified current source load inverter configuration

## 2.2 OSCILLATORS

The last section presented a possible instantaneous A/D converter that converts the peak voltage at the input to a digital level based on triggering one or more voltage-sensitive latch circuits. Another possibility for converting the input level to a digital reading is using an oscillator-based A/D. The basic idea is to use an oscillator configuration where the number of oscillations over a given time will vary with the pad

voltage during the event. By counting the number of oscillations, a digital level can be obtained.

- 2.2.1 Concepts and Schematics. Multiple methods of implementing an oscillator-based A/D for a transient event are possible. One scheme presented in this section is self-triggered and is automatically triggered during the transient event. The others require an out-of-range voltage detector with very small threshold to trigger the oscillator when a transient event occurs. For the windowed oscillator, the oscillator counts the number of oscillations over a fixed window of time to determine the level of the event to determine the energy in the event. In yet another approach, the trigger starts the oscillator after the event has passed. A capacitor is charge to the peak level of the event, and the number of oscillations is dependent on the time it takes to discharge the capacitor through a resistor.

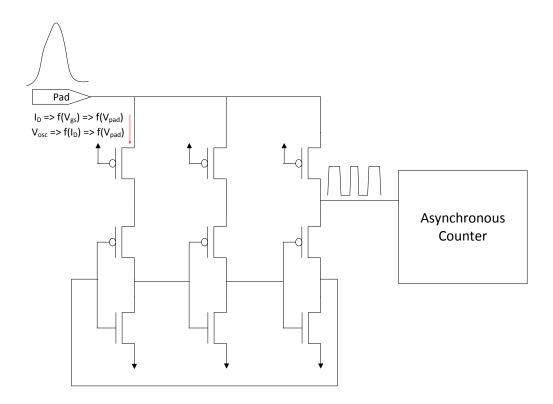

- **2.2.1.1 Self-triggered oscillator.** The self-triggered oscillator in Fig. 2-30 will oscillate whenever the pad voltage goes above Vdd (for a positive event). The frequency of oscillation depends on the pad voltage. The total number of oscillations depend both on the voltage over the event as well as its duration, given a rough measure of the energy in the event. The number of oscillations is counted using an asynchronous counter.

- **2.2.1.2 Windowed oscillator.** Two windowed oscillator circuits were investigated. The first is shown in Fig. 2-31.

Each I/O pad will need an out-of-range voltage detector, like those discussed in Section 2.1, with a very low trigger threshold so that it will trigger for any ESD event that the I/O pad receives. When the pad goes above Vdd (for a positive event) the ring oscillator will oscillate. The frequency of oscillations for the ring-oscillator is dependent

upon the pad voltage. The length of time over which the oscillator is active depends on a built-in delay in the circuit. This option allows the oscillator to only count for a short, fixed duration. If the measurement window is kept long enough to capture the whole event, then the energy of the event is measured as with the self-triggered oscillator. If the window is short, then the energy is only measured within a small window, which may or may not capture the peak of the event.

Figure 2-30. Self-triggered oscillator for measuring energy in a transient event

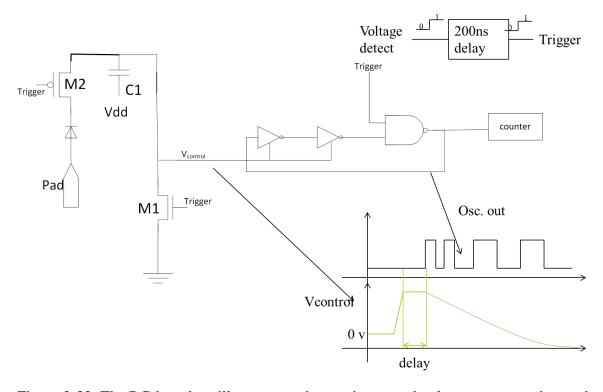

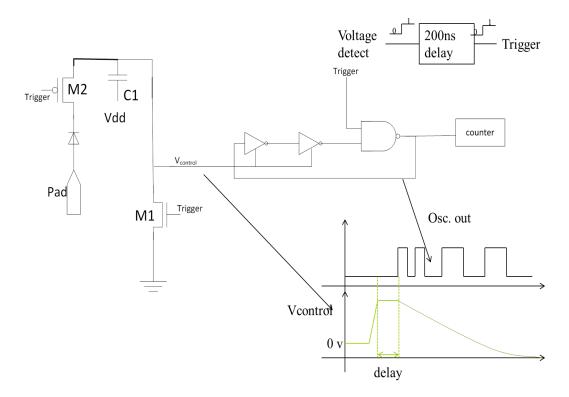

**2.2.1.3 RC-based oscillator.** The windowed oscillator in Fig. 2-31 can capture a voltage, but that voltage may or may not occur at the peak. To capture the voltage at the peak of the event, a diode and capacitor were added as shown in Fig. 2-32.

Theoretically the capacitor can only be discharged by leakage from the diode or leakage from M1. A voltage detect signal is used to trigger the oscillator. The voltage detect signal is generated from an out-of-range voltage detector but is delayed by some time to allow the disturbance on the power deliver network to pass (e.g. 200 ns) and to ensure the capacitor is charged to the peak level of the event. The voltage detect signal activates the ring oscillator and turns on M1 to discharge the capacitor. The oscillator frequency is controlled by the voltage on the capacitor. The length of time the oscillator runs depends on the time to discharge the capacitor through M1. Thus, the number of oscillations depends upon peak voltage stored on capacitor. The peak level of the ESD can be approximated from the count.

Figure 2-31. Windowed oscillator for measuring voltage of transient events

**2.2.2 Simulation Models.** The simulations for the oscillator-based level sensors were similar to the simulations for the out-of range voltage detectors. The basic

simulation setup for both sets of simulations is shown in Fig. 2-33. In this case, the test circuit is the oscillator-based level sensor.

Figure 2-32. The RC-based oscillator stores the maximum pad voltage on a capacitor and then counts the number of oscillations while the capacitor is discharged

Figure 2-33. General simulation model for testing different circuits

**2.2.3 Simulation Results and Analysis.** Simulations were performed for each oscillator-based sensor as discussed in the following sub-sections.

**2.2.3.1 Self-triggered oscillator.** Simulations with the self-triggered oscillator were performed with positive events. Schematic for simulations is shown in Fig. 2-34 The circuit was tested for both ESD and slow events. ESD events were simulated using the ESD source model and slow events were created using an ideal current source in Virtuoso which injects slowly ramped currents into the test pin.

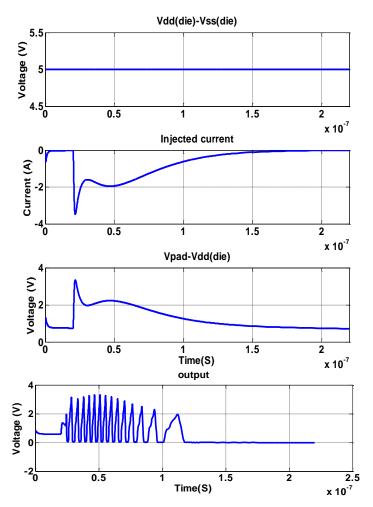

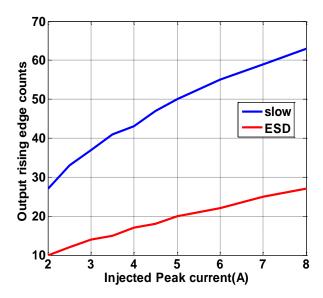

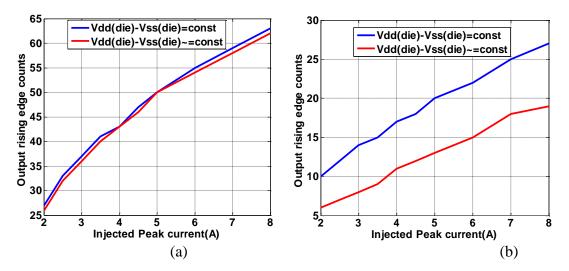

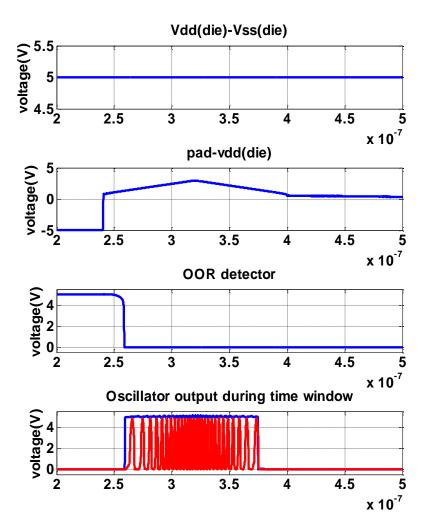

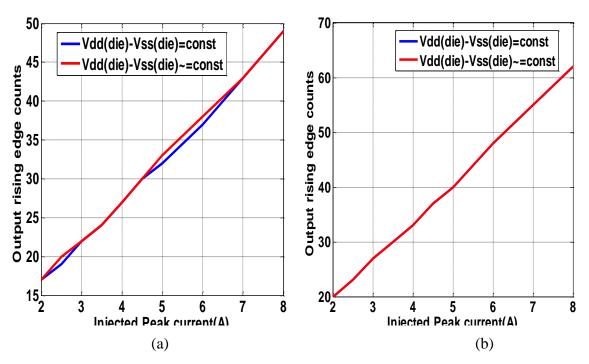

Initial tests were done by holding  $V_{dd}$ (die) and  $V_{ss}$ (die) constant with respect to each other. Results when injecting a slow event with a 3.5 A peak are shown in Fig. 2-35. Results when injecting an ESD event with a 3.5 A peak are shown in Fig. 2-36. The number of oscillations is determined by the number of rising edges. This count will be used as a measure of the level of the event. Figure 2-37 shows the variation in the output count with the level of current injected to the pin. It is clear from Fig. 2-37 that this circuit implementation gives a measure of energy in the event rather than the peak of the event. This measure of energy gives a larger count for a slow event with the same peak current as an ESD event, which passes relatively quickly.

Simulations with a noisy PDN i.e.  $V_{dd}$ (die) and  $V_{ss}$ (die) not held constant w.r.t. each other are done. Figure 2-38 shows such a simulation for slow events and Fig. 2-39 shows the simulation for ESD event.

Figure 2-40 shows that the self-triggered oscillator is not resistant to PDN noise and hence will give a different measure of level for different kinds of events depending upon their rise times, even if they have same amount of energy. As mentioned earlier, this method gives a measure of energy and not the peak disturbance.

Figure 2-34. Simulation setup for self-triggered oscillator

Figure 2-35. Response of self-triggered oscillator to slow events with Vdd(die)-Vss(die) = constant

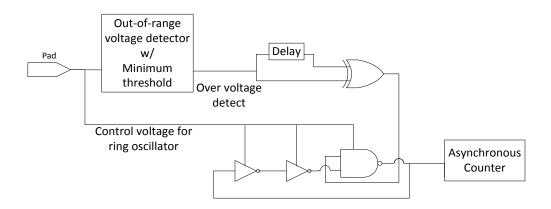

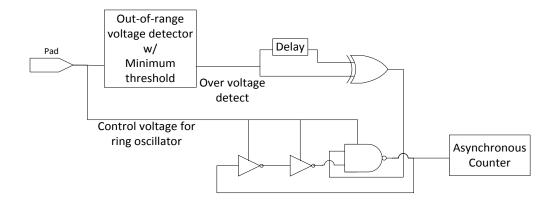

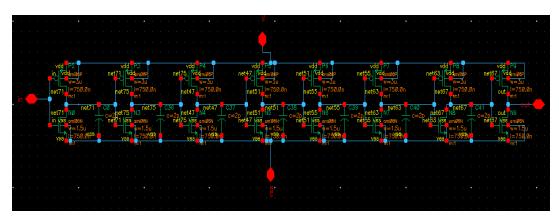

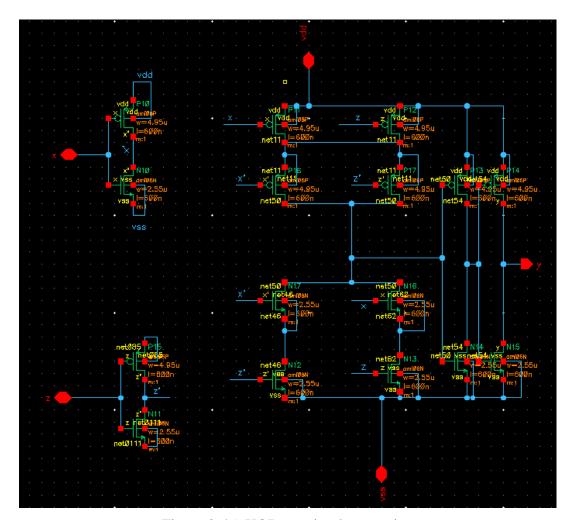

**2.2.3.2 Windowed oscillator.** The windowed oscillator was implemented as shown in Fig. 2-41. The out of range voltage detector is the same detector discussed in Section 2.1 with a very low threshold so it can trigger on almost all transient events on the pad. The implementation used here is shown in Fig. 2-42.

Figure 2-36. Response of self-triggered oscillator with Vdd(die)-Vss(die)=constant

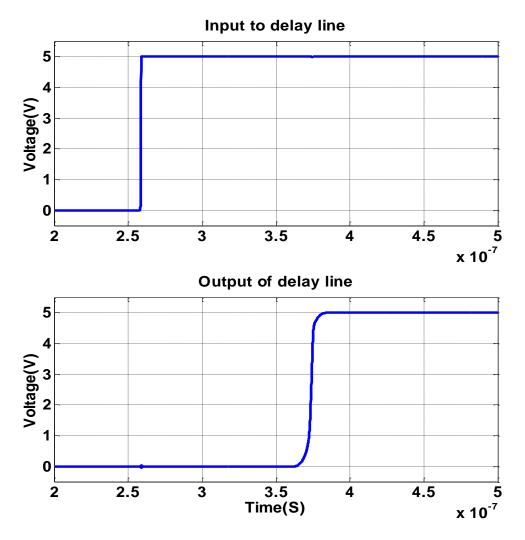

For the proof-of-concept implementation, the delay line was implemented using inverters and capacitors as shown below in Fig. 2-43. This delay line gives approximately

a 115 ns delay between a transition of the input and a transition of the output as shown in Fig. 2-44.

Figure 2-37. Comparison of output counts for self-triggered oscillator for slow rise/fall time and for positive ESD events when Vdd(die)-Vss(die)=constant

Figure 2-38. Response of self-triggered oscillator during a slow event when Vdd(die)-Vss(die) is not constant

Figure 2-39. Response of self-triggered oscillator during an ESD event when Vdd(die)-Vss(die) is not constant

Figure 2-40. Comparison of output counts for cases with and without Vdd(die)-Vss(die)=constant (a) for slow events (b) for ESD events

Figure 2-41. Windowed oscillator level sensor

Figure 2-42. Implementation of the out-of-range voltage detector

The XOR gate implementation is shown in Fig. 2-45. The XOR gate is used to generate a window of operation for the oscillator to measure the level of the event.

Figure 2-43. Implementation of delay line

Figure 2-44. The delay line has a 115ns delay from input to output

Figure 2-45. XOR gate implementation

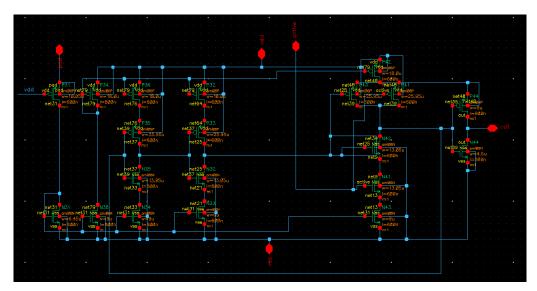

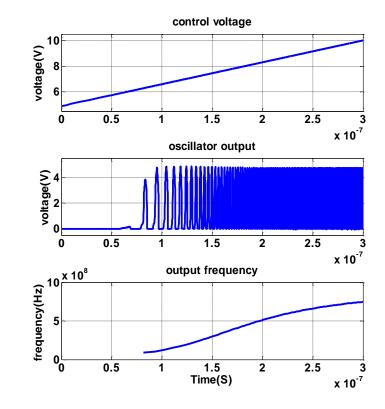

The oscillator was implemented as shown in Fig. 2-46. The frequency response of this oscillator to the control voltage (pad voltage) is shown in Fig. 2-47. The relation is close to linear when the pad voltage is at least diode voltage above Vdd(die). The output frequency varies from 100 MHz to 750 MHz

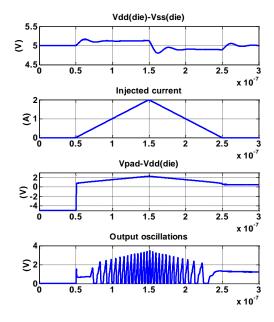

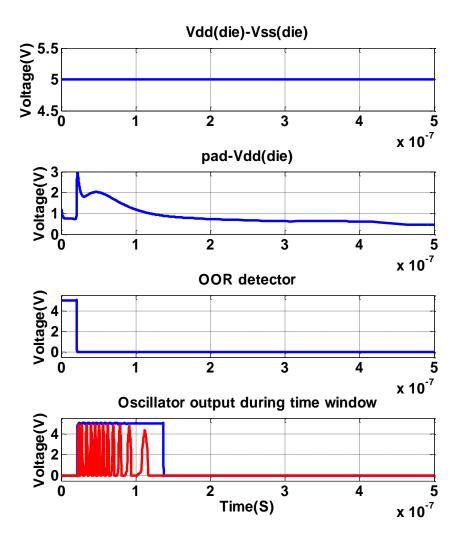

Testing was first done with Vdd(die) and Vss(die) kept constant with respect to each other. Fig. 2-48 shows the response of the oscillator to a slow pulse with a 3 A peak. Figure 2-49 shows the response to an ESD event with a 3 A peak event.

Figure 2-46. Oscillator implementation

Figure 2-47. Variation of ocillator output frequency with the control voltage

One fact that is evident from the plot is that the portion of the input waveform captured by the event depends much on the waveform. For a very slow event, the count may entirely miss the peak. This mismatch causes different parts of slow event to be captured. For and ESD event, the window can be constructed to reliably capture nearly the entire event.

Figure 2-48. Response of windowed oscillator to slow event when Vdd(die)-Vss(die)=constant

Figure 2-49. Response of windowed oscillator to ESD events when Vdd(die)-Vss(die)=constant

Fig. 2-50 shows a comparison of the output count for slow and ESD events when Vdd(die) and Vss(die) were held constant with respect to each other. Since the measurement window is long, the energy in the event is captured rather than peak of the event. This measure of energy results in higher count for slow events that have the same peak as an ESD event, since the area under the curve may be smaller with the ESD event.

Figure 2-51 shows a comparison of counts in cases with and without Vdd(die) and Vss(die) noise (Figure 2-51(a) shows comparison for slow events and Fig. 2-51(b) for ESD events). The results demonstrate that the count for the windowed oscillator is not significantly affected by the Vdd noise caused by the ESD event. The results differ by a maximum of 10% for large events. This result indicates that the output count is a reliable measure of the energy in the event, even in the presence of power supply noise.

Figure 2-50. Comparison of output counts of windowed oscillator for slow and ESD events while Vdd(die)-Vss(die)=constant

If the window of measurement is made over a small window, then the peak of ESD events with fast rise time can be captured, but this small window will only capture the initial portion of a slow event waveform and may entirely miss the peak. One possible resolution to this issue is to record the number of oscillation over multiple, consecutive small windows one after another and saving the maximum count. This method will

require additional circuit and logic to save multiple counts and compare them. If memory allowed one to save all the counts, one could construct an approximation of the waveform at the pad.

Figure 2-51. Comparison of windowed oscillator output counts with and without having Vdd(die)-Vss(die)=constant for (a) slow events (b) ESD events

**2.2.3.3 RC-based oscillator.** Figure 2-52 outlines the basic method for determining the peak level of the event using an RC-based oscillator.

The diode at the pad allows capacitor C1 to charge to within a diode voltage drop of the pad voltage and then keep that charge. Capacitor C1 is referenced to Vdd so that is accurately captures the voltage difference between the pad and Vdd. If C1 were referenced to Vss, the voltage across C1 would be impacted by changes in Vss as well as the voltage at the pad. During normal operation M2 is turned on and M1 is turned off. When an overvoltage event occurs, C1 is charged to within a voltage drop of the peak pad voltage. 200 ns after the event, M2 is turned off, M1 is turned on, and the ring

oscillator is turned on. Waiting until after the event has passed to determine the level mitigates the impact of power supply noise on results. When M1 is turned on, C1 begins to discharge to VSS. M2 is turned off so that C1 can be discharged all the way to VSS, independent of the voltage at the pad. The frequency of oscillation is dependent on the voltage on C1. The period of time the oscillations occur depend on the time it takes for C1 to discharge to VSS. By counting the number of oscillations, one can obtain a measure related to the peak voltage on the pad. A lookup table can be used to correlate the resulting count with the specific voltage value.

Figure 2-52. Basic concept for determining peak level of the event using the RC-based oscillator

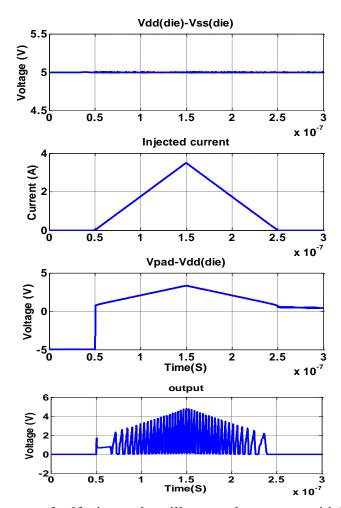

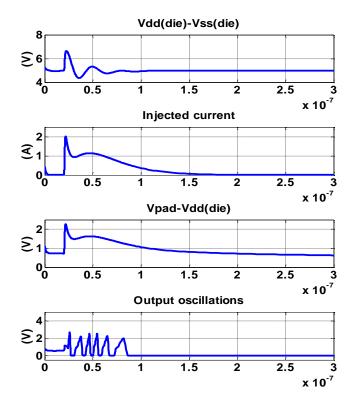

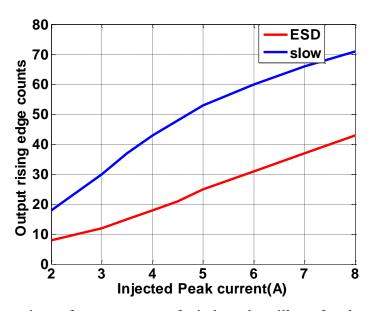

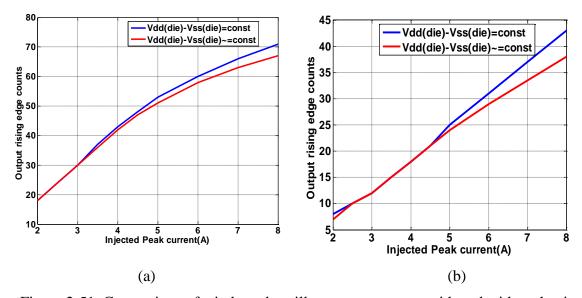

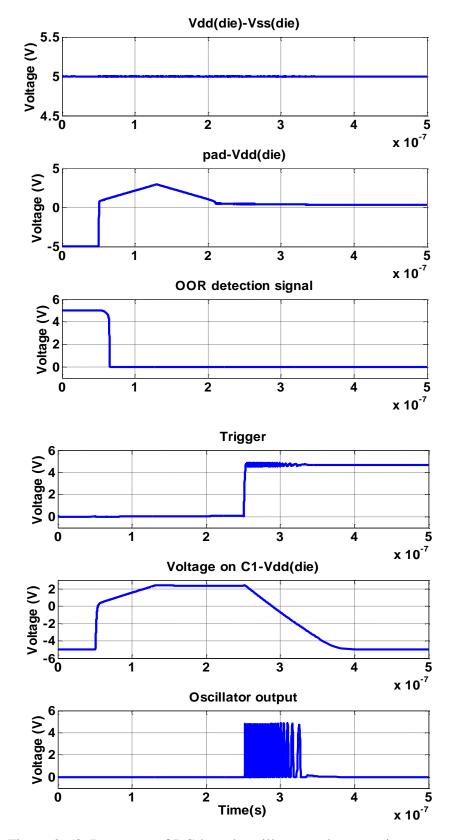

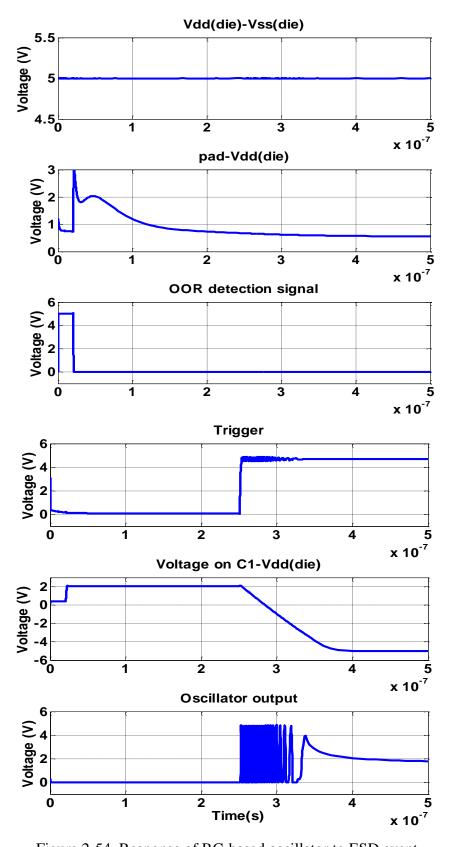

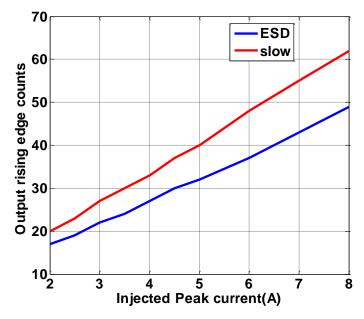

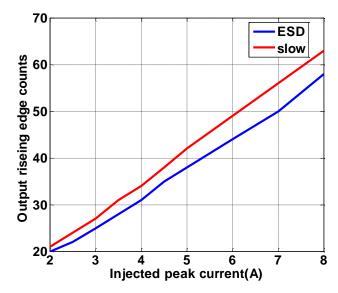

Figure 2-53 shows the behavior of the RC-based oscillator for a slow triangular waveform with a peak current of 3 A and while holding Vdd(die) - Vss(die) constant. Figure 2-54 shows the behavior of the oscillator for an ESD event with a 3 A peak current. Figure 2-55 compares the output count measured for slow and ESD events for different peak levels of the event. Figure 2-56 compares output counts for slow events (Fig. 2-56(a)) and ESD events (Fig. 2-56(b)) with and without a constant power supply. These results demonstrate that the oscillator is largely unaffected by power supply noise. There is, however, a difference in the count for slow and ESD events. For this design, the slow events had a count roughly 20% higher than the ESD events for an 8A event. This difference results because the voltage stored on the capacitor is dependent upon the rise time of the event, due to the resistance between the pad and capacitor C1. In the initial tests, the size of M2 was 10 um/0.6 um. Making M2 wider can reduce the difference, as shown in Fig. 2-57 where the size of M2 was doubled roughly cutting the difference in half. If using a large M2 is unreasonable, the area impact of this large FET could be minimized by using a shared storage (or boost) bus, where multiple pads were connected to the bus through a diode. The peak voltage on any of the I/O connected to the bus would determine the voltage on the capacitor. Only one capacitor and one transistor M1 would be required for the whole bus.

**2.2.4 Limitations.** The oscillator designs are generally large and may be too large to be implemented for each I/O pad. One option is to implement them only on the most critical pads. Another is to implement a single oscillator for a group of I/O or perhaps for an entire IC, when the IC is small. In this case, the pads would be connected to a "boost" bus through a diode, which would isolate the pads from one another.

Figure 2-53. Response of RC-based oscillator to slow transient events

Figure 2-54. Response of RC-based oscillator to ESD event

Figure 2-55. Comparison of output counts for RC-based oscillator for slow and ESD events (M2=10u/0.6u)

Figure 2-56. Comparison of output counts for cases with and without Vdd(die)-Vss(die)=constant for RC-based oscillator (a) slow events (b) ESD events

Figure 2-57. Comparison of output counts for RC-based oscillator for slow and ESD evemts when Vdd(die)-Vss(die) =constant (M2=20u/0.6u)

A transient event at any pad in the group would cause a measurement by the oscillator for the group. This would allow measurement of the level of the event seen by one of the pads within the group. Out-range-voltage detectors could be implemented at each I/O pad to determine on which pad (or pads) the event occurred. One problem with a boost bus is that there may be a voltage drop across the bus or the power supply between the location of the pad where the transient event occurred and the location of the oscillator where the event is measured. This voltage drop may reduce the accuracy of the measured level among the pads and make the measured level vary more with the strength and rise/fall time of the event.

The storage capacitance for the RC-based oscillator could potentially be implemented from the boost-bus wiring itself, as a wire running around an IC will not have an insubstantial capacitance. The problem, however, is that this capacitance may be referenced to Vss in some locations and to Vdd in other locations. The inability to control

than likely, this parasitic capacitance must be supplemented with added FET-based capacitance with a known reference to maximize accuracy of results.

## 3 CENTRALIZED A/D BASED DETECTION METHODS

Measurement of the level of an event at each pad requires substantial area and may be subject to errors from process variation. Using a single level detector for several pads can potentially reduce area, but must consume minimal static current and must be able to handle a large voltage drop across the IC during a transient event.