# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

1972

# An asynchronous circuit design language system

**Gregory Martin Bednar**

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electrical and Computer Engineering Commons Department: Electrical and Computer Engineering

# **Recommended Citation**

Bednar, Gregory Martin, "An asynchronous circuit design language system" (1972). *Doctoral Dissertations*. 194.

https://scholarsmine.mst.edu/doctoral\_dissertations/194

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# AN ASYNCHRONOUS CIRCUIT DESIGN LANGUAGE SYSTEM

Ъy

# GREGORY MARTIN BEDNAR, 1944-

A DISSERTATION

Presented to the Faculty of the Graduate School of the

UNIVERSITY OF MISSOURI-ROLLA

In Partial Fulfillment of the Requirements for the Degree

DOCTOR OF PHILOSOPHY

T2781 157 pages c.I

in ELECTRICAL ENGINEERING 1972

Marguell E. Egelhart Advisor ia

#### ABSTRACT

This paper presents a system for specifying the behavior of asynchronous sequential circuits. The system consists of a special purpose Asynchronous Circuit Design Language (ACDL), a translator and a flow table generation algorithm. The language includes many special features which permit quick and precise specification of terminal behavior. It is best suited for problems originating from a word description of the circuit's operation. The translator is written with the XPL Translator Writing System and is a syntax-directed compilation method. From the translated ACDL specifications, the flow table algorithm generates a primitive flow table which is the required input for the conventional synthesis procedures of asynchronous sequential circuits. A thorough description of the translator and flow table programs is given in the Appendices. In addition a number of example problems illustrating the use of ACDL are provided.

ii

#### ACKNOWLEDGEMENT

I wish to express my sincere appreciation to Dr. James H. Tracey, not only for his assistance and supervision given me throughout this project, but also for his personal concern shown me throughout the pursuit of my degrees. In addition, I extend my thanks to Dr. Tracey for providing me with the opportunity to work with him under a National Science Foundation Research Grant.

I would also like to acknowledge Mr. Wayne Omohundro for his helpful suggestions during this research.

Most of all, I wish to thank my wife, Carol, for her hard work, understanding, and encouragement rendered during the writing of this paper and pursuit of my degrees.

# TABLE OF CONTENTS

|                                             | Page                 |

|---------------------------------------------|----------------------|

| ABSTRACT                                    | ii                   |

| ACKNOWLEDGEMENT                             | iii                  |

| LIST OF ILLUSTRATIONS                       | vii                  |

| LIST OF TABLES                              | ix                   |

| I. INTRODUCTION                             | 1                    |

| II. ASYNCHRONOUS SEQUENTIAL CIRCUITS        | 4                    |

| A. The Conventional Design Process          | 5                    |

| <ul> <li>B. Circuit Specification</li></ul> | 6<br>6<br>7<br>8     |

| III. A DESCRIPTION OF ACDL                  | 10                   |

| A. The Definition of a Metalanguage         | 10                   |

| <ul> <li>B. Vocabulary of ACDL</li></ul>    | 21<br>22<br>23<br>25 |

| C. Sequences                                | 28                   |

| D. Summary                                  | 29                   |

Page

| IV.        | TRANSLATION AND INTERPRETATION 32             |

|------------|-----------------------------------------------|

|            | A. The XPL Translator Writing System (TWS) 32 |

|            | B. ACDL Translation                           |

|            | 1. Internal Form                              |

|            | C. Primitive Flow Table Construction          |

| V <b>.</b> | DESIGN EXAMPLES                               |

|            | A. Example 1                                  |

|            | B. Example 2                                  |

|            | C. Example 3                                  |

|            | D. Example 4                                  |

|            | E. Example 5                                  |

|            | F. Example 6                                  |

|            | G. Example 7                                  |

|            |                                               |

|            | H. Example 8                                  |

| VI.        | CONCLUSION                                    |

| BIBLIOGRA  | арну 56                                       |

| VITA       |                                               |

| APPENDIC   | ES                                            |

|            | Description of the Internal Tables            |

| Α.         |                                               |

|            | 1. Primary Sequence Table 61                  |

|            | 2. Secondary Table 1                          |

|            | 3. Secondary Table 2                          |

|            | 4. Global Transition Table 63                 |

|            | 5. Constraints Transition Table 64            |

|            | 6. Standard Symbol Table                      |

|            | 7. Special Symbol Table                       |

| в.         | Use of the Logic Trace Switch "\$W"           |

| с.         | Job Setup                                     |

| D.         | BNF Description of ACDL for the Translator    |

| 2.         | Writing System                                |

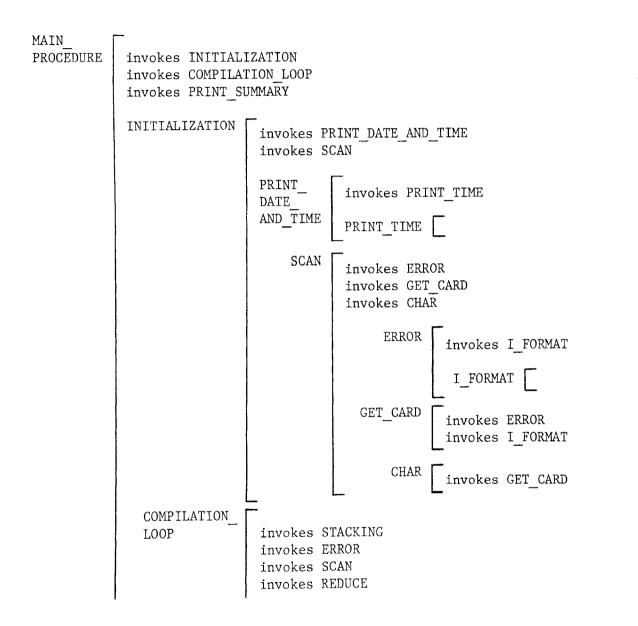

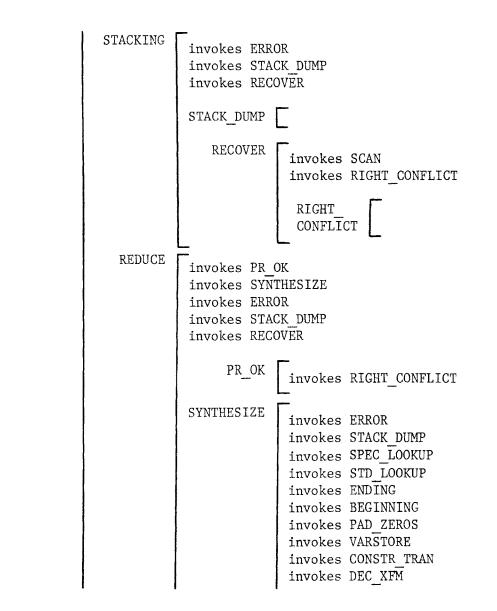

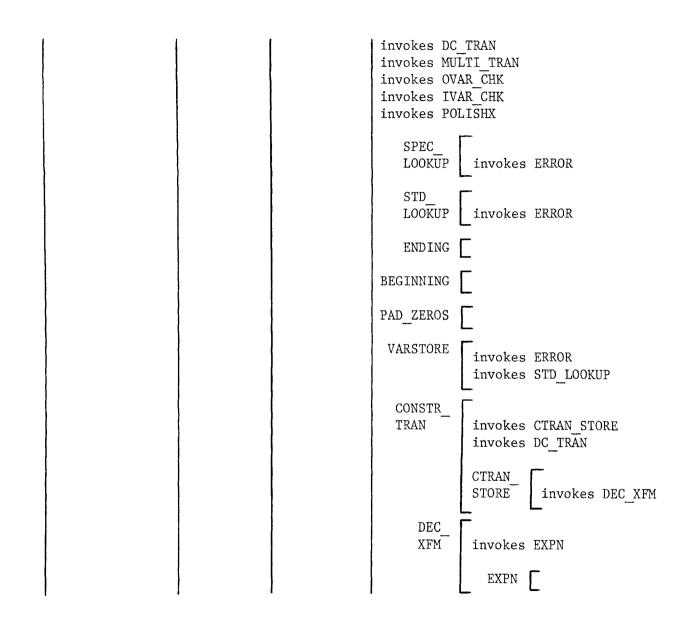

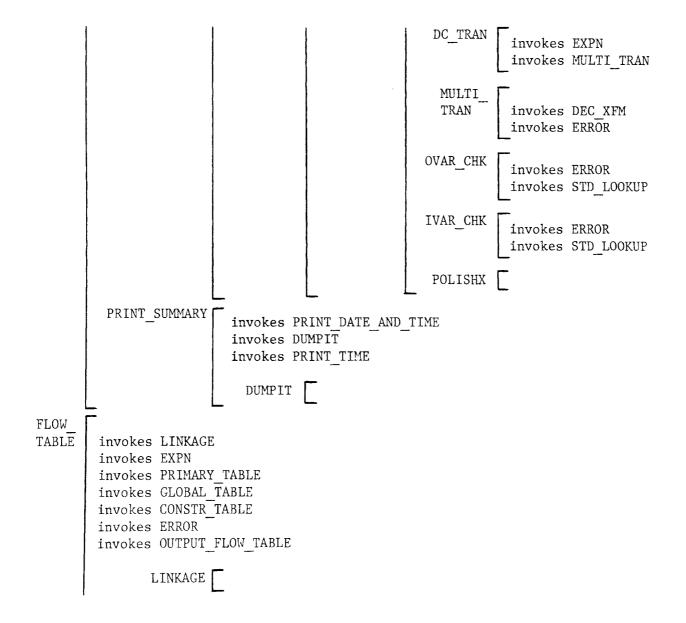

| Ε.         | Program Structure                             |

| F.         | Procedure Descriptions                        |

| _ 2        | 1. MAIN PROCEDURE Procedure                   |

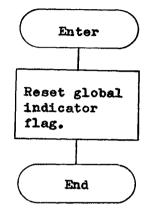

|            | 2. INITIALIZATION Procedure                   |

|            |                                               |

.

| P | а | ge |

|---|---|----|

|   |   |    |

|       |                              |   |   |   |   |   |   |   |   |   |   | Page |

|-------|------------------------------|---|---|---|---|---|---|---|---|---|---|------|

| 3.    | PRINT DATE AND TIME Procedur | e |   |   |   |   |   |   | • |   |   | 84   |

| 4.    | PRINT TIME Procedure         | • | • | • |   |   |   |   |   |   |   | 85   |

| 5.    | SCAN Procedure               |   |   |   | • |   |   |   | • |   |   | 85   |

| 6.    | GET CARD Procedure           |   |   |   | • |   | • |   |   | • | • | 85   |

| 7.    | CHAR Procedure               |   |   | • | • | • | • | • |   |   | • | 85   |

| 8.    | I FORMAT Procedure           |   |   |   |   |   |   |   |   |   |   | 85   |

| 9.    | ERROR Procedure              |   |   | • | • |   |   |   |   |   | • | 85   |

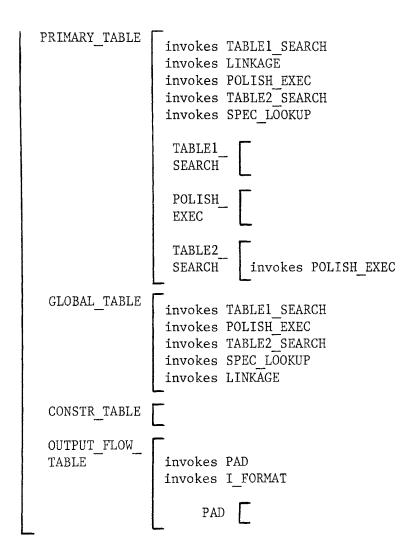

| 10.   | COMPILATION LOOP Procedure   |   | • |   | • |   | • | • | • |   |   | 85   |

| 11.   | STACKING Procedure           | • | • |   |   |   |   |   |   |   | • | 86   |

| 12.   | RECOVER Procedure            |   | • |   |   |   | • | • |   | • | • | 86   |

| 13.   | RIGHT CONFLICT Procedure .   |   | • |   |   | • |   |   |   | • | • | 86   |

| 14.   | STACK DUMP Procedure         |   |   |   |   |   |   |   |   |   |   | 86   |

| 15.   | REDUCE Procedure             |   |   |   |   |   |   | • | • | • | • | 86   |

| 16.   | PR OK Procedure              |   |   |   |   | • | • | • | • |   |   | 87   |

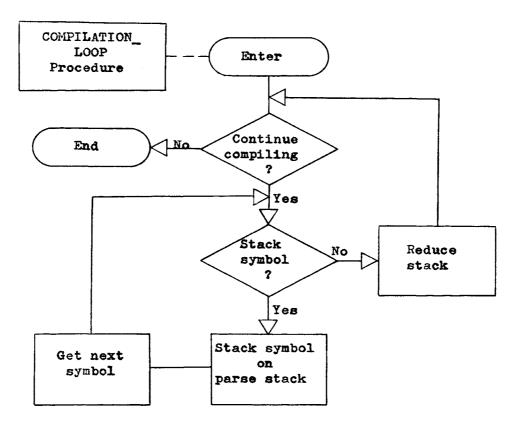

| 17.   | SYNTHESIZE Procedure         |   |   |   |   | - |   |   |   |   | • | 87   |

| 18.   | SPEC LOOKUP Procedure        |   |   |   |   | • |   | • | • | • | • | 87   |

| 19.   | STD LOOKUP Procedure         | • |   |   |   |   |   |   |   |   |   | 88   |

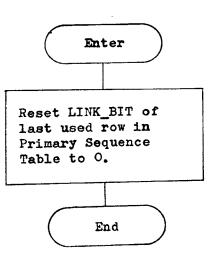

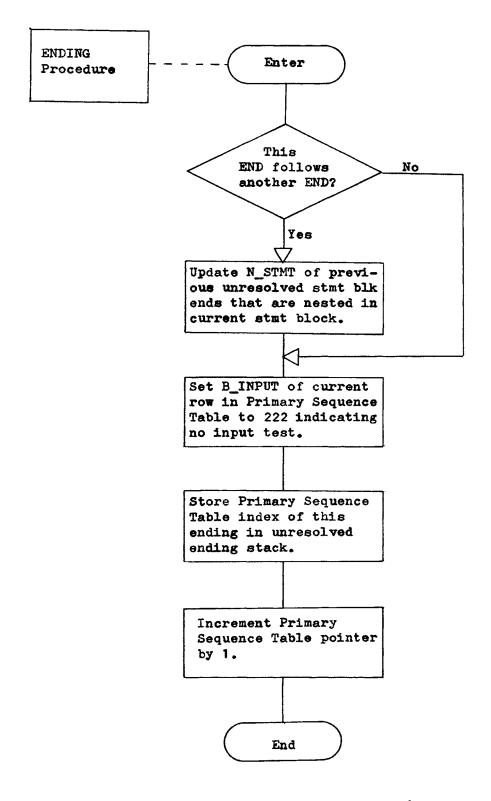

| 20.   | ENDING Procedure             |   |   | • |   | - |   |   |   |   |   | 88   |

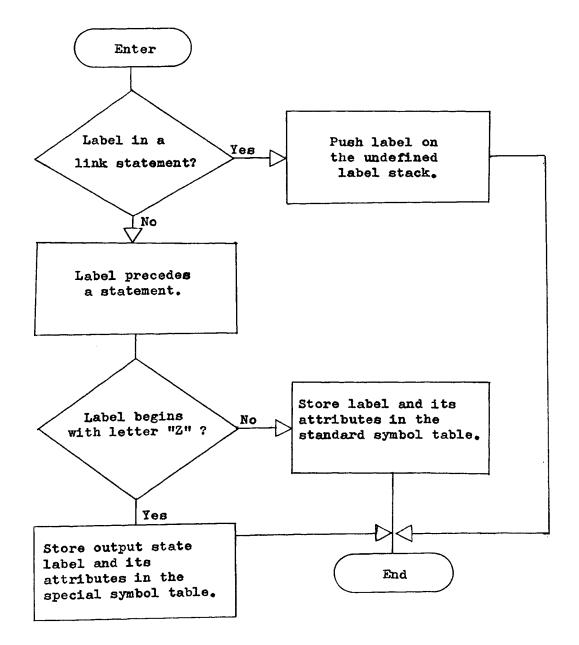

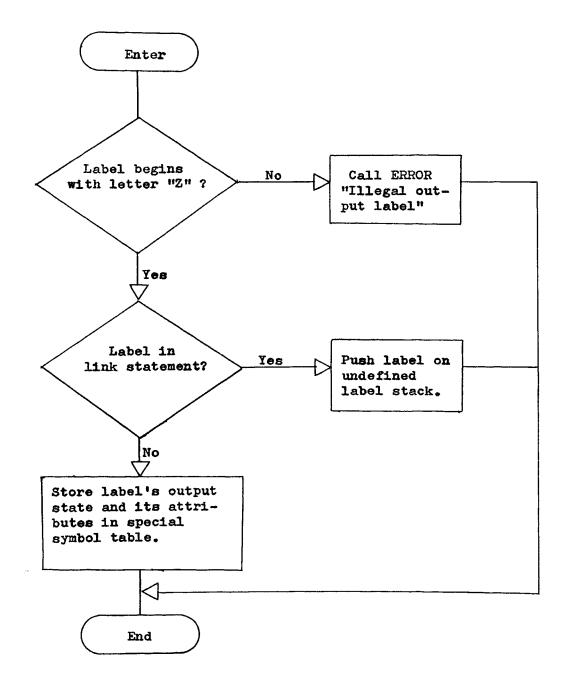

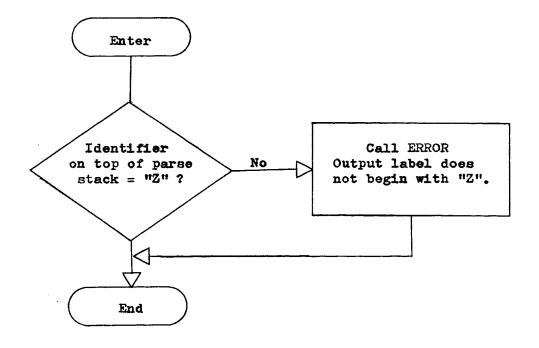

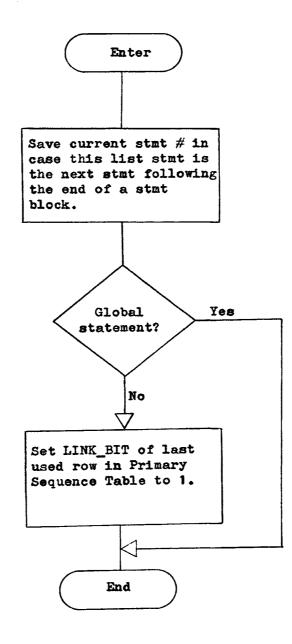

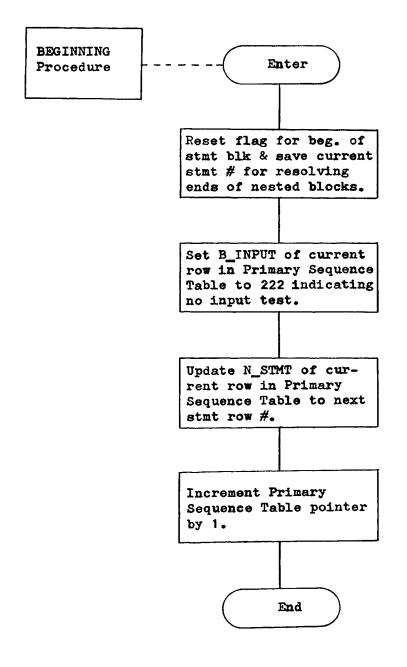

| 21.   | BEGINNING Procedure          |   | • | • |   | • | • | • | • |   |   | 88   |

| 22.   | PAD ZEROS Procedure          | • |   |   | • |   |   | • | • |   |   | 88   |

| 23.   | VARSTORE Procedure           | • | • | • |   | • |   |   |   | • | • | 88   |

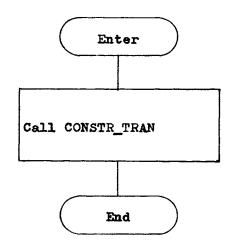

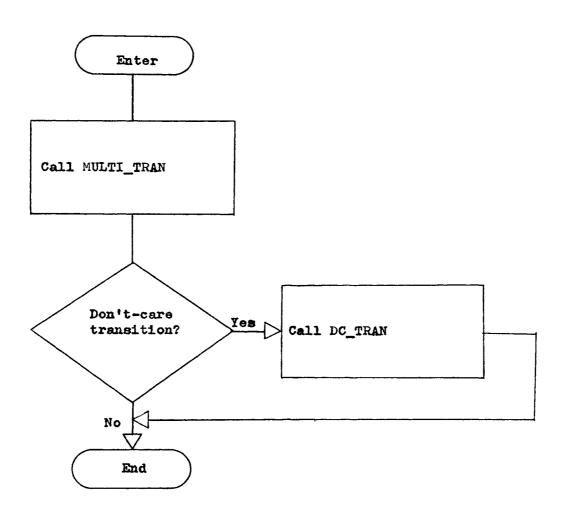

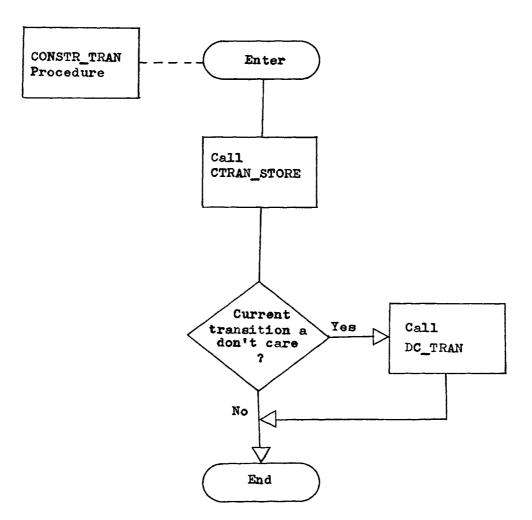

| 24.   | CONSTR TRAN Procedure        | • | • |   | • |   | • |   |   | • | • | 88   |

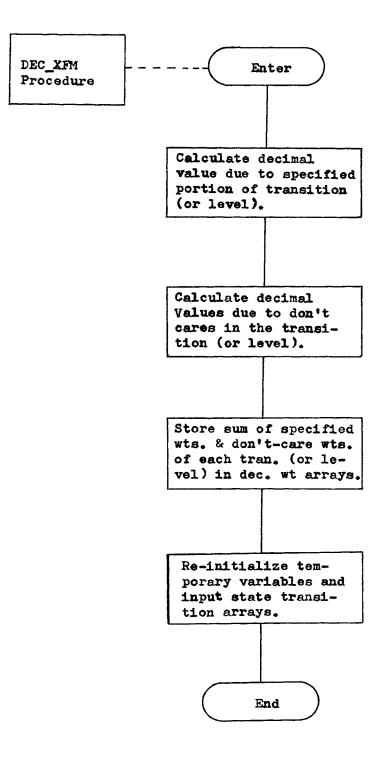

| 25.   | DEC XFM Procedure            |   | • | • |   |   |   | • |   |   | • | 89   |

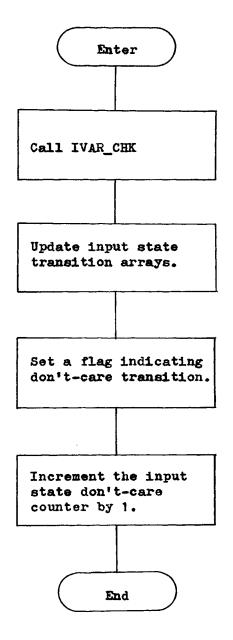

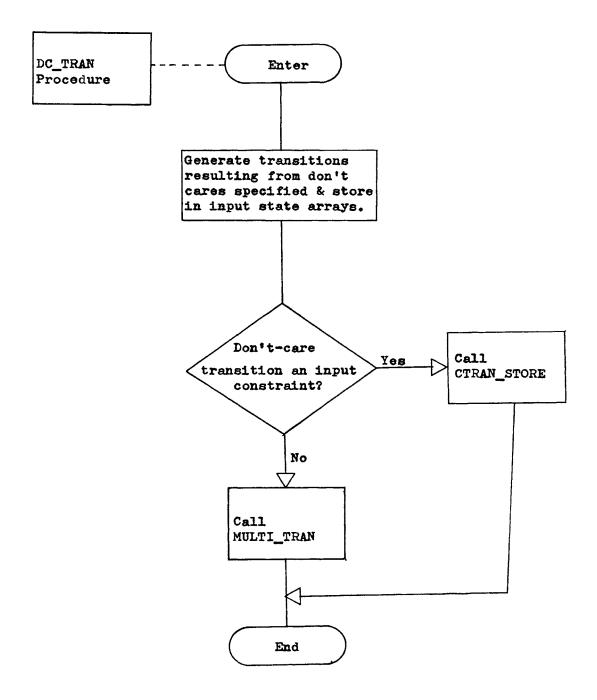

| 26.   | DC TRAN Procedure            |   |   |   |   |   |   | • |   |   |   | 89   |

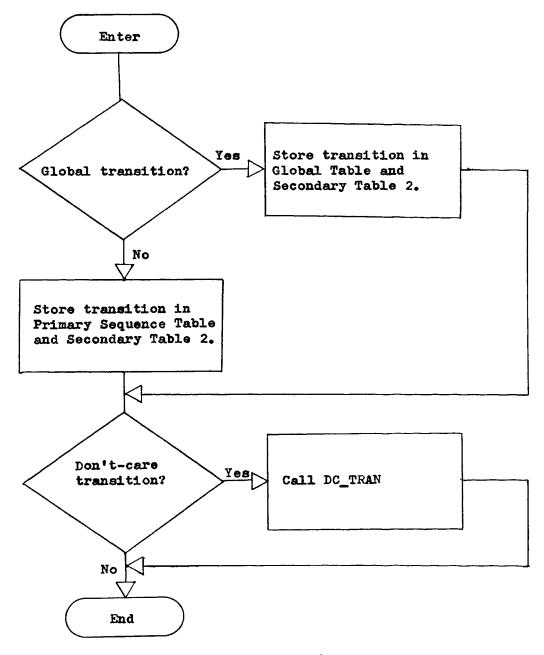

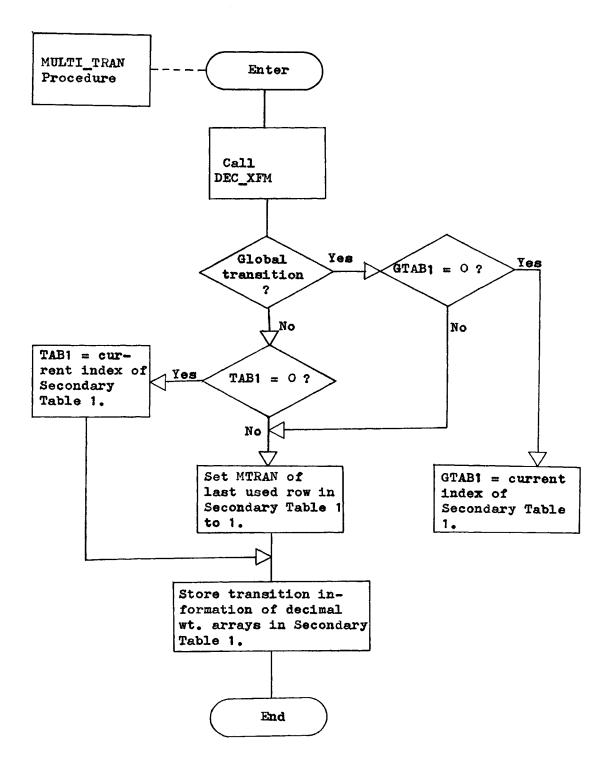

| 27.   | MULTI TRAN Procedure         | • | • |   |   | • | • | • |   | • |   | 89   |

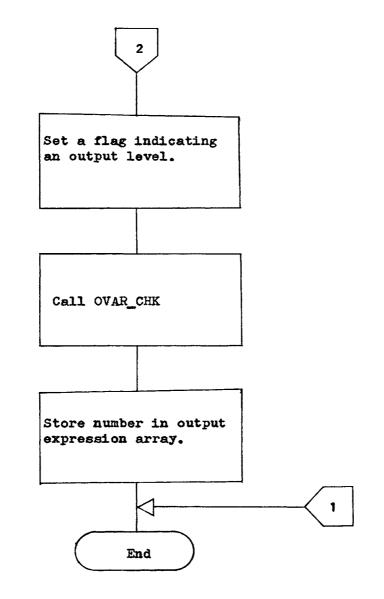

| 28.   | OVAR CHK Procedure           |   |   |   |   |   |   |   |   |   |   | 89   |

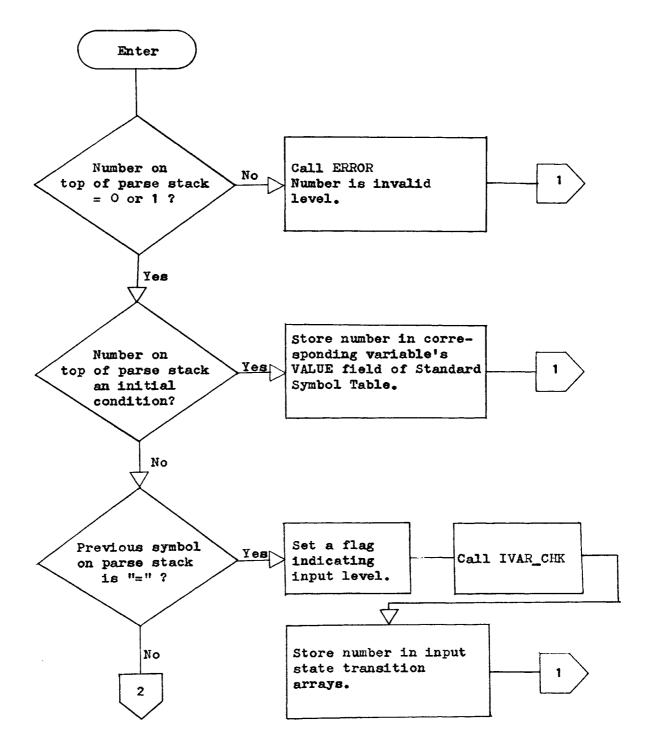

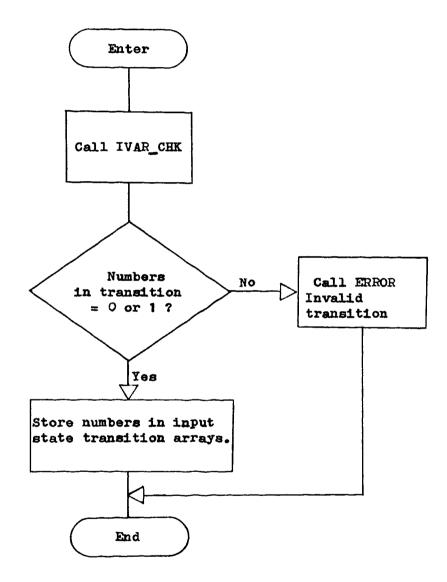

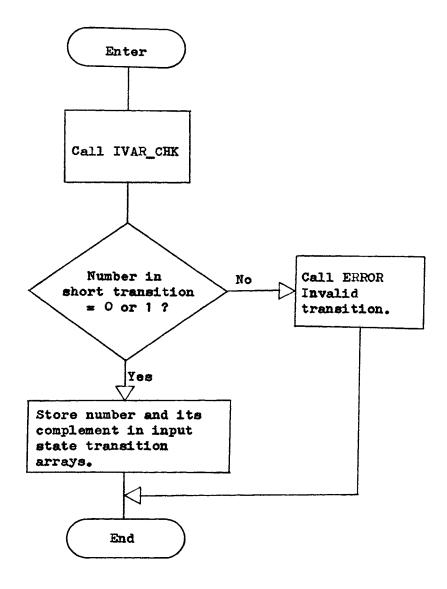

| 29.   | IVAR CHK Procedure           |   |   | • | • |   | • | • | • |   |   | 89   |

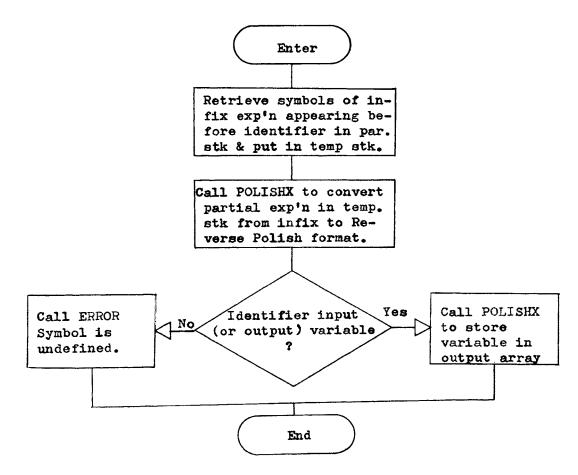

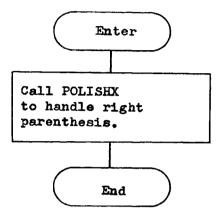

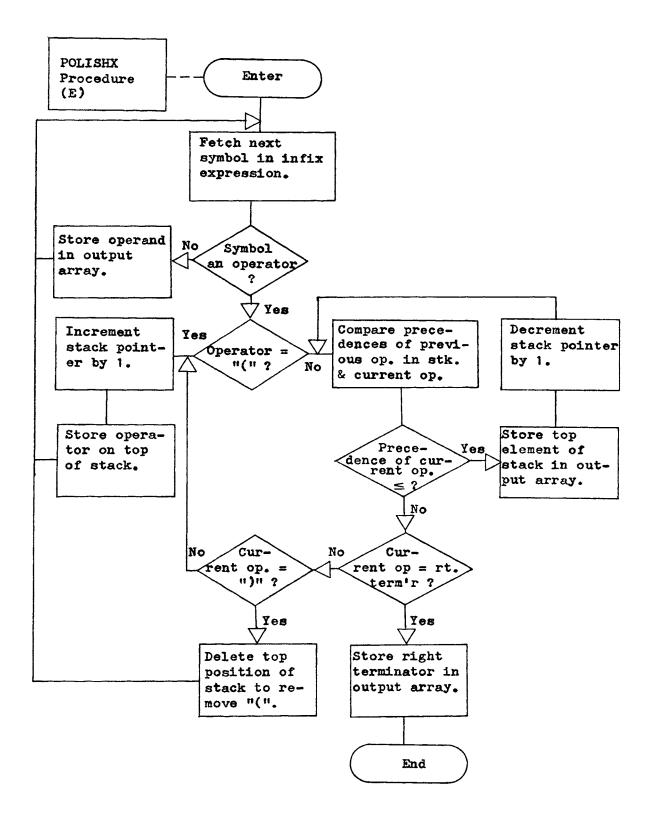

| 30.   | POLISHX Procedure            |   | • |   |   |   | • |   |   |   |   | 89   |

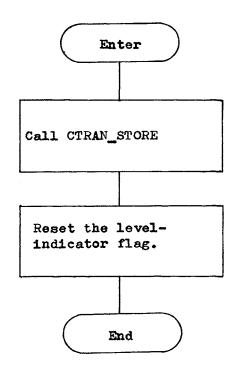

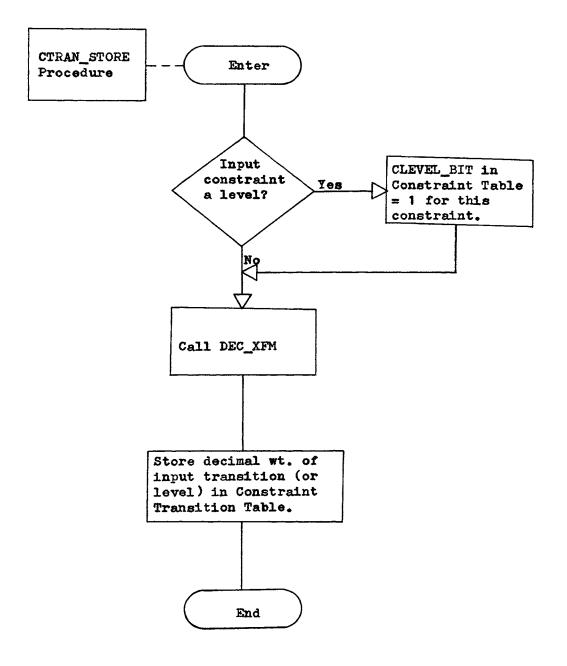

| 31.   | CTRAN STORE Procedure        | • |   |   |   |   |   | • |   |   |   | 89   |

| 32.   | EXPN Procedure               |   | • | • |   | - | • |   | • | • |   | 90   |

| 33.   | PRINT SUMMARY Procedure      |   |   | • |   |   | • |   |   |   | • | 90   |

| 34.   | DUMPIT Procedure             |   |   | • | • |   |   |   | • |   |   | 90   |

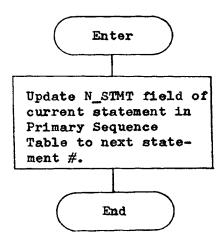

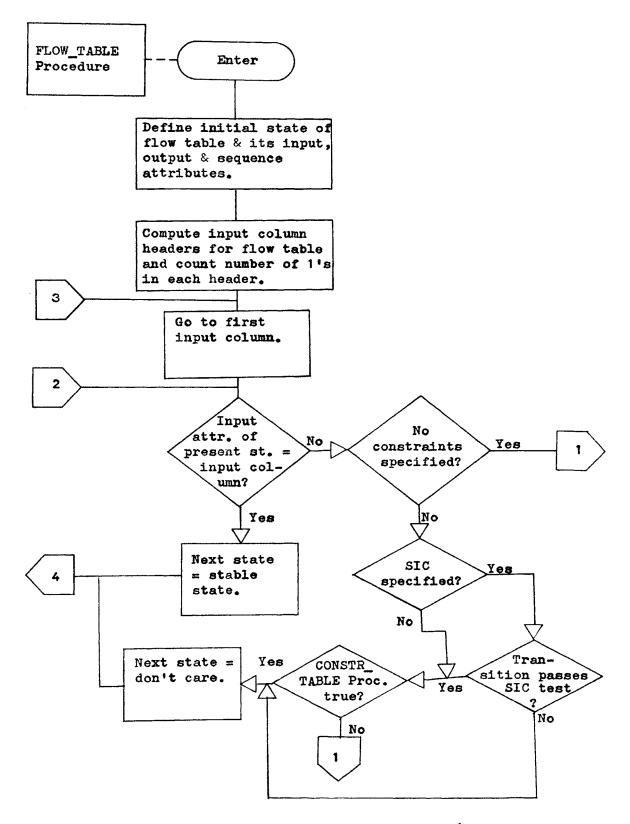

| 35.   | FLOW TABLE Procedure         |   | • | • |   |   | • |   |   |   | • | 90   |

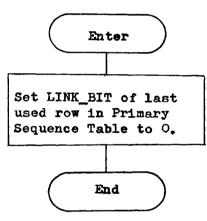

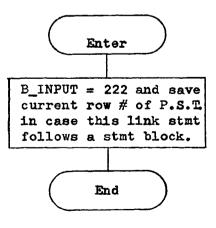

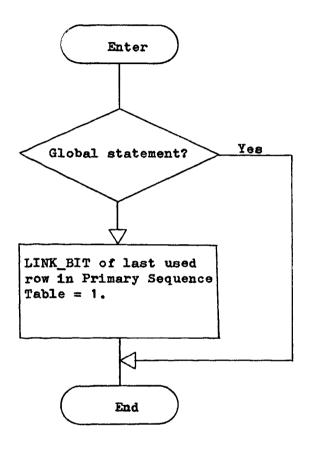

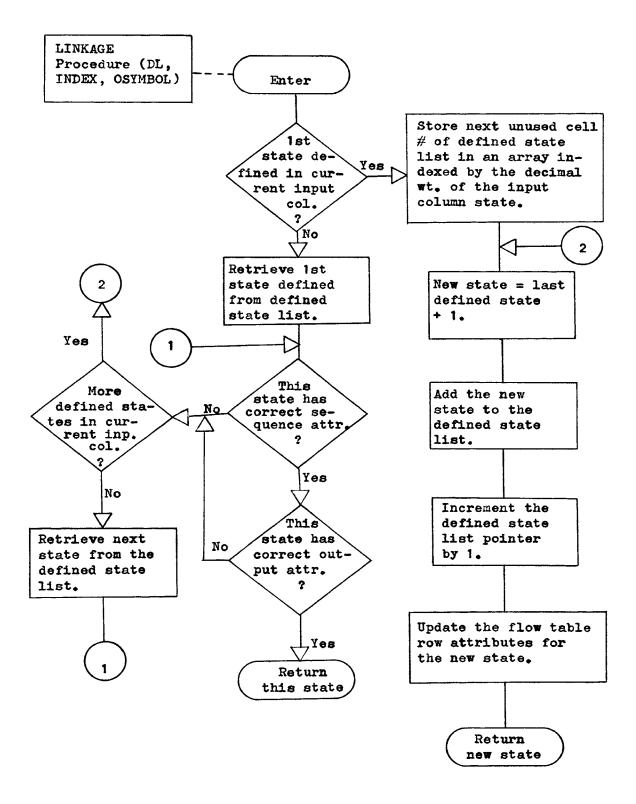

| 36.   | LINKAGE Procedure            |   |   |   |   |   |   |   | - |   |   | 90   |

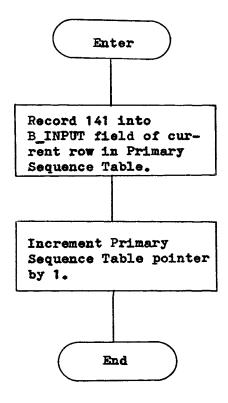

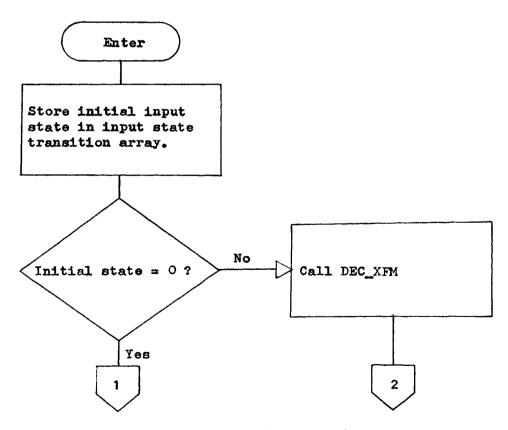

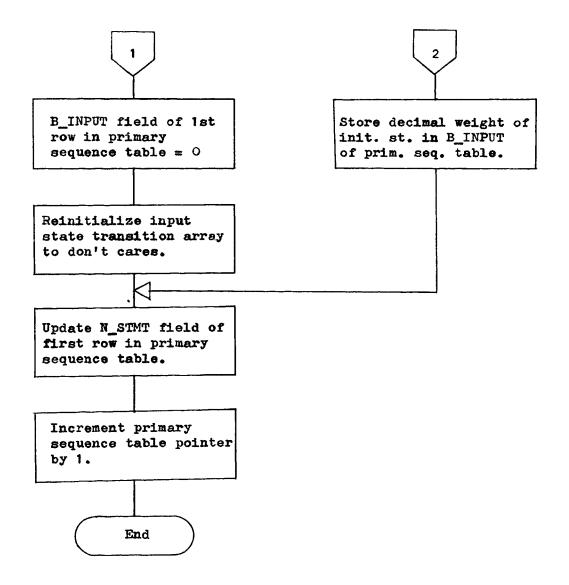

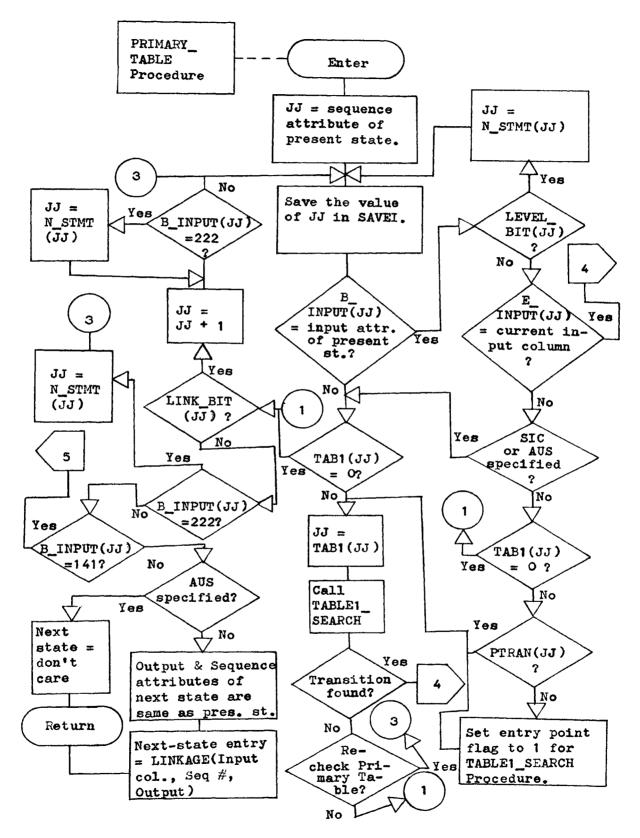

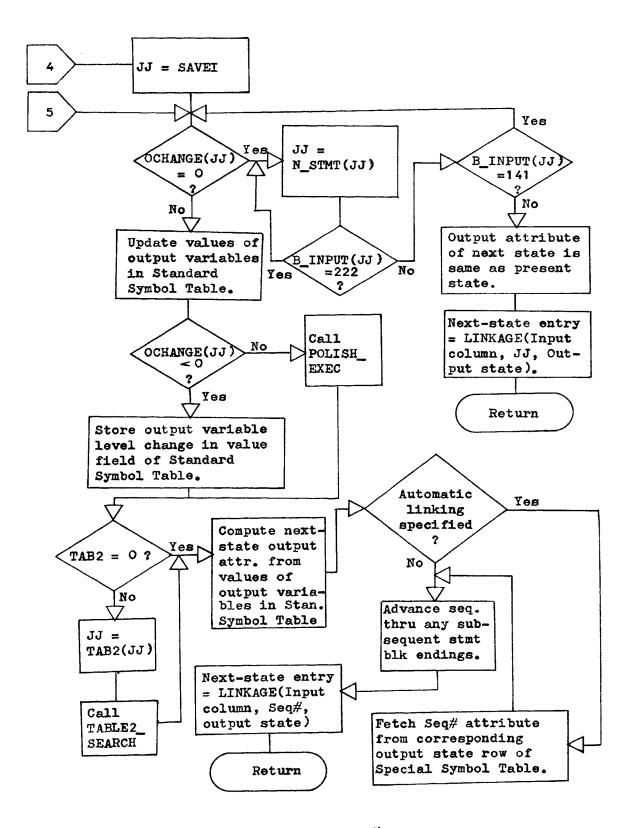

| 37.   | PRIMARY TABLE Procedure      | • |   |   |   |   |   |   |   |   |   | 90   |

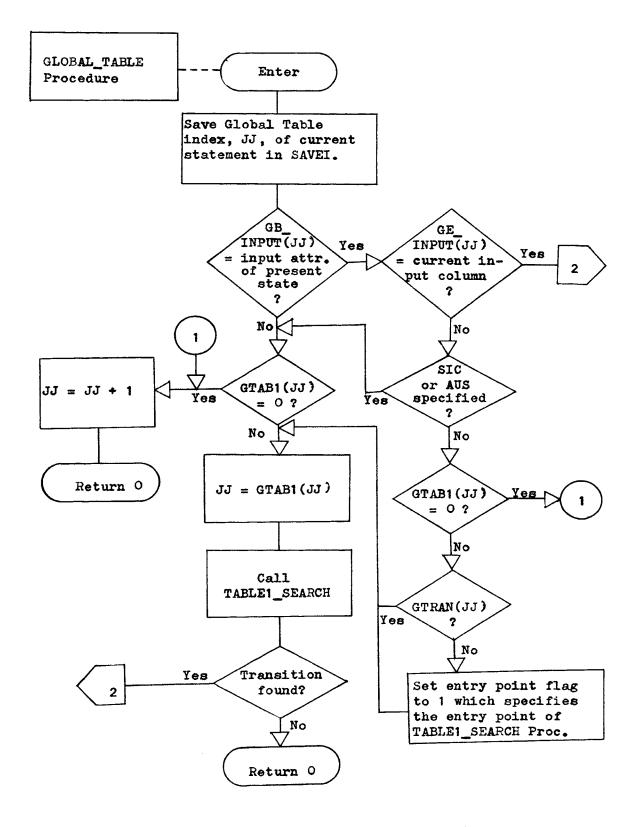

| 38.   | GLOBAL TABLE Procedure       |   |   |   |   |   |   |   |   |   |   | 91   |

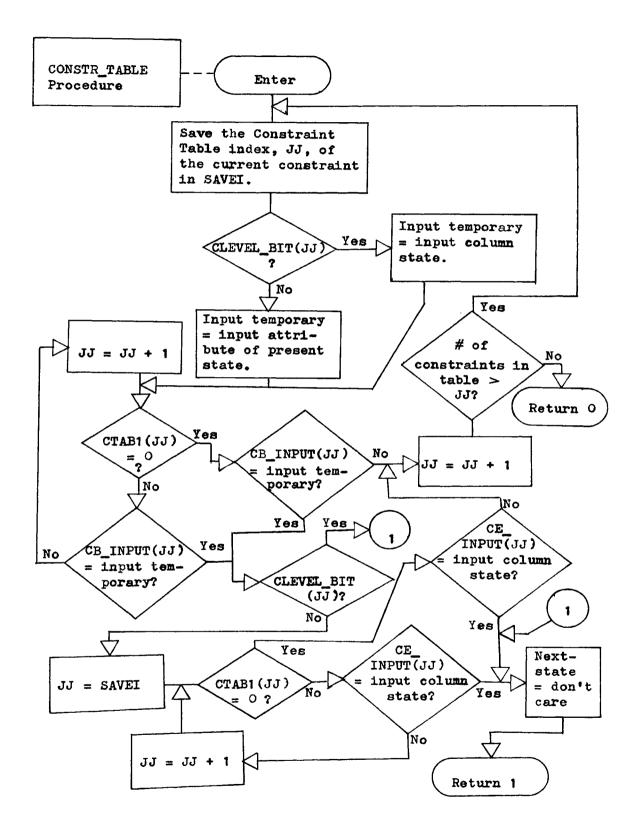

| 39.   | CONSTR TABLE Procedure       |   |   |   | • |   |   |   |   |   | • | 91   |

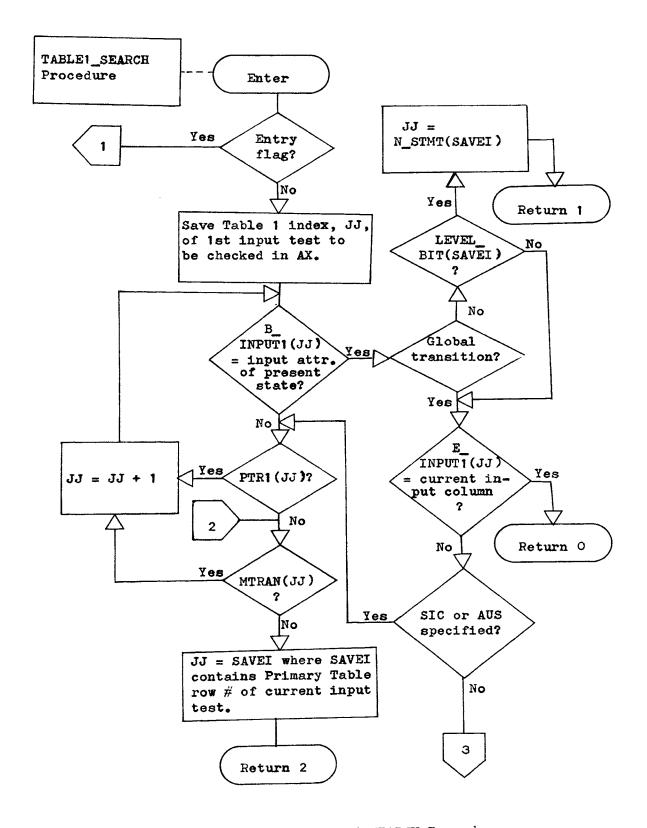

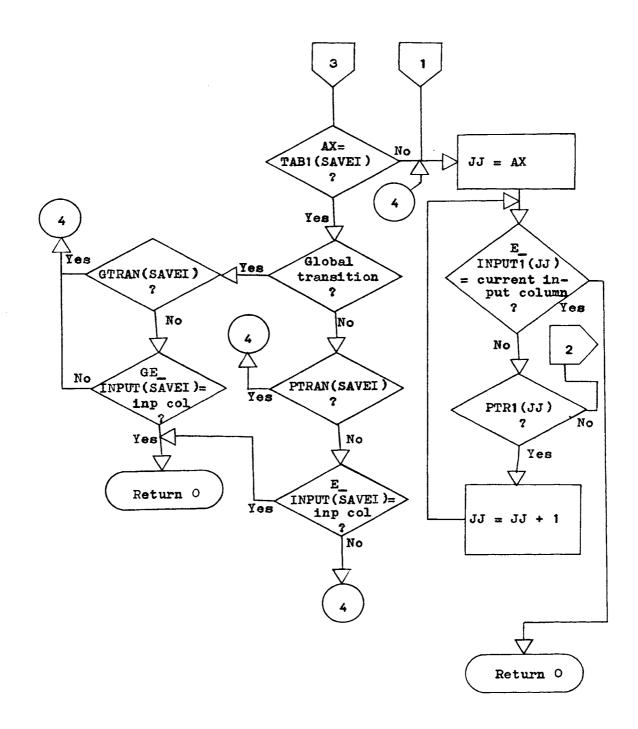

| 40.   | TABLE1 SEARCH Procedure      |   | - |   | • | • |   | • | - | - | - | 91   |

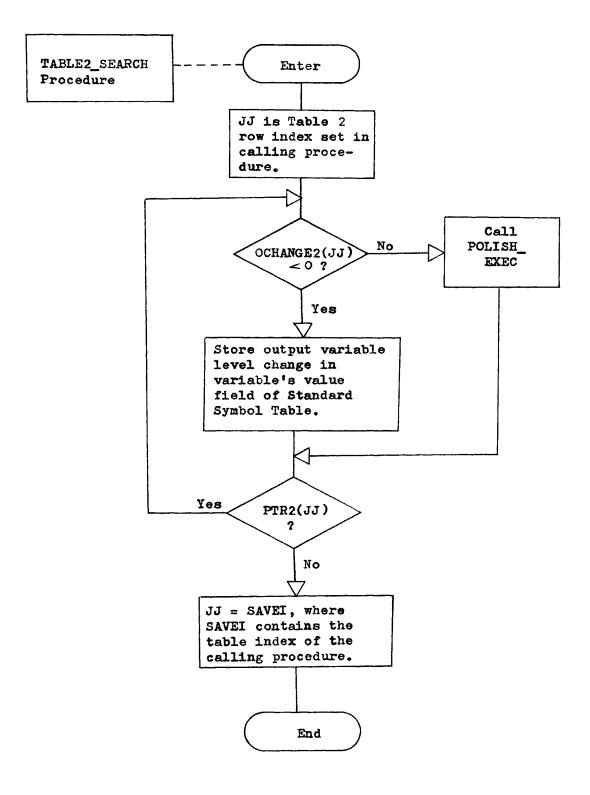

| 41.   | TABLE2 SEARCH Procedure      |   | • |   | - |   |   |   |   |   |   | 91   |

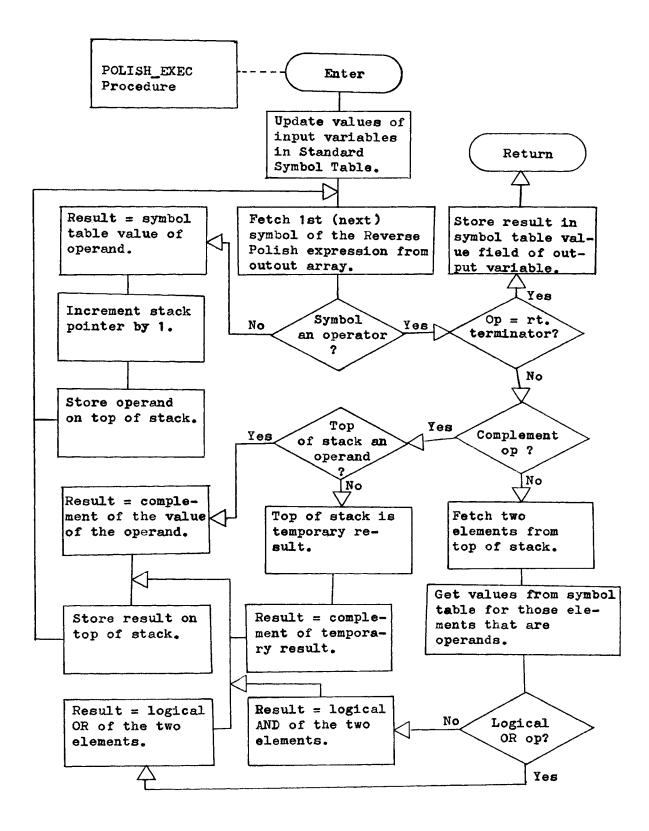

| 42.   | POLISH EXEC Procedure        |   |   | - | - | - | - |   |   | • | • | 92   |

| 43.   | —                            |   | - | - | - | - | - | - | - | • | • | 92   |

| 44.   | PAD Procedure                |   |   |   | - |   |   | • | • | • | • | 92   |

| • • • |                              |   | - | - | - | - | - | - | - | • | - | / 4+ |

# LIST OF ILLUSTRATIONS

| Figu | res P                                                     | age |

|------|-----------------------------------------------------------|-----|

| 1.   | The Interfacing Characteristics of ACDL                   | 1   |

| 2.   | Timing Chart                                              | 6   |

| 3.   | XPL Translator Writing System                             | 33  |

| 4.   | Flow Chart of the Primitive Flow Table Construction       | 37  |

| 5.   | Timing Chart Indicating Allowable Sequences for Example 6 | 49  |

| 6.   | Structure of the ACDL Translator/Interpreter<br>Program   | 79  |

| 7.   | Flow Chart of COMPILATION_LOOP Procedure                  | 93  |

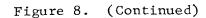

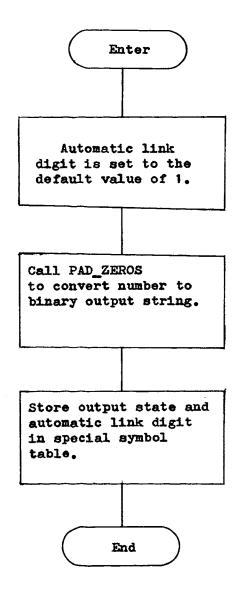

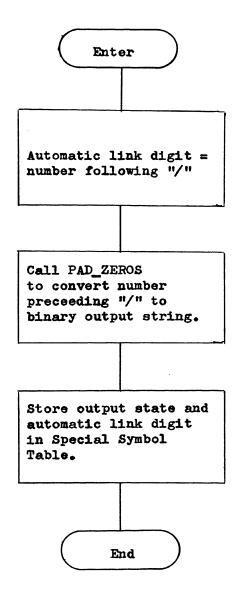

| 8.   | Flow Chart of SYNTHESIZE Procedure                        | 93  |

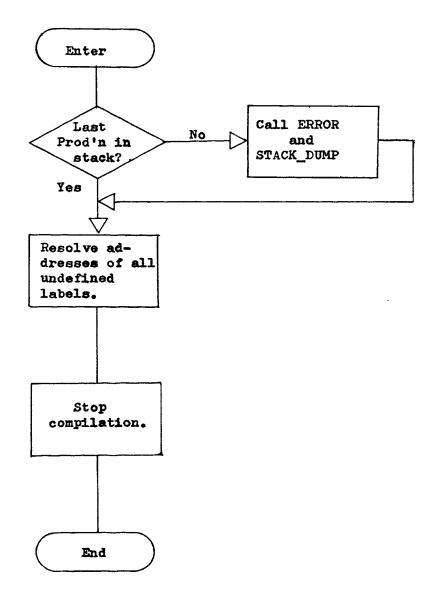

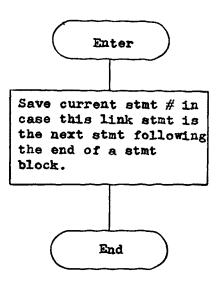

| 9.   | Flow Chart of ENDING Procedure                            | 129 |

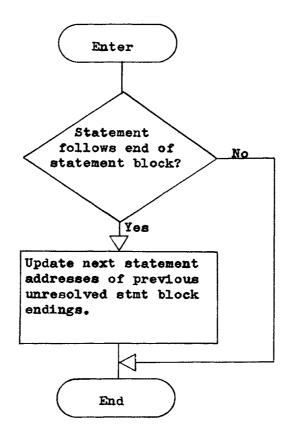

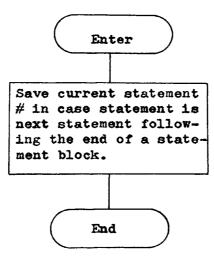

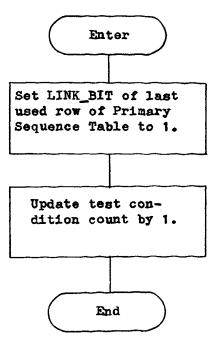

| 10.  | Flow Chart of BEGINNING Procedure                         | 130 |

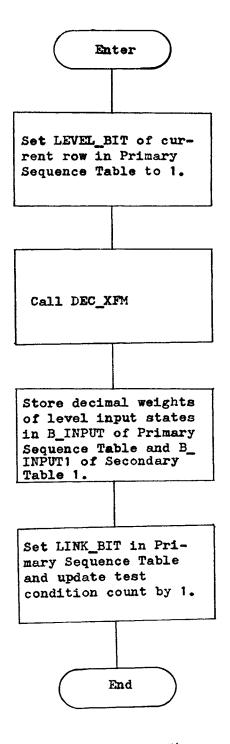

| 11.  | Flow Chart of CONSTR_TRAN Procedure                       | 131 |

| 12.  | Flow Chart of DEC_XFM Procedure                           | 132 |

| 13.  | Flow Chart of DC_TRAN Procedure                           | 133 |

| 14.  | Flow Chart of MULTI_TRAN Procedure                        | 134 |

| 15.  | Flow Chart of POLISHX Procedure                           | 135 |

| 16.  | Flow Chart of CTRAN_STORE Procedure                       | 136 |

| 17.  | Flow Chart of FLOW_TABLE Procedure                        | 137 |

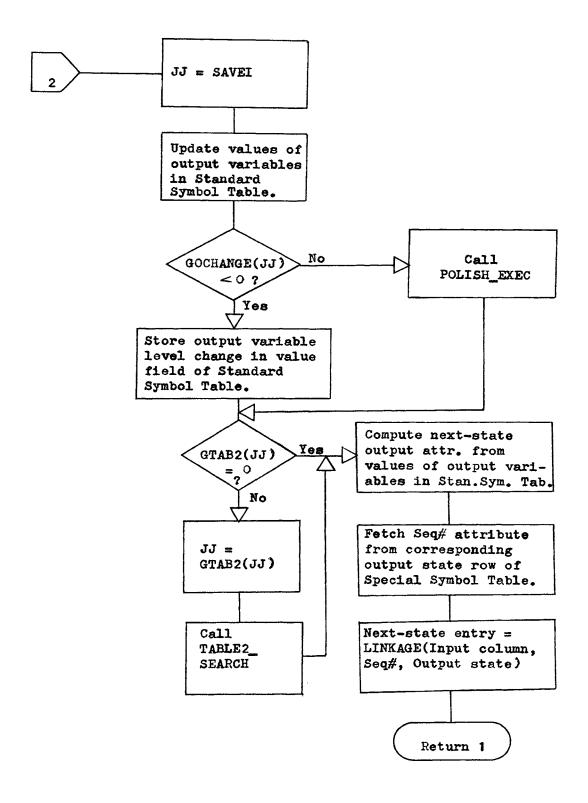

| 18.  | Flow Chart of LINKAGE Procedure                           | 139 |

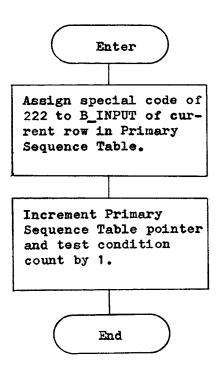

| 19.  | Flow Chart of PRIMARY_TABLE Procedure                     | 140 |

| 20.  | Flow Chart of GLOBAL_TABLE Procedure                      | 142 |

| 21.  | Flow Chart of CONSTR_TABLE Procedure                      | 144 |

| Figu | res  |       |    |         |        |           |   |   |     |   |   |   |   |   |   | H | age |

|------|------|-------|----|---------|--------|-----------|---|---|-----|---|---|---|---|---|---|---|-----|

| 22.  | Flow | Chart | of | TABLE1_ | SEARCH | Procedure | e | • | • • | • | • | • |   | • | ٠ | • | 145 |

| 23.  | Flow | Chart | of | TABLE 2 | SEARCH | Procedur  | e | • |     | • | • | • | • | • | • | • | 147 |

| 24.  | Flow | Chart | of | POLISH  | EXEC P | rocedure  | • | • | • • | • | • | • |   | • | • | • | 148 |

# LIST OF TABLES

| Table  |                                                           | Pa | ıge |

|--------|-----------------------------------------------------------|----|-----|

| I.     | FLOW TABLE                                                | •  | 4   |

| II.    | PRIMITIVE FLOW TABLE                                      | •  | 7   |

| III.   | EXAMPLES OF BOOLEAN EXPRESSIONS                           | •  | 14  |

| IV.    | SHORTHAND NOTATION FOR RELATION EXPRESSIONS               | •  | 14  |

| V.     | EXAMPLES OF THE RELATION EXPRESSION                       | •  | 15  |

| VI.    | EXAMPLES OF LABELS                                        | •  | 16  |

| VII.   | EXAMPLES OF THE DESIGN AND DECLARE STATEMENTS             | •  | 19  |

| VIII.  | EXAMPLES OF THE TRANSITION STATEMENT                      | •  | 21  |

| IX.    | EXAMPLES OF LINK STATEMENTS                               | •  | 23  |

| х.     | EXAMPLES OF THE LIST STATEMENT                            | •  | 25  |

| XI.    | COMMENT CONTROL OPTIONS                                   | •  | 27  |

| XII.   | SUMMARY OF ACDL                                           | •  | 30  |

| XIII.  | PARTIAL FLOW TABLE                                        | •  | 41  |

| XIV.   | RESULTING FLOW TABLE FOR EXAMPLE DESIGN                   | •  | 42  |

| XV.    | PRIMITIVE FLOW TABLE FOR EXAMPLE 1                        | •  | 44  |

| XVI.   | PRIMITIVE FLOW TABLE FOR EXAMPLE 2                        | •  | 44  |

| XVII.  | PRIMITIVE FLOW TABLE FOR EXAMPLE 3                        | -  | 46  |

| XVIII. | THREE BIT GRAY CODE                                       | •  | 46  |

| XIX.   | PRIMITIVE FLOW TABLE FOR EXAMPLE 4                        | •  | 47  |

| XX.    | PRIMITIVE FLOW TABLE FOR EXAMPLE 5                        | •  | 48  |

| XXI.   | PRIMITIVE FLOW TABLE FOR EXAMPLE 6                        |    | 51  |

| XXII.  | PRIMITIVE FLOW TABLE FOR EXAMPLE 7                        | •  | 52  |

| XXIII. | A TABLE DUMP OF THE INTERNAL FORM FOR EXAMPLE<br>DESIGN 9 | •  | 59  |

## I. INTRODUCTION

A number of synthesis procedures for asynchronous sequential circuits now exist and many of these have been programmed for computer application. Although considerable work has been directed toward improving the synthesis procedures, little has been done in interfacing the user to these procedures.

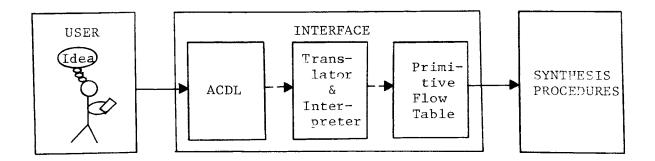

This dissertation presents an Asynchronous Circuit Design Language (ACDL) system which interfaces the user to the conventional synthesis procedures of asynchronous sequential circuits as illustrated in Figure 1. ACDL is a special purpose language used to describe the terminal behavior of asynchronous sequential circuits. This description is then translated, and interpreted into a primitive flow table which is the initial input requirement of the conventional synthesis procedures.

Figure 1. The Interfacing Characteristic of ACDL

Presently, a few procedures exist for specifying asynchronous sequential circuits when the terminal characteristics of the machine are easily expressed in input/output sequences [1,2]. However, only a small percentage of the designs are suitable for this type of terminal description. Hence typically, the designer will hand-construct a

1

primitive flow table from a word statement or mental conception of the problem. This is not an easy or straightforward task since word statements and mental conceptions are informal descriptions of the problem.

After studying the specification problem for some time, it was decided that a language was needed that had the following three important characteristics:

- it should permit ease of expression by coinciding with the designer's thinking process,

- 2) it should retain a formal meaning of the circuit description,

- it should have a structure which would permit relatively easy automatic translation.

A review of all the well-known digital design languages was made to determine their applicability to the asynchronous circuit specification problem [3-9]. In general, it was found that these languages were intended for networks whose designs could best be described by functional operations and information transfers between basic hardware elements such as registers, switches, terminals, memory etc. None of the above languages were found to satisfy all of the desired characteristics mentioned for specifying the terminal (input/output) behavior of an asynchronous sequential circuit. Specific drawbacks of these languages included the inability to assign transition values to variables, the inability to make proper declarations such as "input constraints" and the inability to list multiple independent sequence paths without introducing additional control variables or cluttering the listing with many "go to" type statements.

ACDL was developed to meet the three important characteristics of the desired language and to overcome the drawbacks of the digital design

2

languages noted above. This language provides a means to satisfy the specification problem by enabling the user to express his circuit characteristics formally, so the design can be carried out automatically.

#### II. ASYNCHRONOUS SEQUENTIAL CIRCUITS

Sequential circuits whose operation is not synchronized with clock pulses are called asynchronous sequential circuits. An important advantage of asynchronous sequential circuits is their ability to respond to input changes at basic device speed, rather than having to await the arrival of clocking signals. Also, many small circuits can be designed more easily and efficiently asychronously because it is not necessary to build a clock and synchronization circuitry. A further advantage of asynchronous design is seen in large circuits where signal lines are long and the skewing effect (difference in path propagation times) of the distributed clocking signals becomes a serious problem.

The operation of an asynchronous sequential circuit is often described by means of a flow table. As shown in Table I, it is a twodimensional array consisting of next-state entries with its columns representing the input states and its rows representing the internal states of the circuit. The row in which the circuit is currently operating is often referred to as the present internal state or just the present state. For example, if the present state of the circuit described by Table I is 1 and then an input of  $I_2$  is applied, the next state or state that the circuit will go to is 2.

|          |   | In             | put sta        | tes            |   |   |  |

|----------|---|----------------|----------------|----------------|---|---|--|

|          |   | I <sub>1</sub> | 1 <sub>2</sub> | 1 <sub>3</sub> |   |   |  |

|          | 1 | 1/0            | 2              | 3              | - |   |  |

| Internal | 2 | 1              | 2/0            | 3              |   |   |  |

| States   | 3 | 1              | 4              | 3/0            |   |   |  |

|          | 4 | 1              | 4/1            | 3              |   | _ |  |

TABLE I. FLOW TABLE

If a next-state entry is found to be the same as the internal state representing that row, then the internal state is said to be stable with respect to that input column and is denoted by a circled next-state entry. Output states are usually only associated with stable next states as shown.

An asynchronous circuit is said to be operating in fundamental mode if the inputs are never changed unless the circuit is in a stable state. This paper only treats asynchronous circuits operating in fundamental mode. Further information on this class of circuits can be found in references [10] and [11].

#### A. The Conventional Design Process

The design process for asynchronous circuits can be divided into two major parts. The first part provides a formal description of the circuit's behavior such as a flow table. Based upon this formal description, the second part applies established synthesis techniques to generate the circuit design equations. These techniques include flow table reduction, internal-state assignment, hazard elimination and nextstate and output equation generation [10,11].

Computer programs have made the synthesis techniques entirely automated. D. G. Raj-Karne [12] has recently programmed algorithms to provide either a Unicode Single Transition Time (USTT), Universal Totally Sequential (UTS) or combination USTT and UTS (Mixed Mode) state assignment. A flow table reduction algorithm and an algorithm to generate the static-hazard-free design equations have been programmed by R. J. Smith et al. [2,13].

5

#### B. Circuit Specification

#### 1. Initial Descriptions

Presently, the most common initial description of a design is the English-word statement. This is an informal description that must be reworked into some type of formal description (usually a flow table). The word statement lacks total preciseness and often reflects uncertainty for many input/output conditions. An example of a typical word statement description is:

> A sequential circuit is to have two inputs A and B and one output Z. Z is to turn on only when B turns on, provided A is already on. Z is to turn off only when B turns off. Only one input can change state at a time.

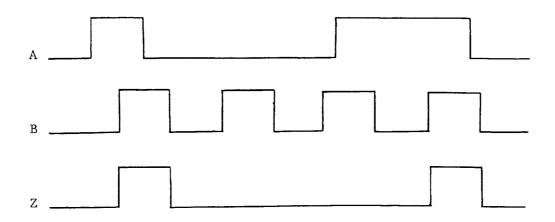

In some designs a word statement may be accompanied by a timing chart [14,15] to express more explicitly particular input/output sequences required of the circuit. The timing chart usually does not show all possible input/output sequences of the circuit but rather shows important sequences which may help clarify the word statement. An example of the timing chart for the above word statement is shown in Figure 2.

Figure 2. Timing Chart

### 2. Primitive Flow Table

In order to make the initial description more precise and appropriate for formal manipulation in the conventional synthesis procedures, the circuit specifications are made in the form of a flow table having exactly one stable state per row. This special table is called a primitive flow table [10,11,14,15] and is illustrated in Table II for the word statement description discussed earlier.

| Internal<br>State | A B<br>00 | 01 | 11 | 10 | Z |

|-------------------|-----------|----|----|----|---|

| 1                 |           | 2  | _  | 3  | 0 |

| 2                 | 1         | 2  | 4  | -  | 0 |

| 3                 | 1         | -  | 5  | 3  | 0 |

| 4                 | -         | 2  | 4  | 3  | 0 |

| 5                 | -         | 6  | 5  | 3  | 1 |

| 6                 | 1         | 6  | 5  | _  | 1 |

TABLE II. PRIMITIVE FLOW TABLE

In constructing the primitive flow table, first a static situation corresponding to the initial state of the circuit is defined. This is usually (but not always) the state where all inputs and outputs are zero as indicated by stable state 1 in Table II. When operating in the initial stable state, the remaining next-state entries for row 1 are completed. Dash entries represent illegal input transitions which are later used in the synthesis as don't-cares. The dash in row 1 means the input transition 00 to 11 is illegal which agrees with the word description constraint of no inputs changing simultaneously. It isn't until state 5 is reached via state 3 that the output is set which concurs with the word description for setting Z.

For practice, the inexperienced reader should verify the remaining rows of the flow table. As seen from this example, considerable thought and time is required to construct the primitive flow table.

3. Other Methods

A method of specifying asynchronous circuits using input/output (I/O) sequences which could be translated into a flow table was developed by Altman [1]. However, the inefficiency of having to repeat long specification lists of I/O pairs at branch points and the inability to describe cyclic behavior of indeterminate duration greatly restricts the use of this method.

By developing a looping and branching technique and enabling the use of don't-care specifications, Smith [2] extended Altman's method to satisfy the above deficiencies. Smith's method is based on the philosophy that independent I/O sequences define submachines or modules; and when properly interconnected, these modules form the required sequential circuit. The method was primarily intended for those designs which originate from a circuit description having a set of I/O sequences and hence, is too restrictive to be a good, generalized design method. Since most designs originate from word descriptions or mental conceptions of an operative nature, listing the set of all independent I/O sequences for these designs becomes a difficult and confusing task.

A different approach to the synthesis of fundamental-mode asynchronous circuits was developed by Chuang [16] and is referred to as the transition logic synthesis method. In this method a binary level

8

transition of 0 to 1 or 1 to 0 is considered as a pulse, and the realization of the circuit is similar to the standard pulse sequential circuit synthesis method [10]. Since no distinction is made between 0 to 1 and 1 to 0 transitions, the application of this method is limited to problems such as counters, where the toggling effect of the transition is of interest rather than the value of the transition's ending state. The specifications are made into an array called a transition flow table. Although the table may have fewer states than an equivalent primitive flow table, the unnatural specification method of flow table construction still exists.

#### III. A DESCRIPTION OF ACDL

This chapter contains a syntactic and semantic description of ACDL. The description begins with the lowest structural level of symbols and progresses to the higher structural levels of statements and programs. A. The Definition of a Metalanguage

To prevent any ambiguities or paradoxes in the definition of ACDL, a metalanguage which is completely distinguishable from ACDL will be used in its description. To formalize the definitions in the metalanguage, each definition is given in the form of a statement or construct, which is analogous to a formula. The metalanguage employed is Backus Normal Form (BNF) [17] and consists of the following symbols:

- $\langle x \rangle$  to be read as "the object named x"

- ::= to be read as "can be formed from"

- to be read as "or" (exclusive or)

The metalanguage construct takes on the following meaning: "the object named in the corner braces may be formed from the objects named or specified on the right". Concatenation of names or objects is implied by the juxtaposition of names or objects in the construct. For clarity, those characters which are to form part of ACDL and the metalanguage symbols will be set in standard type while the names of objects enclosed in corner braces will be italicized.

B. Vocabulary of ACDL

1. Symbols

The set of symbols used in ACDL are defined as follows: <letter := A|B|C|...|Z|#|\_|@|\$|' <binary digit >::= 0|1 10

<nonbinary digit>::= 2|3|4|5|6|7|8|9

<digit>::= &pinary digit>| <nonbinary digit>

<special character>::= "|/|?

<separator>::= , |; |:|.|(|)

<relation symbol>::= = |->|=>

<replacement op>::= <<li>dogical op>::= - |&|+

The relation symbol '->' is the transition symbol and is read as "makes a transition to", and '=>' is the implication symbol which is read as "implies that" or "causes". The special characters have special meanings in ACDL, and each will be explained later in the description at the place it is used. All other symbols take on their standard interpretations [3-9], [18].

2. Constants and Identifiers

The rules for constructing constants and identifiers from the symbols of ACDL are:

<constant>::= <number>|<level>|<transition>

<number>::= <digit>|<number><digit>

<level>::= <binary digit>

<transition>::= <long transition>|<short transition>

<long transition>::= 0->1|1->0

<short transition>::= ->1|->0|->?

<identifier>::= <letter>|<identifier> <letter>|<identifier> <letter>|<identifier> <letter>|<identifier> <letter>|<identifier>

Circuit input variables will take on transition values as well as level values. In many cases, both the beginning and ending states of an input transition are important in determining the resulting output level. The transition constant '0->1' indicates a transition from 0 to 1. The short transition is a shorthand notation for a long transition constant. For example, '->1' and '->0' are short for '0->1' and '1->0', respectively. The short transition '->?' represents a don'tcare transition which essentially says that a transition is to occur and "you don't care" if it is a '0->1' or a '1->0' transition. This shorthand notation is a valuable asset to the user in making quick and easy specifications.

As in PL/I [18], the identifier may consist of both letters and digits with the restriction of beginning with a letter. Ideally, ACDL permits identifiers to be of an arbitrary length. However due to implementation restrictions of the current ACDL translator, the length of an identifier is limited to 256 characters.

3. Relations and Expressions

All expressions in ACDL are logical expressions. There are two types of logical expressions: the transition relation expressions and the Boolean variable expressions. The following rules for constructing these expressions will become more clear as the discussion progresses.

<level relation>::= <identifier> = <level>|<level relation> & <identifier> = <level>|(<level relation>)<transition relation>::= <identifier> = <long transition> |<identifier> <short transition> |<transition relation> & <identifier> =<long transition>|<transition relation> & <identifier> <short transition>|(<transition relation>) <dummy term>::= LINKTEST | LK'T

<Boolean expression>::= <logical factor>|<Boolean expression> + <logical factor>

<logical factor>::= <logical term>|<logical factor>  $_{\&}$  <logical term>

<logical term>::= <logical primary> |¬ <logical primary> <logical primary>::= <level> |<identifier> |(<Boolean expression>)

Since all expressions are logical quantities, they evaluate to either of two values; true or false. The level and transition relations become true whenever the values of the identifiers equal the values of the constants. Similarly, the compound relation becomes true whenever the transition relation becomes true while the level relation is true. In circuit terminology this means some variables are to make a transition while others remain fixed. The dummy term, LINKTEST (LK'T) serves a special function which is described later in conjunction with the link statement.

The Boolean expression is the standard logical variable expression [3-10],[18]. Examples of this Boolean expression are given in Table III.

Free parenthetical form is permitted in Boolean expressions. However, if the order of logical operations is not specified by parenthesis, then the logical operators are applied in the standard hierarchical order of ''', '&' and '+' [18].

| TABLE III.        | EXAMPLES OF BOOLEAN EXPRESSIONS               |

|-------------------|-----------------------------------------------|

| Expression        | Explanation                                   |

| 1                 | logic level l                                 |

| А                 | Boolean variable A                            |

| ¬Ζ                | Complement of Z                               |

| (A + B) & C       | Logical OR of A and B<br>ANDed with C         |

| $\neg A + \neg B$ | Logical OR of the com-<br>plements of A and B |

Table IV further explains the use of the shorthand transition notation discussed earlier, and examples of the relation expression are given in Table V.

| Expression                     | Shorthand Notation |

|--------------------------------|--------------------|

| $\mathbf{X} = 0 \rightarrow 1$ | <b>X</b> -> 1      |

| $\mathbf{X} = 1 \rightarrow 0$ | <b>x</b> -> 0      |

| (X = 0 -> 1) +<br>(X = 1 -> 0) | x -> ?             |

TABLE IV. SHORTHAND NOTATION FOR RELATION EXPRESSIONS

4. Statement Labels

As in all programming languages, labels provide a means to select statements for execution that do not follow in the listed sequence [3-7, 18]. In ACDL there are two different types of labels: standard labels and output labels. These are further described as follows:

<label>::= <standard label>: <output label>: <standard label>::= <letter (except Z)>|<standard label> <letter>|<standard label> <digit></output label>

| Expression                         | Read As                                                                           | Logical Meaning                                                                                | Informal Meaning                                         |

|------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| x1->1                              | Xl makes a transition<br>to l                                                     | Xl goes from O to l                                                                            | Xl turns on<br>Xl goes up etc.                           |

| x1->1 &<br>x2->0                   | Xl makes a transition<br>to l and X2 makes a<br>transition to O<br>simultaneously | Xl goes from 0 to 1 and<br>X2 goes from 1 to 0<br>simultaneously                               | Xl turns on at the same time<br>X2 turns off             |

| x1->1 + x2->0                      | Xl makes a transition<br>to 1 or X2 makes a<br>transition to 0                    | Xl goes from 0 to 1 or<br>X2 goes from 1 to 0                                                  | X1 is to turn on or<br>X2 is to turn off                 |

| x1->?                              | X1 makes a transition                                                             | Xl goes from 0 to 1 or<br>Xl goes from 1 to 0                                                  | Xl changes state i.e. it either<br>turns on or turns off |

| x1->? &<br>x2->?                   | Xl makes a transition<br>and X2 makes a tran-<br>sition simultaneously            | X1 and X2 go from<br>00 to 11<br>or 11 to 00<br>or 01 to 10<br>or 10 to 01                     | X1 and X2 change state<br>simultaneously                 |

| $X1 \rightarrow 1$ WHILE<br>X2 = 1 | Xl makes a transition<br>to l while X2 equals l                                   | X1 goes from 0 to 1<br>while X2 stays at 1<br>i.e., inputs X1, X2<br>go from state 01 to<br>11 | Xl turns on while X2 is<br>held on                       |

# TABLE V. EXAMPLES OF THE RELATION EXPRESSION

<output label>::= Z <output code>| Z (<output state set>)

<output state set>::= <output code>|<output state set>, <output</pre>

code>

<output code>::= <binary digit>|<output code> <binary digit>|

# <output code>/<number>

The letter Z is reserved for the beginning character of output labels, and it is followed by the current output state of the circuit. Hence, the output label serves two major purposes: 1) it provides the designer with the value of the present output state at a particular point in the design sequence; and 2) it indicates the next statement to be executed from that particular output state. The output state of the label is followed by a / <number> when it is necessary to distinguish a previous output label having the same output state. If the / <number> is not specified with the output label, the ACDL translator will assume a default value of /1 for the label. An output label may also be used to specify multiple output states in cases where the next statement to be executed is the same for each state.

A standard label is essentially a valid identifier with the restriction that the first character of the label cannot be the letter "Z". Examples of standard and output labels are given in Table VI.

| Label Type | Examples         |  |

|------------|------------------|--|

| Standard   | FIRST:           |  |

| Standard   | \$31:            |  |

| Standard   | BEGIN_HERE:      |  |

| Output     | 200:             |  |

| Output     | Z(00, 01/2, 11): |  |

| Output     | Z110/3:          |  |

|  | TABLE | VI. | EXAMPLES | OF | LABEL |

|--|-------|-----|----------|----|-------|

|--|-------|-----|----------|----|-------|

### 5. Statements

There are nine types of statements in ACDL. As in PL/I [18], all statements must be separated by a semicolon; otherwise, they can be written in free format. Each is described below.

a. Design Statement

A description of the design statement is given below. <design statement>::= DESIGN | DESIGN <accounting information> <accounting information>::= <design number>|<design number>, <designer's name>|<design number>,

<designer's name>, <date>

<design number>::= <number>

<designer's name>::= <identifier> Kdesigner's name> <identifier>

<date>::= <identifier> <number>, <number>

The design statement indicates the beginning of a new circuit design. The accounting information is optional and may indicate the design number, designer's name and date.

b. Declare Statement

The following is a description of the declare statement.

<declare statement>::= DECLARE<declaration type> |<declare statement> <declaration type>

<declaration type>::= <input declaration>|<constraints declaration>

|<output declaration>|<global declaration>

<initial condition>::= (<level>)

<constraints declaration>::= CONSTR: <constraints>

<output declaration>::= OUTPUTS: <variable definition>

output declaration>, <variable definition>

<global declaration>::= GLOBAL: <list>

The input and output declarations indicate the number and names of the input and output variables required in the design. The initial condition for each variable may or may not be given. If no initial value is explicitly shown, then an initial value of zero is assumed by default.

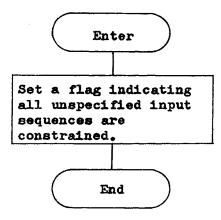

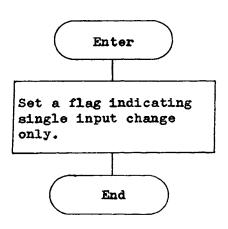

The constraints declaration indicates those input transitions that are not allowed. To assist the designer in problems which permit only single input changes, the constraints specification is given by the mneumonic SIC which stands for "Single Input Change." The mneumonic AUS means that "All Unspecified Sequences" of input transitions, i.e. those sequences which are not explicitly described in the design, are not permitted to occur. This constraint is extremely useful in problems where only a specific number of alternative sequences can occur. Level relation constraints restrict transitions to those input states which agree with the value of the relation. If there are no input transition constraints the word "NONE" must be written. The global declaration is used when there are certain transition conditions which arise frequently throughout the design and are independent of any particular I/O sequence. Instead of repeating the transition statement many times in the design specifications, the statements are listed once in a global declaration. The global list consists of automatic link transition statements which are discussed later.

Some examples of the design and declare statements are given in Table VII.

| Statement Type | Example                                   |

|----------------|-------------------------------------------|

| Design         | DESIGN;                                   |

| Design         | DESIGN 103;                               |

| Design         | DESIGN 103, JOHN DOE, APR 3, 1972;        |

| Declare        | DECLARE INPUTS: A, B                      |

|                | CONSTR: SIC,                              |

|                | A=1 and $B=1$                             |

|                | OUTPUTS: Z;                               |

| Declare        | DECLARE INPUTS: X1(1), X2(0)              |

|                | CONSTR: X1->1 WHILE X2=1, X2->1 WHILE X1= |

|                | OUTPUTS: Z1, Z2                           |

|                | GLOBAL: X2->0=>Z1<-0/;                    |

TABLE VII. EXAMPLES OF THE DESIGN AND DECLARE STATEMENTS

The initial conditions for the input variables are explicitly given in the example of the second declare statement, while they are left to default to zero in the first declare statement. c. Start Statement

The start statement is defined as:

<start statement>::= START

This is always the first statement in the circuit's behavior description. Therefore, it acts as the starting point for the design sequences by invoking the initial I/O conditions and establishing the initial state of the machine.

d. Transition Statement

This statement is used to show input transitions and may relate an input transition to an output change. A description of this statement is shown below.

<transition statement>::= <basic transition statement>

| <automatic link transition statement>

<basic transition statement>::= <transition expression>

<transition expression>

=> <output change>

<output change>::= <identifier><-Boolean expression>

<output change>, <identifier> <-</pre>

<Boolean expression>

<automatic link transition statement>::= <transition expression>

=> <output change>

<autolink>

<auto link>::= /// <number>

Since the inputs to the circuit change at random, the input transitions specified by the transition expression are essentially test conditions for particular changes. When the test conditions are satisfied the specified output change occurs. The slash following the output change is an optional character used when automatic linking is desired. This concept is explained in a subsequent section on the list statement. Examples of basic transition statements are shown in Table VIII.

| Statement                                               | Explanation                                                                                                                                 |  |  |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| A->1;                                                   | Input A is to make a transition to l                                                                                                        |  |  |  |

| A->0=>Z<-1;                                             | Input A making a transition to 0 implies<br>that output Z changes to 1 if not already l                                                     |  |  |  |

| $(C \rightarrow 1) + (B \rightarrow 1)$<br>=>G<-1,R<-0; | Input C making a transition to 1 or input<br>B making a transition to 1 causes output<br>G to be replaced to 1 and R to be replaced<br>to 0 |  |  |  |

TABLE VIII. EXAMPLES OF THE TRANSITION STATEMENT

e. Link Statement

Generally, there will be many sequences of transition statements in a design specification and some subsequences of transition statements will be common to more than one sequence. Whenever a subsequence leads to two or more sequence paths, as in the case of alternate behaviors at a branch point, it is necessary to make the proper connection to each of these paths. These connections can be made with the link statement defined below.

<link statement>::= <link conditional>|<link unconditional> <link conditional>::= <tests> <branch points> <tests>::=(<test condition>|<tests>, <test condition> <test condition>::= <transition expression>|<level relation> |ELSE

<branch points>::= )<single label> |<branch points>, <single label>

<single label>::= <standard label>|z<output code>

<link unconditional>::= LINK <single label>

The tests listed in the conditional link statement are the test conditions of the next transition statement for each new path, respectively. The next statement following the test condition for each path is given by the label corresponding by position to the test condition. Multiple output labels are not allowed in the link statement. This restriction, however, causes no branching limitations. Any statement having a multiple output label can be located by any one of its output states.

Whenever an output change follows a test condition of the LINK, it is shown as the first statement of the new path. In this case the dummy term LINKTEST (abbrev. LK'T) is inserted as the transition expression for this transition statement. This implies that the same test condition causing the link also causes the output change.

The link unconditional is the same as a "go to" statement and is primarily used for branching back to a previously specified statement.

f. Statement Block

Closely associated with the link statement are statement blocks. A description of the statement block is given below.

< statement block::= <beginning> <statement list> <ending>

<beginning>::= BEGIN; | <label> BEGIN;

<ending>::= END <label> END

Actually the BEGIN and END statements act as separators which serve to segregate a block of statements from other statements. This block of statements between a BEGIN and END is called a statement block and can only be entered from a link or list statement. Statement blocks may be nested within other statement blocks. After a statement block has been completed, control is transferred to the next statement in the listing which does not belong to another statement block of the same nested level. Examples of the link statement and statement blocks are given in Table IX.

| Statements                                                                                             | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LINK L3;                                                                                               | Link to the statement having the label L3                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| LINK (B->1,A->0)L1,L2;<br>L1 : BEGIN;<br>LK'T=>Z <-1;<br>END;<br>L2 : BEGIN;<br>C->1;<br>END;<br>B->0; | The lst test condition transfers control to<br>statement block Ll where the lst statement<br>says that the link test B->l causes $Z\langle -1$ .<br>After the lst statement block is completed,<br>control is transferred to the transition<br>statement B->0. If none of the Link state-<br>ment test conditions are true for the cur-<br>rent input transition, the sequence will not<br>advance, but rather will remain at the Link<br>statement until a test condition becomes<br>true for some later transition. |  |  |

| LINK(A=1,ELSE)RESET,<br>CONTINUE;<br>RESET: A->0;<br>CONTINUE: B->1;                                   | If input variable A is currently equal to 1,<br>then branch to RESET else branch to CONTINUE.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

TABLE IX. EXAMPLES OF LINK STATEMENTS

g. Automatic Linking and the List Statement

Earlier it was noted that a slash "/" could follow the output change of a transition statement, and this slash meant automatic linking. This linking is accomplished by branching to the statement identified by an output label having the current output state. The current output state is the state entered after the output change of the transition statement has taken place. Therefore, if automatic linking is designated with the slash, the designer must ensure that a unique and correct output label has been assigned to some statement. To distinguish between output states having the same value, but occur at different points in the sequence, the designer follows the slash with a digit which must agree with the trailing digit of the correct output state label. Again if no digit is specified after the slash, a default value of 1 is assumed.

Automatic linking saves the designer having to explicitly specify a link statement and hence, improves the clarity of the specification listing. It was the automatic linking feature which led to the development of the list statement defined as:

<list statement>::= LIST <list>

<list>::= <automatic link transition statement>l<list>,

<automatic link transition statement>

The list statement is a special purpose link statement in which all test conditions lead directly to an output change. It does not specify an executable sequence of transition statements, but rather, it is a set of statements from which only one is selected and executed. The test conditions of all automatic link transition statements in the list are scanned concurrently, and only one test condition may be true at a time. When a test condition becomes true, its corresponding output change indicates the next statement in the sequence via automatic linking. The transition statements within a LIST statement are separated by commas, while the end of the list is indicated by the LIST

24

statement's semicolon. Some examples of the list statement are given in Table X.

|       | Example                                            | Explanation                                             |

|-------|----------------------------------------------------|---------------------------------------------------------|

| Z00:  | LIST<br>X1->1 => Z1<-1 /,                          | In the list statement either of the two                 |

|       | $X1^{-1} = 21^{-1}$ ,<br>$X2^{-1} = 22^{-1}$ ,     | listed input transitions can occur. If                  |

|       | •                                                  | X1->1 then an automatic link is made to                 |

| Z10:  | •<br>x2->1;                                        | the statement having the output label Z10.              |

|       | •                                                  | Similarly, if $X2->1$ is true, then a branch            |

| Z01:  | ·x1->1;                                            | will be made to ZO1 upon completion of the              |

|       | •                                                  | output change Z2< <b>-1.</b>                            |

|       | •                                                  |                                                         |

| z10:  | LIST<br>$A^{->0} \Rightarrow Z1 < -0, Z2 < -1 /2,$ | If the first test condition $A \rightarrow 0$ occurs, a |

|       | $B \rightarrow 1 \Rightarrow Z2 < -1 /;$           | link will automatically be made to Z01/2.               |

|       | •                                                  | If the second test condition $B->1$ occurs,             |

| Z(01, | ,11): B->0;                                        | a link will be made to the transition state-            |

|       | •                                                  | ment $B$ ->0 since Z11 is contained in the              |

| Z01/2 | 2: B->1 WHILE A=1;                                 | multiple output label Z(00,11).                         |

|       | •<br>•<br>•                                        |                                                         |

| TABLE | Χ. | EXAMPLES | OF | THE | LIST | STATEMENT |  |

|-------|----|----------|----|-----|------|-----------|--|

|       |    |          |    |     |      |           |  |

6. Structure of an ACDL Program

Now that the statements have been defined, it is worth examining the overall structure of a program. <program>::= <program head> < statement list> <ending>.

<program head>::= <design statement>;<declare statement>;

<statement list>::= <statement>|<statement list> <statement> <statement>::= <basic statement>|<statement block>; <basic statement>::= <transition statement>;|<link statement>; |<list statement>:|<label> <basic statement>;

It is seen that the program ending also uses the word END. In this case END is followed by a period rather than a semicolon. The period signifies the end of the design as opposed to the end of a statement block. All links to this ending will indicate the end of certain sequences within the specifications.

The statements which make up the program head must be listed in the order shown. These statements are not part of the input/output behavior of the design, but rather provide basic information about the design. For this reason labels are not assigned to statements in the program head.

7. Comments and Translator Control Toggles Comments are defined as follows: <comment>::= "<almost anything>" <almost anything>::= <any string of valid system 360 characters that does not contain a ">

Comments help explain the program to persons reading it and are normally ignored by the translator. They do not result in the production of any translated text and they may be inserted any place a blank is allowed. There is one case in which comments are not ignored. They may serve the special function of specifying control options which designate how the program is to be treated. For instance, a control option to perform and output a logic trace during the translation and/or execution of a program can be specified. A \$ within a comment specifies that the next character is a control character. The valid control characters in ACDL are given in Table XI. Each control character acts as a toggle which can have the value of true or false. When \$<*character*> is encountered by the translator, the value of the corresponding toggle is complemented. Therefore at the point where "\$W" is first specified, the logic trace will be turned on, and will remain on until another "\$W" is encountered which causes the trace to turn off. A more detailed description and use of the logic trace is given in Appendix B.

| Character | Control Option                                                                                             |

|-----------|------------------------------------------------------------------------------------------------------------|

| D         | Print translation statistics, sequence tables and symbol tables at end of translation (Initially disabled) |

| L         | List the source program (Initially enabled) $^{\star}$                                                     |

| Т         | Begin a machine code trace of the ACDL translator and interpreter (Initially disabled)*                    |

| U         | Terminate the machine code trace of the ACDL translator and interpreter (Initially disabled)*              |

| Ŵ         | Begin high level trace of translation and execution (Initially disabled)                                   |

| I         | Set Margin. The portion of succeeding cards starting from the column containing the   will be ignored.*    |

TABLE XI. COMMENT CONTROL OPTIONS

<sup>\*</sup>These options were already a part of the XPL system (See reference [17]).

#### C. Sequences

Statements in ACDL are executed in the sequential order in which they are listed, except when the physical sequence is interrupted by branching which results from explicit or automatic linking. The rules for interpreting sequences written in ACDL are:

- In a test condition of an ACDL statement, any undesignated input variables are considered as don't-cares in the specified input state transition.

- 2) The sequence will advance to the next statement for any input state transition which agrees with a test condition of the current statement.

- 3) The sequence remains quiescent (i.e. does not move) for any input state transition which does not agree with a test condition of the current statement.

Before the designer can efficiently use ACDL, some idea as to what information is necessary for correctly specifying the operation of the sequential circuit is required.

Definition: A set of minimum length sequences of input states which cause the next output change and starts from the I/O state resulting from the previous output change is called a <u>critical event</u>.

A critical event may be an incompletely specified sequence i.e., a sequence which contains don't-care variables in some states. In this case the critical event will actually represent more than one possible sequence resulting from the random changing of the don't-care variables. However, any intermediate states that are introduced by the don't-care variables will not affect the integrity of the critical event, i.e., these states neither cause an output change nor destroy any past history of the critical event.

The designer must specify in ACDL all critical events of the circuit. This is done by starting from the initial state of the circuit and listing the critical events which cause the first output changes. Continuing from these points in the sequences all subsequent critical events which cause further output changes are listed. The tree process is continued until the critical events for all possible output changes have been listed.

Definition: A <u>proposition</u> of the design is a word statement (or mental conception) which implies one or more critical events.

From the design propositions, the designer should be able to formally specify the critical events in ACDL. Likewise from the ACDL specifications, the propositions should be easily determined. Examples of various types of circuit designs in ACDL are given in Chapter V.

### D. Summary

Table XII summarizes the statements available in ACDL.

| TABLE | XII. | SUMMARY | 0F | ACDL |

|-------|------|---------|----|------|

|       |      |         |    |      |

| Statement  | Gei                            | neral Format Description                                                                          | Use                                                                            |

|------------|--------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Design     | DESIGN                         | optional accounting information<br>of design #, designer's name,<br>and date;                     | Begins ACDL program                                                            |

| Declare    | DECLARE<br>INPUTS:             | input names with or without initial conditions                                                    | Defines all input<br>variables, output                                         |

|            | CONSTR:                        | keywords, level expressions<br>or transition expression<br>constraints                            | variables, constraint<br>transitions and global<br>transitions of the          |

|            | OUTPUT:                        | output names with or without<br>initial conditions                                                | design.                                                                        |

|            | GLOBAL:                        | list of automatic link<br>transition statements;                                                  |                                                                                |

| Start      | START;                         |                                                                                                   | The entry point of the sequence specifications.                                |

| Transition | or<br>input trans<br>without a | ition; (e.g. X->1;)<br>ition=>output change with or<br>automatic linking specified;<br>>1=>Z<-1;) | Expresses the I/O<br>relationships of the<br>critical events of the<br>design. |

| TABLE | XII. | (Continued) |

|-------|------|-------------|

|-------|------|-------------|

| Link               | LINK (test condition list) label list;                              | For branching in ACDL,<br>where the test condition<br>is an input level or<br>transition test, causing<br>a branch to the<br>corresponding label. |

|--------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Statement<br>block | BEGIN ;<br>statement list<br>END ;                                  | For listing independent<br>sequence paths resulting<br>from a link or list<br>statement.                                                          |

| List               | LIST followed by a list of automatic<br>link transition statements; | For branching when all<br>test conditions lead<br>directly to an output<br>change.                                                                |

| Program<br>end     | END.                                                                | Designates the end of the<br>sequence specifications<br>and end of the design.                                                                    |

| Comment            | "any valid character string"                                        | For clarification<br>purposes and specifying<br>control toggles.                                                                                  |

### IV. TRANSLATION AND INTERPRETATION

After the design has been specified in ACDL, a translation process is needed to convert the specifications into appropriate intermediate text. The intermediate text is then interpreted to produce a primitive flow table as the final output.

The translator and interpreter (flow table construction algorithm) is written in XPL, a special purpose translator writing language developed by McKeeman et al. [17]. A brief description of the XPL system follows.

A. The XPL Translator Writing System (TWS)

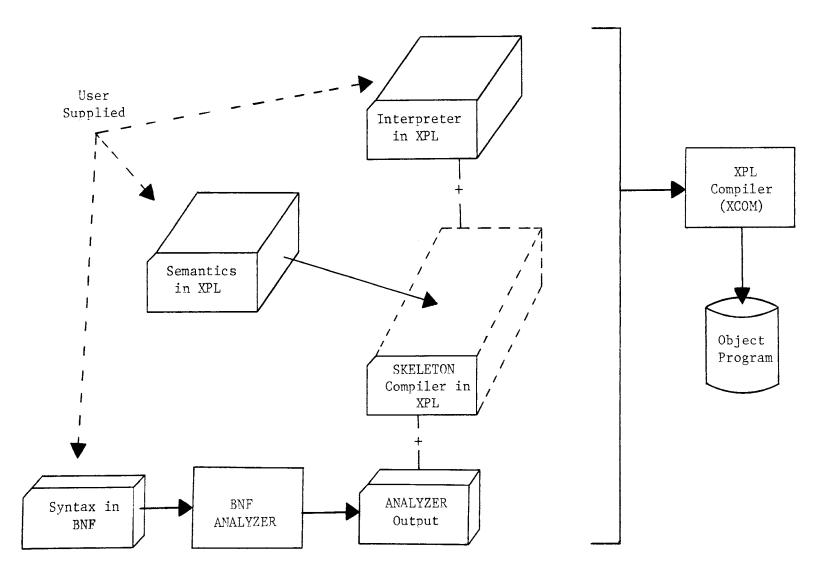

A diagram of the translator writing system provided with XPL is shown in Figure 3. The major components included in the system are:

- 1) a grammar analyzer (ANALYZER)

- 2) a proto-compiler (SKELETON) and

- 3) The XPL compiler (XCOM).

ANALYZER [17] is a program which reads the BNF grammar describing the syntax of the user's language, determines whether it is acceptable to the parsing algorithm and constructs parsing decision tables for that algorithm. SKELETON [17], which is written in XPL, provides the basic framework of the user's compiler such as, the routines for scanning, input and parse-stack maintenance. XCOM [17] is the compiler for the XPL language, and produces a System 360 machine language object program.

Depending on the amount of information supplied to TWS, the system will produce either a syntax checker, a translator or a combined translator/interpreter. If the user supplies only a syntax description (grammar) of his language in BNF, the resulting ANALYZER output deck

Figure 3. XPL Translator Writing System

and the SKELETON deck produce a syntax checker for the language. If the semantic description of his language (written in XPL) is also inserted into the SKELETON deck, the system will produce a translator. If in addition to the syntax and semantic descriptions, an interpreter is written in XPL and is placed behind the SKELETON deck, the system produces a combined translator/interpreter. It is this case which is illustrated in Figure 3.

An important advantage of TWS is the ease in which changes to the user's language can be made. Only the syntactic definition and semantic description corresponding to the language change are updated in the translator. A detailed description of the current syntactic definition (BNF grammar) and semantic routines of ACDL has been provided in Appendix D and Appendices E and F, respectively. Appendix C lists the job setup requirements for making a computer run to update the ACDL translator and the job setup for running a standard ACDL program.

## B. ACDL Translation

From the syntax of a language, the translator knows what type of symbols are expected at every point in a language statement. The semantic routines then determine what action is to be taken, if any, when these symbols are encountered. They also generate internal data-structures which hold the results of the translation. These data-structures are referred to as the internal form or intermediate text. A description of the internal form used in the ACDL translation follows.

1. Internal Form

The internal form of the ACDL translator consists of tables which can be dumped at the end of the translation (see Table XI). The tables contain input/output sequence data as well as symbol information. As a means to increase program execution time, all input states are handled internally and recorded in the tables as decimal weights rather than as binary strings.

The main table used to hold the I/O sequence information is called the Primary Sequence Table. It stores the translated form of the statements making up the critical sequences of the design. The first row of the table is assigned to the START statement, with subsequent rows being assigned to each transition statement and each test condition of a link statement. Input and output secondary tables act as backup for the primary sequence table when statements have more than one input test or output change respectively. This technique of table organization saves storage since the secondary tables do not require all the fields that are needed in the primary table.

A special table called the Global Transition Table holds the information from the globally declared transition statements. The structure of this table is similar to the primary sequence table, and also uses the two secondary tables as backup tables. However, the Global Table functions differently in that all its input tests are queried continuously throughout the design.

The Constraint Transition Table records those input transitions that have been explicitly declared as input constraints. Restricted input transitions resulting from the SIC or AUS declaration are not recorded in this table because violations of these conditions are detected in an algorithmic manner. The constraint table does not use any backup tables. All restricted transitions are stored in sequential order in the table and are checked before examining any other tables. The ACDL translation makes use of two separate symbol tables. One table is a standard symbol table used to record input, output and label names and their corresponding attributes. The other table is a special symbol table used to store output labels and statement pointers for automatic linking. Since only one table has to be searched for a particular operation, the two-table organization provides efficient symbol information retrieval and is especially advantageous in the automatic linking process.

A detailed description of the above tables and their corresponding fields is given in Appendix A. The appendix also includes an example program and corresponding table dump.

Another feature of the internal form is the handling of the Boolean output expressions. These expressions are converted from standard infix form to Reverse Polish form. The Reverse Polish form is stored in and executed from a single-dimensioned array. Special terminators are also stored in the array to indicate the beginning and end of an expression. For easy and rapid manipulation, the operators and operands are represented by their precedent values and symbol table indexes, respectively. For this reason, the Polish array was not included in the dump. However, the array is printed out whenever the logic trace is specified.

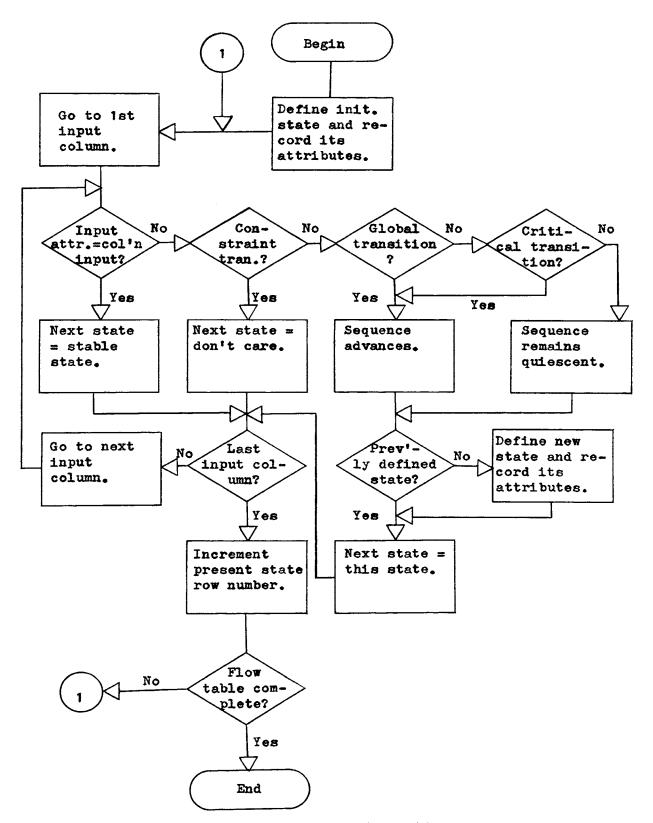

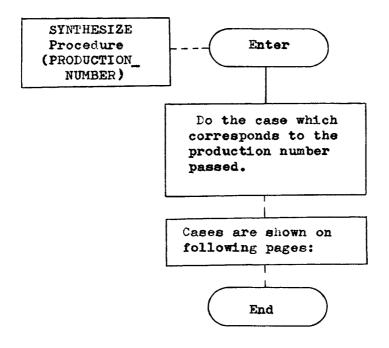

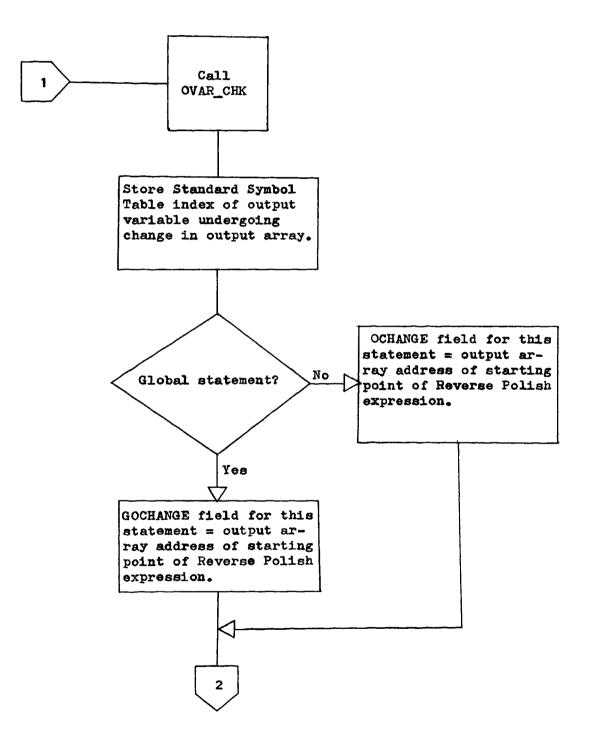

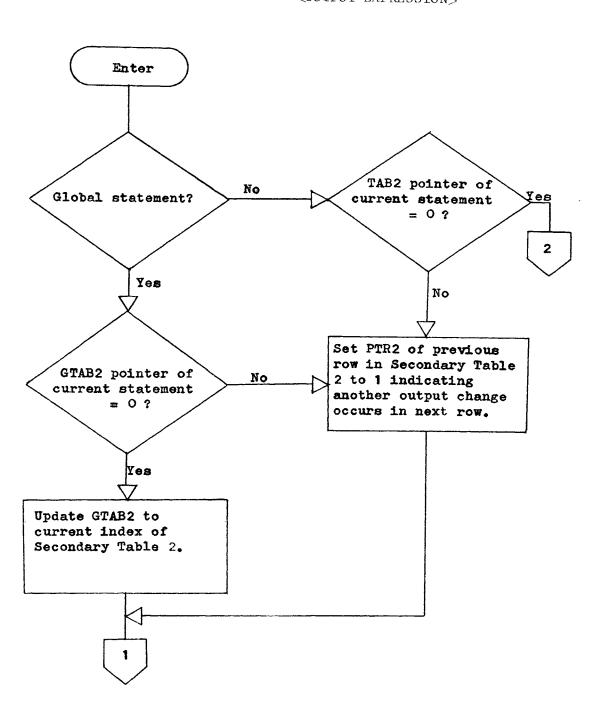

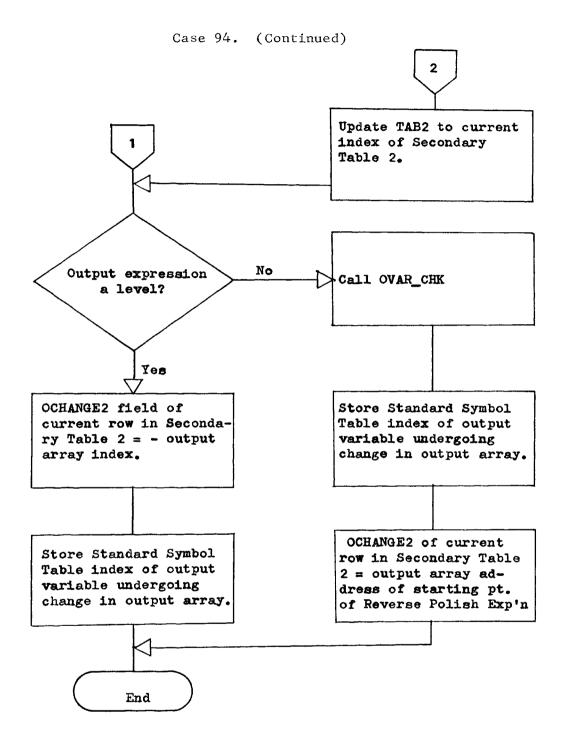

# C. Primitive Flow Table Construction

Once the translation process has been completed, the interpretation process begins. Here the interpreter is an algorithm to construct a primitive flow table from the tables of the internal form. A flow chart describing the basic philosophy of the flow table algorithm is given in Figure 4.

Figure 4. Flow Chart of the Primitive Flow Table Construction Algorithm

In addition to the output state, the flow table algorithm assigns input and sequence attributes to each row of the flow table. Each attribute has its own function in the flow table construction algorithm. The sequence attribute is an index which points to the statement in the Primary Sequence Table that is tested during the construction of the corresponding flow table row. It essentially keeps track of a flow table state's position in the design sequence. The input attribute contains the input state for which the corresponding flow table row is stable. Input transitions for a flow table row are simulated by using the input attribute as the beginning state and the column inputs as the ending states. This permits the computation of next-state entries to be conducted in an orderly manner with stable entries being recognized whenever the input attribute equals a column state.

To help understand the flow table algorithm, the following example problem [14] will be considered:

Design a circuit which has two inputs, OSC and BTN, and one output, Z. The input OSC is the output of a square wave oscillator, and BTN is a button which, when depressed, gates one and only one full width oscillator pulse to the output. If the button is depressed for too short of time, a pulse will not occur at the output. An output pulse can occur only if the button depression overlaps the leading edge of an oscillator pulse. The inputs cannot change simultaneously.

The ACDL program for this design is:

DESIGN 1, JOHN BROWN, SEP 27, 1972;

DECLARE

OSC, BTN INPUTS: CONSTR: SIC OUTPUTS: Z; Seq.# 0 START; 1 L2: BTN->1;2 LINK (OSC->1, 3  $BTN \rightarrow 0$ ) L1, L2; LK'T=>Z<-1; 4 L1: 5  $OSC \rightarrow 0 \Rightarrow Z < -0;$ 6 END.

To simulate the internal form, the sequence numbers assigned to the statements in the above program correspond to the row indices of the Primary Sequence Table in which their translated form is stored. The start statement has the sequence number 0, because the Primary Sequence Table begins at index 0. The sequence numbers of the above program also relate to the sequence number attribute of each flow table row.

The first step in the algorithm is to define the initial state of the circuit. Since the start statement is responsible for setting up the initial conditions, this information is retrieved from row 0 of the Primary Sequence Table and assigned to the attributes of the first flow table row. At this point in the construction, the partial flow table resembles Table XIII (a). The sequence number attribute of flow table row 1 corresponds to the sequence number of the next statement to be executed in the ACDL program. The next step is to compute next-state entries for row 1 of the flow table. The next state for the first input column is stable since the input attribute equals this input column. For the next input column, the first three input tests of the algorithm failed and the critical transition test is performed. For this test, the flow table transition, 00 to 01, is compared to the test condition, BTN->1, which is pointed to by the sequence attribute of 1. The test condition agrees with the flow table transition; therefore, the sequence advances. Since there is no previously defined state with correct attributes (i.e. Seq #=2, I=01, Z=0), the new state 2 is defined as shown in Table XIII (b).

The next input column implies the transition 00 to 10. Again the first three input tests failed, and since the flow table transition does not agree with the specified transition BTN->1, the critical transition test also fails. Therefore the sequence remains quiescent, and the next state retains the same sequence number and output state attributes as the present state. A new state 3 is defined because there is no previously defined state with the required attributes.

The last input column implies the transition 00 to 11, which will be detected by the constraint transition test as an illegal transition. A don't care will be entered in this column and row 1 is complete as shown in Table XIII (c). The algorithm moves to the next incomplete flow table row which is row 2 in this example and repeats the same procedure.

After all flow table rows are complete, the algorithm will terminate and produce the resulting flow table shown in Table XIV. From this table it is observed neither the sequence attribute 4 nor 6 is associated with any of the flow table rows. This is due to a property of

the algorithm which advances the sequence through non-active test conditions such as LK'T, BEGIN, END and ELSE. The reader should now be able to verify the remaining flow table rows.

| ـد<br>        |               | ARTIAL FLOW TABLE |             |

|---------------|---------------|-------------------|-------------|

| Attributes    | Present       | OSC BTN           |             |

| <u>Seq# I</u> | <u>State</u>  | 00 01 10 11       | <u>Z</u>    |

| 1 00          | 1             |                   | 0           |

| (a)           | Definition of | the Initial State |             |

| Attributes    | Present       | OSC BTN           |             |

| <u>Seq# I</u> | <u>State</u>  | 00 01 10 11       | _ <u>Z_</u> |

| 1 00          | 1             | 1 2               | 0           |

| 2 01          | 2             |                   | 0           |

|               | (b) Definiti  | on of State 2     |             |

| Attributes    | Present       | OSC BTN           |             |

| <u>Seq#</u> I | State         | 00 01 10 11       | Z           |

| 1 00          | 1             |                   | 0           |

| 2 01          | 2             |                   | 0           |

| 1 10          | 3             |                   | 0           |

|               | (c) Complet   | tion of Row 1     |             |

TABLE XIII. PARTIAL FLOW TABLE

An important feature of the algorithm is its ability to distinguish different states having the same input/output attributes. As seen from states 2 and 6 in Table XIV, it is the sequence attribute which provides this distinction.

To simplify the explanation of the flow table construction algorithm the previous example was performed without converting to internal form. Since the internal form is only a translated description of the ACDL statement, it should be clear that the same philosophy will apply. A more detailed description of the flow table procedures as they utilize the internal form is given in the flow charts of Appendix F.

| Attril       | outes            | Present | OSC | BTN |                |    |   |

|--------------|------------------|---------|-----|-----|----------------|----|---|

| <u>Seq</u> # | <u>    I    </u> | State   | 00  | 01  | 10             | 11 | Z |

| 1            | 00               | 1       |     | 2   | 3              | -  | 0 |

| 2            | 01               | 2       | 1   | 2   | -              | 4  | 0 |

| 1            | 10               | 3       | 1   | -   | 3              | 5  | 0 |

| 5            | 11               | 4       | -   | 6   | 7              | 4  | 1 |