# MULTIFUNCTIONAL OPTICAL DEVICES BASED ON 5x5 MULTIMODE INTERFERENCE ON AN SOI PLATFORM FOR ALL-OPTICAL COMPUTING APPLICATIONS

### Trung-Thanh Le\*

Hanoi University of Natural Resources and Environment, Hanoi, Vietnam

\*Email: <u>thanh.le@hunre.edu.vn</u>

Received: 21 May 2011; Accepted for publication: 24 June 2012

#### **ABSTRACT**

The design of multifunctional devices based on Multimode Interference (MMI) structures for all-optical computing applications is presented in this paper. Based on the self-imaging effect in a multimode silicon planar waveguide, a variety of all-optical devices such as all-optical beam splitters, combiners, optical XOR and OR logic gates can be realized. The analytical expression describing the characteristics of the proposed devices is analysed and derived. Designs of the proposed devices on a silicon on insulator (SOI) platform are then verified and optimised using numerical simulation methods.

*Keywords:* Optical computing, multimode interference (MMI) couplers, optical signal processing, CMOS technology, SOI platform

### 1. INTRODUCTION

Although photonics digital signal processing is still in an embryonic stage, a number of research on all-optical flip-flops, switches and logical gates, have been published [1, 2]. Future photonic networks will require optical digital functions such as packet buffering, bit-length conversion, header processing, retiming, reshaping, time-division multiplexing and demultiplexing. All this operations can be realized by using elementary building blocks such as optical flip-flop, optical logical gates, and optical switches. These basic subsystems can then be combined to perform complex operations. However, the size, speed, and power consumption of the proposed devices in much cases is such that they allow only for very small integration levels, and they are by far not competitive with modern electronics. An advantage of photonics over electronics would be that it does not incur the charge displacement which form the speed bottleneck in electronic switching. Photons can, therefore, operate at a higher speed than electronics and in principle, its switching speed is limited by the time that light needs for effective interaction in the switching structure. In order to really become an option for digital processing, photonic technology has to improve far its features in terms of reduced component size and power consumption.

There is a great need for implementing all-optical logic gates having small size, low power consumption and high-speed [3, 4]. There are many existing approaches for realizing optical logic gates. Many materials and devices have been suggested for use in optical logic. So far, optical logic schemes have been mainly based on nonlinear materials [5, 6]. The disadvantage of these approaches is that high optical powers are needed in order to obtain a nonlinear interaction. In addition, since the nonlinear coefficient is often small, long interaction lengths are generally required

In this paper, novel designs for realizing al-optical devices such as optical splitters, combiners, optical XOR and OR logic gates based on 5x5 multimode interference (MMI) couplers on the Si nano-wire waveguides is presented for the first time. In this work, silicon on insulator (SOI) technology is used for the design of MMI based devices because SOI technology is compatible with existing complementary metal—oxide—semiconductor (CMOS) technologies for making compact, low cost, highly integrated and multifunction devices [7, 8].

## 2. ALL-OPTICAL DEVICES BASED ON 5x5 RESTRICTED MULTIMODE INTERFERENCE

The conventional MMI coupler has a structure consisting of a homogeneous planar multimode waveguide region connected to a number of single mode access waveguides [9]. There are three main interference mechanisms. The first is the general interference (GI) mechanism which is independent of the modal excitation. The second is the restricted interference (RI) mechanism, in which excitation inputs are placed at some special positions so that certain modes are not excited. The last mechanism is the symmetric interference (SI), in which the excitation input is located at the centre of the multimode section.

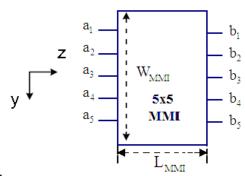

The structure of a 5×5 RI-MMI coupler is shown in Fig. 1. The width and the length of the MMI coupler are  $W_{MMI}$  and  $L_{MMI}$ , respectively. Here the length of the MMI coupler is chosen to be  $L_{MMI} = \frac{L_{\pi}}{4}$ , where  $L_{\pi}$  is the beat length of the MMI coupler [10],  $a_i$  (i=1,2,3,4,5) and  $b_j$  (j=1,2,3,4,5) are the complex amplitudes of the signals at input and output ports, respectively.

Figure 1. A 5×5 MMI coupler based on the restricted interference used for the design of 2×2 MMI couplers having arbitrary power splitting ratios

By using the transfer matrix method [11], the MMI coupler can be described by a transfer matrix, which shows the relationship between the output complex amplitudes and input amplitudes at the input and output ports as follow

$$\begin{bmatrix} b_1 \\ b_2 \\ b_3 \\ b_4 \\ b_5 \end{bmatrix} = \frac{1}{\sqrt{12}} \begin{bmatrix} \eta^7 & \sqrt{3}\eta^4 & 2\eta^{-1} & \sqrt{3}\eta^{-8} & \eta^7 \\ \sqrt{3}\eta^4 & \sqrt{3}\eta & 0 & \sqrt{3}\eta & \sqrt{3}\eta^{-8} \\ 2\eta^{-1} & 0 & 2\eta^3 & 0 & 2\eta^{-1} \\ \sqrt{3}\eta^{-8} & \sqrt{3}\eta & 0 & \sqrt{3}\eta & \sqrt{3}\eta^4 \\ \eta^7 & \sqrt{3}\eta^{-8} & 2\eta^{-1} & \sqrt{3}\eta^4 & \eta^7 \end{bmatrix} \begin{bmatrix} a_1 \\ a_2 \\ a_3 \\ a_4 \\ a_5 \end{bmatrix}$$

(1)

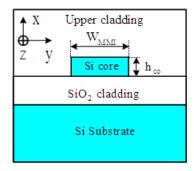

The waveguide structure used in the designs is shown in Fig. 2. Here,  ${\rm SiO_2}$  ( ${\rm n_{SiO_2}}=1.46$ ) is used as the upper cladding material. An upper cladding region is used to avoid the influence of moisture and environmental temperature. The parameters used in the designs are as follows: the waveguide has a standard silicon thickness of  ${\rm h_{co}}=220$  nm and access waveguide widths are  ${\rm W_a}=0.48~\mu{\rm m}$  for single mode operation. It is assumed that the designs are for the TE polarization at a central optical wavelength  $\lambda=1550$  nm.

Figure 2. Silicon waveguide cross-section used in the designs of the proposed device

The width of the MMI coupler is  $W_{MMI} = 12 \mu m$  and the optimised length calculated by the 3D-BPM is L  $_{MMI} = 96.7 \ \mu m$ . Using the same notation as shown in Fig. 1, the device can operate as a multifunction device as follows.

*Optical combiner and splitter*: When incident light is presented at input port 1, the signals at the five output ports are:

$$b_1 = \frac{1}{\sqrt{12}} \eta^7 a_1, \ b_2 = \frac{1}{2} \eta^4 a_1, \ b_3 = \frac{1}{\sqrt{3}} \eta^{-1} a_1, \ b_4 = \frac{1}{2} \eta^{-8} a_1, \ b_5 = \frac{1}{\sqrt{12}} \eta^7 a_1$$

(2)

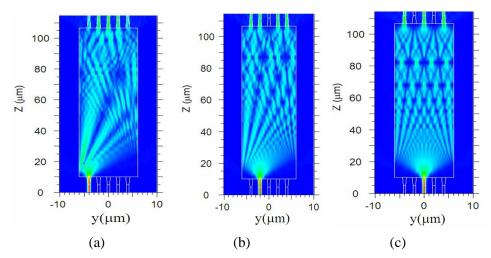

where  $\eta = \exp(j\frac{\pi}{12})$ . This means that a non-uniform power splitter can be realized (Fig. 3(a)). If

an input signal is applied to input port 2 (or input port 4), then 1x4 equal power splitters are formed (Fig. 3 (b)). On the other hand, when an input beam enters input port 3, a  $1\times3$  uniform power splitter is built (Fig. 3(c)). The 3D-BPM simulations for these cases are presented in Fig. 5.16. The excess loss for all these cases is 0.36dB.

Figure 3. 3D-BPM simulations for realizing optical splitters using a 5×5 RI-MMI structure (a) 1×5 optical splitter with a non-equal power splitting ratio, (b) 1×4 MMI splitter and (c) 1×3 MMI splitter. Input and output ports (from left to right) are 1, 2, 3, 4 and 5

Two-port devices: An all-optical XOR gate can be used for comparison of data patterns for address recognition and optical generation of pseudorandom patterns. It is also an important element of an half adder. So far, the XOR gate has been realized using semiconductor microresonators and SOAs [12]. Optical logic gates such as OR, XOR and NOT can also be formed by using the 5×5 RI-MMI structure. When two input ports 2 and 4 having the same phase are used for input signals, the complex amplitudes of output signals at the five output ports are

$$b_1 = \frac{1}{2\eta^8} (a_4 - a_2); \ b_2 = b_4 = \frac{1}{2} \eta (a_2 + a_4); \ b_3 = 0; \ b_5 = -\frac{1}{2\eta^8} (a_4 - a_2)$$

(3)

This means that the analog optical sum and difference of these two light beams can be obtained at output ports 2, 4 and 1, 5 respectively. The truth table for this two-port device is shown in Table 1, where "0" is for logic "0" (no power presented in the waveguides) and "1" for logic "1" (there is power presented in waveguides). Table 1 shows that two OR gates and two XOR logic gates are formed simultaneously.

| Logic level at input port 2 | Input port 4 | Output port 1 | Output port 2 | Output port 4 | Output port 5 |

|-----------------------------|--------------|---------------|---------------|---------------|---------------|

| 0                           | 0            | 0             | 0             | 0             | 0             |

| 0                           | 1            | 1             | 1             | 1             | 1             |

| 1                           | 0            | 1             | 1             | 1             | 1             |

| 1                           | 1            | 0             | 1             | 1             | 0             |

| Gate                        |              | XOR           | OR            | OR            | XOR           |

Table 1. Truth table of a two-port device based on a 5x5 MMI structure

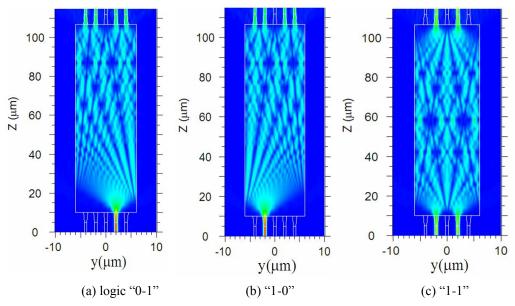

Figure 4 shows the 3D-BPM simulation results for three cases (a) the signal is applied input port 4 (input "0-1"), (b) the signal is applied to input port 2 (input "1-0") and (c) two signals are applied to input port 2 and 4 (input "1-1"). It is clear from these simulations that two OR gates and two XOR gates can be realized at output ports 2,4 and 1, 5, respectively. The 3D-BPM simulations shows that the minimal normalized output power in this case is 0.23.

Figure 4. 3D-BPM simulations for two beams presented at input ports 2 and 4 (a) input logic "0-1", (b) logic "1-0" and (c) logic "1-1"

Similarly, when a phase shifter is employed at input port 4 to change the phase of the signal at that port by  $\pi$ , then the following truth table (Table 2) is formed. If input port 4 is used as a reference signal, input port 2 is used for the data signal and the output is taken at output port 2, then a NOT logic gate can be created as shown in the shaded sections of the table. Table 5.9 also shows that two OR gates and two XOR gates can be formed at output ports 1, 5 and 2, 4 respectively when two input ports 2 and 4 are used.

| Logic level at input port 2 | Logic level at input port 4 | Output port 1 | Output port 2 | Output port 4 | Output port 5 |

|-----------------------------|-----------------------------|---------------|---------------|---------------|---------------|

| 0                           | 0                           | 0             | 0             | 0             | 0             |

| 0                           | 1                           | 1             | 1             | 1             | 1             |

| 1                           | 0                           | 1             | 1             | 1             | 1             |

| 1                           | 1                           | 1             | 0             | 0             | 1             |

| Gate                        |                             | OR            | XOR           | X<br>OR       | OR            |

Table 2. Truth table of 5×5 MMI-based logic gates

It is noted that if a phase controller is used in input port 4 to switch the phase of the signal at this port between 0 and  $\pi$ , then the logic operation of output port 1 will change from the XOR operation to the OR operation and vice-versa.

### 3. DISCUSSIONS

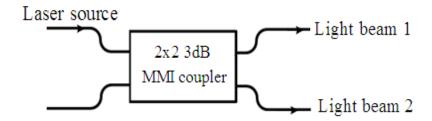

In order to construct optical logic gates based on the interference theory, the light beams must have the same polarization and wavelength. This means that they must be synchronized. To meet this requirement, light beams originating from the same light source can be used as proposed in Fig. 5, where the same single laser source is used in order to provide the reference beams as well as the modulated information signals to all the logic devices on the same chip. Another approach is to separate the polarization components of an input signal as proposed by Watts et al. [13].

Figure 5. Schematic of a circuit for constructing input light beams having the same polarization and wavelength from a laser source

In practice, optical logic gates would have to be coupled with an electronic detector and thresholder to determine whether bit "0" or bit "1" is received. This process thus limits the speed of optical logic devices. Recently, the design of optical limiters and optical thresholders has been carried out theoretically by use of MMI couplers based on slot waveguide structures, in which the slot region uses a nonlinear material [14]. These approaches promise the implementation of optical logic gates in the optical domain without optical-electrical-optical conversion.

### 4. CONCLUSION

In this paper, we have shown that the realization of multifunctional all-optical devices based on 5x5 RI-MMI structures is possible. A variety of all-optical devices for optical computing applications such as optical beam splitters, combiners, all-optical logic OR and XOR gates have been realized. The designs for these devices have been implemented on the silicon on insulator platform and the 3D-BPM was used to optimise the device structures.

### REFERENCES

1. Pramono Y. H., et al. - Optical logic OR, AND, NOT and NOR gates in waveguides consisting of nonlinear material, IEICE Transactions on Electronics, 2000. E83-C: p. 1755.

- 2. Ibrahim T. A., R. Grover, and L. C. K. et. al. All-optical AND/NAND logic gates using semiconductor microresonators, IEEE Photonics Technology Letters **15** (10) (2003) 1422-1424.

- 3. McAulay A. D. Optical Computer Architectures: The Application of Optical Concepts to Next Generation Computers, Wiley-Interscience, 1991.

- 4. Hardy J. and J. Shamir Optics inspired logic architecture, Optics Express 15 (1) (2007) 150-165.

- 5. Cotter D., R. J. Manning, and K. J. B. et. al. Non-linear Optics for High-Speed Digital Information Processing, Science **286** (5444) (1999) 1523-1528.

- 6. Wu Y., T. Shih, and M. Chen New all-optical logic gates based on the local nonlinear Mach-Zehnder interferometer, Optics Express **16** (1) (2008) 248-257.

- 7. Janz S., P. Cheben, and D. D. et. al. Microphotonic elements for integration on the silicon-on-insulator waveguide platform, IEEE Journal of Selected Topics in Quantum Electrononics **12** (6) (2006) 1402-1415.

- 8. Soref R. The past, present, and future of silicon photonics, IEEE Journal of Selected Topics in Quantum Electrononics **12** (2006) 1678-1687.

- 9. Cahill L. W. The Modelling of MMI Devices. in Proc. International Conference on Transparent and Optical Networks 2006 (ICTON 2006), Nottingham, UK, June 2006.

- 10. Le T. T. and L. W. Cahill Accurate Modeling and Analysis of Multimode Interference Structures by Fourier Technique. in Proc. the Tenth international Symposium on Contemporary Photonics Technology (CPT2007), Tokyo, Japan, 10-12 Jan., 2007.

- 11. Le T. T. and L. Cahill Microresonators based on 3x3 restricted interference MMI couplers on an SOI platform. in IEEE LEOS Annual Meeting Conference Proceedings (LEOS 2009), 2009. Belek-Antalya, Turkey, 4-8 Oct.

- 12. Van V., et al. Optical signal processing using nonlinear semiconductor microringresonators, IEEE Journal of Selected Topics in Quantum Electronics 8 (3) (2002) 705-713.

- 13. Watts M. R., H. A. Haus, and E. P. Ippen An integrated mode-evolution-based polarization splitter, Optics Letters **30** (9) (2005) 967-969.

- 14. Barrios C. A. High performance all-optical silicon micro-switch, Electronics Letters **40** (4) (2004) 862-863.

### TÓM TẮT

THIẾT BỊ TOÀN QUANG ĐA CHÚC NĂNG DỰA VÀO CẦU TRÚC GIAO THOA ĐA MODE 5×5 TRÊN VẬT LIỆU SOI DÙNG CHO ỨNG DỤNG XỬ LÍ TOÀN QUANG

Lê Trung Thành

Trường Đại học Tài nguyên và Môi trường Hà Nội

Email: thanh.le@hunre.edu.vn

Trong bài báo này, chúng tôi đề xuất phương pháp thiết kế thiết bị toàn quang đa chức năng dựa vào thiết bị giao thoa đa mode 5 cổng đầu vào và 5 cổng đầu ra trên vật liệu Si cho các ứng dụng xử lí tín hiệu toàn quang. Một số thiết bị chức năng như bộ chia quang, bộ ghép quang, cổng logic XOR và OR toàn quang được thiết kế. Toàn bộ cấu trúc của thiết bị được thiết kế tối ưu sử dụng phương pháp ma trận truyền dẫn và phương pháp mô phỏng số BPM trên máy tính.

*Từ khóa:* Tính toán quang, thiết bị giao thoa đa mode, xử lí tín hiệu quang, công nghệ CMOS, vât liêu SOI.