# Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

1960

# Design of an intermediate frequency amplifier and variable frequency oscillator

Robert Charles McIntyre

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons

Department:

#### **Recommended Citation**

McIntyre, Robert Charles, "Design of an intermediate frequency amplifier and variable frequency oscillator" (1960). Masters Theses. 2668.

https://scholarsmine.mst.edu/masters\_theses/2668

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# DESIGN OF AN INTERMEDIATE FREQUENCY. AMPLIFIER AND VARIABLE FREQUENCY OSCILLATOR

BY

ROBERT CHARLES MCINTYRE

Α

THESIS

submitted to the faculty of the SCHOOL OF MINES AND METALLURGY OF THE UNIVERSITY OF MISSOURI in partial fulfillment of the work required for the

Degree of

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

Rolla, Missouri

1960

Approved by

### ACKNOWLEDGEMENT

The author wishes to acknowledge the guidance and assistance given him by Doctor Roger E. Nolte, and Professor Robert H. Nau, of the Electrical Engineering Department.

# TABLE OF CONTENTS

| CHAPTE | R.         |                                                            | P   | AGE             |

|--------|------------|------------------------------------------------------------|-----|-----------------|

| I.     | THE        | PROBLEM                                                    | •   | 1               |

|        | <b>A</b> • | INTRODUCTION                                               | •   | 1               |

|        | В.         | THE PROBLEM                                                | • . | 1               |

|        | C.         | THE SCOPE OF THE INVESTIGATION                             | •   | 3               |

|        | D.         | REVIEW OF LITERATURE                                       | •   | 3               |

|        | E.         | ORGANIZATION OF THE REMAINDER OF THE THESIS.               | •   | 4.              |

| II.    | NEUT       | TRALIZATION OF THE TRANSISTOR AMPLIFIER                    | •   | 5               |

|        | Α.         | INTRODUCTION                                               | •   | 5               |

|        | В•         | THEORY OF NEUTRALIZATION                                   | •   | 5               |

|        | C.         | EXPERIMENTAL DETERMINATION OF THE NEUTRALIZING CAPACITANCE | •   | 11              |

| III.   | INPU       | UT AND OUTPUT IMPEDANCE DETERMINATION                      | •   | 15              |

|        | A:         | INTRODUCTION                                               | •   | 15              |

|        | ₿•         | THEORETICAL ANALYSIS OF INPUT AND OUTPUT IMPEDANCES        | •   | 16              |

|        | C.         | EXPERIMENTAL DETERMINATION OF INPUT AND OUTPUT IMPEDANCE   | •   | 18              |

| IV.    | BIAS       | S NETWORK DESIGN                                           | •   | 24              |

| •      | A.         | INTRODUCTION                                               | •.  | 24              |

|        | В.         | DESIGN CONSIDERATIONS                                      | •   | 26 <sup>.</sup> |

| :      | C.         | DESIGN OF THE BIAS NETWORK                                 | •   | 29              |

|        | D.         | EXPERIMENTAL RESULTS                                       | •   | 32              |

| v.     | DES:       | IGN OF COUPLING NETWORKS                                   | •   | 36              |

|        | Α.         | INTRODUCTION                                               |     | 36              |

| CHAPTE | 3.      |                                               | 3     | PAGE |

|--------|---------|-----------------------------------------------|-------|------|

|        | В•      | DESIGN OF SINGLE TUNED STAGES                 | • • • | 41   |

| VI.    | AMPI    | LIFIER GAIN                                   | • •   | 47   |

|        | Α.      | INTRODUCTION                                  | • • • | 47   |

|        | В.      | CONSTRUCTION                                  | • • • | 48   |

|        | C.      | EVALUATION OF THE GAIN                        | , ø • | 51   |

| vII.   | THE     | VARIABLE FREQUENCY OSCILLATOR                 | • • • | 55   |

|        | A.      | INTRODUCTION                                  | • •   | 55   |

| •      | В•      | DESIGN OF 10 MC VARIABLE FREQUENCY OSCILLATOR | • • • | 55   |

| VIII.  | SUGO    | ESTIONS FOR ADDITIONAL INVESTIGATION          | • • • | 63   |

| BIBLIO | GRAPI   | -Y                                            | • • • | 65   |

| APPEND | IX I    |                                               | • • • | 66   |

| APPEND | IX I    | I                                             | • • • | 70   |

| ATIV   | • • • • |                                               |       | 72   |

# LIST OF TABLES

| TABLE |                                                                         | PAGE |

|-------|-------------------------------------------------------------------------|------|

| I.    | NEUTRALIZING CAPACITANCE                                                | . 13 |

| II.   | INPUT AND OUTPUT IMPEDANCE OF THE 2N1271 WITH FREQUENCY AS THE VARIABLE | . 21 |

| III.  | COLLECTOR CURRENT VERSUS TEMPERATURE                                    | • 35 |

| IV.   | COEFFICIENT OF COUPLING                                                 | . 44 |

| V.    | OUTPUT VOLTAGE VERSUS FREQUENCY                                         | • 45 |

| VI.   | POWER GAIN PER STAGE                                                    | • 51 |

# LIST OF FIGURES

| FIGU | RES                                          | PAGE |

|------|----------------------------------------------|------|

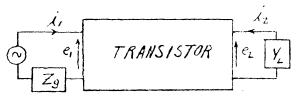

| 1.   | TRANSISTOR TERMINAL VOLTAGES AND CURRENTS    | 7    |

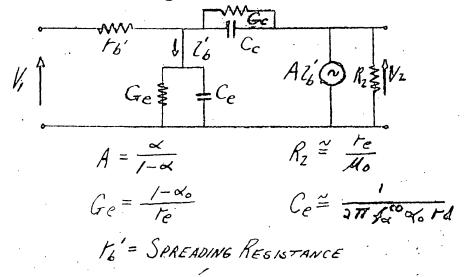

| 2.   | HIGH FREQUENCY EQUIVALENT CIRCUIT            | 10   |

| 3•   | A BRIDGE NEUTRALIZED CIRCUIT                 | 10   |

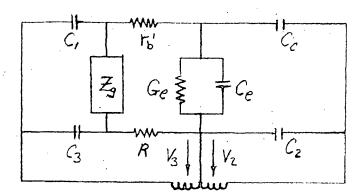

| 4.   | NEUTRALIZATION OF THE TRANSISTOR             | 12   |

| 5.   | THE BASE TO EMITTER VOLTAGES                 | 12   |

| 6.   | DETERMINATION OF OUTPUT IMPEDANCE            | 23   |

| 7.   | TRANSISTOR CURRENTS                          | 25   |

| 8.   | TYPICAL GROUNDED EMITTER STAGE               | 27   |

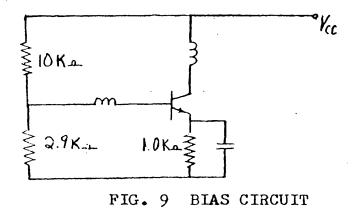

| 9•   | BIAS CIRCUIT                                 | 32   |

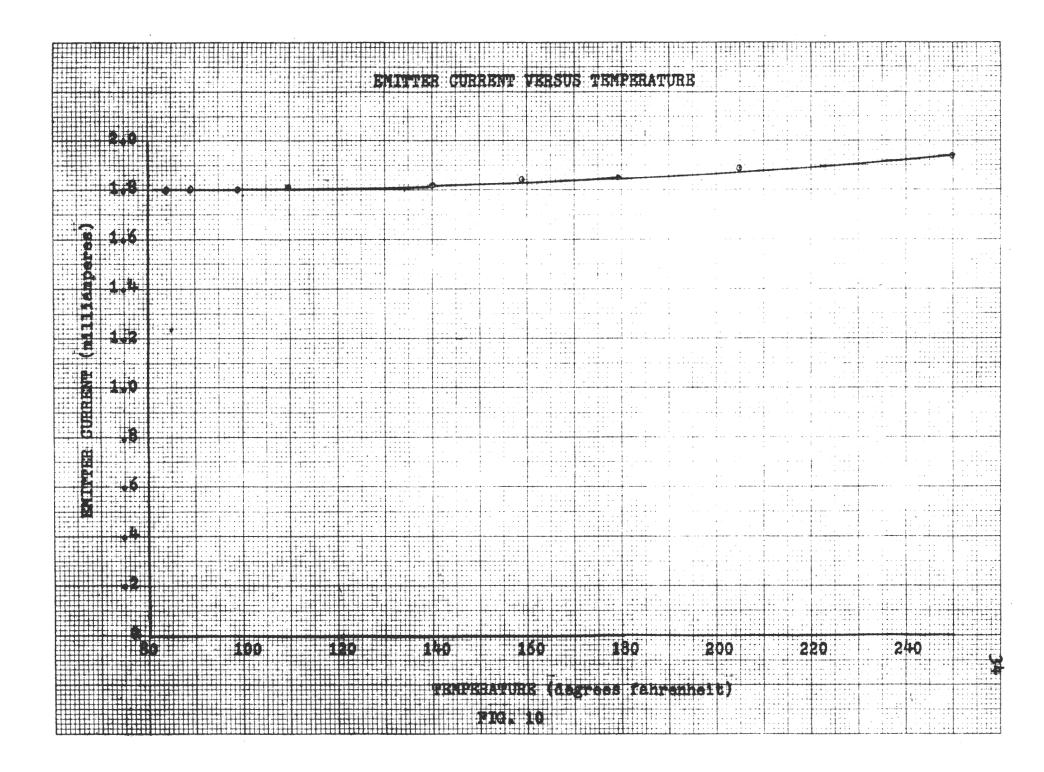

| 10.  | TEMPERATURE VERSUS COLLECTOR CURRENT         | 34   |

| 11.  | COUPLING NETWORK                             | 40   |

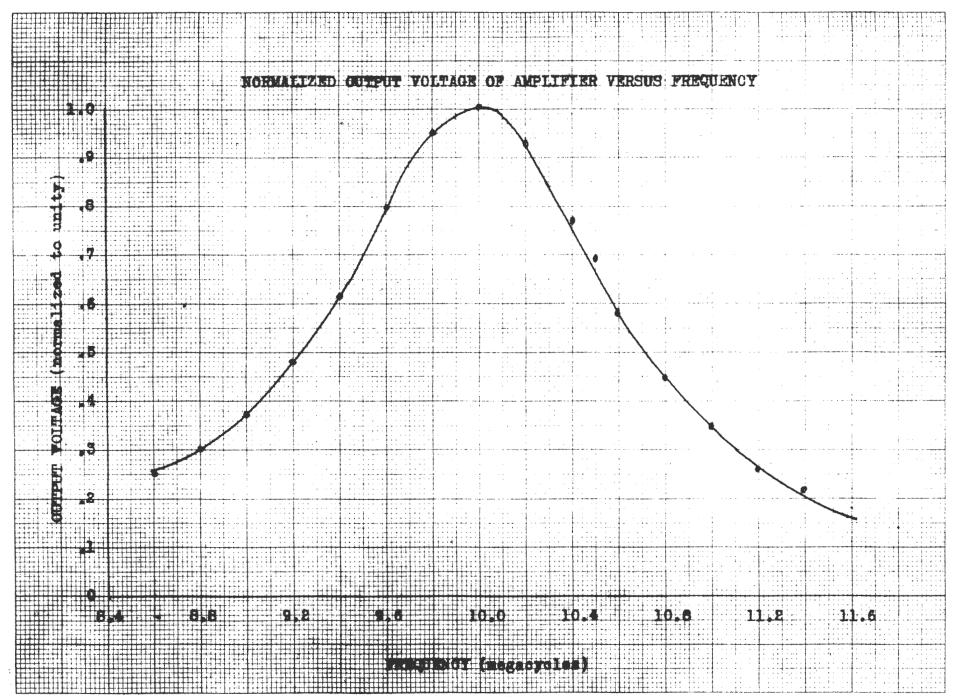

| 12.  | OUTPUT VOLTAGE OF AMPLIFIER VERSUS FREQUENCY | 46   |

| 13.  | 10 MC AMPLIFIER STRIP                        | 49   |

| 14.  | ASSEMBLED UNITS                              | 50   |

| 15.  | GENERAL FEEDBACK CIRCUIT                     | 55   |

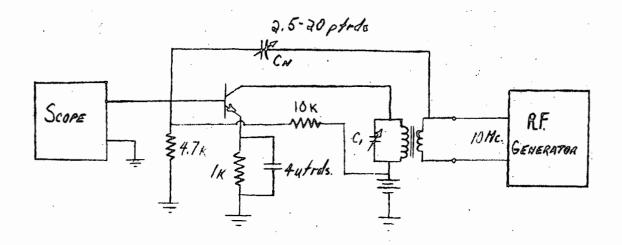

| 16.  | HIGH FREQUENCY OSCILLATOR                    | 56   |

| 17.  | GENERAL FEEDBACK DIAGRAM                     | 56   |

| 18.  | FEEDBACK NETWORK                             | 57   |

| 19.  | APPROXIMATE FEEDBACK NETWORK                 | 58   |

| 20.  | NEUTRALIZING NETWORK                         | 66   |

| 21.  | TRANSISTOR EQUIVALENT CIRCUIT                | 67   |

| 22.  | TRANSISTOR EQUIVALENT CIRCUIT                | 70   |

### LIST OF SYMBOLS

```

---- Amplification

Α

C

---- Capacitance

---- Collector

С

---- Decibel

db

---- AC input voltage

e_i

---- AC output voltage

e<sub>o</sub>

f

---- Frequency

---- Frequency at which | is reduced by 3 db

G

---- Power Gain

---- Input conductance

gi

go

---- Output conductance

h<sub>ij</sub>

---- Hybrid parameters

I

---- DC current

IR

---- DC base current

Ic

---- DC collector current

coo

---- Collector current with collector junction reversed biased and base open circuited.

IcBo

---- Collector junction is reversed biased and emitter

is do open circuited.

Ico

---- Same as above

---- DC emitter current

i

---- AC current

---- AC base current

ic

---- AC collector current

ic

---- AC emitter current

```

```

i ---- AC output current

i, ---- Network currents

---- T-T

j

K

---- A fraction

---- Inductance

\mathbf{L}

---- Mutual inductance

M

---- N type semiconductor material

N

---- Power

Ρ

Q

---- Ratio of reactance to resistance

{

m R}

---- Resistance

R<sub>B</sub> ---- External base resistance

R<sub>E</sub> ---- External emitter resistance

Rg ---- Generator resistance

---- Equivalent base resistance

---- Base spreading resistance

---- Equivalent collector resistance

---- Emitter diffusion resistance

--- Stability factor

---- Collector bias voltage

---- Capacitive reactance

X<sub>C</sub>

X<sub>L</sub> ---- Inductive reactance

Υ.

---- Admittance

---- Short circuit parameters

Уi

---- Impedance

z ---- Open circuit impedance parameters

```

### GREEK LETTER SYMBOLS

--- Short circuit current amplification factor

& ---- Current amplification of feedback network

Af ---- Bandwidth

η ---- Efficiency

$\pi$  ---- Number of radians equivalent to 180 $^{\circ}$

W ---- Angular frequency

#### CHAPTER I

#### THE PROBLEM

### A. INTRODUCTION

Since the advent of the transistor in 1948 many technological barriers have been overcome in the field of semiconductors. Unfortunately, however, there is a considerable period of time between the discovery of a scientific phenomena and its widespread use and understanding by practicing engineers. The motivating factor which prompted this investigation was primarily the lack of knowledge which the author possessed concering transistors. The selection of the amplifier and oscillator design confined the study primarily to the transistor. Considerable time, however, had to be spent in the study of basic transistor theory before any phase of the design could be effected.

### B. THE PROBLEM

Statement of problem. This study was undertaken to investigate the theoretical and practical application of the transistor in a band pass amplifier and a variable frequency oscillator. The primary objective was to develope a unified

design approach for both circuits. The specifications which the intermediate frequency amplifier was expected to meet were; (1) a power gain of 50 db; (2) a one megacycle flat response using stagger tuning. The oscillator was to be variably tuned and operate at a frequency of ten megacycles.

Importance of the study. Band pass amplifiers are used in many electronic applications. In any communication network where radio frequencies are used as the carrier of information it is necessary to have at the receiving portion of the system ample means for the amplification of the incoming signal. The intermediate frequency amplifiers in radio receivers, for example, provide up to 90% of the required gain, therefore, these amplifiers are a major part of most receiving systems. Oscillators find application in many types of systems including radar, radio, and television as prominent examples.

It might be well to point out, at this time, that many of the concepts used in design of low frequency amplifiers are applicable to high frequency circuit design with some reservation. In general, the design of high frequency circuits are more complex due to the nature of the transistor and circuit components.

### C. THE SCOPE OF THE INVESTIGATION

The investigation was divided into two parts, a theoretical analysis of the circuits and an experimental verification of the design.

Theoretical investigation. The design of the amplifier circuit involved an investigation of the neutralization of transistors, coupling networks, bias stability, input impedance measurements, high frequency equivalent circuits, and basic transistor theory. Much of the information obtained in the study of the amplifier proved useful in the design of the oscillator circuit.

Experimental verification. The intermediate amplifier and oscillator were constructed. Experiments were then conducted to enable a comparison with the theoretically expected results and those actually obtained.

## D. REVIEW OF LITERATURE

In the interest of preserving the coherence of the investigation a review of literature will not be given at this time. As the need arises, background information will be provided during the development of the different phases

of the design.

### E. ORGANIZATION OF THE REMAINDER OF THE THESIS

In Chapter II the equivalent circuit to be used in the design of the amplifier is presented. Included also is a study of the theory of neutralization, the design of the neutralizing circuit, and the experimental results obtained.

Chapter III is devoted to the theoretical determination and experimental verification of the input impedance of the transistor in the grounded emitter configuration. The bias network and stability of the transistor is treated in Chapter IV. Chapter V is concerned with the determination of the required bandwidth and coupling networks. Chapter VI is devoted to the determination of power gain. The material in Chapter VII is concerned entirely with radio frequency oscillator design and experimental results obtained from tests performed on the circuit.

The conclusions and suggested fields of endeavor which could prove fruitful as far as providing additional information about transistor amplifiers and oscillators are mentioned in Chapter VIII.

### CHAPTER II

### NEUTRALIZATION OF THE TRANSISTOR AMPLIFIER

### A. INTRODUCTION

A two terminal pair network is unilateral if an excitation placed at one terminal pair produces a response at the second terminal pair and an excitation applied to the second terminal pair produces no response at the first terminal pair. Networks capable of transmission in both the forward and reverse direction are considered nonunilateral or bidirectional.

A transistor is inherently a nonunilateral device.

This fact presents the design engineer with a formidable problem when attempting to design a tuned radio frequency amplifier. In this respect vacuum tubes have a definite advantage since they are essentially unilateral in nature except at extremely high frequencies.

### B. THEORY OF NEUTRALIZATION

Methods of neutralization. The transistor being of a nonunilateral nature is capable of backward transmission or internal feedback. The disadvantage of this is twofold:

- 1. The input and output immittances respectively are functions of the load and generator impedances.

- 2. The circuit may become oscillatory without the addition of an external feedback circuit.

The above disadvantages make it necessary to neutralize transistor circuits used in the above mentioned application.

when stages of an amplifier are tuned the dependence of output and input immittances on the load and generator impedances make accurate alignment of the stages

virtually impossible. For example, if the reasonant frequency of the second stage of a three stage amplifier is

changed by some increment of frequency, the impedance offered to the following stage is subject to a change as well

as the input impedance to the second stage. Therefore, a

means by which these disadvantages are eliminated is required if transistors are to be used at high frequencies

in tuned amplifiers.

currently there are two means available by which the effects of backward transmission on the input and output impedances of transistors can be eliminated. First, the stages may be purposely mismatched, that is, instead of matching a

1500 ohm output to a 300 ohm input, allow the output to soe approximately a 300 ohm load. The loss of power for a micratch such as this is only approximately 2 db. Second, the amplifier may be made unilateral or neutralized by the addition of an external network. It is the second method which is of primary concern since, its use results in maximum power gain from the transistor. In some cases the thoro complete neutralization is used, the amplifier has a greater gain than that obtained from the unneutralized unit.

Theory of neutralization. A two port device can be dofined completely by two voltages and two currents as shown below in Fig. 1.

FIG. 1 TRANSISTOR TERMINAL VOLTAGES AND CURRENTS

There are six sets of two linear equations which may be used to describe a two terminal pair network. These equations involve six sets of different parameters, four of which are useful in determining internal feedback. These parameters are:

All references are in the bibliography

- 1. h parameters

- 2. y parameters

- 3. z parameters

- 4. g parameters

These equations have this general form in matrix notation:

$$\begin{bmatrix}

M_1 \\

M_2

\end{bmatrix} = \begin{bmatrix}

K_{11} & K_{12} \\

K_{21} & K_{22}

\end{bmatrix} \times \begin{bmatrix}

L_1 \\

L_2

\end{bmatrix} \tag{1}$$

where  $M_i$  denotes the dependent variable,  $L_i$  the independent variable, and  $K_i$  the network parameters. The K parameters have a physical relationship to the network depending on their position in the matrix. They are:

K<sub>11</sub> is an input immittance

$K_{12}$  is a backward transfer ratio

$K_{21}$  is a forward transfer ratio

$K_{22}$  is an output immittance

${

m K}_{12}$  is the parameter which determines the magnitude of the response at the input terminal for an excitation at the output terminals.  ${

m K}_{12}$  is responsible for internal feedback.

The network is unilateral if K<sub>12</sub> is equal to zero. The importance of unilateralization is readily seen by comparing the input and output immittance of a unilateral and a nonunilateral network.

Consider the circuit in Fig. 1. The two linear equations for the nonunilateral configuration are:

$$e_1 = h_{11} l_1 + h_{12} e_2$$

$$l_2 = h_{21} l_1 + h_{22} e_2$$

(2)

The input impedance is

The output admittance is

$$10 = h_{22} - \frac{h_{11}h_{21}}{h_{11} + Zg}$$

(4)

When the network is made unilateral  $h_{12}$  is equal to zero and the input impedance is

$$Z_{IN} = h_{II} - 0 \tag{5}$$

The output admittance is

Thus, we see that a neutralized network has an input and output immittance which is independent of  $Z_g$  or  $Y_L$ . The problem of reflected impedances is thereby eliminated by complete neutralization, which in essence, is achieved by making the input terminals response independent of the ex-

eitation at the output terminals.

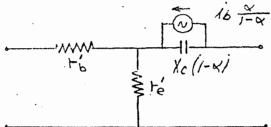

An equivalent circuit for the common emitter connection is shown in Fig. 2 below<sup>2</sup>.

FIG. 2 HIGH FREQUENCY EQUIVALENT CIRCUIT

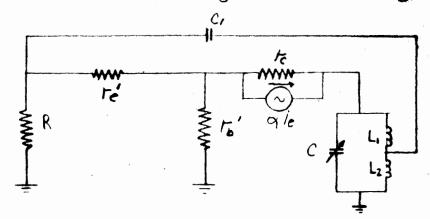

To determine the external feedback required to cause the backward transmission to be zero a balanced bridge circuit shown in Fig. 3 is utilized in the analysis. R<sub>2</sub> and r<sub>c</sub> are neglected because of their large relative magnitudes.

FIG. 3 A BRIDGE NEUTRALIZED CIRCUIT

The required elements to effect complete neutralization are  $c_1$ ,  $c_2$ ,  $c_3$ , and  $c_3$ . For a balanced bridge

$$\frac{C_{i}}{C_{3}} = \frac{R}{F_{6}} = \frac{C_{c}}{C_{2}} \tag{7}$$

If  $r_b \ll \frac{1}{\omega c}$  then the effects of feedback through  $C_c$  are cancelled by inserting only  $C_1$ . This does not result in complete neutralization but does considerably reduce the variation of input and output impedance. The partially neutralized output impedance is derived in Appendix 1.

The 2N1271 has an extremely low  $r_b$  °C<sub>c</sub> product, typically, 300 psec. The symbol used for  $10^{-12}$  is "p". C<sub>c</sub> is approximately 3 pfrds and  $r_b$  is very much less than  $X_c$ .

### C. EXPERIMENTAL DETERMINATION OF THE NEUTRALIZING CAPACITANCE

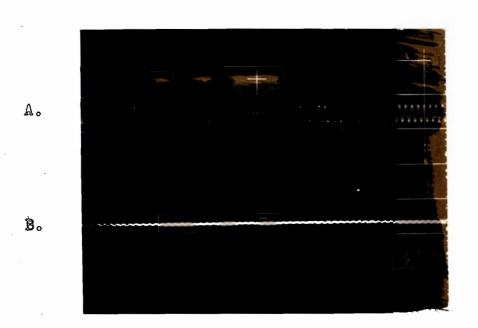

The neutralizing capacitance was determined experimentally by applying a RF signal at 10 Mc. to the output of the transistor. The magnitude of the signal at the input: was tuned to a minimum by varying Cn. The circuit used to accomplish this is shown schematically in Fig. 4. Fig. 5 shows the actual reduction of feedback voltage by neutralization. The actual change was .03v to .002v with a signal of .31v on the collector.

FIG. A NEUTRALIZATION OF TRANSISTOR

FIG. 5 THE BASE TO EMITTER VOLTAGE

- A. UNNEUTRALIZED

- B. NEUTRALIZED

Procedure. The procedure used in the experimental determination of  $C_n$  was to apply a signal to the output and vary  $C_1$  until maximum voltage was obtained at the oscilloscope. This indicated when the collector tank circuit was tuned to 10 Mc.  $C_n$  was then adjusted until the signal at the base was the smallest value obtainable. The neutralizing capacitor was then measured on the "Q" Meter. The values obtained for  $C_n$  are shown in Table 1.

TABLE I NEUTRALIZING CAPACITANCE

| Unit | c <sub>n</sub> ( | N <sub>2</sub> /N <sub>1</sub> C <sub>n</sub> |

|------|------------------|-----------------------------------------------|

| В    | 4.0              | 1.66                                          |

| С    | 4.8              | 1.96                                          |

| D    | 7.6              | 3.15                                          |

The quantity  $N_2/N_1$   $C_n$  is the value of  $C_n$  used if the output transformer had a turns ratio of one to one.  $C_n \times N_2/N_1$  should be approximately equal to  $C_c$  where  $N_1/N_2 = 2.41$

Conclusions. The effect of neutralization on the circuit was realized when upon completion of the amplifies otages an attempt was made to accurately tune the coupling

networks. Without neutralization the spurious oscillations were so severe that no tuning could be accomplished until the neutralizing capacitors were adjusted. The values obtained for  $\mathtt{C}_n$  were within the specified range for  $\mathtt{C}_c$  and are therefore in agreement with the theoretical expectations.

### CHAPTER III

### INPUT AND OUTPUT IMPEDANCE DETERMINATION

### A. INTRODUCTION

Prior to the design of interstage coupling networks the input and output impedances of the transistor must be known. This enables the designer to meet the circuit requirements for a specified Q and, at the same time, match impedances to effect maximum power transfer from stage to stage.

Statement of the problem. The input and output impedance of a transistor used in high frequency applications must be neutralized unless the transistor has incorporated in it some particular mechanism which causes it to completely or, at least, for all practical purposes to act as a unilateral device. The tetrode transistor is one of this type. A potential is placed across the base region which reduces the effective path for carriers, consequently, a decrease in the high frequency resistance  $\mathbf{r}_b$  is realized.

The transistor chosen for this particular application is a surface alloy diffused base transistor manufactured by the Philco Corporation. This transistor is es-

pecially suited for high frequency applications at ten megacycles because it has a low  $r_b$ '  $C_c$  product. This transistor, however, must be neutralized by some external means. Neutralization and the reason it is required are discussed in Chapter II.

The problem is the determination of the input and output impedance of the transistor with neutralization. The neutralized input and output impedances are, with good approximation, equal to the input and output short circuit impedances of the transistor. This method is suggested by the Philco Corporation.

The chapter is divided into two parts, (1) a theoretical analysis of the experimental measurements to be carried on and (2) experimental results.

### B. THEORETICAL ANALYSIS OF INPUT AND OUTPUT IMPEDANCES

The transistor can be described adequately using h parameters.

$$e_{i} = h_{ii} \lambda_{i} + h_{i2} e_{2}$$

$$\lambda_{2} = h_{2i} \lambda_{i} + h_{22} e_{2}$$

(8)

Upon addition of a neutralizing network adjusted so that  $h_{12} = 0$  a new set of h parameters are obtained.

$$e_{1} = h_{11} l_{1} + (0) e_{2}$$

$$l_{2} = h_{21} l_{1} + h_{22} e_{2}$$

(9)

If in a transistor  $E_2 = 0$  a good approximation to the neutralized input impedance is

$$Z_{IN} = \frac{\ell_I}{\ell_I} = h_{II} \tag{10}$$

The y parameters for the transistor are defined by the following equations:

$$\begin{cases}

1 & | = y_1 e_1 + y_1 e_2 \\

1 & | = y_2 e_1 + y_2 e_2

\end{cases}

\tag{11}$$

In the typical junction transistor today  $y_{11}$  is much less than  $y_{12}$ . The magnitude of difference between  $y_{11}$  and  $y_{12}$  being approximately a factor of 10 or greater, the input impedance is not affected appreciably by neutralization, that is,

$$\mathcal{Y}_{ii} = \mathcal{Y}_{ii} + \mathcal{Y}_{ii}^{"} \tag{12}$$

$$\mathcal{Y}_{n}^{"}\cong\mathcal{Y}_{12} \tag{13}$$

$$y'' \stackrel{\cong}{=} y'' \tag{14}$$

The admittance parameters  $y_i$  apply to the neutralized circuit,  $y_i$  to the neutralizing circuit alone, and  $y_i$  to the transistor.

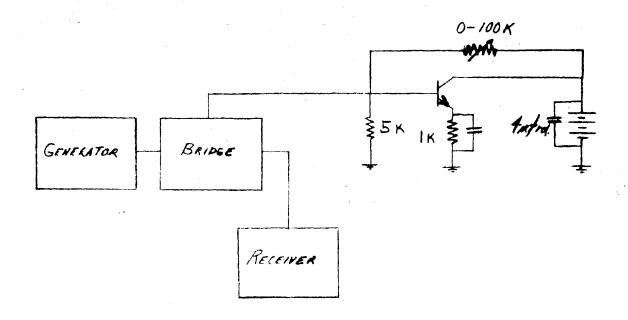

The short circuited input impedance was measured at 9.0, 9.5, 10.0, 10.5, and 11 megacycles. The circuit used to measure this is shown in Fig. 6. The equivalent circuit used to theoretically determine the input impedance was chosen because it is well suited for this particular application. It was developed by J. B. Angell. The equivalent circuit and solution for the input impedance is shown in Appendix 2. The short circuit and partially neutralized output impedances are determined and compared in Appendix 1.

### C. EXPERIMENTAL DETERMINATION OF INPUT AND OUTPUT IMPEDANCE

The first method investigated to provide input and output impedances proved too inaccurate and cumbersome to warrant its use. Essentially, the approach was to resonate a tank circuit with the input capacitance of the transistor and then remove the tank circuit from the input. The tank circuit was then connected to the input terminals of a Q meter and the required capacitance to resonate the circuit at the specified frequency was measured. The magnitude of the input impedance was determined by measuring the voltage across the input and the current through it. Once the magnitude of the input impedance and the capacitive reactance was obtained the resistive component of the input was

determined. The result of the measurement was not in agreement with the theoretical expectations due to the variation in stray capacitance caused by moving the tank circuit, and the difficulty in reading input voltages accurately.

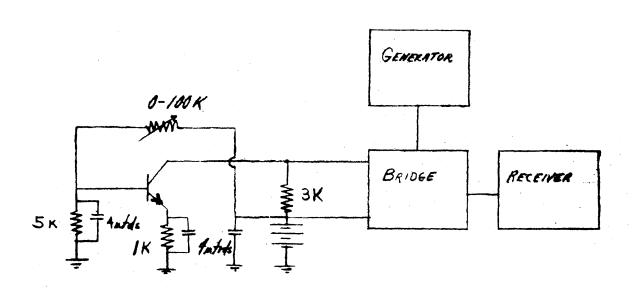

The method which was used with a fair degree of success was one incorporating a high frequency bridge circuit used in conjunction with a sensitive receiver. The bridge circuit also provided measurement in far less time than the previous method described.

The equipment used in this measurement was 605A General Radio Frequency Standard Oscillator, A General Radio Type 916A Bridge, and a Hammerlund Super-pro Receiver. This equipment was connected as shown in Fig. 6.

The Type 605B Standard Signal Generator has a frequency Range of 9.5 k.c. to 30 Mc. and the output is continually variable from 0.5 microvolts to .1 volt. The type 916A Radio Frequency Bridge is a null instrument for use in measuring impedance at frequencies from 400 k.c. to 60 Mc. The Hammerlund Super-pro Receiver covers a frequency range of 100 k.c. to 20 Mc. The receiver has two features which are essential to permit its use as a bridge detector, a manual

AVC "on-off" switch, and a beat frequency oscillator.

The oscillator, which provided a constant amplitude signal, was connected to the input of the bridge. The unknown terminals were connected to the input (or output) terminals of the transistor. The output of the bridge was connected to the receiver which was tuned to the frequency of the oscillator. The AVC was turned off to enable accurate selection of the null point, and the beat frequency oscillator in the receiver allowed detection of the constant amplitude RF from the bridge.

The impedances were read from the bridge. Since the bridge was a series impedance measuring device the readings were converted to their effective parallel impedances. This was accomplished and the result shown in Table II.

TABLE II

INPUT AND OUTPUT IMPEDANCE OF THE 2N1271

WITH FREQUENCY AS THE VARIABLE

$$I_c = 2 \text{ ma.}, V_c = 10$$

# UNIT B.

| Frequency | R <sub>in</sub> (ohms) | C <sub>in</sub> (pfrds) | R <sub>O</sub> (ohms) | C <sub>o</sub> (pfrds) |

|-----------|------------------------|-------------------------|-----------------------|------------------------|

| 11,0      | 467                    | 15                      | 2290                  | 5                      |

| 10.5      | 504                    | 15                      | 2290                  | .5                     |

| 10.0      | 505                    | 1 <u>5</u>              | 2000                  | 5                      |

| 9.5       | 523                    | 15                      | 2600                  | 5                      |

| 9.0       | 467                    | 15                      | 2270                  | . 5                    |

| 9.5       | 523                    | 15                      | 2600                  | 5<br>5<br>5            |

### UNIT C.

| Frequency | R <sub>in</sub> (ohms) | C <sub>in</sub> (pfrds) | R <sub>o</sub> (ohms) | Co (pfrds) |

|-----------|------------------------|-------------------------|-----------------------|------------|

| 9,0       | 467                    | 15                      | 4700                  | 2          |

| 9.5       | 489                    | 15                      | 2810                  | 2          |

| 10.0      | 571                    | 15                      | 3080                  | 2          |

| 10,5      | 548                    | 15                      | 3120                  | 2          |

| 11.0      | 640                    | 15                      | 3250                  | 2          |

TABLE II (continued)

UNIT D.

| Frequency | R <sub>in</sub> (ohms) | Cin (pfrds) | R <sub>o</sub> (ohms) | C <sub>o</sub> (pfrds) |

|-----------|------------------------|-------------|-----------------------|------------------------|

| 11.0      | 191                    | 20          | 2060                  | 2                      |

| 10.5      | 194                    | 20          | 2050                  | 2                      |

| 10.0      | 214                    | 20          | 2350                  | 2 ·                    |

| 9.5       | 201                    | 20          | 2221                  | 2                      |

| 9.0       | 177                    | 20          | 2010                  | 2                      |

A. DETERMINATION OF INPUT IMPEDANCE

B. DETERHINATION OF CUTPUT IMPEDANCE

FIG. 6 DETERMINATION OF INPUT AND OUTPUT IMPEDANCE

#### CHAPTER IV

### BIAS NETWORK DESIGN

#### A. INTRODUCTION

There has been considerable work done on the bias stabilization of transistors. It is the purpose of this chapter to design a bias network which will afford stability over a range of temperature from 78°F. to 250°F. The method of approach to this problem has been investigated by S. K. Ghandi<sup>5</sup> and it is his conclusions which are used in the physical explanation.

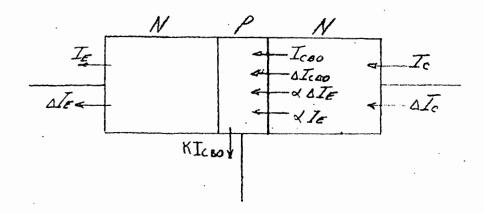

Changes in temperature to which a transistor is subjected results in a shift in operating point and in some instances causes the transistor to destroy itself. Increasing temperatures cause electon-hole pairs to be generated in the base and collector regions. In an NPN transistor the electrons tend to migrate to the collector and the holes to the base. The result is the leakage current increases, and the base region developes a hole-excess causing base current to flow. The amount of base current which flows depends on the magnitude of the impedance in the base lead. If in a unit time only a fraction, K, of the electrons entering in

FIG. 7 TRANSISTOR CURRENTS

the base are removed the base current is K I<sub>cDo</sub>. The (1-K) I<sub>cDo</sub> causes electrons to be injected from the emitter, which increases the emitter current. A fraction of these electrons reach the collector and (1-0() combine with holes in the base, which results in the current relationships

$$\Delta I_{E}(1-\alpha) = (1-\kappa)\Delta I_{CBO}$$

(15)

$$\Delta I_{c} = \alpha \Delta I_{E} = \frac{I-K}{I-\alpha} \Delta I_{cBo} \alpha$$

(16)

This increase in collector current results in increased dissipation in the collector and consequently a slightly higher temperature which causes an increase in electron-hole pair production and the process is repeated. The ambient temperature and the cooling technique utilized determines if the process increases until the transistor destroys itself, or at some elevated temperature becomes stable.

The second factor which increases the thermal sensitivity of this device is the forward resistance of the base to emitter diode. The resistance of this junction decreases as the temperature is increased resulting in a further increase in emitter current. The magnitude of this increase is dependent on the relative impedance levels of the base and emitter leads.

In general stabilization is improved if (1) The base is fed from a low impedance source ( $K \rightarrow 1$ ); (2) The emitter is fed from a high impedance source ( $AI_E \rightarrow 0$ ).

### B. DESIGN CONSIDERATIONS

The previous section provides a physical explanation of the mechanism of operating point variations with temperature changes. It is necessary now to examine each factor in particular which affects the stabilization of the operating point.

The specified maximum and minimum values of current gain  $h_{fe}$  at the operating point is an important consideration since the variation in  $h_{fe}$  takes into account the change in current gain anticipated if the transistors are replaceable. The variation of  $h_{fe}$  caused by temperature changes must also

be included; this information can be obtained from graphs usually made available by the manufacturer. The variation of collector current which was discussed previously increases 6.5 - 8% per degree centigrade and doubles with a temperature change of 9-11°C. In the design of the bias network, the minimum valve of I<sub>CBO</sub> is assumed zero, and the maximum value is obtained from transistor curves of I<sub>CBO</sub> versus temperature.

The variation of  $V_{\text{BE}}$  must be taken into account. Under normal bias conditions  $V_{\text{BE}}$  for a silicon transistor is approximately + .7 volts but it may become necessary at elevated temperatures to reverse bias this junction to obtain low values of collector current.

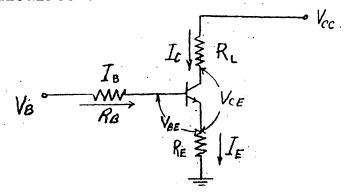

Fig. 8 shows a typical grounded emitter stage which is a general circuit. This circuit was analyzed and from the results the resistive components used in the final circuit were calculated.

FIG. 8 TYPICAL GROUNDED EMITTER STAGE

The following equations apply to the circuit in Fig. 8.

$$h_{AB} = \frac{\omega}{I - \omega} \tag{17}$$

$$I_c = dI_e + I_{co}$$

(19)

$$\overline{I}_{E} = (h_{fe} + I) \overline{I}_{b} + \overline{I}_{co}$$

(20)

The method used to design the bias network was to obtain two equations for  $V_{\mathcal{S}}$ :

I. When the temperature is at its minimum value, IE is a minimum and the worst conditions that could occur are for h = h fe min, V = V se max and I = 0. Thus,

$$V_{B} = \frac{\int R_{B}}{(b_{fo}+I)} + k_{E} \int I_{E} \operatorname{Mid} + |b_{E}| \operatorname{Max}$$

(22)

In is a maximum and the worst value the parameters could have are for he fe max

Very Very I = I Thus,

BE BE min co co max

Solving Equations 22 and 23 the value of R can be calculated in terms of R and the circuit parameters. The resulting

equation is of the form

$$R_B = KR_E - C \tag{24}$$

where K and C are constants. To convert to a single battery bias network  $V_{\mathfrak{p}}$  had to be determined from Equation 22. This is done in Section C.

Stability relationship. The stability factor of the bias circuit is defined as the rate of change of  $I_c$  with respect to  $I_{co}$ . This factor gives an indication as to the relative merit of the bias circuit when subjected to changes in temperature. Equation 21 is used in the determination of the stability of the network with the following substitution for base current:

$$\overline{I}_{B} = \frac{(-\alpha)\overline{I}_{c}}{\alpha} - \underline{I}_{co} \qquad (25)$$

Making this substitution for  $I_b$ , replacing  $I_c$  by  $I_b$  +  $I_e$ , and neglecting  $V_{be}$  an equation for stability is obtained by differentiating  $I_c$  with respect to  $I_{co}$ .

$$S = \frac{1}{R_E \ll} + 1 - \infty$$

(26)

## C. DESIGN OF THE BIAS NETWORK

Enumerated below is the procedure used in the bias circuit design. 7

- 1. Range of temperature was 78°F to 250°F.

- 2. The values of  $I_{QO}$  obtained from a graph supplied by the manufacturer was  $I_{CO max} = 50$  micro amperes and  $I_{CO min} = 0$ .

- 3. The current gain was determined by using the manfacturer's tolerance and adding to the maximum

specified value the variation due to temperature at the upper limit. This was determined

from a plot of the transistor parameters versus

temperature. The minimum value of h<sub>fe</sub> remained

the same because the parameter variations were

normalized to 78°F. The maximum value for h<sub>fe</sub>

was 47, and the minimum value was 11.

- 4. The maximum and minimum values of emitter current were determined by the points on the  $I_c$  versus power out curve at which the gain was reduced by 1 db. The values of  $I_e$  determined were  $I_{e max} = 2.76$  ma. and  $I_{e min} = 1.55$  ma. The actual values used in the design equations were modified by a factor of 15% due to the tolerance of bias resistors. The correction resulted in  $I_{e max} = 2.23$  ma and  $I_{e min} = 1.795$  ma.

- 5. Using Equations 22 and 23  $R_{\mbox{\scriptsize B}}$  was then solved in terms of  $R_{\mbox{\scriptsize E}}$ .

Let  $R_{\varepsilon} = 1000$  ohms which is sufficient to swamp the base to emitter forward resistance. Rg is equal to 2.25K ohms.

The value of  $V_{\mathbf{R}}$  is determined from Equation 22 which is the condition of minimum temperature. Close examination of Equation 23 shows why the V<sub>B</sub> is determined from the equation for minimum temperature. The term -(I RE) which becomes significant at high temperatures has a tendency to lower Vg. Therefore, in the design the highest value of V6 is chosen and the associated voltage divider is calculated for this particular quantity.

The bias circuit used for the amplifier is a single battery type shown in Fig. 9.  $R_3$  is equal to  $R_E$  . The resistor R2 may be found from the following relationship which neglects the input coil resistance.

$$\frac{R_1}{R_B} = \frac{V_{CC}}{V_B}$$

$$(28)$$

$$R_1 = \frac{R_B V_{CC}}{V_B} = 10 \text{ (29)}$$

$$R_1 = \frac{R_B Vcc}{VB} = 10 KA$$

(29)

$$R_2 = \frac{R_1 V_B}{V_{CC} - V_B} = Z.9 K_A \tag{30}$$

The final bias circuit is shown in Fig. 9.

#### D. EXPERIMENTAL RESULTS

The procedure. To check the accuracy of the design equations one of the units was subjected to a temperature change of  $172^{\circ}F$  to determined the variation of  $I_{\mathbf{g}}$ . The transistor was inserted in the designed bias circuit, and the voltage across  $R_{\mathbf{g}}$  was monitored by using a vacuum tube voltmeter. A heating element was connected to the transistor. The temperature was controlled by a variac which supplied power to the heat source. Temperature readings were obtained from a Weston thermometer attached to the heating element Approximately 15 minutes was allowed for the temperature to stabilize before the initial reading of  $I_{\mathbf{g}}$  was taken. The same interval of time was allowed between each successive

reading. This data shown in Table III.

Conclusions. The results are plotted graphically in Fig. 10. The variation in  $I_{\rm g}$  as the temperature was changed from  $84^{\rm O}F$  to  $250^{\rm O}F$  was 144 micro amperes. The emitter current stayed well within the upper limit of the desired value of 2.76 ma., since, the maximum experimental value of  $I_{\rm g}$  was less than 2.0 ma. The minimum value of  $I_{\rm g}$  allowed was 1.55 ma. which was considerably less than the minimum obtained experimentally (1.8 ma.).

The stability predicted theoretically was 2.94, this is in close agreement with the experimental results. The graph of  $I_{\rm CO}$  versus temperature provided by the manufacturer shows a variation in  $I_{\rm CO}$  of 50 micro amperes over the range of temperature considered. The expected increase in  $I_{\rm C}$  is S  $I_{\rm CO}$  which is 150 micro amperes. The value found experimentally was 144 micro amperes change in  $I_{\rm E}$ .

Since the network is designed for maximum protection at the higher temperatures, the value of  $I_{\rm c}$  is usually lower than the optimum value of 2 ma. at which maximum power gain occurs. This problem is eliminated by increasing the size of  $R_2$ . This results in only a slight change in stability.

TABLE III. STABILITY DATA

| READING | TEMPERATURE | CURRENT (ma) |

|---------|-------------|--------------|

| 1       | 84.0        | 1.80         |

| 2       | 88.0        | 1.80         |

| 3       | 99.0        | 1.80         |

| 4       | 109.5       | 1.81         |

| 5       | 140.0       | 1.82         |

| 6       | 159.0       | 1.84         |

| 7       | 179.0       | 1.85         |

| 8       | 205.0       | 1.89         |

| 9       | 250.0       | 1.94         |

#### CHAPTER V

#### DESIGN OF COUPLING NETWORKS

#### A. INTRODUCTION

The coupling networks used in the amplifier interstage networks were of the single-tuned transformer coupled type. The original design was for three staggered tuned stages separated to give a flat bandwidth between 9.5 and 10.5 Mc. Theoretically this is entirely feasible, however, practically the design of these stages proved impossible. When it was found that a one megacycle flat response could not be obtained the design requirements were changed to allow a one megacycle response between the three db points. This chapter is divided into two parts; (1) devoted to the work done in an endeavor to stagger tune the stages; (2) the final design of the single-tuned stages which were ultimately used in the amplifier.

Interstage design for stagger-tuned amplifiers. First, the center frequency and required Q for the networks was determined. This was accomplished using methods previously developed for vacuum tubes. To obtain the required bandwidth, two stages with a dissipation factor of D at frequencies of  $f_0$  and  $f_0$  were required. The third stage was tuned to

the center frequency of the cascade and had a dissipation factor of S. The dissipation factor is defined as  $1/Q_L$ .  $Q_L$  is the loaded Q of the coil, and A is equal to one plus .433S.

From the design equations previously mentioned the frequencies of the tuned circuits were found to be 9.58 Mc., 10 Mc., and 10.433 Mc. with loaded circuit Q's of 20,10, and 20, respectively. The design of the two stages requiring a Q<sub>L</sub> of 20 were impossible to fabricate with the material available.

To illustrate the difficulty encountered, consider the design of an interstage coupling network at a frequency of 10.433 Mc. This is typical of the problem which arose in attempting to secure a  $Q_{\rm L}$  of 20.

The coils were wound by hand and a trial and error procedure, was used to obtain the values of inductance because the permeability of the core was not known. Initially it was assumed that the coupling circuit acted as a perfect transformer which transformed impedance proportional to the square of the turns ratio. This assumption is only valid if the coefficient of coupling between the primary and secondary inductances is approximately equal to one. This assumption is verified in another section of this chapter. It is desir-

ous to match the output of a generator to the load if maximum power transfer is to be realized. This match is obtained when  $R_{\rm o} = Q^2 R_{\rm in}$  where  $R_{\rm in}$  is the input resistance to the transistor and  $R_{\rm o}$  is the output resistance neglecting coil losses. The selectivity or bandwidth relation is determined by the  $Q_{\rm L}$  of the circuit which is equal to

$$Q_L = \frac{f_0}{Af} = \frac{2\pi R_0 C_T f_0}{2} \tag{31}$$

where  $C_{\rm t}$  is the capacitance required to cause the tank to resonate at the desired frequency and  $R_{\rm o}/2$  is the resistance in parallel with the coil. Using the above relationship  $C_{\rm t}$  was found to be equal to 247 pfrds. Having determined  $C_{\rm t}$ ,  $L_{\rm t}$  was readily found from the relationship  $L_{\rm t} = 1/\omega_0^2$   $C_{\rm t}$ .  $L_{\rm t}$  was found to be .943 x 10<sup>-6</sup> micro henries.

The coil was then wound on a Miller #4500 adjustable ceramic form with a ferrite core. When the Q was measured on a Q Meter it was found that the coil possessed a Q of 30. However, upon further investigation it was found if the coil was wound too near the mounting nut, this fastener would act as a short circuited turn, lowering the Q of the coil by 40 to 50 percent. When the coil was properly located on the form the Q of the circuit was found to range between 50 and 60 for the three coils forms. Knowing the value of Qu the effective shunt resistance of the coil could be found from

the equation  $R_c = Q_u X_L = 58 \times 61.7 = 3580$  ohms.  $Q_u$  is the unloaded Q, that is, the Q of the coil alone. The output resistance of the transistor was found to be 2486 ohms. By matching the input to the output the effective resistance in shunt with the tank circuit is 1243 ohms, neglecting the effective coil resistance. When the resistance of the coil is taken into account an effective shunt resistance of 1243/4823 3580 = 1060 ohms is obtained. The loaded  $Q_L$  is now  $R_{\odot}/X_L$  = 1060/61.7 = 17.2. The obvious thing to do is to reduce the value of  $X_{T,\bullet}$ . A reduction in  $X_{T,\bullet}$  is accompanied by a reduction in  $\mathbf{R}_{\mathbf{c}}$  (shunt resistance of the coil), and it was found that no matter how much  $X_{L}$  was decreased the  $Q_{L}$  would never approach the value of Q desired. This condition is a result of initially having a low value of inductive reactance. If X<sub>T</sub> decreases, and the  $\mathbf{X}_{\mathbf{L}}$  is large enough, the change in  $\mathbf{R}_{\mathbf{c}}$  in parallel with R of the transistor is not as large as the change obtained in  $X_{\underline{L}}$ , thus, the  $Q_{\underline{L}}$  would increase. cases, when the  $Q_{\tau}$  of the circuit is not too high a reduction in inductance usually compensates for the resistance of the coil.

A more thorough theoretical investigation into the feasibility of obtaining the desired selectivity characteristic with a  $Q_{\rm u}$  of 50 proved interesting. 9

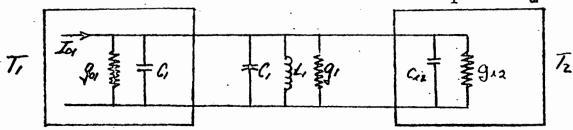

If  $B_1$ ' is defined as  $Af/f_0$ ,  $g_{01}$  as the output conductance of transistor one,  $g_{12}$  as the input conductance of transistor two, then an equation is developed which gives maximum power transfer efficiency as a function of  $B_1$ ' and  $Q_0$ .

FIG. 11 COUPLING NETWORK

Referring to Fig. 11 the power available from transistor one is  $P_{i} = \frac{\left| \prod_{o,i} \right|^{2}}{4 g_{oi}}$  (32)

where I is output current of transistor one. The power of

$$P_{z} = \frac{|I_{0}|^{2}g_{iz}}{(g_{01} + g_{1} + g_{iz})^{2}}$$

(33)

Power transfer efficency is defined as

delivered to transistor two is

$$V_{1}^{2} = \frac{P_{2}}{P_{1}} = \frac{4901922}{(901+922+91)^{2}}$$

(34)

this shows that for n to be equal to unity,  $g_1$  must be equal to zero and  $g_{01}$  equal to  $g_1$ .

B<sub>1</sub> can also be expressed as

$$B_{i}' = \frac{g_{0i} + g_{i2} + g_{i}}{g_{i} Q_{ij}}$$

(35)

Obtaining  $g_1$  from Equation 35 and substituting into Equation 34 n is found as a function of  $g_{01}$  and  $g_{12}$ . Differentiating n with respect to  $g_{12}$  and equating the result to zero yields

$$\eta_{\text{EQUX}} = \left( \left| -\frac{1}{B_1' Q_0} \right|^2 \right) \tag{36}$$

Upon substituting values for  $B_1$  and  $Q_n$  the efficiency is 43% of the maximum obtainable if  $g_1$  was zero. This loss of 57% of the available power shows that even if the coupling circuit could be designed this loss of power would greatly affect the configuration of the response curve and a flat response would not be obtained.

The inability to obtain the desired  $Q_{\rm L}$  and the above mentioned effect on the response curve resulted in changing the coupling circuit requirement to a 1 Mc. bandwidth between 3 db. points. This problem was a result of the authors lack of knowledge on the subject of transistors and coupling networks at the time the selectivity requirements for the amplifier were chosen.

#### B. DESIGN OF SINGLE-TUNED STAGES

To obtain the desired bandwidth with three cascaded stages of amplifiers single-tuned, allowance had to be made for the reduction of bandwidth due to the selectivity of

each circuit. It is intuitively evident an overall bandwidth of 1 Mc between 3 db points cannot be obtained by the use of three stages, of bandwidth equal to 1 Mc. It has been shown that n single-tuned stages have an overall bandwidth

$$\beta_{1n} = \beta_1 \sqrt{2^{\gamma_n} - 1}$$

(37)

where  $B_1$  is equal to the bandwidth of one stage,  $B_1$  is equal to the bandwidth of n stages and n is the number of stages.  $^{10}$

Solving this for  $B_1$  with  $B_{1n}=1$  Mc., and n=3 it was found that  $B_1=1.96$  Mc. Equation 31 yielded a value of  $C_t$  equal to 65.3 pufrds. from which L was determined to be 4.64 x  $10^{-6}$  micro henries. The Q of the coil above was 58 which yielded an equivalent  $R_c=16,800$  ohms. It was found that neglecting the resistance of the coil the output resistance of the amplifier was 1243.5 ohms which resulted in a loaded  $Q_L$  of 4.28. This Q was too low to meet the per stage bandwidth requirement of 1.96 Mc. Again a trial and error process was used and the  $L_t$  of the coil reduced in small steps until a  $L_t$  of 3.47 micro henries was obtained.

This value of inductance resulted in an inductive reactance which made the  $Q_L$  obtainable with a slight mismatch. The resistance of the coil ( $R_c = Q X_L$ ) was combined with the output resistance of the transistor which was matched to the

input of the following stage. The parallel resistance of  $R_{\rm C}$  and  $R_{\rm O}$  was found to be 2080 ohms. If the input were matched to this resistance we would have 1040 ohms across the tank circuit which results in a loaded Q of 4.78. Therefore, rather than reduce  $X_{\rm L}$  any further the reflected input impedance was made of such size that the required  $Q_{\rm L}$  could be obtained. The value of  $a^2R_{\rm in}$  was found to be 2380.  $R_{\rm in}$  was equal to 408 ohms, therefore,  $a^2$  was 5.82. The final turns ratio was 17/7.05 = 2.41 = a.

The value of inductance originally required was 4.64 micro henries, which finally became 3.47 micro henries. The factor by which the inductance was reduced was 1.34, to keep the reasonant frequency constant the capacitance was increased by 1.34, resulting in a  $C_{\pm}$  of 87.6 pfrds. To determine the capacitance actually needed in the circuit the transferred input capacitance (2.9 pfrds.), the output capacitance (3 pfrds.) and the stray wiring capacitance (0-20 pfrds.) had to be subtracted from Ct. This resulted in a physical capacitance of approximately 60 pfrds, which was obtained from a fixed capacitance of 45.3 pfrds. and a trimmer capacitor of 5 to 20 pfrds. The graphical results of the frequency response is shown in Fig. 12. The overall bandwidth is a small amount less than 1 Mc. The percent error being approximately 2.5%. Table V shows the values used in plotting the graph of Fig. 12.

Determination of the coefficient of coupling. method of measurement of the coefficient of coupling utilized the Q Meter to determine the mutual inductance of the This was accomplished by first measuring the inductance of the primary and secondary windings. Two coils which are mutually connected have a total inductance given by the expression  $L_t = L_1 + L_2 + 2M$ , the plus or minus sign is determined by whether or not the coils are connected so the mutual fluxes are aiding. If the primary and secondary are connected one value for Lt is obtained, by reversing the connections on one winding another value for  $L_{t}$  is obtained. The difference in these values is 4 times the mutual inductance between the two coils. Knowing the mutual, primary, and secondary inductances K could be evalulated from the relationship  $K = M/\sqrt{L_1L_2}$ . Table IV shows the values of K obtained for the three units.

TABLE IV COEFFICENT OF COUPLING

| United Tested | Coefficient<br>of Coupling |

|---------------|----------------------------|

| 1             | •974                       |

| 2             | •965                       |

| 3             | •98                        |

With the coefficient of coupling near unity the transferred

impedance of the coupling network could be assumed proportional to the square of the turns ratio. This verifies the assumption made in the design of the coupling networks.

TABLE V FREQUENCY RESPONSE DATA

| FREQUENCY (Mc) | AMPLITUDE | FREQUENCY<br>(Mc) | AMPLITUDE |

|----------------|-----------|-------------------|-----------|

| 8.0            | .175      | 10.2              | •9        |

| 8.2            | .19       | 10.4              | •75       |

| 8.4            | •21       | 10.6              | • 58      |

| 8.8            | •30       | 10.8              | .45       |

| 9.0            | •37       | 11.0              | •35       |

| 9.2            | •48       | 11.2              | •26       |

| 9.4            | .61       | 11.4              | .22       |

| 9.6            | •79       | 11.6              | .18       |

| 9.8            | •95       | 11.8              | .14       |

| 10.0           | 1.00      | 12.0              | .10       |

FIG. 12

#### CHAPTER VI

#### AMPLIFIER GAIN

#### A. INTRODUCTION

The high frequency power gain of a transistor may be expressed in terms of fundamental device parameters. The first portion of this chapter will be devoted to the theoretical determination of high frequency power gain and then the experimental results will be evaluated. Construction of the amplifier will be considered and the problems encountered will be discussed.

Rigorous analysis by Pritchard<sup>11</sup> has shown that the high frequency power gain of the transistor can be expressed by the following equation

$$G = \frac{1}{25} \frac{f_0^2}{f_0^3} \frac{f_0^2}{f_0^2}$$

(38)

Experiments have shown that this equation is valid in the following frequency range.

$$05 - 01 < \frac{\omega}{\omega_{ro}} < Z \tag{39}$$

The transistor selected for use in this amplifier is a Surface Alloy Diffused-base silicon semiconductor. It has

an  $\swarrow_{\text{co}}$  frequency of approximately 60 Mc. The power gain predicted with the use of Equation 38 was a minimum of 18 db. and a maximum of 21.6 db. depending on the value of  $^{\circ}_{\text{b}}$  c used in the calculation, 300 or 165 psec respectively. The above mentioned range of  $^{\circ}_{\text{b}}$  c is controlled in the manufacture of the unit.

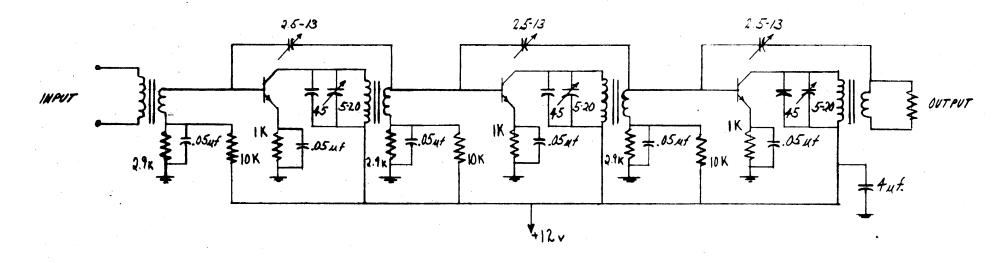

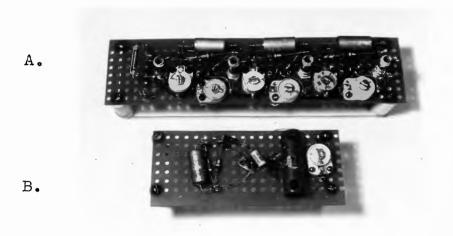

#### B. CONSTRUCTION

In the construction of the intermediate amplifier shown schematically in Fig. 13 a two inch wide and eight and one half inches long strip of plastic bread board material was used. Fittings could be inserted in the plastic for mounting the components and transistor easily. The circuit was constructed and a resistance check performed to ensure that no wiring errors were made. The assembled amplifier is shown in Fig. 14. The battery voltage was then applied, this caused the circuit to start a random oscillation which prevented any attempts to tune the coupling networks. This was due to a lack of neutralization. It was found that each circuit must be neutralized before these oscillations would desist. The second and third transistors were removed from the circuit and the first stage neutralized as described in Chapter II. Once this circuit was neutralized the second transistor was inserted and neutralized. This process was repeated on the third stage and oscillations did not recur. When the Stand-

# THREE STAGES OF AMPLIFICATION USING THE ZN1271

NOTE: ALL CAPACITANCE IN NMF. EXCEPT WHERE INDICATED OTHER VISE.

FIG 13. TOTAL AMPUFIER STRIP

ard Frequency Oscillator was connected to the input, oscillations were encountered if the amplitude of the signal input was raised larger than .5 milli volts.

FIG. 14 ASSEMBLED UNITS

#### A. AMPLIFIER

#### B. OSCILLATOR

It was found that if the supply voltage was bypassed by a 4 ufrd tantalytic capacitor the oscillations ceased. This capacitor was put directly across the battery connections at the amplifier.

With the circuit funtioning properly the neutralization was returned, to account for any slight variation due to the load changes since the initial adjustment was made with the circuit not terminated. Tuning was accomplished by plac-

ing the scope leads across the 427 ohm load registance and tuning from the input to the output stage. This had the disadvantage of adding some shunt capacity to the final stage due to the 14 uuf present in the scope probe. This would be corrected in an actual circuit.

#### C. EVALUATION OF GAIN

The power gain of the transistors to be used in the amplifier were checked and found to have the gains shown in Table VI. These gains were obtain from a circuit which was terminated in 427 ohms.

TABLE VI POWER GAIN PER STAGE

| UNIT | POWER GAIN |  |

|------|------------|--|

| A    | 18         |  |

| В    | 16         |  |

| С    | 18.6       |  |

|      |            |  |

The actual power gains are somewhat less than the theoretical values due to the wide tolerances on parameters allowed in the manufacture, as an example, the variation allowed

for h is 11 to 36, a variation of over 300%. The coupling

and bias networks may cause a reduction from the theoretical

power gain of .5 db. to 3 db., and the equation itself gives a slightly higher gain than can be obtained at the lower frequencies.

When the three amplifiers were cascaded the overall power gain was found to be approximately 49.4 db. margin for a large percentage of error in the measurement of the overall power gain due to the test equipment available. The measurement of voltages was accomplished by the use of a Techtronix Type 514 AD Scope whose vertical amplifier upper frequency limit was 10 Mc. The scope was the only voltage indicator available in that frequency range with sufficient sensitivity. The high frequency probe had to be used to keep shunt capacitance to a minimum which was 14 pfrds. The calibrated voltage range on the scope was from .03 to 50 volts peak to peak with a maximum vertical sensitivity of .03 volt The input voltage was on the order of .0015 volts. Therefore, the input voltage at best is a close approximation. The overall power gain of the three amplifiers in series was 49.4 db. Individually the amplifiers totaled to a gain of 52.6 db. which can be seen from Table VI. The power lost in the coupling networks can be computed from the equation  $P_{\tau}$  = 10 log<sub>10</sub>1/n where n is the efficiency calculated from Equation 34 Chapter V. The power lost is .66 db. and the efficiency is 86%.

Conclusions. The actual theoretical gain for the amplifier should be from 18 db to 21.6 db. Neglecting the losses in the coupling networks, the overall gain should be 54 to 64.8 db. depending on the value of  $r_b$   $^{\circ}C_c$ . The overall gain actually obtained was 51.38 neglecting coil losses. The gain obtained was slightly low, however, considering the limitations on the theoretical equation for power gain and parameter variations the results were reliable.

#### CHAPTER VII

#### THE VARIABLE FREQUENCY OSCILLATOR

#### A. INTRODUCTION

Quite frequently an alternating current energy source is required for some application, this energy can be supplied by a transistor oscillator. The purpose of this chapter is to design a radio frequency oscillator which will operate at 10 Mc. and be variably tuned. The main objective here is to obtain a design procedure, if a particular specification is desired once the procedure has been determined the design can be modified to fulfill these conditions.

#### B. DESIGN OF 10 MC VARIABLE FREQUENCY OSCILLATOR

Design procedure. It has been shown that the "T" equivalent circuit can be used in the analysis of transistor oscillators 12 if the effective capacitance across the collector to base region is assumed to modify the resonant frequency by its shunt capacitance. The use of the high frequency circuit in the analysis of oscillators provides accurate results in the establishing of conditions for oscillations.

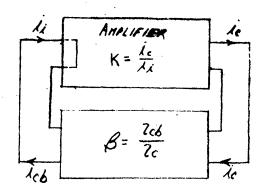

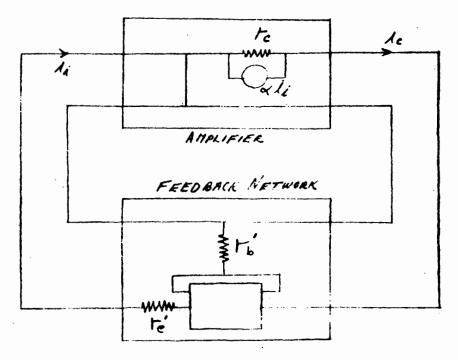

The general feedback circuit is shown in Fig. 15

FIG. 15 GENERAL FEEDBACK CIRCUIT

The amplifier is assumed to have zero input impedance, an output impedance  $Z_0$ , a short circuit current amplification of  $A_1$ , and be unilateral. The feedback network has for a short-circuited output, an input impedance  $Z_1$  and a current amplification  $\beta$ .

The current amplification when the amplifier is working into the feedback network is

$$K = Ai \frac{Z_0}{Z_0 + Z_i} \tag{40}$$

The starting condition for oscillation is that the total current amplification be unity, that is,

$$KB = Ai \left[ \frac{Z_0}{Z_0 + Z_i} \right] B = 1$$

(41)

$$\beta = \frac{1}{A_i \frac{z_0}{z_0 + z_i}} \tag{42}$$

The transistor does not have zero input impedance, but, by combining the parameters r<sub>b</sub>' and r<sub>e</sub>' with the feed - back network the circuit is arranged as shown in Fig. 17.

FIG. 16 HIGH FREQUENCY OSCILLATOR

FIG. 17 GENERAL FEEDBACK DIAGRAM

If in Equation 42 r is substituted for Z and of for A

$$\beta = \frac{1}{\alpha} \left( 1 + \frac{z_i}{f_e} \right) \tag{43}$$

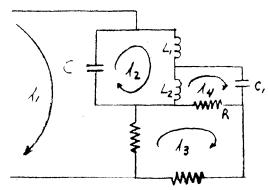

The input impedance to the network is usually much less than  $r_c$ . With good approximation  $\beta$  is equal to  $1/\alpha$ . The feedback network can be represented as shown in Fig. 18 if  $i_c = i_1$  and  $i_e = i_3$

FIG. 18 FEEDBACK NETWORK

Bwill be equal to  $i_3/i_1$  which is the current amplification of the feedback network. The analysis may be simplified if it is realized that the capacitance  $C_1$  provides feedback to the emitter circuit. If  $X_{c_1}$  is made small in comparison to the input impedance of the emitter circuit it can be neglected with little loss of accuracy. The resistance R which shunts the emitter input can be neglected if it is required that R be much larger than the input impedance of the transistor. The function of R is twofold, it developes the feedback voltage, and provides bias to the amplifier. When these approximations are incorporated in the feedback network the resultant circuit is shown in Fig. 19.

FIG. 19 APPROXIMATE FEEDBACK NETWORK

The resulting loop equations are:

Eliminating i2 from the above equations

Solving for  $\frac{1}{3}/1$  = the result obtained is

$$\frac{\dot{l_2}}{l_1} = \frac{\frac{L_2 + M}{c} + \frac{1}{6} \left( \rho l_7 + \frac{1}{\rho C} \right)}{\left( \rho l_7 + \frac{1}{\rho C} \right) \rho l_2 - \left( \rho l_2 + \rho M \right)^2 + \left( r_c' + r_a' \right) \left( \rho l_7 + \frac{1}{\rho C} \right)}$$

(47)

In the analysis of the feedback network it was found for the loop gain to be unity a  $\beta$  was required which was approximately equal to  $1/\alpha$ . To effect this relationship Equation 47 was set equal to  $1/\alpha$ :

The real part of the numerator multiplied by was set equal to the real part of the denominator, and the imaginary part of the denominator was set equal to waltiplied by the real part of the numerator.

Equating the imaginary parts

For this to be an equality  $(pL_T + 1/pC)$  must be zero. Thus, at resonance the effective series impedance of the tank circuit is zero. The resistance of the coil was neglected since the Q of the coil was approximately 150. Equating  $(pL_T + 1/pC)$  to zero we obtain

$$\omega^2 = \frac{1}{L_T C} \tag{50}$$

Equating the real parts the following relationship is obtained:

Sinse (pL, + 1/pC) is equal to zero

$$\frac{L_2 + H}{C} = -\left(\rho L_2 + \rho H\right)^2 \tag{52}$$

from which the magnitude of  $(L_2 + H)$  relative to  $L_t$  for escillations to start is obtained

$$\alpha = \frac{L_2 + M}{L_T} \tag{53}$$

This means that  $L_2$  + M must be very much larger than  $L_1$  + M. It was found, however, the point at which the tap for feedback was placed on the oscillator coil was not critical. Oscillations were started and sustained by the oscillator for turns ratios of  $2/22 < N_1/N_2 < 22/22$ . The industance used had a value of 15.5 micro henries and was resonated with a capacitor which could be varied from 5 to 20 pfrds.

The frequency range over which the circuit was tumable was to be theoretically 9.2 Mo to 16.8 Mc. The values obtained from the circuit were 9.48 Mc and 16.65 Mp. This resulted in a 2.94% error at the low end and a 1.2% error at the high end. The instrument used in the determination of frequency was the Techtronix Type 514 AD Oscilloscope which has a maximum sweep of .1 usec/per cm. At ten megacycles a reasonable approximation to the actual signal frequency is obtained. There is a high probability of error in reading the scope face, since 1/20 th of a centermeter error in reading the scope results in a 1/2 megacycle error in frequency. The stability of the oscillator could not be deterquency.

mined due to the limitations of the available measuring equipment.

The tunable range of frequencies was 16.65 Mc to 2.5 Mc. The upper limit could be extended if small values of inductance were used. The lower limit could be extended if larger values of inductance were used. Decreasing the frequency to 2.5 Mc by the addition of capacitance caused a continued decrease in collector load impedance to such an extent that oscillations could no longer be sustained.

The output was taken from the voltage developed across the emitter resistor R shown in Fig. 18. If maximum output power from the unit was required it could be obtained by transformer coupling. The coupling required to effect maximum power is determined by matching the load to the output impedance of the transistor assuming Class A operation. The circuit output is determined by the maximum voltage swing of the collector. The oscillations build up until the power dissipated is equal to the power generated or until a point of nonlinearity is reached preventing a further change in collector current.

Bias network. The bias network used on the oscillator was the same one designed for the grounded emitter amplifier and provided good results. The legitimacy of using this same

network is verified if the effect on stability is examined due to a 2 K resistance in the emitter circuit. The stability is defined by Equation 30. This change in  $R_1$  results in a value of S = 1.12 instead of 2.94.

<u>Conclusion</u>. The frequency output of the oscillator was described adequately by the equations developed, and the condition for oscillations to start was verified.

#### CHAPTER VIII

### SUGGESTIONS FOR ADDITIONAL INVESTIGATION

In the course of this study on transistors the author became aware of three additional subjects which might prove fruitful if investigated. Specific problems are not presented here but, rather, a general area which might be considered for additional development.

Intermediate frequency amplifiers to be used in a communication receiver usually must have provisions for automatic gain control. The gain control of stages is important when the input signal varies in intensity. This might be caused by radio frequency "skip" of signals which depend on the refractive effects of the ionosphere for long distance transmission.

Vacuum tube tranconductance can be easily varied by changing the operating point, providing easy control of the gain. Transistors, however, have essentially the same our rent gain over a wide variation of the operating point. A dependable means by which this gain can be adequately controlled presents an interesting problem.

Mixer circuits and converters are important to re-

ceivers and an investigation of the design of these two circuits would be valuable. An understanding of the design of the two circuits presented in this thesis, and the three additional subjects mentioned here, should prove helpful to an engineer considering a future in transistor circuit design.

#### BIBLIOGRAPHY

- 1. Stern, Aldridge, and Chow, "Neutralization of Transisto Amplifiers," The Proceedings of the IRE, Vol. 43, pp.87 847, July, 1955.

- 2. Chu, G.Y., "Unilaterization of Junction Transitors," The Proceedings of the IRE, Vol. 43, pp. 1001-1006, August, 1955.

- 3. Philcó Corp., "Tuned Amplifiers Design," Application Notes, Note 1, Form LTC 450, December 1959.

- 4. Angell, J.B., "High Frequency and Vidéo Amplifiérs,"

Handbook of Semiconductor Electronics, pp. 12-1,-12-26

McGraw Hill Book Company, New York, 1956.

- 5. Ghandi, S.K., "Analysis and Design of Transistor Bias Networks," Proceedings of the National Electronics Conference, Vol. 12, pp. 491-503, 1956.

- 6. Shea, R.F., "Transistor Circuit Engineering" pp. 55-59 John Wiley & Sons, Inc., New York, 1957.

- 7. Gottlieb and others, "General Electric Transistor Manual," pp. 36-39, General Electric Company, New York 1959.

- 8. Van Voorhis, S.M., "Microwave Receivers," Radiation Laboratory Series, Vol. 23, pp. 163-169, McGraw Hill Book Co.,

- 9. Shea, R.F., "Transistor Circuit Engineering," pp.160-172.

- 10. Sealy, S. "Radio Electronics," pp. 225-6, McGraw Hill Book Co., New York, 1956.

- 11. Pritchard, R.L., "High Frequency Amplifier Gain of Junction Transistors," The Proceeding of the IRE, Vol. 44, 1050-1052, August, 1956.

- 12. Shea, R.F., "Principles of Transistor Circuits," pp. 2: 229, John Wiley & Sons, Inc., New York, 1953.

- 13. Shea, R.F., "Principles of Transistor Circuits," pp. 340.

#### APPENDIX I

#### A. PARTIALLY NEUTRALIZED OUTPUT IMPEDANCE

The following is a determination of the partially neutralized output impedance of a transistor using a high frequency equivalent circuit. The procedure presented provides a method for determination of the output impedance with a feedback path. The equations presented here are of the transistor alone and do not consider the stray capacittance which is present in a practical circuit.

The neutralizing network is shown in Fig. 20.

$$E_{i} = \int \omega C_{N} \qquad \qquad \int e_{2}$$

$$y_{i} = \int \omega C_{N} \qquad \qquad y_{i} = \int \omega C_{N}$$

$$y_{2i} = \int \omega C_{N} \qquad \qquad y_{2i} = \int \omega C_{N}$$

FIG. 20 NEUTRALIZING NETWORK

The short circuit admittance equations for the neutralizing circuit are

$$L_1 = \ell_1 \mathcal{Y}_{11} + \ell_2 \mathcal{Y}_{12} \tag{54}$$

$$L_1 = \ell_1 \int_{11}^{11} + \ell_2 \int_{12}^{12}$$

(54)

$L_2 = \ell_1 \int_{21}^{11} + \ell_2 \int_{22}^{12}$  (55)

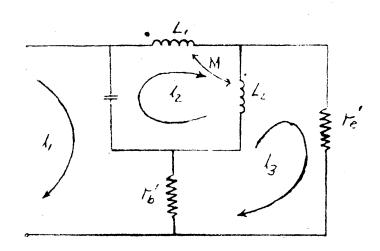

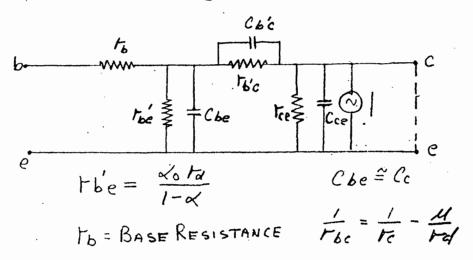

Fig. 21 is the high frequency equivalent circuit of the transistor.

$$Z_{11} = fe' + fe'$$

$$Z_{12} = fe'$$

$$Z_{21} = fe' + f \times x$$

$$Z_{22} = fe' - f \times x = fe'$$

FIG. 21 TRANSISTOR EQUIVALENT CIRCUIT

The determinant of the open circuited z parameters in Fig. 21 is

The neutralizing circuit is in parallel with the transistor, therefore, if the transistor z parameters are converted to y parameters, they can be added together as shown in Equation 60.

The open circuit impedance equations are

Conversion of the open circuit parameters to their equivalent y parameters is shown in Equation 59.

$$\begin{bmatrix} V \end{bmatrix} = \begin{bmatrix} \frac{Z_{22}}{\Delta Z} & -\frac{Z_{12}}{\Delta Z} \\ -\frac{Z_{21}}{\Delta Z} & \frac{Z_{21}}{\Delta Z} \end{bmatrix}$$

(59)

The array for the short circuit admittance parameters of the neutralizing network and transistor is

The doterminant of the array is

The output impedance with a generator admittance equal to  $y_{\rm ff}$  ( $y_{\rm ff} = 1/R_{\rm ff}$ ) is

$$\frac{Z_{0} = \frac{y''' - y_{0}}{\Delta y'' + y_{0}^{2} y_{0}} = \frac{Z f_{0}' + f_{0}'(1 - \alpha) - J \left(\frac{X'}{R_{0}} \left[f_{0}' + f_{0}'(1 - \alpha) + 1 - \Delta\right]\right)}{Z + \frac{f_{0}' + f_{0}'}{R_{0}} + J \frac{f_{0}'}{X_{CN}} - \frac{f_{0}' + f_{0}'(1 - \alpha)}{R_{0}}}$$

where  $R_{R} < X_{cm}$ .

The parameters values are  $r_0$  =13.5,  $r_0$  = 110 ohms.  $c_0 = c_n = 1.5$  pfrds, and  $R_g = 204$  ohms. The resulting value for  $z_0$  is 12.82 - j595 ohms.

# B. SHORT CIRCUIT OUTPUT IMPEDANCE

The open circuit z parameters of the transistor are shown in Equations 57 and 58. Solving for Zo with equal to zero yields

$$Z_0 = \frac{C_2}{I_2} = -\frac{Z_{1Z}Z_{2J}}{Z_{1J}} + Z_{2Z}$$

(63)

Substituting values as in part A the output impedance obtained is 12 - j1610 ohms

An examination of the Equations for  $Z_0$  in part A and B shows the resistive components to be approximately equal and, the capacitance to differ by 11 pfrds.

#### APPENDIX II

# SHORT CIRCUITED INPUT IMPEDANCE DETERMINATION

The equivalent circuit used to determine the input impedance is shown below in Fig. 22.

FIG. 22 TRANSISTOR EQUIVALENT CIRCUIT

When the collector and emitter are shorted the resulting input impedance is

$$X_{c} = \frac{1}{\omega(c_{se} + c_{se})} = 78.1$$

The input impedance calculated from Equation 65 is 486 - j71.5 ohms. The parameter values are given in Appendix I.

# LIBRARY SSW NOV 16 1960 PROPERTY POLLA, NO.

## ATIV

Robert C. McIntyre was born on June 22, 1932, in Brooklyn, New York. He attended parochial grammar school from 1938 to 1946. In 1946 he entered Brooklyn Technical High School, from which he was graduated in 1950.

After completion of high school the author was employed by the Plant Department of the New York Telephone Co. and attended Brooklyn College Evening School until December 26, 1951. On December 26, 1951 he entered the United States Air Force where he attended various electronics schools including Radar and Radio Communications. He served as a Technican and Electronics Instructor, and attended Belleville Junior College Evening School from September 1954 to June 1955. Upon completion of his military obligation he entered Belleville Junior College as a full time student. He transferred to the University of Missouri School of Mines and Metallurgy in September 1956 from which he was graduated in June of 1959 and received the Degree of Bachelor of Science in Electrical Engineering.

In January of 1959 he entered the University of Missouri School of Mines and Metallurgy as a graduate student with an assistantship in the Electrical Engineering Department. He is a member of Eta Kappa Nu, and IRE.