ADVANCED ELECTROMAGNETICS, Vol. 2, No. 1, February 2013

## Assessment of 50%-Propagation-Delay for Cascaded PCB Non-Linear Interconnect Lines for the High-Rate Signal Integrity Analysis

Thomas Eudes<sup>1</sup>\*, Blaise Ravelo<sup>1</sup> and Rabee Al Hayek<sup>2</sup>

<sup>1</sup>IRSEEM, EA 4353, at the graduate School of Engineering ESIGELEC, Av. Galilée, BP 10024,

76801 Saint-Etienne du Rouvray CEDEX, France

Phone: +33 (0)2 32 91 59 71 / Fax: +33 (0)2 32 91 58 59

<sup>2</sup>LeCroy SARL, 19 Avenue de Norvège, 91953 Courtaboeuf, CEDEX, France.

\*corresponding author, E-mail: eudes@esigelec.fr

### **Abstract**

This paper is a special issue from the work presented in the Advanced Electromagnetics Symposium 2012 (AES'12) which presents an enlarged study about the 50-% propagation-time assessment of cascaded transmission lines (TLs). First and foremost, the accurate modeling and measurement technique of signal integrity (SI) for high-rate microelectronic interconnection is recalled. This model is based on the reduced transfer function extracted from the electromagnetic (EM) behavior of the interconnect line RLCG-parameters. So, the transfer function established takes into account both the frequency dispersion effects and the different propagation modes. In addition, the transfer function includes also the load and source impedance effects. Then, the SI analysis is proposed for high-speed digital signals through the developed model. To validate the model understudy, a prototype of microstrip interconnection with  $w = 500 \,\mu\text{m}$  and length  $d = 33 \,\text{mm}$  was designed, simulated, fabricated and tested. Then, comparisons between the frequency and time domain results from the model and from measurements are performed. As expected, good agreement between the S-parameters form measurements and the model proposed is obtained from DC to 8 GHz. Furthermore, a de-embedding method enabling to cancel out the connectors and the probe effects are also presented. In addition, an innovative time-domain characterization is proposed in order to validate the concept with a 2.38 Gbit/sinput data signal. Afterwards, the 50-% propagation-time assessment problem is clearly exposed. Consequently an extracting theory of this propagation-time with first order RC-circuits is presented. Finally, to show the relevance of this calculation, propagation-time simulations and an application to signal integrity issues are offered.

## 1. Introduction

Over the last 50 years, the tremendous growth of the microelectronics industry has lead to an incessant increase of operating frequencies and integration scale densities of the chips and the electronic systems [1]. The combination of

the functional diversification ("More than Moore") and the integration technologies ("More Moore") lead to new EMC challenges in order to make coexisting these micro-systems in restricted environments [1-2]. This arrangement of technologies is the worthwhile and strategic work to target in order to obtain a high value system [2-4]. In addition to this constant increase in density, since the digital systems reach very high data rates, the fidelity of these RF-digital signals must be taken into account by designers [3-6], [11]. In order to preserve the acceptable functioning of modern high speed digital electronics, since the early 1990s, critical requirements on the signal integrity (SI) were established [3], [5-6]. It is widespread that all electronic products have the same configuration, there are drivers that outputting signals to receivers through the interconnects [6]. This statement illustrates that the effects of interconnection lines cannot be neglected [7-8], for integrated circuits (ICs) [9] and PCBs [10-11].

Subsequently, one of the most important degradations in such systems is linked to the interconnection modeling for high-speed applications [1-3], [6], [12]. For this reason, more and more accurate interconnection network models are necessary to balance correctly the signals at different stage of the electronic boards [10-12]. A fast and accurate modeling of PCB TLs (Printed Circuit Boards Transmission Lines) for high-rate digital-mixed signal interconnects has been recently performed [13-14]. Whereas PCBs or TLs are well-known since the early of 1980s [15], some improvements seem to be still required [11] for the better understanding of the physical behavior [16] and the signal integrity forecasting for modern applications [17-22]. Indeed, facing to the widespread microwave theory, the PCB interconnects require faster and more accurate broadband models [18] and measurement techniques [23]. Therefore this field of investigation is extremely attractive, in particular for differential TLs or multilayer TLs [17] and time-domain analysis [24-25]. Undeniably, over the last five years many enhancements about the knowledge of TLs behavior have been highlighted [16-26]. Despite this technical progress, a major issue is inherent to the timedomain prediction [27] and the calibration process [23]. In fact, the de-embedding technique is the critical point in order to accomplish a good agreement with the models [28]. Consequently, the ABCD matrix is one parameter which allows one to explore this bottleneck [17], [29], particularly for estimating the transient responses [25-28]. This statement motivates us to develop simpler and faster models to forecast the transient responses for digital interconnection lines on PCBs to help designers for high-speed applications [13-14], [30]. Moreover, as exposed above, interconnects play an important role in designing modern electronic and microelectronic systems. So the degradations engendered by these interconnects can be partially reduced by the repeaters insertion [31] or completely reduced using the NGD concept as recently introduced [32-35].

Furthermore, since the early 1990s, it has been evidenced that the interconnect delays of high speed digital IC dominate widely gate delays [1]. In telecommunication area, these technological issues can be sources of distortions, asynchronous effects of the transmitted analog signals and erroneous symbols of numerical data. In order to deal with this difficulty, intensive researches for the enhancement of on-chip interconnects have been conducted [36-41]. To estimate the interconnect delay, the most popular method is based on the use of RC-models as introduced by Elmore in 1948 [42-54]. In that case, the propagation delay expression can be established only from the first order approximation of the system transfer function. The main advantage of this model lies on its simplicity and its possibility for fast delay estimation when considering sophisticated signal paths of integrated system. However, its drawback is its drastic high imprecision compared to other high order delay models. It was reported that Elmore model can involve to more than 30-% relative errors [55-57]. For this reason, more accurate approximated second order RLC model with closed form of delay times (propagation-, rise-/fall- and settling- time delays) were developed in [55-57]. Furthermore, as developed in [56-57], authors determine the step unit response of lumped RLC tree networks via second moments of the polynomial transfer function. Then, they deduce the basic characteristics of the transient response (over- or under-damped responses) and propose also the specific expression of 2nd order propagation delay. The main advantage of this 2nd order delay model is the fact that it enables to investigate the signal delay with good accuracy for non-monotone time-domain Furthermore, compared to SPICE-computation, this model can guarantee relative errors lower than 5%.

Propagation delay  $T_{\rm p}$  is one of the fundamental important parameters for the evaluation of the numerical-analogue high-speed system characteristics. This delay plays an important role for the interconnect structure optimization [58]. In fact, the propagation delay can limit the speed or the rate  $f_{\rm max}$  of the operating data as explained by the relation:

$$f_{\text{max}} < \frac{1}{T_p} \,. \tag{1}$$

Till now, the most popular model for estimating the propagation delay was established by Elmore [9], [59-61]. To overcome this technical limitation, in this paper, a modeling method of cascaded system propagation delay is established. To gain a better understanding, this paper is structured in five sections, with the first third sections from the works presented in [70]. Section 2 offers the theoretical approach of extracting the RLCG model of microstrip lines. First of all, the characteristic impedance and the propagation constant including frequency dispersion and propagation modes effects are established in function of the geometrical and physical properties of the interconnect line. Then the overall voltage transfer function for an interconnected electronic system is extracted, including source impedance and load impedance effects. In order to demonstrate the relevance of this model, Section 3 presents frequency- and time-domain investigations performed with an original "omega" shape interconnect line. The validation process will be presented by considering frequency-/time-domains measurements achieved with the innovative improved TDR / TDT (Time-Domain Reflectometry / Time-Domain Transmissiometry) equipment introduced in [62-69]. This allows one to illustrate the evidence of the effects of connectors and the de-embedding process consequences. Subsequently, the trouble in evaluating properly the propagation time is exposed, thus a theory of propagationtime extraction is presented in Section 4. This theoretical study is followed by verification results reported in Section 5. Finally, the last section draws the conclusion of the paper.

## 2. Theoretical approach

This section is structured in two paragraphs. First, we recall the characterization theory of microstrip lines including the extraction method of per unit length parameters R, L, C and G. Then, knowing the RLCG-model of the line, the analytical expressions of the transfer function and the access impedances of the line are introduced in the second paragraph.

# 2.1. Electromagnetic parameters extraction of a single transmission line (TL)

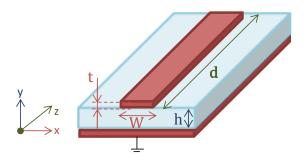

One considers a microstrip TL, of length d, with EM (Electromagnetic) parameters propagation constant  $\gamma(\omega) = \alpha(\omega) + j\beta(\omega)$  (with  $j = \sqrt{-1}$ ) and characteristic impedance,  $Z_c(\omega)$ , defined from physical properties (permittivity  $\varepsilon_r$ , dielectric loss tangent  $tan\delta$ , metal resistivity  $\rho...$ ) and geometrical properties (width w, metallization thickness t and substrate height h) in function of the frequency as sketched on Figure 1.

Figure 1: Geometrical representation of a microstrip TL.

According to the microwave theory [15], the well-known microstrip line synthesis and analysis relations [20], which are used in the EMDS (Electromagnetic Design System) environment of ADS (Advanced Design System) simulation tool, permit to extract the characteristic impedance:

$$Z_c = \frac{\eta_0}{2\pi\sqrt{\varepsilon_{eff}}} \ln \left[ \frac{h \cdot F(w/h)}{w} + \sqrt{1 + \frac{4h^2}{w^2}} \right], \quad (2)$$

where

$$F(w/h) = 6 + (2\pi - 6) \cdot \exp\left[-\left(\frac{30.66h}{w}\right)^{0.7528}\right],\tag{3}$$

$\eta_0$  is the air impedance and  $\varepsilon_{\rm eff}$  is the effective relative permittivity of the medium. In order to reach a better accuracy, this model must be valid a wide frequency bandwidth. For this reason, frequency dispersion effects can be taken into account if the characteristic impedance is considered as follow:

$$Z_{c}(f) = Z_{c} \cdot \sqrt{\frac{\varepsilon_{eff}}{\varepsilon_{r}(f)}} \cdot \frac{\varepsilon_{r}(f) - 1}{\varepsilon_{eff} - 1}, \tag{4}$$

with

$$\varepsilon_r(f) = \varepsilon_r - \frac{\varepsilon_r - \varepsilon_{eff}}{1 + g \cdot \left(\frac{f}{f_p}\right)^2},$$

(5)

$$g = \frac{\pi^2}{12} \cdot \frac{\varepsilon_r - 1}{\varepsilon_{eff}} \cdot \sqrt{\frac{Z_c}{\eta_0}} , \qquad (6)$$

$$f_p = \frac{Z_c}{2 \cdot \mu_0 \cdot h} \,. \tag{7}$$

And by replacing u = w/h,  $\varepsilon_{\text{eff}}$  is given by:

$$\varepsilon_{eff} = \frac{\varepsilon_r + 1}{2} + \frac{\varepsilon_r - 1}{2} \cdot \left(1 + \frac{10}{u}\right)^{-a(u)b(\varepsilon_r)}, \quad (8)$$

$$a(u) = 1 + \frac{1}{49} \ln \left( \frac{u^4 + \left( \frac{u}{52} \right)^2}{u^4 + 0.432} \right) + \frac{1}{18.7} \ln \left( 1 + \left( \frac{u}{18.1} \right)^3 \right), (9)$$

$$b(\varepsilon_r) = 0.564 \cdot \left(\frac{\varepsilon_r - 0.9}{\varepsilon_r + 3}\right)^{0.053}.$$

(10)

In this reminder, it is worthy of note to mention that a particular point of attention should be considered regarding the effective width  $w_{eff}$  of the structure. Indeed, a conformal transformation should be performed with respect of the value of u [15] as follow:

$$w_{eff} = \begin{cases} w + \frac{1.25}{\pi} \cdot \left( 1 + \ln\left(\frac{2h}{t}\right) \right), & \text{if} \quad u < \frac{1}{2\pi} \\ w + \frac{1.25}{\pi} \cdot \left( 1 + \ln\left(\frac{4\pi w}{t}\right) \right), & \text{if} \quad u \ge \frac{1}{2\pi} \end{cases}$$

(11)

One also considers the propagation mode effects, hence the propagation constant in function of the frequency can be written, by denoting c the celerity, as:

$$\gamma(f) = \alpha_c(f) + \alpha_d(f) + j \frac{2\pi f}{c} \sqrt{\varepsilon_r(f)}, \qquad (12)$$

includes the metallic conductor and the dielectric losses respectively given by:

$$\alpha_{c}(f) = 1.38 \cdot \left\{ 1 + \frac{h}{w_{eff}} \cdot \left[ 1 + \frac{1}{\pi} \cdot \ln\left(\frac{2h}{t}\right) \right] \right\} \cdot \frac{R_{s}(f)}{h \cdot Z_{c}(f)} \cdot \frac{32 - \left(\frac{w}{h}\right)^{2}}{32 + \left(\frac{w}{h}\right)^{2}}$$

$$\tag{13}$$

$$\alpha_d(f) = 27.3 \cdot \frac{\varepsilon_r}{\varepsilon_r - 1} \cdot \frac{\varepsilon_{eff} - 1}{\sqrt{\varepsilon_{eff}}} \cdot \frac{\tan(\delta)}{\frac{2\pi f}{\varepsilon_r}}$$

(14)

with

$$R_s(f) = \sqrt{\pi \cdot f \cdot \mu_0 \cdot \rho} \tag{15}$$

For the calculation including the radiating losses, more explicit analytical expressions of the propagation constant real part or the per unit length losses constant  $\alpha(f)$  is presented in [15-16]. Since the RLCG model is associated

with the propagation constant and the characteristic impedance of the transmission line as:

$$\gamma(j\omega)\cdot d = \sqrt{R + j\omega L} \times \sqrt{G + j\omega C} , \qquad (16)$$

$$Z_{c}(j\omega) = \frac{\sqrt{R + j\omega L}}{\sqrt{G + j\omega C}},$$

(17)

one can also extract straightforwardly the RLCG parameters of any interconnect lines by substituting [13]:

$$R(f) = \Re\{\gamma(f) \cdot Z_c(f)\} \cdot d, \qquad (18)$$

$$L(f) = \frac{\Im\{\gamma(f) \cdot Z_c(f)\}}{\omega} \cdot d, \qquad (19)$$

$$C(f) = \frac{\Im\left\{\frac{\gamma(f)}{Z_c(f)}\right\}}{\omega} \cdot d, \qquad (20)$$

$$G(f) = \Re\left\{\frac{\gamma(f)}{Z_c(f)}\right\} \cdot d, \qquad (21)$$

### 2.2. Voltage transfer function determination of a TL

Getting an accurate voltage transfer function (VTF) of an interconnection line yields to determine the domain of validity of the presented equations (2) to (15). The simpler approximation that one can provide is to bound the upper frequency,  $f_{\text{max}}$ , in function of the substrate height [11] as:

$$f_{\text{max}} \le \frac{c}{10 \cdot h \cdot \sqrt{\varepsilon_r}} \,. \tag{22}$$

In this case one can assume that the TL offers quasi-TEM solution for propagating. Hence, the TL is characterized by the following ABCD matrix [15]:

$$[M_{TL}] = \begin{bmatrix} \cosh(\gamma(\omega) \cdot d) & Z_c(\omega) \cdot \sinh(\gamma(\omega) \cdot d) \\ \frac{\sinh(\gamma(\omega) \cdot d)}{Z_c(\omega)} & \cosh(\gamma(\omega) \cdot d) \end{bmatrix}$$

(23)

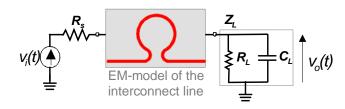

One proposes the real electronic system like two gates connected together through a PCB interconnection line, as depicted on Figure 2 for evaluating the SI.

Figure 2: Circuit diagram representing interconnect line driven by source gate with impedance  $Z_S$  and loaded by input impedance  $Z_L$ .

Since, the SI assessment is based on the equivalent analog bandwidth of a considered input signal. Consequently, the RLCG-interconnection VTF should present the same bandwidth, this becomes challenging especially for high-rate signal due to important rise times [13]. Indeed, the equivalent frequency bandwidth BW for a trapezoidal signal is related to the 10% to 90% rise time,  $t_{r\,90-10}$ , as:

$$BW \approx \frac{0.35}{t_{r_{90-10}}}. (24)$$

As a result, the frequency-domain of validity of the VTF must satisfy relations (22) and (24). So, the overall TL

transfer matrix  $M_{ij}$  including the source  $Z_S$ , and load  $Z_L$ , impedances within the frequency band of interest is given by the matrix product expressed in (25). Afterwards, SI parameters can be established straightforwardly from the impedance matrix and the transient responses [14].

$$\begin{bmatrix} M_{11}(\omega) & M_{12}(\omega) \\ M_{21}(\omega) & M_{22}(\omega) \end{bmatrix} = \begin{bmatrix} 1 & Z_S(\omega) \\ 0 & 1 \end{bmatrix} \times \begin{bmatrix} M_{TL} \end{bmatrix} \times \begin{bmatrix} 1 & 0 \\ \frac{1}{Z_L(\omega)} & 1 \end{bmatrix}$$

(25)

In fact, the VTF denoted  $H(j\omega)$ , the input impedance  $Z_{\rm in}(j\omega)$ , the output impedance  $Z_{\rm out}(j\omega)$  and the transfer impedance  $Z_{\rm T}(j\omega)$  of the considered system of the Figure 2 are respectively summarized in Table 1:

Table 1: Summary of extracted frequency-domain SI parameters.

| SI Element         | Expression                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $H(j\omega)$       | $\frac{1}{\left[\frac{Z_c(j\omega)}{Z_L(j\omega)} + \frac{Z_S(j\omega)}{Z_c(j\omega)}\right] \cdot \sinh(\gamma(j\omega) \cdot d) + \left[1 + \frac{Z_S(j\omega)}{Z_L(j\omega)}\right] \cdot \cosh(\gamma(j\omega) \cdot d)}$                                                                                                                                    |

| $Z_{in}(j\omega)$  | $\frac{\left(Z_{c}^{2}(j\omega)+Z_{L}(j\omega)\cdot Z_{S}(j\omega)\right)\cdot \sinh\left(\gamma(j\omega)\cdot d\right)+Z_{c}(j\omega)\cdot\left(Z_{L}(j\omega)+Z_{S}(j\omega)\right)\cdot \cosh\left(\gamma(j\omega)\cdot d\right)}{Z_{L}(j\omega)\cdot \sinh\left(\gamma(j\omega)\cdot d\right)+Z_{c}(j\omega)\cdot \cosh\left(\gamma(j\omega)\cdot d\right)}$ |

| $Z_{out}(j\omega)$ | $\frac{Z_c(j\omega) \cdot Z_L(j\omega) \cdot \cosh \big( \gamma(j\omega) \cdot d \big)}{Z_L(j\omega) \cdot \sinh \big( \gamma(j\omega) \cdot d \big) + Z_c(j\omega) \cdot \cosh \big( \gamma(j\omega) \cdot d \big)}$                                                                                                                                            |

| $Z_T(j\omega)$     | $\frac{Z_c(j\omega) \cdot Z_L(j\omega)}{Z_L(j\omega) \cdot \sinh(\gamma(j\omega) \cdot d) + Z_c(j\omega) \cdot \cosh(\gamma(j\omega) \cdot d)}$                                                                                                                                                                                                                  |

## 3. Frequency- and time-domain investigations

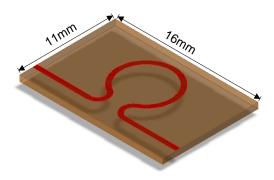

As concrete proof-of-concept, the "**omega**" shape microstrip interconnect displayed in Figure 3 was considered and characterized by the TDR/TDT techniques. The equipment used in this experiment applies de-noising algorithms [68] on all the 40-GHz instantaneous bandwidth TDR/TDT traces. This allows performing straightforwardly and accurately the de-embedding of the SMA connectors in [62]. The interconnect-under-test (IUT) presents a width w = 0.5 mm, and a length d = 32.944 mm printed on the FR4-epoxy substrate, of height h = 1.6 mm, having relative permittivity  $\varepsilon_r = 4.4$ . Figure 4 represents the schematic diagram of the circuit tested by considering an interconnection with complex form. This interconnect corresponds to the length of PCB interconnections for mixed-circuit as PLL or clock distribution [69].

Figure 3: Interconnect microstrip line under test.

EM full-wave simulations of the 3-D structure represented by the black box of Figure 4 were performed in the EM design system environment, "Momentum", of ADS microwave/electronic tool. This IUT was also modeled with the method proposed in *Section* 2.

Figure 4: Schematic diagram used for the EM/circuit co-test.

### 3.1. Assessing the de-embedding effects

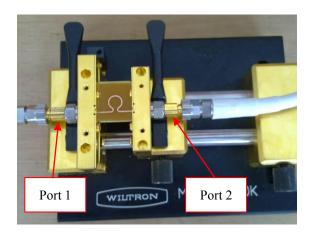

At present time, the de-embedding process of the SPARQ is under consideration. First, the IUT is characterized with using a VNA (Vector Network Analyzer) within the frequency-domain from 100 kHz to 8.5 GHz. The calibration was made in SOLT including port extension (open and short) of the universal test fixture for PCB, as presented by the photograph in Figure 5.

Figure 5: Universal test fixture used for the IUT characterization

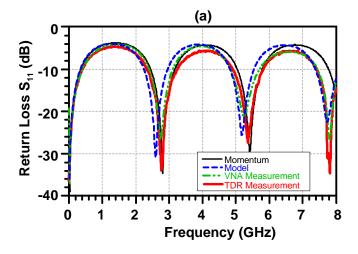

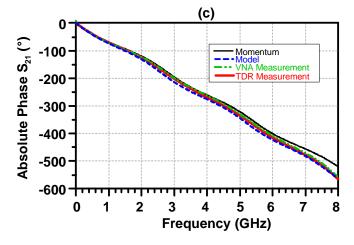

Afterwards, comparison was made with the SPARQ measurement in the time-domain for de-embedding ports 1 and 2. The ports are de-embedded via an algorithm that uses S-parameter measurement, and thus the S-parameters for these components must be known prior to the time of measurement. Hence, SPARQ calculates first the gatedport's S-parameters and then uses them in de-embedding connectors [62, 63]. Table 2 proposes the comparison between the time delays engendered by the connectors obtained from VNA with port extension (SOLT calibration) and TDR/TDT measurement performed with the SPARQ. Then, the S-parameters were also obtained with the SPARO measurement within the time-domain including the "gating" process for de-embedding connectors [62-63], [68]. Hereafter, magnitude of the  $S_{11}$  (a),  $S_{21}$  (b) and phase of the  $S_{21}$  (c) are offered in Figure 6, from the EM simulation (black continuous curves), the proposed model (blue dashed curves), the VNA measurement (green dashed curves) and the SPARQ measurement (red continuous curves).

Table 2: Port extension for de-embedding connectors.

| Port   | VNA     | SPARQ |

|--------|---------|-------|

| Port 1 | 91.4 ps | 90 ps |

| Port 2 | 90.5 ps | 89 ps |

Figure 6: Comparisons of  $S_{11}$ -amplitude (a) and  $S_{21}$ -amplitude (b) and  $S_{21}$ -phase (c) from the EM model obtained from momentum, the developed model, the VNA measurement and the TDR/TDT measurement.

#### 3.2. Application to the signal integrity forecasting

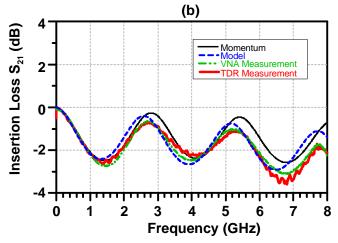

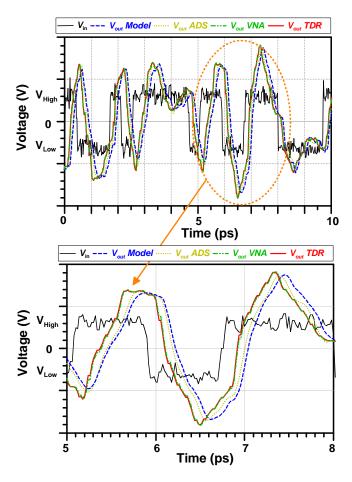

Using the SI Studio feature, a noisy digital-mixed input  $v_{in}$  with 2.38-Gbit/s rate and 42-ps rise-time was simulated. Then, in order to emulate SI parameters degradation by considering  $R_s = 20 \Omega$ ,  $R_L = 500 \Omega$  and  $C_L = 2 \text{ pF}$ , the Virtual-Probing was performed [44].

Figure 7: Comparison between the different techniques for a NRZ noisy 2.38 Gpbs input signal.

Indeed, the SI Studio capability allows one to forecast the transient response of the system as shown by Figure 7. In addition, comparisons were made between the transient responses obtained from SI Studio with the VNA (green dashed curves) and the SPARQ measurements (red continuous curves) and between the simulations obtained from the developed model (blue dashed curves) and from ADS (ocher dashed curves). An excellent correlation was found between the VNA results and the SPARQ measurements that give evidence of the de-embedding method efficiency. In addition a very good agreement is established between the developed theoretical model and the measurements.

A major issue in signal integrity is inherent to the accurate assessment of the 50%-propagation time. Indeed, this latter is linked to the group delay of the system which evolves considerably in a wide frequency band. To manage this problem some complicated numerical approaches exist, but this difficulty increases when one considers cascaded transmission lines.

## 4. Theoretical extraction of the propagation-time

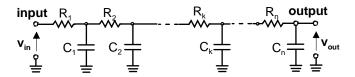

For the complex structures composed of different systems in cascade as the circuit network depicted in Figure 8, the sum of the Elmore propagation delay is generally used [44-47]:

$$T_p = \sum_{k=1}^n R_k \cdot C_k \ . \tag{26}$$

But this relation is susceptible to generate a relative error higher than 35 % [50][56-57].

Figure 8: RC-network composed of n-cells in cascade.

It is well-known that the voltage transfer function (VTF) of linear circuits can be expressed as:

$$G_n(s) = \frac{1}{1 + \sum_{k=1}^{n} a_k \cdot s^k},$$

(27)

In this case, the Elmore model propagation delay induced by this system is written as [42]:

$$T_{pElmore} = a_1. (28)$$

As argued above this expression present a very high inaccuracy [50][56-57], so, in the next paragraphs, we will develop mathematical expressions enabling to realize more precise value of propagation delay associated to more generalized systems.

## 4.1. Transfer function modeling of cascaded RC-network

This subsection focus is on the modeling of the RC network introduced in Figure 8 for  $k = \{1...n\}$ . Being given that this lumped network is a linear circuit, its transfer equation should be governed also by a linear differential equation. This finding leads us to suppose that the elements of the ABCD-matrix:

$$[T_n(s)] = \begin{bmatrix} T_{1\,1,n}(s) & T_{1\,2,n}(s) \\ T_{2\,1,n}(s) & T_{2\,2,n}(s) \end{bmatrix},$$

(29)

as polynomial expressions having real coefficients. So that, the two first elements  $T_{1,n}(s) = A_n(s)$  and  $T_{1,n}(s) = B_n(s)$  can be written as:

$$A_n(s) = 1 + \sum_{k=1}^{n} a_k \cdot s^k , \qquad (30)$$

$$B_n(s) = \sum_{k=0}^n b_k \cdot s^k , \qquad (31)$$

with  $a_k$  and  $b_k$  are real coefficients. For n = 1, one takes the initial value:

$$A_1(s) = 1 + R_1 \cdot C_1 \cdot s \,, \tag{32}$$

$$B_1(s) = R_1. (33)$$

For  $k = \{1,...,n\}$ , The whole ABCD-matrix can be determined with the successive matrix product [71]:

$$[T_{k+1}(s)] = [T_k(s)] \cdot \begin{bmatrix} 1 + R_{k+1} \cdot C_{k+1} \cdot s & R_{k+1} \\ C_{k+1} \cdot s & 1 \end{bmatrix}, \tag{34}$$

with

$$[T_1(s)] = \begin{bmatrix} 1 + R_1 \cdot C_1 \cdot s & R_1 \\ C_1 \cdot s & 1 \end{bmatrix}.$$

(35)

The coefficients  $a_k$  and  $b_k$  can be determined easily via substitutions of expressions (30) and (31) into relation (34). This yields the following iterative relations enabling the calculation of three first coefficients corresponding to  $a_k(l)$  and  $b_k(l)$  for  $l = \{0, 1, 2\}$ . So, by identification of  $T_{11,n}(s)$ -coefficients, the following expressions are established [71]:

$$a_{k+1}(1) = \begin{cases} R_1 \cdot C_1 & \text{if} \quad k = 0\\ a_k(1) + C_k \cdot b_k(0) + R_k \cdot C_k & \text{if} \quad k \ge 1 \end{cases}, \tag{36}$$

$$a_{k+1}(2) = \begin{cases} 0 & \text{if } k = 0\\ a_k(2) + R_k \cdot C_k \cdot a_k(1) + C_k \cdot b_k(1) & \text{if } k \ge 1 \end{cases}, (37)$$

The same analysis applied to the  $T_{12,n}(s)$  -coefficients permits to demonstrate the following expressions:

$$b_{k+1}(0) = \begin{cases} R_1 & \text{if} & k = 0\\ b_k(0) + R_k & \text{if} & k \ge 1 \end{cases}$$

(38)

$$b_{k+1}(1) = \begin{cases} 0 & if \quad k = 0 \\ b_k(1) + R_k \cdot a_k(1) & if \quad k \ge 1 \end{cases}$$

(39)

$$b_{k+1}(2) = \begin{cases} 0 & \text{if } k = 0 \\ R_k \cdot a_k(2) + b_k(2) & \text{if } k \ge 1 \end{cases}$$

(40)

By using this polynomial characteristic function, in the next section, we will evaluate the propagation delay for the highorder linear systems.

## 4.2. Propagation delay modeling of first order cascaded systems

For the better illustration, knowing the real constants  $\tau_a$  and  $\tau_b$ , one assigns the hereafter elementary transfer function:

$$G_a(s) = \frac{1}{1 + \tau_a \cdot s},\tag{41}$$

and

$$G_b(s) = \frac{1}{1 + \tau_h \cdot s} \,. \tag{42}$$

For the sake of simplification, the following 50%-propagation delays are considered:

$$\begin{cases} T_{p\alpha} = \tau_a, T_{p\beta} = \tau_b & if \quad \tau_a < \tau_b \\ T_{p\beta} = \tau_a, T_{p\alpha} = \tau_b & if \quad \tau_b < \tau_a \end{cases}$$

(43)

So that one denotes  $\lambda$  the real constant higher 1 given by:

$$\lambda = \frac{T_{p\beta}}{T_{p\alpha}} \quad , \tag{44}$$

One demonstrates mathematically that if  $\lambda \le 4$ , the 50%-propagation delay associated to the cascaded system with transfer function  $G(s) = G_a(s) \cdot G_b(s)$  is defined as:

$$T_{p} = 0.41 \cdot T_{p\alpha} \left( e^{\sqrt{\lambda}} + \lambda \cdot e^{\frac{1}{\sqrt{\lambda}}} \right). \tag{45}$$

In the contrary case  $\lambda > 4$ , it is expressed as follows:

$$T_{p} = \frac{\lambda \cdot \ln\left(\frac{2 \cdot \lambda}{\lambda - 1}\right)}{\ln 2} \cdot T_{p\alpha} \,. \tag{46}$$

To verify the effectiveness of this theoretic concept, in the next section, validation results are proposed.

## 5. Application to the analysis of the SI issues

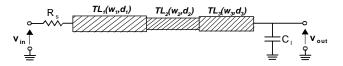

Up to certain frequency bandwidth, the microstrip interconnect circuit depicted in Figure 9 can be assumed as an RC-network cascaded.  $R_S$  and  $C_L$  represent respectively the source resistance and the load capacitance.

Figure 9: Microstrip lines in cascade.

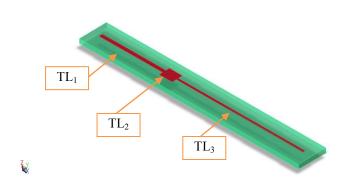

Let us consider the structure as presented above having the characteristic summarized in Table 3 and depicted on Figure 10. The physical dimensions of the interconnections are printed on the FR4-substrate (relative permittivity  $\varepsilon_r = 4.4$  and height  $h = 500 \ \mu m$ ). By applying the modeling method introduced in [13] and [70] one evaluates the per unit length parameters at 7 GHz shown in Table 3.

Figure 10: Microstrip lines in cascade understudy.

Table 3: Parameters of the interconnect microstrip line under consideration.

| TL     | w (mm) | d (mm) | $R_{\rm U}$ $(\Omega.m^{-1})$ | C <sub>U</sub> (pF.m <sup>-1</sup> ) |

|--------|--------|--------|-------------------------------|--------------------------------------|

| $TL_1$ | 0.5    | 10     | 296.46                        | 54.40                                |

| $TL_2$ | 1.5    | 2.0    | 203.04                        | 83.96                                |

| $TL_3$ | 0.3    | 20     | 345.56                        | 47.05                                |

By considering each elementary interconnect lines by the following characteristic impedance:

$$Z_c(s) = \sqrt{R_u/(C_u \cdot s)} , \qquad (47)$$

and propagation constant:

$$\gamma(s) = \sqrt{R_u \cdot C_u \cdot s} \ , \tag{48}$$

the corresponding m ABCD matrix of the m-th interconnect line, denoted  $[TL_m]$ , where here  $m = \{1,2,3\}$ , is given by:

$$[TL_{m}(s)] = \begin{bmatrix} \cosh(\gamma_{m}(s) \cdot d_{m}) & Z_{c_{m}}(s) \cdot \sinh(\gamma_{m}(s) \cdot d_{m}) \\ \frac{\sinh(\gamma_{m}(s) \cdot d_{m})}{Z_{c_{m}}(s)} & \cosh(\gamma_{m}(s) \cdot d_{m}) \end{bmatrix}.$$

(49)

By taking into consideration the maximum frequency bandwidth of a digital signal  $v_{\rm in}$ , any transmission lines m can be modeled by  $N_{\rm m}$  RC-circuits if  $N_{\rm m}$  respects the following condition:

$$N_m \ge \frac{d_m \cdot f_{\text{max}} \cdot \sqrt{\varepsilon_{\text{reff}_m}}}{0.035 \cdot c} \,. \tag{50}$$

Thus, in the presented case the ABCD matrix of each transmission line m will be given by:

$$[TL_{m}(s)] \approx \begin{bmatrix} 1 + \frac{R_{u} \cdot C_{u} \cdot s \cdot d_{m}}{N_{m}} & \frac{R_{u} \cdot d_{m}}{N_{m}} \\ \frac{C_{u} \cdot s \cdot d_{m}}{N_{m}} & 1 \end{bmatrix}^{N_{m}} . \tag{51}$$

So the overall matrix denoted  $M_{TT}$ , of the whole system presented in Figure 9, can be considered as:

$$[M_{TT}(s)] \approx \begin{bmatrix} 1 & R_S \\ 0 & 1 \end{bmatrix} \times \begin{bmatrix} \prod_{m=1}^{m=3} [TL_m(s)] \end{bmatrix} \times \begin{bmatrix} 1 & 0 \\ C_L \cdot s & 1 \end{bmatrix}.$$

(52)

By using this relation, the two different length topologies of the structure presented in Figure 10 were studied. The number of cells characterizing each  $TL_{\rm m}$  by considering a trapezoidal input signal having 50ps rise-time is given below by Table 4:

Table 4: Number of elementary cells for  $d_m$  length in the case 1 and in the case 2.

|   | Case 1                |                  | Case 2                |                  |

|---|-----------------------|------------------|-----------------------|------------------|

| m | $d_{\rm m}({\rm mm})$ | $N_{\mathrm{m}}$ | $d_{\rm m}({\rm mm})$ | $N_{\mathrm{m}}$ |

| 1 | 10                    | 12               | 1.0                   | 2                |

| 2 | 2.0                   | 3                | 0.2                   | 1                |

| 3 | 20                    | 24               | 2.0                   | 3                |

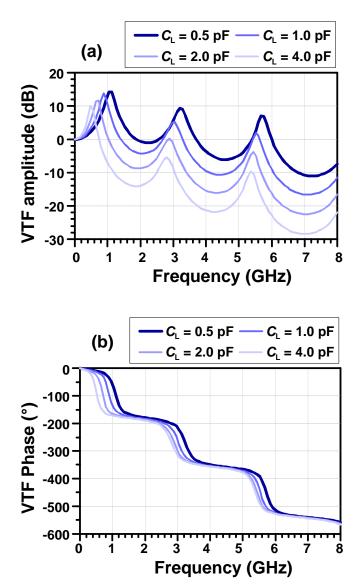

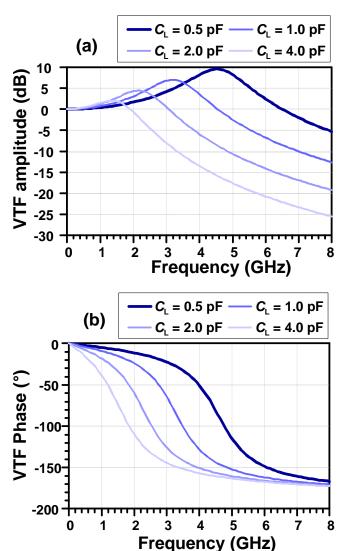

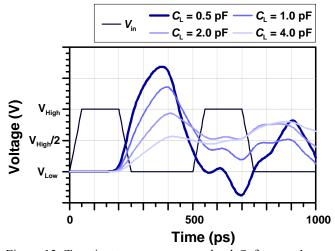

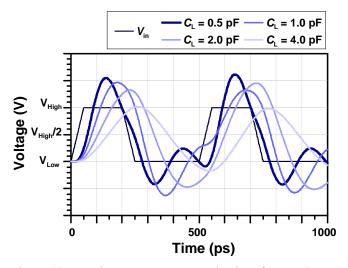

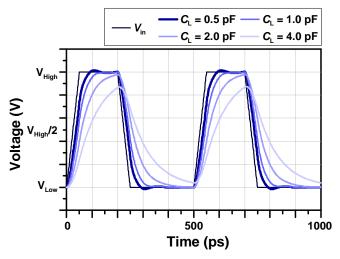

First, the VTF of the whole system was simulated using ADS with the microstrip TL model. By varying  $C_L = \{0.5, 1.0, 2.0, 4.0\}$  pF the magnitude (a) and the absolute phase (b) of the VTF is depicted on Figure 11 for case 1 and on Figure 12 for case 2. Then the transient responses were also simulated in the ADS environment by varying  $C_L$  for case 1 (Figure 13) and case 2 (Figure 14). Finally the 50%-propagation time calculated from the described model was compared with the Elmore one and the equivalent RC-model of the TLs in SPICE (Figure 15). Results, including relative errors, are summarized in Table 5 to Table 8.

Figure 11: Frequency responses versus load  $C_L$  for the magnitude (a) and the phase (b) of the VTF for case 1.

Figure 12: Frequency responses versus load  $C_L$  for the magnitude (a) and the phase (b) of the VTF for case 2.

Figure 13: Transient responses versus load  $C_L$  for case 1.

Figure 14: Transient responses versus load  $C_L$  for case 2.

Figure 15: RC-SPICE Transient responses versus load  $C_L$  for case 2.

Table 5: Comparison of the 50%-propagation delay computed with SPICE and calculated with the proposed model the Elmore one versus load  $C_L$  for the case 1.

|                 | ADS                | SPICE RC-        | Model              | Elmore           |

|-----------------|--------------------|------------------|--------------------|------------------|

| $C_{ m L}$ (pF) | $50\% - T_{\rm p}$ | Circuits 50%-    | $50\% - T_{\rm p}$ | $50\%-T_{\rm p}$ |

| (pr)            | (ps)               | $T_{\rm p}$ (ps) | (ps)               | (ps)             |

| 0.5             | 225.2              | 40.0             | 56.17              | 56.15            |

| 1.0             | 244.6              | 47.0             | 71.51              | 71.31            |

| 2.0             | 260.1              | 58.0             | 102.0              | 101.6            |

| 4.0             | 270.2              | 72.0             | 162.8              | 162.2            |

Table 6: Relative error between the 50%-propagation delay computed with the proposed model and the Elmore versus load  $C_{\rm L}$  for the case 1.

| $C_{\rm L}({ m pF})$ | Model Relative<br>Error (%) | Elmore Relative<br>Error (%) |

|----------------------|-----------------------------|------------------------------|

| 0.5                  | 74.9                        | 75.0                         |

| 1.0                  | 70.7                        | 70.8                         |

| 2.0                  | 60.7                        | 60.9                         |

| 4.0                  | 39.7                        | 39.9                         |

Table 7: Comparison of the 50%-propagation delay computed with SPICE and calculated with the proposed model and the Elmore one versus load  $C_L$  for the case 2.

|                  | ADS                  | SPICE RC-        | Model                | Elmore             |

|------------------|----------------------|------------------|----------------------|--------------------|

| $C_{\rm L}$ (pF) | $50\%$ - $T_{\rm p}$ | Circuits 50%-    | $50\%$ - $T_{\rm p}$ | $50\% - T_{\rm p}$ |

| (pr)             | (ps)                 | $T_{\rm p}$ (ps) | (ps)                 | (ps)               |

| 0.5              | 52.1                 | 13.0             | 13.92                | 13.91              |

| 1.0              | 71.3                 | 21.0             | 24.44                | 24.43              |

| 2.0              | 97.1                 | 32.1             | 44.46                | 44.45              |

| 4.0              | 120.6                | 51.1             | 87.52                | 87.51              |

Table 8: Relative error between the 50%-propagation delay computed with the proposed model and the Elmore one versus load  $C_L$  for the case 2.

| $C_{\rm L}({ m pF})$ | Model Relative<br>Error (%) | Elmore Relative<br>Error (%) |

|----------------------|-----------------------------|------------------------------|

| 0.5                  | 73.2                        | 73.3                         |

| 1.0                  | 65.7                        | 65.7                         |

| 2.0                  | 54.2                        | 54.2                         |

| 4.0                  | 27.4                        | 27.4                         |

## 6. Conclusions

This paper reviews a modeling method of microstrip interconnections with reduced VTF. The theoretical analyses of the interconnections are recalled. Then, basic expressions of the VTF and access impedances including the driven gate and gate load are established. In order to validate the model established, a particular shape microstrip interconnect was characterized, designed and measured. Investigations both with frequency- and time-domain equipments were achieved in order to characterized PCB-interconnects. The de-embedding technique efficiency of the SPARQ Signal Integrity Network Analyzer was also exposed. The potential use for signal integrity forecasting was clearly shown. An excellent agreement was found between modern and complicate electronic simulation tools and the SI studio and Virtual-Probing environments from SPARQ measurements.

In addition, the interest of developed de-embedding technique can be applied to investigations microelectronic systems, as well bounding wires or lead frame effects compensation. In the continuation of these works, the 3D interconnect coupling in-package effects will be investigated.

The dilemma of assessing the 50%-propagation delay in high-order non-linear interconnects was shown. The role played by the inductive part of transmission line is really important rather than the pure RC-circuit assumption especially for microelectronic interconnects. Numerical modeling of interconnects is a good way to achieve the calculation of SI parameters and reach the existing polynomial theories in complex transfer function. Furthermore, the accurate assessing of 50%-propagation time, rise-time and attenuation by a signal integrity model is necessary to design the new innovative equalization technique introduced [32-35], [71].

## Acknowledgements

These research works have been implemented within the frame of the "Time Domain Electromagnetic Characterization and Simulation for EMC" (TECS) project which is part-funded by the Haute-Normandie Region and the ERDF via the Franco-British INTERREG IVA program. Singular acknowledgments are made to LeCroy SARL for the measurements with the SPARQ that were performed and for supplied the expertness in time-domain deembedding techniques.

## References

- [1] International Technology Roadmap for Semiconductors Update Overview, 2011. [Online]. Available: <a href="http://www.itrs.net/">http://www.itrs.net/</a>

- [2] B. Bottom, "Assembly and Packaging White Paper on System Level Integration," *ITRS white papers*, 2009. Available [Online]: <a href="http://www.itrs.net/papers.html">http://www.itrs.net/papers.html</a>

- [3] F. Jun, Y. Xiaoning, J. Kim, B. Archambeault, and A. Orlandi, "Signal Integrity Design for High-Speed Digital Circuits: Progress and Directions," *IEEE Trans. EMC*, Vol. 52, No. 2, pp. 392-400, May 2010.

- [4] J. F. Buckwalter, "Predicting Microwave Digital Signal Integrity," *IEEE Trans. Advanced Packaging*, Vol. 32, No. 2, pp. 280-289, May 2009.

- [5] J. Kim, and E. Li, "Special Issue on PCB Level Signal Integrity, Power Integrity, and EMC," *IEEE Trans. EMC*, Vol. 52, No. 2, pp. 246-247, May 2010.

- [6] E. Bogatin, "Essential Principles of Signal Integrity," *IEEE Microwave Magazine*, Vol. 12, No. 5, Aug. 2011.

- [7] Y. I. Ismail, and E. G. Friedman, "Effects of Inductance on the Propagation, Delay and Repeater Insertion in VLSI Circuits", *IEEE Trans. VLSI Systems*, Vol. 8, No. 2, pp. 195-206, Apr. 2000.

- [8] A. Deutsch, G.V. Kopcsay, P. Restle, G. Katopis, W. D. Becker, H. Smith, P. W. Coteus, C. W. Surovic, B. J. Rubin, R. P. Dunne, T. Gallo, K. A. Jenkins, L. M. Terman, R. H. Dennard, G. A. Sai-Halasz, and D. R. Knebel, "When are transmission-line effects important for on-chip interconnection", *IEEE Trans. MTT*, Vol. 45, No. 10, pp. 1836-1846, Oct. 1997.

- [9] M. Celik, L. Pileggi, and A. Odabasioglu, *IC Interconnect Analysis*, Kluwer Academic Publisher, Dordrecht, Germany, 2002.

- [10] M. Zolog, and D. Piticã, "Controlling the Signal Integrity through the Geometry of the Microstrip on the Digital PCBs," *Electronic System-Integration Technology Conference (ESTC)*, Berlin, Germany, Sep. 2010.

- [11] F. W. L. Kung and H. T. Chuah, "System Modeling of High-Speed Digital Printed Circuit Board Using SPICE," *Progress In Electromagnetics Research*, Vol. 20, pp. 179-211, 1998.

- [12] T. Granberg, "Handbook of Digital Techniques for High Speed Design," Pentrice Hall Modern Semiconductor Design Series, Ed. by Pentrice Hall, Chapter 1, pp. 3-16, 2004.

- [13] T. Eudes, B. Ravelo, and A. Louis, "Transient Response Characterization of the High-Speed Interconnection RLCG Model for the Signal Integrity Analysis," *PIER J.*, Vol. 112, 183-197, Jan. 2011.

- [14] T. Eudes, B. Ravelo, and A. Louis, "Experimental validations of a simple PCB interconnect model for high-rate signal integrity," *To be published in IEEE Trans. EMC. doi: 10.1109/TEMC.2011.2165216*, pp. 1-8, Sept. 2011.

- [15] G. L. Matthaei, L. Young, and E. M. T. Jones, *Microwave Filters, Impedance Matching and Coupling Structures*, Artech House Microwave Library, Norwood, MA, Ed. by Artech House, 1980.

- [16] P. G. Huray, *The Foundations of the Signal Integrity*, Ed. by Wiley and Sons Inc., Hoboken, NJ, 2010.

- [17] J. Cho, E. Song, H. Kim, S. Ahn, J. S. Pak, Ji. Kim and Jo. Kim "Mixed-Mode ABCD Parameters: Theory and Application to Signal Integrity Analysis of PCB-Level Differential Interconnects," *IEEE Trans. EMC*, Vol. 53, No. 3, pp.1-9, Aug. 2011.

- [18] J. H. Kim, D. Oh, and W. Kim, "Accurate Characterization of broadband Multiconductor Transmission Lines for High-Speed Digital Systems," *IEEE Trans. Advanced Packaging*, Vol. 33, No. 4, pp. 857-867, Nov. 2010.

- [19] A. Koul, P. K. R. Anmula, M. Y. Koledintseva, J. L. Drewniak and S. Hinaga, "Improved Technique for Extracting Parameters of Low-Loss Dielectrics on Printed Circuit Boards," in Proc. of *IEEE EMC Symp.*, pp. 191-196, Aug. 2009.

- [20] K. S. R. Krishna, J. L. Narayana and L. P. Reddy, "ANN Models for Microstrip Line Synthesis and Analysis," *Int. J. Elect. Syst. Sci. Eng.*, Vol. 1, pp.196-200, 2008.

- [21] J. Lilja, R. Mäkinen, V. Pynttäri, P. Mansikkamäki, and M. Kivikoski, "Application of Thin-Film RCLG Model for the Modeling of Inkjet Printed Microstrip Lines", in Proc. of *12*<sup>th</sup> Workshop on SPI, pp. 1-4, May 2008.

- [22] Y. Shlepnev, "Modeling Frequency-Dependent Conductor Losses and Dispersion in Serial Data Channel Interconnects," *Simberian Inc.*, 2007. Available [Online]: http://www.simberian.com

- [23] M. Resso, and E. Bogatin, *Signal Integrity Characterization Techniques*, Int. Engineering Consortium, Ed. by IEC Publications, 2009.

- [24] N. Nakhla, M. Nakhla, and R. Achar, "A General Approach for Sensitivity Analysis of Distributed Interconnects in the Time Domain," *IEEE Trans. MTT*, Vol. 59, No. 1, pp. 46-55, Jan. 2011.

- [25] S. Roy, and A. Dounavis, "RLC Interconnect Modeling using Delay Algebraic Equations," in Proc. of *IEEE CAS Workshop*, Dallas, CO, Oct. 2009.

- [26] S. Gupta, A. Parsa, E. Perret, R. V. Snyder, R. J. Wenzel and C. Caloz, "Group-Delay Engineered Noncommensurate Transmission Line All-Pass Network for Analog Signal Processing," IEEE Trans. MTT, Vol. 58, No. 9, pp. 2392-2407, Sept. 2010.

- [27] J. L. Naredo, J. A. Gutérrez, F. A. Uribe, J. L. Guardado and V. H. Ortiz, "Frequency Domain Methods for Electromagnetic Transient Analysis," in Proc. of *IEEE Power Engineering General Meeting*, pp. 1-7, June 2007.

- [28] P. Wittwer and P. J. Pupalaikis, "A general Closed-Form Solution to Multi-Port Scattering Parameter Calculations," in Proc. of the 72<sup>nd</sup> ARFTG Microwave. Meas. Symp., pp. 137-143, Dec. 2008

- [29] D. A. Frickey, "Conversions Between S, Z, Y, h, ABCD and T Parameters which are Valid for Complex Source and Load Impedances," *IEEE Trans. MTT*, Vol. 42, No. 2, pp. 205-216, Feb. 1994.

- [30]B. Ravelo and T. Eudes, "Fast estimation of RL-loaded microelectronic interconnections delay for the signal integrity prediction," *To be published in Int. J. Numer. Model. DOI: 10.1002/jnm.838.*

- [31] V. Adler, E. G. Friedman, "Repeater Design to Reduce Delay and Power in Resistive Interconnect," *IEEE Trans. on CAS II*, Vol. 45, No. 5, May 1998.

- [32]B. Ravelo, A. Perennec, and M. Le Roy, "New Technique of Inter-Chip Interconnect Effects Equalization with Negative Group Delay Active Circuits", *VLSI*, Chap. 20, INTECH Book, Ed. by Z. Wang, 409-434, Feb. 2010.

- [33]B. Ravelo, A. Perennec, and M. Le Roy, "Experimental Validation of the RC-Interconnect Effect Equalization with Negative Group Delay Active Circuit in Planar Hybrid Technology," in Proc. of *13th IEEE Workshop SPI*, Strasbourg, France, May 2009.

- [34] B. Ravelo, A. Pérennec, M. Le Roy, and Y. Boucher, "Active Microwave Circuit with Negative Group Delay," *IEEE MWC Lett.*, Vol. 17, No. 12, pp. 861-863, Dec. 2007.

- [35] T. Eudes and B. Ravelo, "Cancellation of Delays in the High-Rate Interconnects with UWB NGD Active Cells," *Applied Physics Research*, Vol. 3, No. 2, Nov. 2011.

- [36] J. Cong, L. He, C.K. Koh, and P.H. Madden, "Performance Optimization of VLSI Interconnect Layout," *Integration VLSI J.*, Vol. 21, No. 1-2, Nov. 1996, pp. 1-94.

- [37] L. Xiao-Chun, M. Jun-Fa, and T. Min, "High-speed Clock Tree Simulation Method Based on Moment Matching," in *2005 Proc. PIERS*, Hangzhou (China), Vol. 1, No. 2, pp. 142-146.

- [38] L. Hungwen, S. Chauchin and L. J. Chien-Nan, "A Tree-Topology Multiplexer for Multiphase Clock System," *IEEE Tran. CAS I*, Vol. 56, No. 1, Feb. 2009, pp. 124-131.

- [39] N. Rakuljic and I. Galton, "Tree-Structured DEM DACs with Arbitrary Numbers of Levels," *IEEE Tran. CAS I*, Vol. 52, No. 2, Feb. 2010, pp. 313-322.

- [40] G. F. Bo and P. Ampadu, "On Hamming Product Codes With Type-II Hybrid ARQ for On-Chip Interconnects," *IEEE Tran. CAS I*, Vol. 56, No. 9, Sep. 2009, pp. 2042-2054.

- [41] M. Voutilainen, M. Rouvala, P. Kotiranta and T. Rauner, "Multi-Gigabit Serial Link Emissions and Mobile Terminal Antenna Interference," *13th IEEE Workshop on SPI*, Strasbourg (France), May 2009.

- [42] W. C. Elmore, "The transient response of damped linear networks," *J. Appl. Phys.*, Vol. 19, Jan. 1948, pp. 55-63.

- [43] L. Wyatt, "Circuit Analysis, Simulation and Design. North-Holland," *The Netherlands : Elsiever Science*, 1978.

- [44] Jr. P. Penfield and J. Rubinstein, "Signal delay in RC tree networks," in 1981 Proc. of Caltech Conf. on VLSI, pp. 269-283.

- [45] J. Rubinstein, Jr. P. Penfield, and M. A. Horowitz, "Signal delay in RC tree networks," *IEEE Trans. CAD*, Vol. 2, No. 3, Jul. 1983, pp. 202-211.

- [46] C. A. Zukowski, "Relaxing bounds for linear RC mesh circuits," *IEEE Trans. CAD*, Vol. 5, Apr. 1986, pp. 305-312.

- [47] P. K. Chan and M. D. F. Schlag, "Bounds on Signal Delay in RC Mesh Networks," *IEEE Trans. CAD*, Vol. 8, Jun. 1989, pp. 581-589.

- [48] M. A. Horowitz, "Timing Models for MOS Pass Networks," in 1983 Proc of IEEE ISCAS, pp. 198-201.

- [49] Jr. J. L. Wyatt, "Signal Delay in RC Mesh Networks," *IEEE Tran. CAS*, Vol. 32, No. 5, May 1985, pp. 507-510.

- [50] Jr. J. L. Wyatt, "Signal Propagation Delay in RC Models for Interconnect," Circuit Analysis, Simulation and Design, Part II: VLSI Circuit Analysis and Simulation, A. Ruchli, ed., Vol. 3 in the series Advances in CAD for VLSI, North-Holland, 1987.

- [51] N. K. Jain, V. C. Prasad and A. B. Bhattacharyyaa, "Delay-Time Sensitivity in Linear RC Tree," *IEEE Trans. CAS*, Vol. 34, No. 4, 1987, pp. 443-445.

- [52] A. C. Deng and Y. C. Shiau, "Generic Linear RC Delay Modeling for Digital CMOS Circuits," *IEEE Tran. CAD*, Vol. 9, No. 4, Apr. 1990, pp. 367-376

- [53] R. Gupta, B. Tutuianu and L. T. Pileggi, "The Elmore delay as a bound for RC trees with generalized input signals," *IEEE Tran. CAD*, Vol. 16, No. 1, 1997, pp. 95-104.

- [54] Y. I. Ismail, E. G. Friedman and J. L. Neves, "Equivalent Elmore Delay for RLC Trees", *IEEE Tran. CAD*, Vol. 19, No. 1, Jan. 2000, pp. 83-97.

- [55] F. R. Awwad, M. Nekili, V. Ramachandran and M. Sawan, "On Modeling of Parallel Repeater-Insertion Methodologies for SoC Interconnects," *IEEE Tran. CAS I*, Vol. 55, No. 1, Feb. 2008, pp. 322-335.

- [56] A. B. Kahng, and S. Muddu, "An Analytical Delay model of RLC interconnects," *IEEE Trans. CAD*, Vol. 16, Dec. 1997, pp. 1507-1514.

- [57] A. Ligocka and W. Bandurski, "Effect of Inductance on Interconnect Propagation Delay in VLSI Circuits", in *Proc. of 8th Workshop on SPI*, 9-12 May 2004, pp. 121-124.

- [58] W. Maichen, "When Digital Becomes Analog-Interfaces in High Speed Test," *Proc. 12th IEEE Workshop on SPI*, Avignon (France), May 2008.

- [59] J. A. Charles, F. Liu, C. V. Kashyap and A. Devgan, "Closed-Form Delay and Slew Metrics Made Easy," *IEEE Tran. CADICAS I*, Vol. 23, No. 12, Dec. 2004, pp. 1661-1669.

- [60] C. V. Kashyap, C. J. Alpert, F. Liu and A. Devgan, "Closed-Form Expressions for Extending Step Delay and Slew Metrics to Ramp Inputs for RC Trees," *IEEE Tran. CADICAS I*, Vol. 23, No. 4, Apr. 2004, pp. 509-516

- [61] C. J. Alpert, F. Liu, C. Kashyap, and A. Devgan, "Delay and Slew Metrics Using the Lognormal Distribution," In *Proc. of the 40th annual Design Automation Conf.*, 2003, pp. 382-385.

- [62] A. Blankman, "De-embedding Gigaprobes® Using Time Domain Gating with the LeCroy SPARQ," *LeCroy SPARQ Application Note*. Available [Online]: <a href="http://www.lecroy.com/sparg/">http://www.lecroy.com/sparg/</a>

- [63] A. Blankman, "LeCroy SPARQ S-Parameter Measurement and Methodology," *LeCroy Technical Brief*, Rev. 3, July 2011. Available [Online]: <a href="http://www.lecroy.com/support/techlib/">http://www.lecroy.com/support/techlib/</a>

- [64] A. Blankman, "SPARQ S-Parameter Measurements with Impulse Response Time Limiting," LeCroy

- Technical Note, Rev. 2, June 2011. Available [Online]: http://www.lecroy.com/support/techlib/

- [65] P. J. Pupalaikis, "SPARQ Dynamic Range," *LeCroy Technical Brief*. Available [Online]: http://www.lecroy.com/support/techlib/

- [66] M. Schnecker, M. Miller and J. Schachner, "Signal Integrity Measurement in High Bit Rate Systems," Presented at *DesignCon2009*, Santa Clara, CA, US, Feb. 2009.

- [67] J. Kenney and P. J. Pupalaikis, "Timing Measurement Problems and Solutions in Source Terminated Memory Systems with Inaccessible Probing Points," in Proc. of *DesignCon2010*, Santa Clara, CA, US, Feb. 2010.

- [68] P. J. Pupalaikis, "Wavelet Denoising for TDR Dynamic Range Improvement," in Proc. of *DesignCon2011*, Santa Clara, CA, US, Feb. 2011.

- [69] "240-Pin PC-6400/PC-5300/PC-4200/PC-3200 DDR2 SDRAM Registered DIMM Design Specification," JEDEC Standard, No. 21C, Rev. 4.04, Jan. 2010. Available [Online]: http://www.jedec.org

- [70] T. Eudes, B. Ravelo and R. Al Hayek, "Fast and Accurate Modeling of PCB Interconnection Lines for High-Rate Signal Integrity Analysis," (Accepted for communication) Proc. of AES 2012, Paris, Apr. 2012.

- [71]B. Ravelo, "Time-domain analysis of microwave pulse compression with NGD circuit", *To be published in International Journal of Communication Engineering Applications (IJCEA)*, IJCEA-TJ-04-68, 2012.