# Simulation of a 0.6 V Wideband CMOS LNA Design Using Forward Body Bias

Jian-Ming Wu\*, Chih-Yu Huang, Cheng-Shong Hong, You-Ruei Jhuang

Department of Electronic Engineering, National Kaohsiung Normal University, Kaohsiung, Taiwan Received 15 May 2019; received in revised form 5 June 2019; accepted 1 July 2019

### **Abstract**

A 0.6-V wideband Low-Noise Amplifier (LNA) design using a 0.18  $\mu$ m CMOS standard process is presented in this paper. An important goal for the design is to achieve wideband under a low supply voltage. The presented LNA design is a three-stage amplifier, which is based on a common gate stage and two common source stages. The common gate stage provides a wideband input matching. The two common source stages provide a flat gain. A forward body bias technique is used to reduce the supply voltage of the wideband LNA. The forward body bias, that is, the body-source voltage ( $V_{BS}$ ) is greater than 0 V, decreases the threshold voltage of the NMOS transistor, achieving the low voltage LNA. The supply voltage that is applied to the wideband LNA is only 0.6 V and the Power Consumption ( $P_{DC}$ ) is 9.24 mW. Simulation results indicate that the gain exceeds 10 dB and the Noise Figure (NF) is below 6.5 dB from 1.62 GHz to 7.02 GHz. The main advantage of the LNA is it's wideband with a low supply voltage.

Keywords: low-noise amplifier (LNA), forward body bias, low voltage, wideband

## 1. Introduction

The Fifth Generation (5G) wireless system will be the major mobile communication technology for information delivery in the near future. The 5G wireless system is a fast network, providing high data rates above 1G bit/s [1]. The 5G wireless system uses a massive Multi-Input Multi-Output (MIMO) technique to achieve high data rates. High data rates require a wide bandwidth. The 5G wireless system uses a carrier aggregation technique to obtain broadband.

A massive MIMO technique is used to increase the data rates of the 5G wireless system. A massive MIMO system consists of multiple antennae phased arrays with a beamforming technique. A massive MIMO system using a beamforming technique scans multiple users at the same time to increase the throughputs of the 5G wireless system. A massive MIMO technique provides a spatial multiplexing and a spatial diversity against multiple path attenuations and reduces noise interferences, which raise the data rates of the 5G wireless system.

In general, a wireless system has a less continuous bandwidth. Therefore, a carrier aggregation technique is used to aggregates discontinuous or continuous carrier components that have different frequency bands to achieve broadband, meeting the requirements of the 5G wireless system. For instance, a discontinuous carrier component has a 20-MHz bandwidth and then aggregating five discontinuous carrier components can obtain a bandwidth of 100 MHz. The characteristic of a carrier aggregation technique is to use discontinuous carrier components that have different frequency bands, implying that a carrier aggregation technique can use fragmented frequency bands to obtain a wide bandwidth.

<sup>\*</sup> Corresponding author. E-mail address: jianmingwu@nknucc.nknu.edu.tw

Broadband considerations require that an RF receiver of the 5G wireless system must have a wide bandwidth. An RF receiver in the 5G wireless system must also have low Power Consumption (PDC) to support long standby times of mobile devices. Operating an RF component at a low supply voltage can substantially reduce the power consumed by 5G receivers. A Low-Noise Amplifier (LNA) is the first component in an RF receiver and is used to amplify an RF signal. An LNA is the first stage in an RF receiver so its Noise Figure (NF) dominates the noise characteristics of the overall receiver.

Proposed approaches to design a wideband LNA include 1) common gate amplifier [2-3], 2) resistive shunt-feedback technique [4], 3) distributed amplifier [5], and 4) balanced amplifier [6]. The common gate amplifier can be done with simplicity but has a poor frequency response. The resistive shunt-feedback technique can greatly increase bandwidth but is not efficient in power consumption. The distributed amplifier provides a good input and output impedance matching, but a large chip area is needed. The balanced amplifier can provide a high gain but is complicated to implement.

Methods have been reported to design an LNA with a low supply voltage. They are summarized to include the: 1) forward body bias technique [7-8], 2) folded cascade technique [9], and 3) current reused technique [10]. The forward body bias technique can be simple to implement but has a leakage current in the body-source junction of a transistor. The folded cascade technique provides high linearity and good isolation but is done with complexity. The current reuse technique is good at the decrease in power consumption but requires a high supply voltage.

The purpose of this work is to design a wideband LNA using the TSMC 0.18 µm CMOS standard process for 5G applications. The common gate technique is used to achieve wideband due to its simplicity. The forward body bias technique is used to reduce a supply voltage because of its simplicity. In this paper, Section 2 presents the circuit design of the wideband LNA. The simulated results are demonstrated in Section 3. Section 4 shows the conclusion of this paper.

# 2. Experimental Details

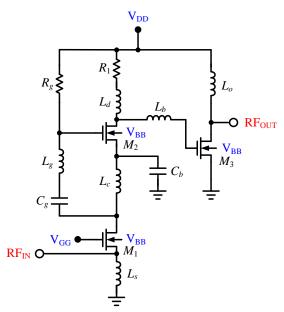

Fig. 1 schematically depicts the circuit of the 0.6-V wideband LNA. The presented LNA design uses a common gate technique and a forward body bias technique [2]. The LNA is a three-stage amplifier. The first stage is a common gate stage, which consists of a transistor  $M_1$ , a source inductance  $L_s$ , and an inductance  $L_c$ . The transistor  $M_1$  is the main active element of the first stage. Since  $L_s$  has a small reactance at a low frequency, the LNA has a small input impedance at a low frequency. At a high frequency, the input impedance of the LNA approximates to  $1/g_{m1}$  where  $g_{m1}$  is the transconductance of the transistor  $M_1$  [2].  $L_c$  can block RF signals from the source of the transistor  $M_2$ . The function of the first stage is to provide a wideband input matching.

The second stage is a common source amplifier. The transistor  $M_2$  is the main amplified element of the second stage.  $L_g$  and  $C_g$  consist of a series resonator. The inductance  $L_d$  is used to increase the gain.  $R_g$  and  $R_1$  are the biasing resistances of the transistors  $M_1$  and  $M_2$ .  $C_b$  is a bypass capacitance. The third stage is also a common source amplifier, which consists of a transistor  $M_3$ , an inductance  $L_b$ , and a drain inductance  $L_o$ .  $R_1$  is also the biasing resistances of the transistor  $M_3$ . The transistor  $M_3$  is the main amplified element of the third stage.  $L_b$  and the gate-source capacitance of the transistor  $M_3$  form a series resonator.  $L_o$  at the drain of the transistor  $M_3$  is used to increase the gain. The second and third stage provides a flat gain.

A forward body bias technique is used to reduce the supply voltage of the wideband LNA. By referring to [11], the threshold voltage  $(V_{th})$  is expressed as

$$V_{th} = V_{t0} + \gamma (\sqrt{2\phi_f - V_{BS}} - \sqrt{2\phi_f}) \text{ (V)}$$

where  $V_{BS}$  presents a body-source voltage,  $V_{t0}$  is a threshold voltage when the  $V_{BS}$  is equaled to 0 V,  $\gamma$  denotes a fabrication-process parameter, and  $\phi_f$  presents physical Fermi potential. A forward body bias, that is,  $V_{BS}$  is greater than 0 V, reduces the threshold voltage of the NMOS transistor, achieving a low supply voltage of the LNA.

Fig. 1 Circuit schematic of 0.6-V wideband LNA

# 3. Layout and Simulation

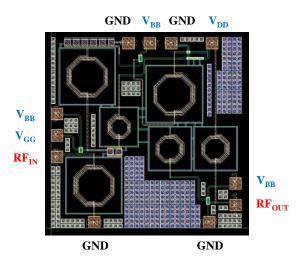

The wideband LNA circuit is designed using the TSMC  $0.18~\mu m$  CMOS foundry process. Fig. 2 shows the chip layout of the LNA RFIC. The chip area is  $1.2~mm \times 1.2~mm$ . It is considered that mutual coupling between the components causes signal interferences. On the periphery of each component, a guard ring is connected to the ground to prevent signals from interfering with each other. A short trace reduces the parasitic elements including resistance, inductance, and capacitance. A mitered trace has a small impedance variation, reducing signal reflection.

Fig. 2 Chip layout of wideband LNA

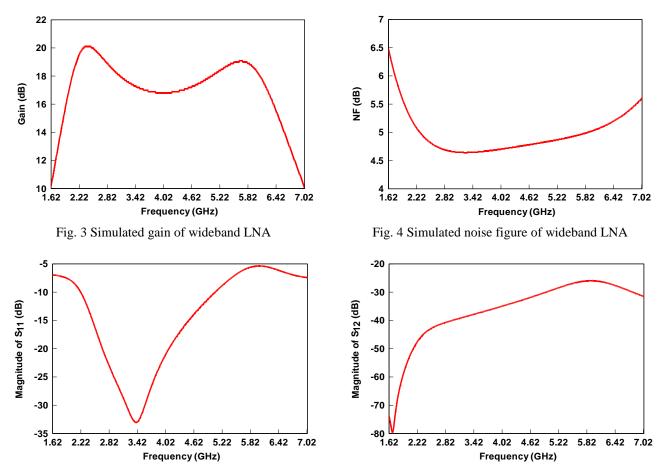

The wideband LNA RFIC is now being fabricated. A supply voltage is 0.6 V and the current consumption is 15.4 mA. Power consumption is calculated by supply voltage multiplying by current consumption, which equals to 9.24 mW. Fig. 3 shows the simulation results of the gain. Fig. 3 shows that the gain exceeds 10 dB from 1.62 GHz to 7.02 GHz. Fig. 4 plots the simulated noise figure. It can be seen that the noise figure is below 6.5 dB from 1.62 GHz to 7.02 GHz. Fig. 5 plots the simulated magnitude of the reflection coefficient seen looking into the RF<sub>IN</sub> port. Fig. 5 shows that the reflection coefficient

magnitude is less than -5.36 dB from 1.62 GHz to 7.02 GHz. Fig. 6 plots the simulated magnitude of  $S_{12}$ , corresponding isolation. Fig. 6 reveals that the magnitude of  $S_{12}$  is below -25.94 dB from 1.62 GHz to 7.02 GHz. Table 1 summarizes the performance merits of this work and compares it with previous proposed wideband LNA designs in [12-18]. The comparison shows that the presented wideband LNA has the lowest supply voltage among the works listed in Table 1.

Fig. 5 Simulated magnitude of the reflection coefficient seen looking into the RFIN port of wideband LNA

Fig. 6 Simulated magnitude of S12 of wideband LNA

| Table 1 Performance summary for this work and comparison with prior works |            |          |         |       |        |          |           |       |

|---------------------------------------------------------------------------|------------|----------|---------|-------|--------|----------|-----------|-------|

| Specification                                                             | This work* | [12]     | [13]    | [14]  | [15]   | [16]     | [17]*     | [18]* |

| Frequency (GHz)                                                           | 1.62-7.02  | 1.3-12.1 | 2.3-9.2 | 2-7   | 0.4-10 | 3.4-11.4 | 3.1-10.6  | 2-10  |

| Maximum gain (dB)                                                         | 20.13      | 8.15     | 9.3     | 13    | 12.4   | 16       | 11.037    | 12.2  |

| Minimum NF (dB)                                                           | 4.65       | 2.5      | 4       | 4.1   | 4.4    | 3.1      | 1.811     | 3.7   |

| S <sub>11</sub> (dB)                                                      | < -5.36    | < -17.5  | < -9.9  | < -17 | <-10   | < -8     | < -1.390  | < -13 |

| S <sub>12</sub> (dB)                                                      | < -25.94   | < -25.8  | < -43   | < -40 | N/A    | < -40    | < -14.265 | N/A   |

| Supply voltage (V)                                                        | 0.6        | 1.2      | 1.8     | 2.5   | 1.8    | 1.8      | 1.2       | 1.8   |

| $P_{DC}$ (mW)                                                             | 9.24       | 10.68    | 9       | 9.3   | 12     | 11.9     | N/A       | 48    |

Table 1 Performance summary for this work and comparison with prior works

Simulated results.

#### 4. Conclusions

A 0.6-V wideband LNA with a forward body bias technique has been designed using the TSMC 0.18  $\mu$ m standard CMOS process. The wideband LNA RFIC achieves that the gain exceeds 10 dB and the noise figure is below 6.5 dB from 1.62 GHz to 7.02 GHz when the supply voltage is only 0.6 V. The main advantage of the LNA is it's wideband with a low supply voltage. Therefore, the LNA can be applied to 5G wireless systems, Internet of Things (IoT), Wireless Sensor Networks (WSN), and automobile electronics.

# Acknowledgment

This work was supported by the Ministry of Science and Technology, Taiwan, under Grant 107-2221-E-017-004. The authors wish to thank the Taiwan Semiconductor Research Institute, Taiwan, for providing the TSMC  $0.18~\mu m$  CMOS foundry service.

# **Conflicts of Interest**

The authors declare no conflict of interest.

## References

- [1] M. Elkholy, S. Shakib, J. Dunworth, V. Aparin, and K. Entesari, "A wideband variable gain LNA with high OIP3 for 5G using 40-nm bulk CMOS," IEEE Microwave and Wireless Components Letters, vol. 28, no. 1, pp. 64-66, January 2018.

- [2] A. Dehqan, E. Kargaran, K. Mafinezhad, and H. Nabovati, "An ultra-low-voltage ultra-low power CMOS UWB LNA using forward body biasing," IEEE International Midwest Symposium on Circuits and Systems, 2012, pp. 266-269.

- [3] J. Y. Lee, H. K. Park, H. J. Chang, and T. Y. Yun, "Low-power UWB LNA with common-gate and current-reuse techniques," IET Microwaves, Antennas & Propagation, vol. 6, no. 7, pp. 793-799, May 2012.

- [4] Y. C. Lin, M. L. Yeh, W. R. Liou, and C. C. Chang, "A tunable 3.9-7.1 GHz CMOS LNA for ultra-wideband wireless communication," International Conference on Communications, Circuits, and Systems, 2007, pp. 1226-1229.

- [5] S. C. Shin, C. S. Lin, M. D. Tsai, K. Y. Lin, and H. Wang, "A low-voltage and variable-gain distributed amplifier for 3.1-10.6 GHz UWB systems," IEEE Microwave and Wireless Components Letters, vol. 16, no. 4, pp. 179-181, April 2006.

- [6] D. M. Pozar, Microwave engineering, 2nd ed. New York: John Willey & Sons, 1998.

- [7] J. M. Wu, Y. T. Lin, and Y. S. Tsai, "A sub-mW CMOS LNA for WSN applications," Asia Pacific Microwave Conference, 2012, pp. 899-901.

- [8] D. Wu, R. Huang, W. Wong, and Y. Wang, "A 0.4-V low noise amplifier using forward body bias technology for 5 GHz application," IEEE Microwave and Wireless Components Letters, vol. 17, no. 7, pp. 543-545, July 2007.

- [9] H. H. Hsieh, J. H. Wang, and L. H. Lu, "Gain-enhancement techniques for CMOS folded cascade LNAs at low-voltage operations," IEEE Transactions Microwave Theory and Techniques, vol. 56, no. 8, pp. 1807-1816, August 2008.

- [10] R. M. Weng, C. Y. Liu, and P. C. Lin, "A low-power full-band low-noise amplifier for ultra-wideband receivers," IEEE Transactions Microwave Theory and Techniques, vol. 58, no. 8, pp. 2077-2083, August 2010.

- [11] A. S. Sedra and K. C. Smith, Microelectronic Circuits, 5th ed. New York: Oxford University Press, 2004.

- [12] H. Y. Yang, Y. S. Lin, and C. C. Chen, "2.5 dB NF 3.1-10.6 GHz CMOS UWB LNA with small group-delay variation," Electronics Letters, vol. 44, no. 8, pp. 528-529, April 2008.

- [13] A. Bevilacqua and A. M. Niknejad, "An ultrawideband CMOS low noise amplifier for 3.1-10.6 GHz wireless receivers," IEEE Journal of Solid-State Circuits, vol. 39, no. 12, pp. 2259-2268, December 2004.

- [14] T. K. K. Tsang, K. Y. Lin, and M. N. El-Gamal, "Design techniques of CMOS UWB amplifier for multistandard communications," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 55, pp. 214-218, March 2008.

- [15] K. H. Chen, J. H. Lu, B. J. Chen, and S. I. Liu, "An ultra-wide-band 0.4-10 GHz LNA in 0.18-μm CMOS," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 54, pp. 217-221, March 2007.

- [16] Y. J. Lin, S. H. Hsu, J. D. Jin, and C. Y. Chan, "A 3.1-10.6 GHz ultra-wideband CMOS low noise amplifier with current-reused technique," IEEE Microwave and Wireless Components Letters, vol. 17, pp. 232-234, March 2007.

- [17] Aditi and M. Bansal, "A high linearity and low noise shunt resistive feedback UWB LNA," Conference on Information and Communication Technology, November 2017, pp. 1-5.

- [18] S. Mubashir and V. Singh, "A 2-10 GHz ultra-wideband common-gate low noise amplifier using body bias technique in 0.18 μm CMOS," Devices for Integrated Circuit, pp. 541-545, March 2017.

Copyright<sup>®</sup> by the authors. Licensee TAETI, Taiwan. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY-NC) license (http://creativecommons.org/licenses/by/4.0/).