A Keerthi\* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.7, Issue No.5, August-September 2019, 9240-9242.

# Design Of N Bit Adder And Subtractive Using Quantum Dot Cellular Automata

A KEERTHI

MTech student, Dept of ECE, Priyadarshini Institute of Technology & Science for Women's, Chintalapudi, Tenali, A.P, India. SK SHABANA

Assistant Professor, Dept of ECE, Priyadarshini Institute of Technology & Science for Women's, Chintalapudi, Tenali, A.P, India.

*Abstract:* Relatively easy to fix reasoning as well as quantum dot cellular robot (QCA) with each other can be taken into consideration as one of the most encouraging innovations for future generation computer systems. As CMOS circuits are coming close to restrictions in minimizing area as well as power dissipation, relatively easy to fix reasoning and also QCA modern technology have prospective to change CMOS. Moreover, restricted research is done on reversible sequential circuits with QCA implementation. This paper targets style as well as application of a standard sequential element, a relatively easy to fix dual side set off D flip flop, utilizing QCA. The logical capability, computational as well as power evaluation of the recommended circuit has actually been checked out in this work. This is one of such first attempts to make, analyze as well as carry out relatively easy to fix consecutive element using QCA. This layout will certainly help with the perception of complicated relatively easy to fix sequential circuits in the location of QCA circuits.

Keywords: Flip-Flop; Majority Gate; Quantum Dot; Kink Energy; Energy Dissipation;

## I. INTRODUCTION

QUANTUM dot cellular automata (QCA) is one of the emerging technologies that shows features to overcome the limitations like high computation throughput and power consumption faced in CMOS technologies. A lot of research has been done in designing universal logic gates, combinational circuits, sequential circuits and ALU using QCA and has shown its efficiency due to its small size and high computational speed. Apart from these advantages of QCA, it also has a great potential for low power consumption. Among several other alternatives, Quantum Dot Cellular Automata (QCA) is a revolutionary promising transistor less quantum paradigm that performs computation and routing information at Nano domain. The unique feature of QCA is that logic states are represented by a cell. A cell is a Nano scale device capable of transferring data by two state electron configurations. Alternatives to conventional CMOS technology is QCA which provides higher density, lower dissipation of power, higher clock frequency and better output results are needed. Quantum Dot Cellular Automata (OCA) technology is explored and introduced. When a new technology is introduced, new design principles are also necessary to consider. The design nature of QCA is not very complicated, instead it is simple than the conventional technologies.

## **II. PREVIOUS WORK:**

After the introduction of QCA, various styles of combinational and also consecutive QCA circuits have actually been reported. However, there are extremely few papers which define reversible circuits with QCA application. As currents as well as voltage degrees are not made use of in QCA, the power intake is minimal. Timer as well as Lent in 2002 show power dissipation as well as gain in QCA cell. Nonetheless, a number of researches have focused on power evaluation of QCA circuits. A top bound power dissipation version for QCA circuits was reported by Srivastava et al. Very first device for power evaluation QCApro was illustrated by Srivastava et al. which brings makeover in QCA circuit analysis. Some posts showed different methods of power computation in QCA circuits. Couple of research papers has reported power analysis of particular rational entrances such as XOR entrances making use of QCA circuits. Relatively easy to fix calculation is recognized for its application in loss less computer and quantum dot mobile robot (QCA) is known for its outstanding homes such as exceptionally high density and also high procedure rate with ultra-low power dissipation. Most definitely combining reversibility in QCA domain name will add incredible benefits resulting in ultra reduced power, highly dense circuits for future generation computers. Execution of couple of reversible gates such as Fredkin entrance, Feynman entrance and their power evaluation is reported. also Consecutive circuits create core of the digital systems; hence in this paper writers have shown the execution of standard foundation of sequential circuits and also their in-depth analysis. The term CMOS means "Complementary Metal Oxide Semiconductor". CMOS innovation is just one of the most preferred technology in the computer chip design market and broadly made use of today to create integrated circuits in countless as well as varied applications. Today's computer system memories, CPUs and also cell phones make use of

this modern technology as a result of numerous vital benefits. This technology utilizes both P channel and N network semiconductor gadgets. One of one of the most popular MOSFET innovations readily available today is the Corresponding MOS or CMOS innovation. This is the dominant semiconductor modern technology for microprocessors, microcontroller chips, memories like RAM, ROM, EEPROM and application particular integrated circuits (ASICs).

Fig.2.1. QCA model.

## **CMOS METHODOLOGY:**

In CMOS technology, both N-type and P-type transistors are used to design logic functions. The same signal which turns ON a transistor of one type is used to turn OFF a transistor of the other type. This characteristic allows the design of logic devices using only simple switches, without the need for a pull-up resistor. In CMOS logic gates a collection of n-type MOSFETs is arranged in a pull-down network between the output and the low voltage power supply rail (Vss or quite often ground). Instead of the load resistor of NMOS logic gates, CMOS logic gates have a collection of ptype MOSFETs in a pull-up network between the output and the higher-voltage rail (often named Vdd). Thus, if both a p-type and n-type transistor have their gates connected to the same input, the ptype MOSFET will be ON when the n-type MOSFET is OFF, and vice-versa. The networks are arranged such that one is ON and the other OFF for any input pattern. CMOS offers relatively high speed, low power dissipation, high noise margins in both states, and will operate over a wide range of source and input voltages.

## III. PROPOSED SYSTEM

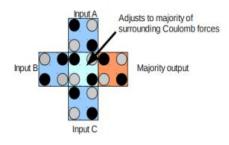

QCA is a novel emerging technology in which logic states are not stored as voltage levels, but rather the position of individual electrons. Conceptually, QCA represents binary information by utilizing a bi-stable charge configuration rather than a current switch. Unlike conventional logic circuits in which information is transferred by electrical current, QCA operates by the Columbic interaction that connects the state of one cell to the state of its neighbors. Hence the information transfer (interconnection) is the same as information transformation (logic manipulation) in the QCA technology. The QCA cell in contrast to electronics based on transistors, QCA does not operate by the transport of electrons, but by the adjustment of electrons in a small limited area of only a few square nanometers. QCA is implemented by quadratic cells, the so-called QCA cells. In these squares, exactly four potential wells are located, one in each corner of the QCA cell. In the QCA cells, exactly two electrons are locked in. They can only reside in the potential wells. The potential wells are connected with electron tunnel junctions. There are two diagonals in a square, which means the electrons can reside in exactly two possible adjustments in the OCA cell. Regarding these two arrangements, they are interpreted as a binary '0' and binary '1', i.e. each cell can be in two states. The state '0' and the state '1', as shown in figure 3. A binary system is something familiar, as Boolean logic is used already in today's computers. There, a high voltage is often interpreted as binary '1' and a low voltage as binary '0'

Fig.5.1.Output Results

The minimum energy requirement to dissipate the energy between the two neighboring cells is kink energy and is less than from the equation 3 because if more energy is given at the input cell, then there will be more tunneling of quantum dots from one potential well to another potential well then there is a possibility of extra energy to dissipate due to the rotational tunneling and remains same polarization as before. This rotational tunneling may not happen in the previous cells because these cells are already adjusted accordingly and it is difficult to modify them again within the QCA design. We cannot predict the electron tunneling as well as we cannot distinguish that the same electron will remain same position. Ina cell of two electrons, they may exchange their position and it will happen when the applied dissipated energy is more than the required. In that case to stabilize the energy within the cell, the electrons may rotate their position.

Fig .5.2. power dissipation.

#### V. CONCLUSION

In this paper we have developed a standard equation from SR flip flop and using that equation other flip flops like D, T and JK flip-flops are subsequently designed. This is a new approach of designing flip-flops with less hardware complexity in nanotechnology. Any memory storage device can be built using the flip-flops designed in the above mentioned approach. The layout has been generated and simulation results are verified using QCA Designer simulation tool. The stability of the circuit has been clearly determined by the 3-D plots of kink energy of the two possible combinations of the output cell. In future there is a scope for design other sequential circuits like registers, counters, memory blocks and other flip flops using this generalized block.

#### REFERENCES

- [1] M. Furdek, M. Danko, P. Glavica, L. Wosinska, B. Mikac, N. Amaya, G. Zervas, and D. Simeonidou, "Efficient optical amplification in selfhealing synthetic ROADMs," in 2014 International Conference on Optical Network Design and Modeling, May 2014, pp. 150–155.

- [2] S. M. Bowers, K. Sengupta, K. Dasgupta, B. D. Parker, and A. Hajimiri, "Integrated selfhealing for mm-wave power amplifiers," IEEE Transactions on Microwave Theory and Techniques, vol. 61, no. 3, pp. 1301– 1315, 2013.

- [3] I. Ivan, C. Boja, and A. Zamfiroiu, "Selfhealing for mobile applications," Journal of Mobile, Embedded and Distributed Systems, vol. 4, no. 2, pp. 96–106, 2012.

- [4] K. Khalil, O. Eldash, and M. Bayoumi, "Self-healing router architecture for reliable network-on-chips," in IEEE International Conference on Electronics, Circuits and Systems (ICECS). IEEE, 2017.

- [5] S. Narasimhan, S. Paul, R. S. Chakraborty,F. Wolff, C. Papachristou, D. J. Weyer, andS. Bhunia, "System level self-healing for

parametric yield and reliability improvement under power bound," in Adaptive Hardware and Systems (AHS), 2010 NASA/ESA Conference on. IEEE, 2010, pp. 52–58.

- [6] M. R. Boesen, J. Madsen, and P. Pop, "Application-aware optimization of redundant resources for the reconfigurable self-healing eDNA hardware architecture," in 2011 NASA/ESA Conference on Adaptive Hardware and Systems (AHS), June 2011, pp. 66–73.

- [7] Q.-Z. Zhou, X. Xie, J.-C. Nan, Y.-L. Xie, and S.-Y. Jiang, "Fault tolerant reconfigurable system with dual-module redundancy and dynamic reconfiguration," vol. 9, no. 2, 2011, pp. 167–173.

- [8] T. Koal, M. Ulbricht, P. Engelke, and H. T. Vierhaus, "On the feasibility of combining on-line-test and self repair for logic circuits," in 2013 IEEE 16th International Symposium on Design and Diagnostics of Electronic Circuits Systems (DDECS), April 2013, pp. 187–192.

- [9] K. Khalil, O. Eldash, and M. Bayoumi, "A novel approach towards less area overhead self-healing hardware systems," in International Midwest Symposium on Circuits and Systems (MWSCAS). IEEE, 2017.