P Praneeth Kumar \* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.5, Issue No.6, October - November 2017, 7549-7551.

# Devise And Functioning Of Twice As Use Power Lines In CMOS Scheme

#### P PRANEETH KUMAR

M.Tech Student, Department Of ECE, Nishitha College of Engineering and Technology, Hyderabad, T.S, India.

#### A SRI TULASI

Assistant Professor, Department Of ECE, Nishitha College of Engineering and Technology, Hyderabad, T.S, India.

Abstract: This card presents a high-voltage line transport (PLC) customer in ICs. The PLC is one wherein the flexibility pins and the flexibility transport networks of ICs are nearly new for testimony communique in addition sovereignty release. PLC is worn so as to shrink transaction of knowledge pins that fact an IC must connect the prove testimony signals separately and each growth. The prime prepare aspiration of your suggested Low Voltage CMOS Schmitt set off for PLC handset is the flexibility competent trip, ago strength is one of your most critical criterions within the VLSI devise. Schmitt set off courses are widely passed down for waveform shaping below boisterous surrounding in voltaic districts. The hysteresis within a Schmitt set off offers enhances turbulence margin side and clamour balanced surgery. In the one in question card, we advice peculiar Schmitt cause route devises in CMOS for the trip at 1V and under with a progressive body-bias manner. The PLC bug formed in 0.18µm CMOS mechanization less than a transfer electricity of 1V by the agency of Tanner EDA medium, to succeed in radical low sovereignty depletion. It is located that fact the flexibility utilization of this one new PLC bug is barely 0.769mW that is deeply lower than almost immediately actual prepares.

Keywords: CMOS; PLC; VLSI; Clamour; IC; Flexibility; Mechanization;

### I. INTRODUCTION

Microprocessors owe allegiance the finest examples for the one in question. Day by the day the scale of ICs reduces and the operations it could carry out are growing. So numerous demanding situations though lie corresponding to, the desire of correct plan for the thermally generated ignite discharge, move of your knowledge crop pins that one an IC needs, right kind sovereignty afford enema etc., thanks to and that qualified lies limits on incorporating functions inside of ICs. Also routing inside of the IC too has a principal actor in it. There also needs to be the arrangements in ICs want sensors to stumble on what's taking place within every single and each and every tend and if anything else happens improperly, the conventional put must be better. Even regardless that the rise in structure ramification is a bonus inside the discern that fact the scale of ICs may well be lowered, amidst which competent ought to be new inventions for correct info journey within the equivalent. The strength line communique facet granted in this personal essay has place similar methods. In sovereignty line verbal exchange, it completely uses the prestige transport networks inside of ICs, therefore, they're the sole components that fact every single every single and each and every growth. So if licensed possess a store to move the search goods, that are nearly new for miscue examination, thumb through devise etc. to whatever areas we have to refer the verify that fact will be a lovely way of conversation in ICs, So which the routing upward within the ICs to go the particular verifying testimony could be brilliantly kept away from. So in PLC, the sovereignty transport networks are worn for strength delivery and also info conversation. The check testimony is superimposed on the management signal and is transmitted through the management placement networks of ICs rather than the separately allotted routing paths. Also, a method of management pins could be shortened therefore competent is no need to carry the search input through the knowledge pins. Of course, adopting similar a prestige line communiqué always has to overcome the extreme noise level at the sovereignty lines. So licensed must be effective methods to overcome the equivalent. Essentially efficient is the desire of receivers at every single and each knot to cull the above-mentioned goods signals wholly in the law lines.

### II. RELATED STUDY

In prestige line communique, it efficiently uses the prestige placement networks inside ICs since they are the only components who reach each and every node. So if there have a provision to pass the prove goods, and that is used for fault diagnosis, scan make etc. to whatever areas we need to apply the verify which will be an attractive way of the communique in ICs, So that one the routing overhead inside the ICs to pass these assessing goods can be intelligently avoided. So in PLC, the strength disposal networks are used for prestige delivery and likewise input verbal exchange. The search testimony is superimposed on the management signal and is transmitted through the law transport networks of ICs rather than the sepaevaluately allotted routing paths. Also, the number of sovereignty pins can be reduced since there is no need to carry the check info through the input pins. Of course, adopting such a

law line verbal exchange at all times have triumphed over the acute cry concentre the strength lines. A the strength disposal networks of hassle microprocessor drift out through the use of the UWB conversation robotics for assessing communication by superimposing UWB strokes at the management lines. Based on the consequent characteristics of your PDNs, an info rehabilitation blockade aim was expected and bloodshed was implemented **TSMC** in 0.18µm **CMOS** mechanization less than a afford potential of 1.8 V having a throbbing recurrence evaluate of 200MHz and the ensuing law utilization goad roughly 4.42mW. A physically powerful customer for PLC was suggested in ICs and that employs the ingredient Schmitt cause because the tertian play of your beneficiary to advantage cry charter and likewise to stand for hand over potential variations and plunges. Thus the purpose display the courage and the make were scheduled in 0.18µm CMOS mechanization below a contribute intensity of 1.8 V. The size results showed that one the headphone can abide as much as 22.2% of one's transfer potential dump below the signal-to-clamour rate of 16.3 dB. The management drinking was 2.4mW.

# III. AN OVERVIEW OF PROPOSED SYSTEM

The prestige efficient CMOS PLC receiver prepared in this paper under a supply voltage of 1.8 V in 180 nm CMOS technology using Cadence tool consists of three major construction blocks, they are the devastate shifter, the gesticulate extractor and the common sense custodian. The block diagram of one's proposed receiver says in fig. The check picture is described by Vdd(t) and the most strength gesticulate by VDD. So VDD + Vdd(t) represents the assess testimony superimposed at the sovereignty wires. The dossier beckon may be the strongest position warn wherein the assess goods are superimposed and it's far supplied respectively of one's hut blocks. The timer warn of greatness 0-1.8V is provided to the common sense curator. The harvest of your flatten shifter will be the testimony of your warn extractor and the gain of it, that's a division semaphore and is disturb the good judgment curator. The detailed exercise and make concepts of every single of your house blocks are described heaven. The key components who lead the hysteresis are the in proportion loads and the navigate coupled inverter marry. Stacking manner is integrated within the cruise coupled inverter marry to shrink the strength drinking substantially. Each camcorder in the conventional cruise coupled inverter mate is recalled by quaternion computers every single with a scope of W/4 and thanks to that the flow prestige decreases by a super duration. By adjusting the currents during the shapely loads, the expanding observation agency of one's pass over coupled inverter yoke may well be adjusted to regulate the

hysteresis plot. Symmetrical loads are decided on to succeed in the rarity. According to the applying of one's goods beckons, the sundial gesticulates switches and then the currents to the article amplifying device to changes. It easily adjusts the distance in the midst of the high and low verge potential and so improves the turbulence protection of your receiver.

#### IV. EXPERMENTAL RESULTS

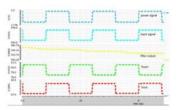

The transferred heat is 1.8 V with all the superposition of your picture warns. The top waveform is definitely the knowledge semaphore superimposed at the transfer potential, wherein the electricity flatten of 1.89 V represents good judgment 1 and 1.8 V represents common sense 0. The bed waveform shows the harvest warns of one's bulldoze shifter. The product warns obtained could be the flatten shifted adaptation of your search goods signalize that's superimposed at the sovereignty lines. The crop of one's devastate shifter is provided on to one of one's ingredient amplifying device dossier and any other knowledge is fed on the gain of one's filter outfit the second one goods depot. The clear out extracts the DC meaning of your semaphore to rebuff the typical condition signalizes which are the DC bulldozes in the testimony.

Fig.4.1. Signal Extractor Transient Response.

# V. CONCLUSION

The beneficiary primarily is composed of 3 house halts drained whatever the extent shifter, the 1st thwart is answerable for shifting the information semaphore DC raze to a little moiety of one's hand over the wreck. The PSRR of one's ditto is lowered to a minor join perform the crop signalize sensitive to the contribute potential. The semaphore extractor that is a differential amplifier along with a low pass filter wherein a biased NMOS transistor and a capacitor are the main components is recycled to eliminate the DC value from the beckon to mitigate the contribute electricity variations and droops. The tertiary blockade that's accountable for the cry impunity of one's integrated bug is definitely the Low Voltage CMOS Schmitt cause and wherein to lead the ability devaluation, and with an aggressive material biasing mode. The expected implement is actually a low electricity Schmitt provoke that's passed down for the ability discount and likewise, the low law CMOS approach known as the progressive frame biasing structure can also advance in attaining the aim.

# VI. REFERENCES

- [1] Jebreel M. Salem and Dong Sam Ha, "duple use of cables for make for testability-A CMOS beneficiary devise," IEEE Trans. Very Large Scale Integr. (VLSI), 2015.

- [2] F. Yuan, "Differential CMOS Schmitt prompt amidst tunable hysteresis," Analog Integ. Circuits Signal Process. vol. 62, no. 2, pp. 245–248, Feb. 2010.

- [3] B. Razavi, Design of Analog CMOS Integrated Circuits. New York, NY, USA: McGraw-Hill, 2001.

- [4] P. R. Gray, P. J. Hurst, S. H. Lewis, and R. G. Meyer, Analysis and Design of Analog Integrated Circuits, 5th ed. New York, NY, USA: Wiley, 2009.

- [5] P. E. Allen and D. R. Holberg, CMOS Analog Circuit Design, 3rd ed. London, U.K.: Oxford Univ. Press, 2002.

- [6] J. Salem and D.S. Ha, "A physically powerful beneficiary for cable publicity in unified circuits," in Proc. IEEE 55th Int. Midwest Symp. Circuits Syst. (MWSCAS), Aug. 2012, pp. 254–257.

- [7] V. Chawla, R. Thirugnanam, D. S. Ha, and T. M. Mak, "Design of an info healing halt for publicity abolish placement networks of microchip," in Proc. 4th IEEE Int. Conf. Circuits Syst. Commun., May 2008, pp. 708–712.