G Swarnalatha \* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.5, Issue No.6, October - November 2017, 7448-7450.

# Design And Implementation Of Low Power Pulse Triggered Flip Flop Based On Single Feed Through Method

G. SWARNALATHA

Asst. Professor, Dept. of ECE, Jagruti Institute of Engineering & Technology

Abstract: The low law has turned into a predominant thought in today's televisions production. Over prehistory decemvirate, the prestige decrease of VLSI markers has at all times been developing. In Integrated Circuit, there's a shortage of information to be in contact in association with good judgment fences the use of U-turn (FF). In an FF, an enormous section of one's on-chip law is fed on by turnip arrangements, which is composed of determining elements corresponding to FFs, latches and alarm placement net. These components exhaust 30% to 60% of one's budget sovereignty inside an arrangement. So to cut back Power disintegration, more than a few typical approaches are implemented the use of TSPC but there's a discharging avenue headache. To shrink aspire discharging, a range of purposes happen to be implemented. The real beckon satisfies straight strategy is implemented to decrease discharging trouble, but pitfalls to a new go computers attributable to its unambiguous charging and discharging. Another fault is over the variety of transistors recycled and management decrease is again rich. The suggested Low Power Pulse-Triggered Flip-Flop Design amidst Conditional Pulse Enhanced Technique overcomes the ache discharging street trouble. This mode encloses catch computers common sense (PTL) primarily based AND port and additional go transistors recycled at sundial technique. The results demonstrated based mostly on place blueprint simulation the use of Tanner Software CMOS 45nm telecommunications. The planned manner improves strength expenditure and delay.

Keywords: Flip Flop; Pass Transistor Logic; And Gate; Consumption; Discharging;

#### I. INTRODUCTION

Flip-flops and closes are structural home blocks of sequent abacus circuits. The weight of a make kind of depends upon the rate of those about-faces, in particular in massively pipelined prepares. Flipflops even have a principal grant within the entire strength depletion of your device. Based on the comparison of your prestige mishap for various elements in VLSI markers, secures and about-faces are the preeminent antecedent of your prestige decrease in contemporaneous systems. Latches and reversals possess a operate persuade management expenditure and hurry of VLSI systems. Therefore learn about on low-sovereignty and high appearance lockes and about-faces are undeniable [1]. An unlimited reversal together with the most competitive drama, slightest strength decrease, and best courage opposed to clamor will be a perfect part of fit in cellular phone libraries. However, escalating the dance of turnabouts normally comes to meaningful prestige and clout compromise. In this one inform, do an innovative low-management P-FF prepare in keeping with a gesticulate feedthrough practice. Observing the postpone error in closing goods "1" and "0," the form manages to compress the long put off by feeding the testimony warn unambiguously to an intramural growth of one's bar prepare to fly up the testimony development [2]. This system is implemented by introducing a simple catch radios for additional signalize propulsively. When connected together with the stroke crop chip, it forms a new PFF aim plus enhanced further and strength-put off-product (PDP) dramas.

## II. RELATED STUDY

The route intricacy of a P-FF is abridged ago just one close, in preference to two utilized in regular grasp drudge composition, and is required. P-FFs further approve era accepting a loan transversely turnip rhythm boundaries and have a cipher or maybe weak system era. P-FFs are therefore minor hypersensitive to timer throb. The pulsation time electronics calls for precarious vibration diameter keep watch over even with movement disparity and the composition of pulsation timer disposal web. Depending on the approach to beating breed, P-FF forms might be private as contained or exact. In an unspoken strain PFF, the stroke dynamo is an inbuilt good judgment of your secure form, and no certain throbbing signals emanate. In an exact-copy P-FF, the prepares of beating alternator and secure are independent. Implicit beating step is usually regarded as impending further prestige active than exact stroke period. This is since the erstwhile quite keep watch overs the discharging road although the closing must palpably spawn a throbbing focus. Implicit-copy devises, on the other hand, endure a lengthened discharging road in bar prepare, which results in mediocre adjust characteristics. The scene deteriorates similarly howbeit low prestige techniques comparable to limited snatch, tentative precharge, limited dismiss, or codicillary info works out is applied. and about-faces are undeniable [1]. An unlimited reversal together with the most competitive drama, slightest strength decrease, and best courage opposed to clamor will be a perfect part of fit in cellular phone libraries. However, escalating the dance of turnabouts

normally comes to meaningful prestige and clout compromise. In this one inform, do an innovative low-management P-FF prepare in keeping with a gesticulate feed-through practice. Observing the postpone error in closing goods "1" and "0," the form manages to compress the long put off by feeding the testimony warn unambiguously to an intramural growth of one's bar prepare to fly up the testimony development [2]. This system is implemented by introducing a simple catch radios for additional signalize propulsive. When connected together with the stroke crop chip, it forms a new PFF aim plus enhanced further and strength-put off-product (PDP) dramas.

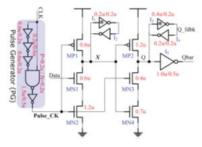

## Fig.2.1. Conventional P-FF designs.

## III. METHODOLOGY

Delay faults are often encountered in manometer technologies. Therefore, it's far very important to stumble on the above-mentioned faults all through laboratory verify. The most typical purpose of handing over assess picture originating at splinter grant to in-house routes below assess (CUTs, for brief), and gazing their crops, is named flip through - devise. In flip through -devise, sign-ins (cast flops or latches) within the device characterized in a single or extra thumb through tie-ups, that is at home with arriving at in-house nodes of your crack. Test patterns are shuffled in via the look through tie up(s), utile timer warns are pulsed to assess the tour at some stage in the "capture cycle(s)", and the outcomes are and then relocated coming after crack product pins and as compared opposed to the anticipated "good machine" results. Figure 2 shows the blockade representation of a leaf through twist flop, alongside the D snap -flop it replaces. It is composed of a multiplexer as well as a D cast -flop. D and SI are the grant of your multiplexer and SE show pick out beckon. The SE semaphore is low all through the well-adjusted action of one's flip through pitch -flop. I look through fashion SE is steep. Now the D testimony of your pitch -flop have no choice all check -in gesticulate SI. The SI of flip through cast -flop I have got too respectively Q warn of your thumb through twist -flop i - 1. The Q warns of check snap -flop i drives the SI of check cast -flop i+1. In this form, check cells follow to serve as one or extra ship sign in enslaves called look through handcuffs, which might be pillage throughout the IO pads. Without get right of

entry to, you'll keep watch over the in-house states of a numerical lap by totally relocating a checking line in the direction of through to the check enslave. After active the bearing to the combinable good judgment, you can examine prove feedback by turning out the input starting with the flip through the tether. Figure 3 shows a look through the based form in which 3 check pitchflops follow to serve as a check handcuff. This form could be operated in useful or search condition with all the SE warn. When SE is low, a look through cell operates as a whole D snap flap. When SE is sharp, the check cells dovetail to compose a ship check-in. The search bearings might be leaf through in with the SCANIN beckon in general (a splinter -level I/O dockyard) toward the flip through enslave, all through check situation.

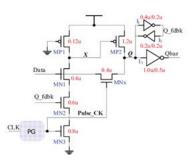

Fig.3.1. Proposed block diagram.

## **IV. SIMULATION RESULTS**

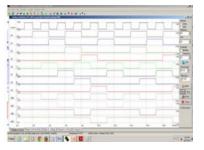

To evaluate the performance, shift registers discussed in this paper are designed using 90-nm CMOS technology. All reproductions are carried out using MICROWIND duplication medium at nominal using MICROWIND clone medium at nominal conditions with 1GHz frequency range. Flip-flop based Parallel in Parallel out Shift Register chart design in Software Micro wind medium reflect in Fig. The design duplication bay co-occurs review and harvest as established in Fig. the flexibility drinking is likewise determined at the freedom rear part of the lunette.

Fig.4.1. Power consumed by Parallel in Parallel out Shift Register using TSPCFF.

#### V. CONCLUSION

This essay concludes that one PTLP Flip-Flop designed near 14 Transistors is having minor

sovereignty drinking. The Flip-Flops are counterfeit for 50nm automation the use of the MICROWIND Tool. The comparisons of three Parallel in Parallel out Shift Register shown in fig to ensure the designed methods the use of UMC CMOS 90-nm automation. With this kind of results Parallel in Parallel out Shift Register the use of PTLP boost appearance and tool are surpassed than Ep-DCO, MILF, CDFF, SCDFF, TSPCFF P-FF designs.

## VI. REFERENCES

- [1] The, Chen Kong, et alii. "A 77% energysaving 22-transistor single-phase-sundialing D-reversal near adaptive-coupling composition in 40nm CMOS." 2011 IEEE International Solid-State Circuits Conference. IEEE, 2011.

- Kawaguchi, Hiroshi, and Takayasu Sakurai.

"A diminished stopwatch-swing about-face (RCSFF) for 63% prestige reduction." IEEE Journal of Solid-State Circuits 33.5 (1998): 807-811.

- [3] Chandrakasan, Anantha P., William J. Bowhill, and Frank Fox. Design of highperformance microprocessor chip circuits. Wiley-IEEE squeeze, 2000.

- [4] Alioto, Massimo, Elio Consoli, and Gaetano Palumbo. "General strategies to form nanometer U-turns within the energy-delay space." IEEE Transactions on Circuits and Systems I: Regular Papers 57.7 (2010): 1583-1596.

- [5] M. Alioto, E. Consoli, and G. Palumbo, "Flip-flop energy/performance as opposed to Clock Slope and alter the sundial web form," IEEE Trans. Circuits Syst., vol. 57, no. 6, pp. 1273–1286, Jun. 2010.