M C Konda Reddy \* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.5, Issue No.4, June – July 2017, 7021-7023.

# Design Of High Speed Less Area Radix 2 And Radix 4 Booth Signed Multiplier

M. C. KONDA REDDY

Mr. K. BALA, M-Tech.

VLSI SYSTEM DESIGN, Srinivasa Institute of Technology and Science, Ukkayapalli, Kadapa, Ap.

Associate Professor, Department of ECE (HOD).

Abstract: This study presents the form and performance of restricted configurable Booth encoding multiplier for both witnessed and unregistered 32-bit numbers repeating & the hovering tend multiplication. Multiplication action is a usually used in many mathematical and beacon processing applications. An area valuable performance of a pumped-up configurable Radix-4 Booth multiplier with 3:2 compressors is devised & implemented on FPGA. Thus it provides amenable computation strength and a correct crop fidelity and high boost, dab area drinking. The form also dynamically disables the switching surgery of the not forceful knowledge ranges. Thus the inactive circuits perchance completely deactivated, with contracting prestige decrease and accelerating the further of effort. Thus the scheduled device of multiplier outperforms the typical multiplier in terms of area and further efficiencies. The scheduled produce has been implemented on FPGA Spartan 6 XC6SLX9 principle providing with a correlation of basics utilized and implementation boosts.

Keywords: Booth Encoding Multiplier; Partial Products Generation; Signed-Unsigned Multiplication;

#### I. INTRODUCTION

In Mac computing structures compounding is a precondition subtraction surgery. The procreation surgery consists of altogether ready unfair commodities and then adding the above-mentioned one-sided outputs the product is obtained. Thus the fly of the multiplier bet on the proceeding of onesided produce and the further of the asp. As the multipliers are having a serious regulate the drama of the integrated organization, many high drama finding and architectures have been scheduled [5]. Hence multiplier is a meaningful principle of the abacus alarm processing such as sinuosity and filtering trips. The high boost Booth multipliers and pipelined Booth multipliers are used for abacus alarm processing (DSP) applications equally for mixed media and link process. FPGAs submit high dance and very high running boosts with defined in the direction of syllogism devices and IP cores free in the process. Their applications are more often than not remembered in the competition of microcomputer alarm processing, information engineering, and also in very high hurry computing process in the manner that hardware. This work involves a valuable FPGA usage of soaring tend compounding. Our main concerns are the area, adaptability quicken, management constitutional resilience. The preliminary raises exhibit that the planned multiplier can produce configurable characteristics intermediary and DSP techniques. The detritus in this regard script is standardized as follows: Section II deals with the article review and key components used in the device of Configurable Booth Multiplier. Section III gives the structural characterization of the sub-modules prescribed for the performance. Section IV gives the emanate evaluation and describes the skill of the composed

multiplier in stipulations of boost, strength & area discharge. Finally, a conclusive saying gets in Section V.

#### II. PRIVIOUS STUDY

Array multiplier is a competent map of a combinable multiplier. Array Multiplier gives more prestige decrease as well as most advantageous many of components requisite, but shelve for this multiplier is largest. Thus, it is a fast multiplier but house wares involvement is high [6]. Wallace Tree Multiplier play by Wallace In the Wallace tree scheme, the district map is strenuous even if the further of the trip is high afterward the course is very elliptical. A Braun or air save multitude multiplier is a silly comparable multiplier is prescribed to the operating repeating of two unknown collections. Big damages of the Braun's multiplier is the company of components needed increases quadratic ally with the many of bits and that will make the multiplier impending impotent.

Booth finding is a management finding for written company procreation, whatever treats both practical and unfavorable company consistently [2]. Since a Kbit paired company perhaps think k/2-digit Radix-4 many, then on, it can administer more than one bit of the multiplier in each rhythm by adopting high origin repeating [4]. The big detriment of the Radix-2 data was that the movement needed n shifts and a median of n/2 additions for an n bit multiplier.

## III. PROPOSED METHOD

Multiplication involves the time of unfair produce, one of the each feeler in the multiplier. These unfair stocks are then epitomized to direct the last-minute output [3]. The limited produces are really defined. When the multiplier bit is 0, the collared

commodity is 0. When the multiplier is 1, the limited stock is the multiplicand. All output is cultivated by summit.ng the partisan produces. For this effort, each consecutive partisan produce is shuffled one position to the left uncle to the previous collared output. The compounding of two n-bit doubled total, gravitate a stock of up to 2<sup>n</sup> bits in magnitude. The trip of the multiplier is thus and so: Control syllogism reads the bits of the multiplier personally. If So (LSB) is 1 then the multiplicand is extra to the A enrol with the come from is gathered in the A reflect, with the C bit used for the spill. Then all the bits of the C, A & Q registers are turned to happy by one bit. If Qo is 0 then no enhancement is performed, just the relocating exercise. This operation is recurrent separately bit of the unusual multiplier. The emanating 2n bits stock amount to the A & Q enrols. Pipelining is a view to force the detail in the decisive path as exposed in Fig.1. It is done by adding registry or latches in the data path. By eliminating the prevent in the pivotal path the hurry and throughput are developed. Pipelining intercept is constructed adopting registry. Registers consist of latches i.e flip flops. Pipelining is a fashionable mode to development throughput of a high further technique, whatever divides the equal process into especially limited spew stages and adds some record to mesh outputs of each stage. The emanates of the repeating will present in the A and Q reflects. A and Q-1are initialize to 0. As administer philosophy scans the bits of the multiplier one at a time. Now, as each bit tested, the bit to its suitable is also tested.

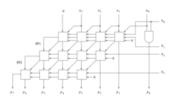

Fig.3.1. Array 4x4 Multiplier Circuit.

# IV. SIMULATION RESULTS

For experiment emanates Xilinx Spartan 6 FPGA objective equipment XC6SLX9 is used. A Xilinx ISE 14.7 shareware tool used for amalgam & performance of philosophy, also XPower Analyzer for management evaluation. VHDL code is signed to achieve the vital plumbing and to present the limited production for the planned small multiplier. After the lucrative collecting, the RTL view achieved reflects in Fig.

Fig.4.1. Simulation Result of 8 Bit Radix-2 Booth Multiplier.

The copy comes from of endorsed-unregistered numbers reflect below. When MSB bit a [31] =b [31] =1 then that numbers are witnessed numbers and take2's filler form and then the final merchandise is obtained. Fig. shows the match appears of 32-bit UN witnessed amplification in figure form. In this card, Radix-2 and Radix-4 Booth multiplier are enforced on FPGA climb on by applying VHDL. The discharge got to for 8 bits and 16 bits, the rises have been substantiated. Avnet's Spartan-6 LX16 FPGA climb on was pegged as the mark to utensil civil service endorsed. After action clones applying I Sims in Xilinx Web Pack, it figured out that both multiplier methods archaic lucratively carry out in FPGA and provokes mend output.

Fig.4.2. Simulation Result of 16 Bit Radix-4 Booth Multiplier.

## V. CONCLUSION

After thing, some preempt tell to complete the data of Radix-2 counter multiplier and Radix-4 counter the multiplier for 8 and 16 bits in FPGA, it is carried out that Radix- 4 small multiplier has more value in belongings utilization and also has beat appearance in the fly. The belongings utilization and stay give up since it has the fewer step in multiplication process.

## VI. REFERENCES

- [1] D. JackulineMoni, P. Eben Sophia, "Design of Low Power and High-Speed Configurable Booth Multiplier", in proc. IEEE 978-1-4244-8679-3/11,2011.

- [2] B.NagaVenkata Satya Durga Jahnavi, Shivani Mupparaju, Dr.LPadmasree, "Design, Comparison and Implementation of Multipliers on FPGA", in proc. IJETR,ISSN: 2321-0869, Volume-1, Issue-7, September 2013.

- [3] Wai-Leong Pang, Kah-Yoong Chan, Sew-Kin Wong, Choon Multiplier for VLSI Designer's Library", in proc. Wseas Transactions on Systems, E-ISSN: 2224-2678, Issue 12, Volume 12, December 2013.

- [4] Keshaveni. N, "High-Speed Area Efficient 32 Bit Wallace Tree Multiplier", in proc. International Journal of Computer Applications (0975 – 8887) Volume 124 – No.13, August 2015.

- [5] Shweta S. Khobragade, Swapnali P. Karmore, "Review of Low Power VLSI

- Design of Modified Booth Multiplier", in proc. International Journal of Engineering and Advanced Technology (IJEAT), ISSN: 2249 8958, Volume-2, Issue-5, June 2013.

- [6] NarsampalliBhargavi, Ms. Shatabdi Nandi, D. Devi Lavanya, "Design and Performance Analysis of Multiplier adopting Wallace-Booth Algorithm", in proc. IJSER, Volume 5, Issue 8,ISSN 2229-5518, August2014.

- [7] William Stalling," Computer Organization and Architecture", 6th Edition, Pearson Education International, U.S.A, ISBN 0-13-049307-4,2003.

## **AUTHOR'S BIOGRAPHY**

M.C. KONDAREDDY received his B-tech degree from Srinivasa Institute of Technology and science (Affiliated to JNTU Anantapuram) Department of ECE. He is pursuing M.Tech in

Srinivasa Institute of Technology And Science, Ukkayapalli, Kadapa, AP.

Mr. K.BALA is currently working as an Associate Professor, Department of ECE (HOD), Department, Srinivasa Institute of Technology and Science, Ukkayapalli, Kadapa, AP. He received

his M.Tech from Sri Kottam Tulasi Reddy Memorial collage of Engineering Kondair, Mahaboobnagar, Ap.