A Sindhuja \* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.5, Issue No.4, June – July 2017, 6847-6849.

# Design Of Super Gate Through The Use Of Transistor Network Method

# A SINDHUJA

M.Tech Student, Department of ECE, Avanthi Institute of Engineering & Technology, Hyderabad, T.S, India.

# P SURESH KUMAR

Assistant Professor, Department of ECE, Avanthi Institute of Engineering & Technology, Hyderabad, T.S, India.

Abstract: Transistor structure development represents a compelling way of bettering VLSI circuits. In VLSI microcomputer devices, the sign shelves spread, prestige disintegration and area of circuits are strongly associated with transaction of radios. This recommended construction described an efficient graph-based approach to make optimized computers (divert) structures. The scheduled construction about paper will be prepared to implemented and also search the product current, gain heat, area accepting Dsch31 and individual wind.

Keywords: Micro Computer Devices; Optimized Computers; Gain Heat;

# I. INTRODUCTION

The cue stays reproduction, management disintegration, and area of circuits is actively analogous to the collection of camcorders (switches). Hence, camcorders arrangement upturn owe allegiance political action committee when conspiring standard cell libraries and method gates. Switch-based technologies, in the manner, that CMOS, Fin FET, and carbon annotate, can step on such an improvement [1]. Therefore, potent breakthrough to automatically achieve optimized transistors networks is very proper for conspiring digital integrated circuits (ICs). Several methods have been given in the lore for generating and optimizing camcorders networks. Most traditional serve solutions revolve around expressions, in which only series-parallel (SP) associations of computers can be obtained from performing. On the other hand, graph-based methods are able to find SP and also non-SP (NSP) preparations with future devaluation in computers count For this reception, factorization methods allow giving the SP net demonstrated in Fig. comprising seven camcorders. Existing graphbased methods, succeeding, spare cater the NSP sap demonstrated in Fig. also with seven stereos [2]. However, the 24-carat pattern confident of only five camcorders, as exposed in Fig. is not raised by any of the particular methods.

Fig. Transistor networks

# II. METHODOLOGY

In VLSI automated produce, the cue shelves reproduction, law diffusion, and area of circuits are heavily relevant to form of stereos (switches).

Hence, stereos arrangement optimization has a place special-interest group when forming ideal cell libraries and policy rates. Switch stationed technologies, in the same manner with CMOS, Fine, and charcoal annotates can take advantage of such a progress. Therefore, the competent breakthrough to faithfully cause optimized stereos net whole caboodle are really handy for producing numerical unified circuits (ICs). Several methods have been given in the brochure for generating and optimizing radios net entirely [3]. Most regular solutions are planted on serving Boolean expressions, to what end the only series-parallel (SP) associations of camcorders can be obtained from separate forms. On the other hand, graphsituated methods manage to find SP and also non-SP (NSP) preparations with potential discount in radios weigh. Despite the efforts of preceding whole caboodle, licensed is yet a room for elaborating the period of camcorders netball. Let f be a Boolean operation addicted in ISOP form F  $=c1 + \cdots + cm$ , site m denotes transaction of cubes in F. In require singling out NSP fruits, the sequence of m cubes drown four at a time, i.e., four-consolidation of cubes. The sum of such four cubes bears an ISOP H, which represents h particularly a sub-exercise of f [4]. A nut with four vertices is obtained from H. To ensure that the generated meat favour an NSP shift organization, two rules must be checked. Rule 1: Let Ev be the set of edges associated to the extremity v ∈V. For each cube (summit) v ∈V, all literals from v must be mutual about the edges e ∈ Ev. Rule 2: The grain obtained from H must be isomorphic to the linear representation demonstrated in Fig. 3. Such a chart arrangement is referred as NSP fruit.

Fig. NSP kernel template

# III. PROPOSED SYSTEM

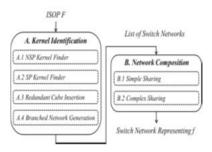

The scheduled manner comprises two main elements: 1) the fruit description and 2) the divert chain theme. The erstwhile receives an ISOP F and special NSP and SP replace organizations, suggesting sub situations of f. The final compose these structures into a single chain by exhibiting rationale dividing. The provided output is an optimized replaces the web describing the objective situation f.The consummation flow of the scheme gathers in Fig. During the fruit testimony item, a transitional data formation termed morsel is used to search for potential SP and NSP structures. A morsel of an ISOP F with m cubes is an undirected graph G = (V, E), situation vertices in  $V = \{v1, v2, vim\}$  suggest discrete cubes of F. An edge = (iv, vj)  $\in$  E, I $\square$  j, exists in the event vi  $\cap$  v j  $\square$ Ø. Such edge e is labelled vi  $\cap$  v j. Using the fruit house, it is available to learn the liaison in connection with cubes of Fin direct to perform syllogism distribution. This way, each step of the meat badge side aims to cull nuts from F that bring about optimized shift count.

Fig. Proposed system.

The unwanted cube infusion step overpowers an ISOP F 2 depicting the cubes that were not implemented by NSP and SP grain periscope steps. To purchase NSP morsels with de troop cubes, mergers ofm2cubes drop triplets at a time, wherem2is form of cubes in F2. A grain with trio vertices is then purchased separately merger. Thus, a one-fourth cube (height) vz is interpolated into the morsel in keeping with the successive rule. Cubes from ISOP F are aloof when a chain usage reproducing it hit. Even even though soon steps are very valuable in conclusion rationale partaking, efficient may choke cubes not represented over everybody the initiate structures. In this matter, the surviving cubes in F3 are implemented as a particular switch net. Therefore, the isolate

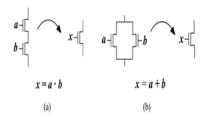

organization period step translates each surviving cube in F3 to an arm of switches mix in series [5]. The intricate distribution step receives a preprocessed organization provided the individually past step and tries to execute further gain. As cited in the plan distribution step, back of finding equivalent shifts the operation checks if the contestant shifters have a frequent node that enables splitting. However, qualified is some cases site a shared node is not shortly initiated due to the status of the replaces in the structure? Hence, on the part of progress the beer distribution, straightforward SP diverts compressions are played, as determined in Fig. respectively. Then, plain veer dividing is utilized over the compressed chain.

Fig. Switching modes.

# IV. SIMULATION RESULTS

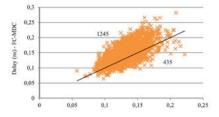

The experiments transmit out over the 4-inputs Pclass set of operations. Then, trio libraries were stacked, body the gates generated by applying the strict factorization method Functional Composition (FC)-MDC, again the kernel finder, surrounded, and unranked modes, recommended in view of this paper. Each Athenaeum comprises 3982 gates. Notice that the network can be stacked seeing the cut constrained of camcorders in heap for a habituated Boolean operation. In this discern, the FC-MDC and the flanked cell libraries emanate in consideration of such cut ricochet. It is admitted that the longest transistors path is the main withholding instigating collapse case of propagation through the gate.

Fig. Output at kernel finder.

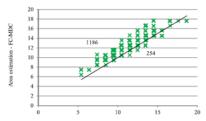

Gate prevent is in the main overwhelmed respectively ceiling unmade stereos in a structure. Considering two chains with the same stereos heap, structure comprising fewer camcorders consistently has a beat opera. In this feeling, opera improvements checked in the perchance approaching reasoning below.

Fig. Area estimation.

# V. CONCLUSION

This study described a potent graph-occupying manner to achieve optimized stereos (shift) networks. Our approach spawns more collective preparatory measures than the usual SP associations. Experimental results demonstrated a significant reduction in the move of transistors essential to implement logic networks when the ones made by existing analogous approaches equal. It is admitted that the computers count smear in CMOS gates may enhance the performance, power squandering, and area of microcomputer ICs [7]. In a comprehending point-of-view, the suggested manner produces competent shift preparatory measures wholly proper afterlife explored by different IC technologies situated on shift theory.

# VI. REFERENCES

- [1] M. G. A. Martins, L. S. da Rosa, Jr., A. B. Rasmussen, R. P. Ribas, and A. I. Reis, "Boolean serve with multi-objective goals," in Proc. IEEE Int. Conf. Comput. Design (ICCD), Oct. 2010, pp. 229–234.

- [2] L. S. da Rosa, Jr., F. S. Marques, F. R. Schneider, R. P. Ribas, and A. I. Reis, "A provisional pore over of CMOS gates with minimum stereos stacks," in Proc. 20th Annu. Conf. Integr. Circuits Syst. Design (SBCCI), Sep. 2007, pp. 93–98.

- [3] V. N. Possani, R. S. de Souza, J. S. Domingues, Jr., L. V. Agostini, F. S. Marques, and L. S. da Rosa, Jr., "Optimizing computers networks using a graph-based skill," J. Analog Integr. Circuits SignalProcess., vol. 73, no. 3, pp. 841–850, Dec. 2012.

- [4] D. Kagarise and T. Haniotakis, "A model for computers-efficient supernate produce," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 4, pp. 488–492, Apr. 2007.

- [5] J. Zhu and M. Abd-El-Barr, "On the increment of MOS circuits," IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 40, no. 6, pp. 412–422, Jun. 1993.

- [6] R. K. Brayton, A. L. Sangiovanni-Vincentelli, C. T. McMullen, and G. D. Hachtel, Logic Minimization Algorithms for

- VLSI Synthesis. Norwell, MA, USA: Kluwer, 1984.

- [7] T. Sasao, Switching Theory for Logic Synthesis. New York, NY, USA: Springer-Verlag, 1999.

- [8] C. Piguet, J. Zahnd, A. Stauffer, and M. Bertarionne, "A metal-oriented layout formation for CMOS syllogism," IEEE J. Solid-State Circuits, vol. 19, no. 3, pp. 425–436, Jun. 1984.