# Complement Encoding Scheme For Digital Signaling

#### DURGAPRASAD GUDISEVA

M.Tech Student, Dept of ECE, Chalapathi Institute of Technology, Guntur, A.P, India **CH.SANDEEP** Asst.Professor, Dept of ECE, Chalapathi Institute of Technology, Guntur, A.P, India

Abstract: Because the multiplier is really a fundamental component for applying computationally intensive applications, its architecture seriously affects their performance. We explore a Non-Redundant radix-4 Signed-Digit encoding plan extending the serial encoding Techniques. While using suggested encoding formula, we preencode the conventional coefficients and store them right into a ROM inside a condensed form. Modified Booth is really a redundant radix-4 encoding technique. As noticed in the NR4SD encoding technique, the NR4SDb form has bigger dynamic range compared to 2's complement form. A finite condition machine synchronized the information flow and also the multiplier operation but wasn't considered in the region/energy calculations. We advise encoding these coefficients within the Non-Redundant radix-4 Signed-Digit (NR4SD) form. Two typical values of N, and is definitely the MB, NR4SD and NR4SDb digits that result when using the corresponding encoding strategies to each worth of N we considered. We added a bar over the negatively signed digits to be able to distinguish them in the positively signed ones. The quantity of stored bits is equivalent to those of the traditional MB design, except which are more significant digit that requires an additional bit because it is MB encoded. When compared to preencoded MB multiplier, in which the MB encoding blocks are overlooked, the preencoded NR4SD multipliers need extra hardware to create the signals. Using an advanced programming language, we generated the pre-encoded values of B which then we kept in the ROMs of pre-encoded designs. Finally, we used Synopsys Prime Time for you to calculate power consumption. The ability dissipation from the multiplier is dramatically decreased as clock period increases since both frequency and overall load charge decrease, as the power use of the ROM is linearly decreased following a frequency reduction. Within this paper, new types of pre-encoded multipliers are explored by off-line encoding the conventional coefficients and storing them in system memory.

*Keywords:* Preencoded; MB Design; Circuits; Modified Booth Encoding; Pre-Encoded Multipliers; VLSI Implementation;

#### I. INTRODUCTION

We have to cover the dynamic selection of the 2's complement form, the most important digit is MB encoded. Regarding power dissipation, the preencoded NR4SD\_ plan consumes minimal power which, within the installments of 16 and 24 items of input width, is equivalent to the ability consumed through the pre-encoded MB design [1]. The NR4SD and NR4SDb encoding algorithms are highlighted in details, correspondingly. The coefficient B includes n = 2k bits and it is driven towards the MB encoding blocks from the ROM where it's kept in 2's complement form. Among the two inputs of those multipliers is pre-encoded in MB or perhaps in NR4SD/NR4SDb both representation. We take into account that this input develops from a group of fixed coefficients. To prevent these inverters and, thus, lessen the area/power/delay of NR4SD, NR4SDb pre-encoded multipliers, the PPGs for that NR4SD, NR4SDb multipliers specified for according to primitive NAND and NOR gates, and replaced. Thus, the region and power values for those multipliers from the designs are helpful for explorations from the suggested preencoded designs according to different memory technologies. The comparison one of the designs starts in the cheapest common

achievable clock period for those designs and continues at greater clock periods by growing the time period by step .2 ns until it reaches 4 ns. However, the ROM utilized in each evaluated design is really a standard cell and it is critical delay, area occupation and both internal and ports' load remain unchanged as clock period increases. Thus, the multiplier changes dramatically as clock period increases however the ROM doesn't change. The memory compiler of the identical library provided the physical ROMs for those coefficients. Because the ROMs needed for that pre-encoded multipliers are bigger compared to one for that conventional MB plan, access time is elevated [2]. However, the pre-encoded designs may achieve lower clock periods compared to conventional MB one since the encoding circuits which are incorporated within the critical path, are overlooked or fewer complex.

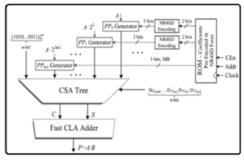

### Fig.1.Proposed system framework

## II. PROPOSED SYSTEM

How big ROM accustomed to keep categories of coefficients is considerably reduced along with the area and power use of the circuit. However, this multiplier design lacks versatility because the partial products generation unit was created particularly for several coefficients and can't be reused for an additional group [3]. The coefficients are encoded off-line according to MB or NR4SD algorithms and also the resulting items of encoding are kept in a ROM. Since our purpose would be to estimate the efficiency from the suggested multipliers, we first present overview of the traditional MB multiplier to be able to compare it using the pre-encoded schemes. We observe that the ROM data bus width equals the width of coefficient B (n bits) which outputs one coefficient on every clock cycle [4]. The brand new ROM can be used to keep the encoding signals of B and feed them in to the partial product generators on every clock cycle. The ROM width is elevated. Each digit demands three encoding bits to become kept in the ROM. Because the n-bit coefficient B needs three bits per digit when encoded in MB form, the ROM width requirement is 3n/2 bits per coefficient. Thus, the width and also the overall size the ROM are elevated by 50 % when compared to ROM from the conventional plan. The CSA tree and CLA adder were imported from Synopsys Design Ware library. The ROM for that 2's complement or preencoded coefficients is really a synchronous ROM of 512 words frequently met at DSP systems. A finite condition machine synchronized the information flow and also the multiplier operation but wasn't considered in the region/energy calculations. We advise encoding these coefficients within the Non-Redundant radix-4 Signed-Digit (NR4SD) form. The suggested pre-encoded NR4SD multiplier designs tend to be more area and power efficient when compared to conventional and pre-encoded MB designs [5]. The memory compiler of the identical library provided the physical ROMs for those coefficients. Because the ROMs needed for those pre-encoded multipliers are bigger compared to one for that conventional MB plan, access time is elevated. However, the pre-encoded designs may achieve lower clock periods compared to conventional MB one since

the encoding circuits which are incorporated within the critical path, are overlooked or fewer complex. We first compare the whole designs incorporating the needed ROMs. Then, we create a comparison one of the multipliers of schemes because they are implemented according to different encoding techniques [6]. Also, we compare the PPGs from the multipliers since they're key subcomponents occupying significant area within the multipliers.

| Design             |        | Input A             | Input B Encoding |                          | ROM           |

|--------------------|--------|---------------------|------------------|--------------------------|---------------|

|                    |        |                     | Type             | Technique                | width         |

| Conventional<br>MB |        | ement               | MB               | MB encoding              | <i>n</i> -bit |

| Pre-<br>Encoded    | MB     | 2's comple<br>n-bit | MB               | Fully Pre-Encoded        | 3n/2-bit      |

|                    | NR4SD- |                     | NR4SD-           | Partially<br>Pre-Encoded | (n+1)-bit     |

|                    | NR4SD+ |                     | NR4SD+           |                          | (n+1)-bit     |

## Fig.2.Multipliers designs

#### **III. CONCLUSION**

Within this paper, we introduce architecture of preencoded multipliers for digital signal processing applications according to off-line encoding of coefficients. Within the pre-encoded MB multiplier plan, the coefficient B is encoded off-line based on the conventional MB form. The resulting encoding signals of B are kept in a ROM. We synthesized all designs at greater clock periods targeting to understand more about their behavior under different timing constraints when it comes to area and power consumption. For every clock period, we simulated all designs using Models and 20 different teams of 512 ROM words. We observe that increases that concern the multipliers from the pre-encoded NR4SD designs within the among the conventional MB plan tend to be greater. Thus, the NR4SD-based pre-encoded multipliers incorporate a less complex partial products generation circuit. We explore the efficiency from the aforementioned pre-encoded multipliers considering how big the coefficients' ROM. Extensive experimental analysis verifies the suggested pre-encoded NR4SDmultipliers, such as the coefficients memory, tend to be more area and power efficient compared to conventional Modified Booth plan.

## IV. REFERENCES

- Z. Huang, "High-level optimization techniques for low-power multiplier design," Ph.D. dissertation, Dept. Comput. Sci., Univ. California, Los Angeles, CA, USA, 2003.

- [2] H.-Y. Lin, Y.-C. Chao, C.-H. Chen, B.-D. Liu and J.-F. Yang, "Combined 2-d transform and quantization architectures for h.264 video coders," in Proc. IEEE Int. Symp. Circuits Syst., May. 2005, vol. 2, pp. 1802–1805.

- [3] C. Xu, X. Dong, N. Jouppi, and Y. Xie, "Design implications of memristorbased rram cross-point structures," in Proc. Design, Automation Test Eur. Conf. Exhib., Mar. 2011, pp. 1–6.

- [4] Y.-E. Kim, K.-J. Cho and J.-G. Chung, "Low power small area modified booth multiplier design for predetermined coefficients," IEICE Trans. Fundam. Electron. Commun. Comput. Sci., vol. E90-A, no. 3, pp. 694–697, Mar. 2007.

- [5] K.-S. Chong, B.-H. Gwee, and J. S. Chang, "A 16-channel low-power nonuniform spaced filter bank core for digital hearing aids," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 9, pp. 853–857, Sep. 2006.

- [6] Y.-E. Kim, K.-J. Cho, J.-G. Chung, and X. Huang, "CSD-based programmable multiplier design for predetermined coefficient groups," IEICE Trans. Fundam. Electron. Commun. Comput. Sci., vol. 93, no. 1, pp. 324–326, 2010.