brought to you by CORE

Katam Ramanjaneyulu\* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.5, Issue No.2, February – March 2017, 5787-5790.

# **Reduced Peak Power Supply Using Clock-Tree Drivers**

KATAM RAMANJANEYULU M.Tech Student, Dept of ECE SRTS, Kadapa, A.P, India N.NAGA MALLIKARJUN Assistant Professor, Dept of ECE SRTS, Kadapa, A.P, India

Abstract: Power noise analysis involves the straightforward Ohm low of multiplying peak current through the power network impedance. The noise can therefore be reduced by decreasing the impedance or staying away from high current peaks. We suggested lessening the height supply current and it is time derivative by distributing with time the switching from the clock-tree motorists, while keeping low skew in the sinks from the tree. We concentrate on lowering the peak current and it is time derivative, which has additionally been treated by various techniques. The time network thus remains an all natural candidate to deal with for optimum current remedy. To acquire proper and powerful sequencing from the logic, the time skew must stay within prescribed limits, not often exceeding 5% from the clock cycle. Once the recursion goes into a node (top-lower), fork substitution happens. Once the recursion returns in the node (bottom-up), delay equalization is resolved. Considerable noise reduction was recently explained using resonant clock distribution systems, generating sinusoidal signal. Its applicability to ordinary CMOS design is questionable because the short-circuit power within the clocked devices is considerably elevated. Driver's incoming wire inherits its triplet in the driver. Within the above convention the wires connecting outputs from the leaf motorists for their loads are assumed to call home at level 3. The very first is a high-lower traversal, in which the clock-tree is built along with a small peak current is acquired. Additionally, it helps to ensure that the skew in the tree's leaves doesn't escape. This is an excellent beginning point for any second, bottom-up traversal phase, aiming at skew nullification by fine adjustments from the clock-motorists positions. The 2nd phase includes a really small effect on the height current, which was already reduced within the first phase.

*Keywords:* Peak Current; Driver; Top-Down Approach; Clock Drivers; Clock Network; Clock-Tree; Power Supply Noise; Clock-Driver;

#### I. INTRODUCTION

Our work flattens the height supply current by governing the timing from the clock signal, but avoids the above mentioned pointed out timing convergence drawback. Instead of distributing the time skew in the sinks, our method misaligns the time switching in the internal nodes from the clock-tree, without consuming the skew budget [1]. That leaves large margin later on timing convergence. The time timing of every FF ended up being allotted with a slot so that they can lessen the peak current. 17% peak current reduction was claimed. When the bottom-up traversal completes, the whole clock-tree is decided. The making of an effective power distribution network getting low resistance and inductance, and capacitance, continues to be extensively studied a 2phase top-lower and bottom-up tree construction formula was presented. It had been implemented in 40 nanometers TSMC process technology, achieving 35% to 70% clock-tree peak current reduction. The present waveform in the tree's root can precisely be derived by summing the currents attracted through the individual motorists. The formula has additionally been experimented on the real design block with 1728 FFs, in which a Clock Tree Synthesizer (CTS) of Pedal rotation has been utilized and enforced to create clock-tree topology. There's an issue in skew distributing though. To make sure a strong signal, clock-trees usually employ LVT motorists, though individuals consume high leakage current. The coherence from the clock signal at tree's internal nodes ensures small skew in the sinks. Using intraversal SPICE simulations is unacceptably time intensive. We rather characterize each clock-driver in advance after which use characteristics data rather of simulations. In electronics and particularly synchronous digital circuits, time signal is really a particular kind of signal that oscillates from a high along with a low condition and it is utilized just like a metronome to coordinate actions of digital circuits. Time signal is created with a clock generator. Although more complicated plans are utilized, the most typical clock signal is by means of a square wave having a 50% duty cycle, usually having a fixed, constant frequency [2]. Circuits while using clock signal for synchronization can become active at either the increasing edge, falling edge, or, within the situation of double data rate, in the increasing as well as in the falling edges from the clock cycle

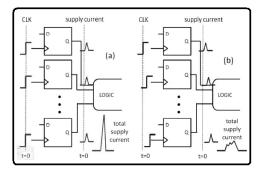

## Fig.1.Peak supply current reduction

## II. CIRCUIT DESIGN

Circuit design plays a huge role in the style of digital circuits like multiplier. First, to be sure the multiplier to operate in the preferred clock rate, the designer has to understand the delay from the critical path and also the needed duration of inserting a pipeline stage. Second, to lessen the part of the multiplier, several architectures of adders are investigated. Circuit analysis helps the designer verify the functions and performances from the adders [3]. The architecture from the adder needs to be determined first. Then the amount of the pipeline stages could be made the decision through the speed from the adder. How big the multiplier ought to be no more than possible if all of the needs could be met. Fast arithmetic requires fast circuits. Fast circuits require small size, to reduce the delay results of wires. Small size implies just one nick implementation, to reduce wire delays, and to really make it easy to implement these fast circuits included in a bigger single nick system to reduce input/output delays. The growing interest in lowpower VLSI asks, amongst others, for power efficient logic styles. Performance criteria for logic styles are circuit speed, circuit size, power dissipation, and wiring complexity in addition to ease-of-use and generality of gates in cell-based design techniques. Dynamic logic styles are frequently great for highspeed, although not for low-power circuit implementations because of the high node activity and enormous clock loads. This chapter focuses overview of various logic styles appropriate for low power. Today CMOS (Complementary Metal Oxide Semiconductor) may be the primary technology within the Semiconductor industry [4]. Most highspeed microprocessors are implemented using CMOS. Contemporary CMOS technologies are characterized by: Small minimum sized transistors, permitting dense layouts, even though the interconnect limits the density. Low Quiescent Power - The ability use of conventional CMOS circuits is basically based on the AC power brought on by the charge and relieves capacitances. Because the circuits get faster, the regularity rises along with the ability

consumption. The steady condition output is going to be in addition to the ratio from the pull-up and pulllower transistor sizes. Due to this, CMOS complementary logic doesn't need to bother about signal degradation problems in pass-transistor logic. Since the power-to-ground path only closes throughout the transition, it almost consumes no static power. The CMOS complementary gate has two function figuring out blocks an n-block along with a p-block. You will find normally 2n transistors within an n-input gate. The transistor connections for any complementary switch or transmission are reviewed. It includes an n-funnel transistor and pfunnel transistor with separate gate connections and customary source and drain connection. The control signal \$ is used towards the gate of n- tool and its complement to gate of p-device. Operation could be well described by thinking about the n and p device individually. Once the control signal \$ is low i.e. '0' both n and p products are off and output is high impedance. Similarly when \$ is high i.e. '1' both n and p products are on and input is used in output node. The related output characteristics are stated within the analysis. Several differential CMOS logic families for example cascade current switch logic happen to be suggested for CMOS circuit speed improvement. CVSL is really a differential type of logic requiring both true and complementary signals to become routed to gates. Two complementary NMOS switch structures are built after which linked to a set of PMOS mix-coupled load, which together can help to eliminate input capacitance, increase logic functionality, and often eliminate inverter circuits. Therefore, these logic families can increase speed. However, the particular benefit of CVSL circuits is under that anticipated within the original paper, as clarified. It is because the PMOS mixcoupled latch cannot be easily inverted because of the "fighting" towards the NMOS pull-lower trees. Highspeed inversion from the PMOS latch can be done only if the gate width from the PMOS is sufficiently little. However, a little gate width seriously degrades the pull-up transit time [5]. The primary concept behind CPL is using an NMOS pass-transistor network for logic organization, and removal of the PMOS latch for example cascade current switch logic (CVSL), as proven in Figure 4.5. CPL includes complementary inputs/outputs, an NMOS pass transistor logic network, and CMOS output inverters. The pass transistors and also the inverters work as pull-lower and pull-up devices. Thus the PMOS latch could be eliminated, allowing the benefit of the differential circuits to become fully utilized. Gate diffusion input (GDI)-a brand new manner of lowpower digital combinational circuit design. This

method enables reducing power consumption, propagation delay, and section of digital circuits while keeping low complexity of logic design. Passtransistor logic continues to be presented for NMOS. They derive from the model, where some control signals is used towards the gates of NMOS transistors. Another group of data signals are put on the causes of the n-transistors. A few of the primary benefits of PTL over standard CMOS design are High-speed, because of the small node capacitances Low power dissipation, because of the lower quantity of transistors Lower interconnection as a result of small area. However, most Pass-transistor logic continues to be presented for NMOS. They derive from the model, where some control signals is used towards the gates of NMOS transistors. Another group of data signals are put on the causes of the ntransistors. A brand new low-power design technique that enables solving the majority of the problems pointed out above-gate diffusion input (GDI) technique. The GDI approach enables implementation of an array of complex logic functions only using two transistors. A Credit Card Application-Specific Integrated Circuit (ASIC) is definitely an integrated circuit (IC) customized for the use, instead of meant for general-purpose use. For instance, a nick designed exclusively to operate a mobile phone is definitely an ASIC. Intermediate between ASICs and industry standard integrated circuits, such as the 7400 or even the 4000 series, are application specific standard products (ASSPs).

## III. SOFTWARE REQUIREMENT

The simulation parameters happen to be examined with the aid of the Spice oral appliance Cosmo scope for that schematic verification SPICE is really a broad function analog electronic circuit simulator. It's a dominant course which is used in IC and board level design to determine the integrity of circuit design and also to predict circuit behavior. Synopsys HSPICE is definitely an optimizing analog circuit simulator. Technology-not only steadycondition, transient, and frequency domains. HSPICE is unequaled for fast, accurate circuit and behavior simulation. It circuit-level analysis of performance. However, there were numerous free of charge and great SPICE variations, HSPICE turns into a regular of the correct circuit simulator. Because it cost lots of money and energy for placing a circuit design into fabrication, precision, and longevity of circuit simulation is really a prime factor. Furthermore, HSPICE was better supported as it is not free presumably. It's worth having to pay currency for circuit design companies for that great simulator [6]. Cosmos Scope is really a graphical waveform analyzer tool that enables you to definitely view and analyzer simulation results by means of the waveform shown on graphs, or as values display in lists.

## **IV. CONCLUSION**

Decrease in the current drop occurring in the package level, in which the inductance dominates the impedance. There, the actual resistance, capacitance, and peak current switching dI/dt are increasing up, thus growing the noise. An application implementation comment is needed. Although the top-lower and also the bottom-up are conceptually distinct phases, involving different computations, they may be taken in one recursive procedure. For this finish a 6-level tree continues to be simulated with SPICE in slow, typical, and fast corners. The sensitivity from the skew to slopes in the tree's root is presented. An answer finds appropriate locations of motorists within their branches. Driver-to driver interconnects lengths are variables, while their partial sums must satisfy branch lengths constraints, determined through the methodology of 2X level-tolevel wire length decrease. Improving the effective use of the de-coupling capacitors by growing their effective distance that's inversely proportional to dI/dt.

#### REFERENCES

- H. Jang, D. Joo, and T. Kim, "Buffer sizing and polarity assignment in clock tree synthesis for power/ground noise minimization," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 30, no. 1, pp. 96–109, 2011.

- [2] R. Samanta, G. Venkataraman, and J. Hu, "Clock buffer polarity assignment for power noise reduction," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 17, no. 6, pp. 770–780, 2009.

- [3] L. D. Smith, R. E. Anderson, and T. Roy, "Chip-package resonance in core power supply structures for a high power microprocessor," in Proc. ASME Int. Electron. Packag. Tech. Conf. Exhib., Kauai, HI, USA, 2001, p. 5.

- [4] P. Vuillod, L. Benini, A. Bogliolo, and G. De Micheli, "Clock skew optimization for peak current reduction," in Proc. 1996 IEEE Int. Symp. Low Power Electron. Design, pp. 265– 270, Press.

- [5] W.-C. D. Lam, C.-K. Koh, and C.-W. A. Tsao, "Clock scheduling for power supply noise suppression using genetic algorithm with

selective gene therapy," in Proc. IEEE 4th Int. Symp. Quality Electron. Design 2003.

[6] Y. Ryu and T. Kim, "Clock buffer polarity assignment combined with clock tree generation for power/ground noise minimization," in Proc. 2008 IEEE/ACM Int. Conf. Comput.-Aided Design, pp. 416–419.

## **AUTHOR's PROFILE**

KATAM RAMANJANEYULU, B Tech ECE CBIT, Proddatur(74.50%)

Pursuing M Tech from SRTS Kadapa.

N.Naga Mallikarjun, M.Tech, Assistant professor, Completed B.Tech from JNTUH in 2008.completed M.Tech from JNTUH in 2013.