Devsoth Rajeshwari\* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.5, Issue No.1, December – January 2017, 5590-5591.

## Mid-Level Outcome To Gain Parity-Check In Deceitful Area-Efficient Structure

DEVSOTH RAJESHWARI M.Tech Student, Dept of ECE Indur Institute of Engineering and Technology Siddipet, T.S, India V.SRINIVAS

Associate Professor, Dept of ECE Indur Institute of Engineering and Technology Siddipet, T.S, India

*Abstract:* A singular tree structure is suggested within this brief to reduce the amount of comparators along with the area-time (AT) complexity. Rather to find the precise second minimum after locating the first minimum, the suggested formula collects the candidates from the second minimum while looking for the very first minimum. The hardware complexity of these an intricate SM requires a significant portion within the overall complexity of the LDPC decoder. Furthermore, the region taken by multiple SMs gets to be more considerable inside a high-throughput decoder, as massive CN operations are carried out in parallel to improve the decoding throughput the general process includes two steps: finding MIN1 using the binary tree structure and selectingMIN2 by way of the multiplexing network controlled by IDX. Because the hardware complexity of the comparator is considerable, the prior tree-based SM can't be economical when the amount of inputs isn't small, designed for recent strong LDPC codes targeting a row degree in excess of 100. A quicker tree-based SM, denoted as SMradix, was achieved by following a mixed-radix plan. However, realizing our prime-radix computation increases comparators and multiplexors drastically.

*Keywords:* Area-Efficient Design; Digital Integrated Circuits; Low-Density Parity-Check (LDPC) Codes; Minimum Value Generation; Tree Structure;

## I. INTRODUCTION

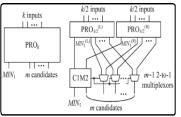

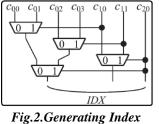

The proposed architecture reduces the number of comparators by reusing the intermediate comparison results computed for the first minimum in order to collect the candidates of the second minimum. Three C1M1 units and one 2-to-1 multiplexor are additionally used to combine two sub trees, but the serially connected block required for finding MIN2 in SMsort is removed so that the critical delay of SMtree is reduced. Depending on the comparison result of the C1M2, the PROk decides m - 1 candidates for the second minimum by selecting either the candidate set [1]. In short, a PROk unit can be realized with two PROk/2 units, one comparator and m + 1 2-to-1 multiplexors. It is apparent that a PRO2 unit processing two inputs is identical to the C1M2 unit. the proposed SM, referred to as SMpro, is constructed to process eight inputs, where a PRO8 unit is followed by a tree structure composed of two C1M1 units to find MIN2 among the three candidates produced in the PRO8 unit [2]. As the proposed structure requires additional comparison steps to find the second minimum among m candidates, the delay of SMpro is between those of the previous sorting- and treebased SMs. We have presented a novel tree structure that finds the first two minima among many inputs. In the proposed structure, the candidates of the second minimum are collected by utilizing the results of comparisons performed for the first minimum.

## Fig.1.Proposed system architecture II. METHODOLOGY

Generally, the hardware block that finds the very first two minima, that is known as a searching module (SM), could be implemented by using the balanced tree structure [3]. To get rid of the complicated hyperbolic computations needed within the sum-product decoding formula, recent LDPC decoders are implemented in line with the min-sum (MS) decoding formula. A singular tree structure is suggested within this brief to reduce the amount of comparators along with the area-time (AT) complexity. Rather to find the precise second minimum after locating the first minimum, the suggested formula collects the candidates from the second minimum while looking for the very first minimum. However, the C1M2 unit consists of one comparator and 2 w-bit 2-to-1 multiplexors to find out both bigger and smaller sized values. Furthermore, each control bit is shadowed to prevent distorting test configurations in the center of test data shifting. The Cisco kid registers are updated in the finish of every pattern upload. Thus, whenever a test pattern launches a brand new test configuration, the related control data have to be packed with its predecessor. The SMtree created for eight inputs is exemplified, in which the

processing occasions for MIN1 and MIN2 are nearly as good as both are in line with the hierarchical tree structure. Hence, it's important to build up a brand new SM that can help to eliminate comparators and keep the critical delay under that of SMsort [4]. To get rid of the complex k-to-1 multiplexors, the suggested architecture introduces a fundamental unit, i.e., PROk, which creates the first the least k inputs and m  $(= \log 2 k)$  candidates for that second minimum. When k isn't a power 2, this kind of SM is possible by pruning some leaf nodes from the balanced SM constructed with 2m inputs where 2m > k, as described in the last literatures. It estimates the resultant effect on test time, when we choose to proceed with merging. Clearly, when the setup class isn't merged using the base, it might reduce test time as there's you don't need to send extra control data developing a brand new test configuration. Because the suggested architecture completely removes the 2m-to-1 multiplexors which are inevitable in SMsort, the critical delay of SMpro is a lot smaller sized compared to SMsort [5]. Additionally, the 2nd minimum is chosen in the candidates by transporting out a couple of comparison steps. It seems, however, that the amount of test configurations, and therefore the quantity of control data one should employ and transfer between your ATE and DSR address registers, may visibly impact test scheduling and also the resultant test time. Consequently, we start this paper by analyzing three alternative schemes you can use to upload control bits and show the way they determine the ultimate SoC test logic architecture. Because of the effective error-correcting capacity, low-density parity-check (LDPC) codes have broadly been put on wireless communication systems, personal area systems, and solid-condition drives. Because the suggested structure eliminates the big-sized multiplexing systems, it increases the AT complexity considerably when compared with individuals from the previous condition-of-the art SMs. Observe that the delay of SMpro is very comparable with this of SMtree [6]. Observe that the critical delay of SMsort is definitely bigger than individuals from the other SMs because of the complex 2m-to-1 multiplexing systems.

III. CONCLUSION

The hardware complexity of these an intricate SM requires a significant portion within the overall complexity of the LDPC decoder. Furthermore, the region taken by multiple SMs gets to be more

considerable inside a high-throughput decoder, as massive CN operations are carried out in parallel to improve the decoding throughput. Consequently, the SMsort necessitates nine comparators, three 8to-1 multiplexors, and nine 2-to-1 multiplexors to process eight inputs and in addition is affected with the lengthy critical delay brought on by the serially connected structure. Three C1M1 units and something 2-to-1 multiplexor are furthermore accustomed to combine two sub trees, however the serially connected block needed for locating MIN2 in SMsort is taken away so the critical delay of SMtree is reduced to 3TC 5TM2. The tree-based architectures described are attractive when it comes to computational delay; however they necessitate a lot of hardware complexity. For any high-speed realization, the tree-based SM architecture, known as SMtree, was suggested. The SMtree created for eight inputs is exemplified. The candidate set is definitely built by reusing the comparison results performed for that first minimum. When compared to previous SM, the suggested SM reduces the amount of comparators by greater than 40%.

## IV. REFERENCES

- IEEE Standard for Local and Metropolitan Area Networks Part 15.3: Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specifications for High Rate Wireless Personal Area Networks (WPANs), IEEE Std. 802.15.3c-2009, Oct. 2009.

- [2] Y. Sun and J. R. Cavallaro, "VLSI architecture for layered decoding of QC-LDPC codes with high circulant weight," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 21, no. 10, pp. 1960– 1964, Oct. 2013.

- [3] Y.-L. Ueng, B.-J. Yang, C.-J. Yang, H.-C. Lee, and J.-D. Yang, "An efficient multistandard LDPC decoder design using hardware-friendly shuffle decoding," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 60, no. 3, pp. 743–756, Mar. 2013.

- [4] C.-L. Wey, M.-D. Shieh, and S.-Y. Lin, "Algorithms of finding the first two minimum values and their hardware implementation," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 11, pp. 3430– 3437, Dec. 2008.

- [5] IEEE Standard for Local and Metropolitan Area Networks Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications, IEEE Std. 802.11n-2009, Oct. 2009.

- [6] J. Kim, D. Lee, and W. Sung, "Performance of rate 0.96 (68254, 65536) EG-LDPC code for NAND Flash memory error correction," in Proc. IEEE ICC, 2012, pp. 7029–7033.