Farha Anjum\* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.5, Issue No.1, December – January 2017, 5443-5446.

# Design Of 4-Bit MCC Adders To Improve Processor Speed In VLSI

Mrs. FARHA ANJUM

Assistant Professor in ECE Dept and Research Scholar, Nagole Institute of Technology and Science, Hyderabad, India.

**Dr. ANIL KUMAR SHARMA** Professor in ECE Dept SunRise University, Alwar, Rajasthan, India. Mr. MOHAMMAD ILIYAS

Assistant Professor in ECE Dept and Research Scholar, Nawab Shah Alam Khan College of Engineering and , Technology, Hyderabad, India.

Dr. R. MURALI PRASAD Professor in ECE Dept, Vardhaman College of Engineering, Hyderabad, India

Abstract: Enhance the processer speed by diminishing the convey delay furthermore decreased the power utilization. The testing paradigm of profound submicron advancements is low-power and fast correspondence computerized flag preparing chips. The execution of numerous applications as advanced flag handling relies on the execution of the math circuits to execute complex Algorithms. Quick number juggling calculation cells including adders are the most often and generally utilized circuits as a part of extensive scale combination (VLSI) frameworks. More over decrease of the power utilization is the basic worry in this field. Presently now a days there is at colossal interest for compact electronic gadgets, the architects are headed to take a stab at littler silicon region, higher speed, and longer battery life. Viper is the center component of complex number-crunching circuits like expansion, duplication, division, exponentiation, et cetera. Static CMOS circuits comprised of a corresponding PMOS as draw up and NMOS as draw down networks. Majority of the circuit outlines are as yet utilizing this as it gives low commotion, low power and quick speed. The principle preferred standpoint of CMOS over NMOS and bipolar is much littler power dissemination. Rationed circuit supplanted the pull up PMOS arrange by associating it to a ground. By interfacing PMOS to a ground, there is an extraordinary diminishment in the draw up transistors utilized when utilized as a part of an unpredictable plan. Dynamic circuit is like ratioed circuit however the PMOS is attached to a clock. PMOS is not generally on as it is controlled by the deliberately arranged clock. Range, deferral and power are the three for the most part acknowledged outline measurements to quantify the nature of a circuit or to think about different styles of circuits. The most generally utilized rationale [1] style is static correlative CMOS. The static CMOS style is truly an expansion of the static CMOS inverter to various data sources. In audit, the essential favorable position of the CMOS structure is vigor (i.e., low affectability to clamor), great execution, and low power utilization (with no static power utilization). As we will see, the greater part of those properties are persisted to substantial fan-in rationale entryways actualized utilizing a similar circuit topology. In this work, we endeavor to address these weaknesses of utilizing DFTL as a part of rationale operations with an examination on the ideal measuring proportion and a "timing window" strategy. For correlation purposes, the vitality versus delay (E-D) conduct of indistinguishable 64-bit Sklansky convey combine tree executed in DFTL, CDL, dynamic rationale, and static rationale doors is broke down.

Keywords: VLSI; MCC Adder; CLA;

#### I. INTRODUCTION

Expansion is the most ordinarily utilized numbercrunching operation furthermore the speedconstraining component to make quicker VLSI processors. With the fast development of the convenient gadgets showcase in the most recent couple of years, the accentuation in VLSI configuration is moving from rapid to low power. Compact applications like remote correspondence and imaging frameworks (computerized journals, savvy cards) request fast calculations, complex functionalities, and frequently constant handling capacities alongside low power utilization. Conventional ways to deal with minimizing the power utilization of static corresponding metaloxide semiconductor (CMOS) rationale systems have upheld direct decrease in the supply voltage.

Since the dynamic power is relative to the square of the supply voltage, this is the best strategy for power decrease. The subsequent increment in deferral can be successfully remunerated through expanded information way parallelism in uncommon reason flag handling applications and via cautious transistor measuring [1], [2]. In a few circumstances it has been suggested that the limit voltage of the transistors be decreased to enhance the circuit execution [3], [4]. Be that as it may, the static power part of the power scattering has a converse exponential reliance on the edge voltage. This infers diminishing the edge voltage could bring about a critical increment in the static power part. Philosophies for minimizing the whole of static and element vitality utilization all in all reason CMOS circuits have been proposed in [5-7]. Add up to power is minimized through watchful

choice of supply and edge voltage qualities and gadget sizes with the end goal that the spillage and exchanging parts of the dispersal are equivalent. The utilization of double edge voltages for power decrease has been inspected in [8] and [9]. In both the techniques, every one of the transistors in the circuit are at first set to have a low edge voltage. Domino CMOS [1] has turned into the predominant rationale family for elite CMOS applications and it is broadly utilized as a part of best in class processors because of its fast abilities. The downside of domino CMOS is that it gives just non-reversing capacities as a result of its monotonic nature. Double Rail Domino rationale, (otherwise called timed Cascade voltage switch rationale [2]) where both polarities of the yield are produced, gives a hearty answer for this issue.

The MCC is an effective and generally acknowledged outline way to deal with build CLA adders. In this brief, we have display new Manchester configuration style that depends on two autonomous convey chains. Every chain processes, in parallel with the other, half of the conveys. Thusly, the speed execution is essentially enhanced concerning that of the standard MCC topology.

Adders are the rationale circuits intended to perform rapid number juggling operations and are critical parts in advanced frameworks due to their broad use in other essential operations, for example, subtraction, increase and division. In numerous PCs and different sorts of processors, adders are utilized not just as a part of the math rationale unit, additionally in different parts of the processor, where they are utilized to ascertain addresses, table files, and same sort of operations. Domino rationale circuits are more power productive and helpfully quicker, so these circuits have a large portion of the transistor number regarding correlative static circuits. Domino rationale is fundamentally a dynamic rationale circuit took after by a static inverter and having a capacitor as a heap. The clock flag is utilized to control the operation of domino rationale circuit. The yield of the dynamic rationale circuit is put away in the parasitic capacitance which is found just before the static inverter. The parasitic capacitance just stores the yield voltage and passes it to the following state which is the yield phase of the domino circuit and put away in the heap capacitor. The dynamic rationale circuit requires two stages. The primary stage, when Clock is low, is known as the pre-charge stage and the second stage, when Clock is high, is known as the assessment stage. In the setup stage, the yield is driven high genuinely (regardless of the estimations of the data sources).

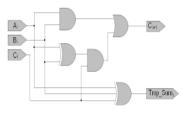

# Fig i: carry and aggregate era

In this circuit, the 2 inside signs Pi and Gi are given by:  $Pi = Ai \bigoplus Bi \dots ...(1)$

$$Gi = AiBi \dots \dots (2)$$

The yield aggregate and convey can be characterized as : i Pi Ci  $S = \bigoplus \dots (3)$

$$Ci + 1 = Gi + PiCi \dots (4)$$

Gi is known as the convey Generate motion since a convey (Ci+1) is produced at whatever point Gi =1, paying little respect to the information convey (Ci). Pi is known as the convey proliferate motion since at whatever point Pi =1, the info convey is engendered to the yield convey, i.e., Ci+1. = Ci(take note of that at whatever point Pi = 1, Gi = 0). Processing the estimations of Pi and Gi just rely on upon the information operand bits (Ai and Bi) as clear from the Figure and conditions. Hence, these signs settle to their enduring state esteem after the proliferation through their particular doors. Figured estimations of all the Pi's are legitimate one XORdoor delay after the operands An and B are made substantial. Registered estimations of all the Gi's are legitimate one AND-door delay after the operands An and B are made substantial. The Boolean articulation of the convey yields of different stages can be composed as takes after:

C1 = G0 + P0C0

C2 = G1 + P1C1 = G1 + P1 (G0 + P0C0) = G1 + P1G0 + P1P0C0

C3 = G2 + P2C2 = G2 + P2G1 + P2P1G0 + P2P1P0C0

C4 = G3 + P3C3 = G3 + P3G2 + P3P2G1 + P3P2P1G0 + P3P2P1P0C0

When all is said in done, the i th carry yield is communicated in the frame Ci = Fi (P's, G's, C0). At the end of the day, every convey flag is communicated as an immediate SOP capacity of C0 as opposed to its first convey flag.

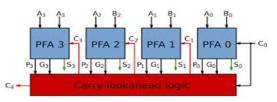

Fig ii. 4-Bit Manchester Carry Chain

The Manchester Carry-Chain Adder is a chain of pass-transistors that are utilized to actualize the convey chain. Amid pre charge, every single transitional hub (e.g. Cout0) are charged to  $V_{dd}$ . A<sub>mid</sub> the assessment stage, Cout\_k is released if there is an approaching convey Cin0 and the past spread signs (P0...Pk-1) are high. Just 4 dissemination capacitances are available at every hub, except the dispersed RC-nature of the chain brings about a post pone that is quadratic with the quantity of bits. Transistor estimating was performed to enhance execution. The points of interest are expounded on in the plan procedure segment. The Manchester convey chain was outlined utilizing dynamic rationale and executes the accompanying legitimate capacity:

$Co_i = G_i + P_i Co_{i-1}$  where Co is the do.

# II. DESIGN STRATEGY

The fortunate thing about Manchester Carry Chains is that there is no entryway between stages. Just 4 dispersion capacitances are available at every hub the terrible news is that the quantity of arrangement transistors increments with the quantity of stages (the basic way includes an arrangement proliferate transistor for every piece); so the deferral will develop like n2.The most pessimistic scenario delay relies on upon the era of convey Propagate signals.

Transistors were estimated in the accompanying way to enhance execution:

Consider the most pessimistic scenario postponement of the accompanying convey chain:

Fig iii: 4bit MCC Elmore postponement is given by

$$t_p = 0.69 \left( \sum_{i=1}^{N} C_i \right) \left( \sum_{j=1}^{i} R_j \right)$$

In this manner, the deferral is

$\label{eq:tp} \begin{array}{l} tp = 0.69(R1C1 + (R1 + R2)C2 + (R1 + R2 + R3)C3 + \\ (R1 + R2 + R3 + R4)C4 + (R1 + R2 + R3 + R4 + R5)C5 + \\ (R1 + R2 + R3 + R4 + R5 + R6)C6. \end{array}$

Since R6 shows up 6 times in the expression, it bodes well to minimize this first when we decrease R by an element of k, capacitance at every stage increments by a variable of k and region is expanded. At k = 1.5, range is expanded by 3.5x BUT deferral is decreased by 40%. This is a flawless case of the exchange off amongst speed and region. Transistor estimating was outlined with the end goal that the resistance of each successive transistor in the chain was somewhat higher than the last to minimize delay (by an element of 1.5 - diminishing postponement by 40% as ascertained utilizing Elmore's deferral). The draw up transistors were measured correspondingly to give the suitable imperviousness to their individual draw down transistors. The test seat schematic and reenactment results are underneath. Because of the huge number of signs, just the yields are shown as this gives us enough data about the postponements brought about by the circuit.

# III. CONCLUSION

A fast and a productive 8 bit Manchester Carry Chain actualized in domino CMOS rationale is reasonable for Carry Look-Ahead Adders in processor applications is examined in this venture. This circuit is outlined and reenacted utilizing MENTOR-GRAPHICS programming. This plan acknowledges better change in decreasing the deferral by presenting parallelism idea in convey chains. Therefore, the 2 isolate convey chains in particular odd convey chain and even convey chain work in parallel along these lines expands speed of operation by lessening the deferral significantly contrasted and 4 bit MCC. Consequently this 8 bit convey chain is more productive and can work at low supply voltages with rapid, accordingly making this convey chain reasonable for the vast majority of the fast processor applications. This rapid Manchester Carry Cain is found to have a defer not exactly contrasted with routine 4 bit MCC delay. Despite the fact that the postponement of 8 bit MCC gets diminished, number of transistors gets expanded in the rapid 8 bit Manchester Carry Chain. As a further work decreasing the zone of this chain and further lessening the postponement by examining this outline in submicron innovation and executing it in a variable bits like 16 bit, 32 bit Manchester Carry Chain in multi yield domino CMOS rationale can be considered.

#### IV. FUTURE SCOPE

We plan our rationale circuit by utilizing transmission door rationale will minimize number of transistors, Minimize every interior capacitance, by minimizing the dynamic range of the transistors, and in this way minimizing power.

# **AUTHOR's PROFILE**

**Mrs. Farha Anjum** received M.Tech in VLSI SD from JNTUH and having more than 8 years of experience in both teaching and industry, currently pursuing Ph.D. at SRU and

working as an Asst. Professor at Nagole Institute of Technology and Science, Hyderabad, India.

**Mohammad Iliyas** received M.Tech. in VLSI SD from JNTUH, and having more than 09 years of experience in both teaching and industry, currently pursuing Ph.D. at SRU and

working as an Asst. Professor at NSAKCET, Hyderabad, India.

**Dr. Anil Kumar Sharma** received his Ph.D in 2011 and having more than 30 years of experience in teaching and industry. Currently he is working as Professor in ECE department at

SRU, Alwar, Rajasthan.

**Dr. R. Murali Prasad** received his PhD from JNTUA, and having more than 22 years of teaching experience. Currently he is working as Professor at Vardhaman College of

Engineering, Hyderabad, India