Sadik\* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.4, Issue No.6, October - November 2016, 4937-4939.

# Introducing An 150NM Technique To Decrease Average Power Consumption

**SADIK**

P.OSMAN

M.Tech Student, Dept of ECE Vidya Jyothi Institute of Engineering & Technology Ongole, A.P, India Associate Professor, Dept of ECE Vidya Jyothi Institute of Engineering & Technology Ongole, A.P, India

Abstract: In the present paper, we advise the style of the entire subtract or using GDI technique that will consume lesser power, exhibit greater speed therefore delivering a much better power delay product plus a reduced transistor count. Gate Diffusion Input (GDI) method is dependent on the effective use of an easy cell that you can use for low power digital circuits. This paper proposes the style of a power efficient, high-speed and occasional power full subtract or using Gate Diffusion Input (GDI) technique. The whole design continues to be performed in 150nm technology as well as on comparison having a full subtract or using the conventional CMOS transistors, transmission gates and Complementary Pass-Transistor Logic (CPL), correspondingly it's been discovered that there's a great deal of decrease in Average Power consumption (Pavg), delay time in addition to Power Delay Product (PDP). This process enables decrease in power consumption, propagation delay and transistor count of digital circuit. The technique may be used to minimize the amount of transistors when compared with conventional Complementary Passtransistor Logic (CPL) and Dual Pass transistor Logic (DPL) CMOS design. Pavg is as little as 13.96nW as the delay time is discovered to be 18.02pico second therefore giving a PDP as little as 2.51x10-19 Joule for 1 volt power. Additionally for this there's a substantial decrease in transistor count when compared with traditional full subtract or employing CMOS transistors, transmission gates and CPL, accordingly implying minimization of area. The simulation from the suggested design continues to be transported in Tanner SPICE and also the layout continues to be developed in Micro wind.

Keywords: Gate Diffusion Input (GDI) Technique; Low Power; High Speed; Power Delay Product (PDP); Transistor Count; Area;

### I. INTRODUCTION

However, recently power consumption has been given equal importance. The reason behind this type of altering trend is attributed most likely because of the rapid rise in portable computers and wireless communication systems which demand high-speed computations and sophisticated functionality with low power consumption. Additionally for this high end processors consume severe power which boosts the cost connected with packaging and cooling [1]. It's been discovered that every 10o increase in operating temperature roughly doubles the failure rate of components comprised of Plastic because of several Plastic failure mechanisms for example thermal runaway, junction diffusion, electro migration diffusion, electrical parameter shift, package related failure and Plastic interconnect failure. Therefore, for more optimization of performance of the full subtract or when it comes to power consumption, delay time in addition to Power Delay Product (PDP), a brand new low power, high-speed energyefficient full subtract or has been suggested using Gate Diffusion Input (GDI) technique. GDI is really a novel modus operandi for low power digital circuits. The technique may be used to minimize the amount of transistors when compared with conventional Complementary Pass-transistor Logic (CPL) and Dual Pass transistor Logic (DPL) CMOS design. The reason behind this type of altering trend is attributed most likely because of the rapid rise in portable computers and wireless communication systems which demand high-speed computations and sophisticated functionality with low power consumption. Additionally for this high end processors consume severe power which boosts the cost connected with packaging and cooling. Subsequently there's a boost in the ability density of VLSI chips therefore disturbing the reliability.

## II. PRELIMINARIES

Gate Diffusion Input (GDI) method is dependent on the effective use of an easy cell that you can use for low power digital circuits. This method is implemented in twin-well CMOS or Plastic on Insulator (SOI) technologies. Within this process, the bulks of both NMOS and PMOS transistors are hardwired for their diffusions to lessen the majority effect that's dependence of threshold current on source-to-bulk current. By using this procedure power consumption could be reduced together with delay time therefore delivering a lower power delay product. Consequently part of the circuit is minimized. It ought to be noted that although the circuit resembles with standard CMOS inverter, there are specific important variations when compared with conventional one [2]. The GDI cell contains 3 inputs- P the input towards the outer diffusion node from the PMOS transistor isn't

linked to Vdd while N the input towards the outer diffusion node from the NMOS transistor isn't linked to GND, and G the common gate input of both NMOS and PMOS transistors. The Out node the common diffusion of both transistors might be utilized as input or output port with respect to the circuit configuration. The ports P and N delivers 2 extra pins which yield the GDI design more compliant when compared to a CMOS design. The primary benefit of GDI cell is the fact that a large number of functions could be transported out using fundamental GDI cell. The GDI gates tend to be more compact and versatile when compared with static CMOS gates and also have really low leakage current. The style of a XOR gate according to GDI procedure, it has two GDI cells where the first cell functions like a fundamental inverter while for that second cell 'x' is offered being an input to port P from the GDI cell whereas 'y' is offered being an input to port G and also the creation of the very first cell is offered being an input to port N from the second cell. The style of an AND gate according to GDI method, it takes just one GDI cell where the supply of the PMOS that's port P is linked to GND along with a is offered being an input to port G while port N is provided input B. The OR gate includes a single GDI cell, where port P is offered a port B, port G a port some time port N is provided with Vdd. The style of the NOT gate according to GDI procedure is comparable to what standard CMOS inverter quite apparent [3].

### III. METHODOLOGY

A complete subtract or is really a combinational circuit which performs subtraction on 3 bits that's minuend bit, subtrahend bit and also the borrow bit in the previous stage [4]. In the present paper, we advise the style of the entire subtract or using GDI technique that will consume lesser power, exhibit greater speed therefore delivering a much better power delay product plus a reduced transistor count. Gate Diffusion Input (GDI) method is dependent on the effective use of an easy cell that you can use for low power digital circuits. This method is implemented in twin-well CMOS or Plastic on Insulator (SOI) technologies. Within this process, the bulks of both NMOS and PMOS transistors are hardwired for their diffusions to lessen the majority effect that's dependence of threshold current on source-to-bulk current. The style of the AND, XOR, OR and never gates using GDI procedure was already discussed. With such logic gates, we advise a brand new circuit style of the entire subtract or. The suggested full subtract or continues to be simulated with all of mixtures of inputs with go up and down duration of .1ns, correspondingly. The circuit operates satisfactorily at an energy supply current of just one volt. The heart beat width, low some time and about time

continues to be come to be 100 ns, correspondingly. Schematic for that suggested circuit happen to be done using Tanner S-Edit in 150nm technology using BSIM3 Ver.3.3... Schematics are utilized to have the net list from the suggested circuit, and net list can be used for simulation and test [5].

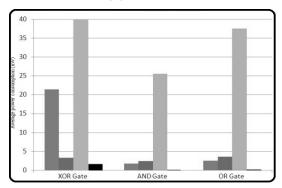

Fig.1.Performance of the system

### IV. CONCLUSION

The present work proposes the style of a complete subtract or using Gate Diffusion Input (GDI) procedure which on simulation has been discovered to eat low power along with lesser delay some time and less transistors while keeping proper outputcurrent swing. To be able to establish we've got the technology independence the current continues to be performed in 150nm technology using Tanner SPICE and also the layout continues to be concocted in Micro wind. Comparisons with standard CMOS, transmission gate and CPL techniques demonstrated a decrease in relation to transistor count, when it comes to average power consumption, when it comes to delay some time and a substantial when it comes to power delay product, correspondingly. In addition, depreciation in area is reaped when judged against a complete subtract or composed following a popular CMOS gates approach, transmission and CPL, proportionately. Due to the significant minimization of power delay product, transistor count and area the suggested logic could be helpful in portable and occasional power applications. Gate Diffusion Input (GDI) method is dependent on the effective use of an easy cell that you can use for low power digital circuits. This method is implemented in twin-well CMOS or Plastic on Insulator (SOI) technologies. Within this process, the bulks of both NMOS and PMOS transistors are hardwired for their diffusions to lessen the majority effect that's dependence of threshold current on source-to-bulk current.

# V. REFERENCES

- [1] N. Weste and K. Eshraghian, Principles of CMOS digital design. Reading, MA: Addison-Wesley, pp. 304–307.

- [2] Sung-Mo Kang and Yusuf Leblebici, CMOS Digital Integrated Circuits- Analysis and Design, 3rd ed., Tata Mc Graw-Hill ed., pp. 115-129, 211-214

- [3] K. Roy, S. Mukhopadhyay, H. Mahmoodi-Meimand, "Leakage Current Mechanisms and Leakage Reduction Techniques in Deep- Submicrometer CMOS Circuits", Proceedings of the IEEE, vol. 91, no. 2, Feb. 2003

- [4] V. Adler and E. G. Friedman, "Delay and power expressions for a CMOS inverter driving a resistive-capacitive load," Analog Integrat. Circuits Signal Process, vol. 14, pp. 29–39, 1997.

- [5] Maurus Cappa and V. Carl Hamacher, "An Augmented Iterative Array for High-Speed Binary Division", IEEE Transaction on computers, vol.c-22, no.-2, February 1973