Shaik Mahaboob Basha\* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.4, Issue No.6, October – November 2016, 4720-4722.

# Anisotropic Strategy To Achieve The Decrease In Blur And Improve In Edge Information

SHAIK MAHABOOB BASHA M.Tech Student, Dept of ECE SKR College of Engineering & Technology Nellore, Andhra Pradesh, India L VIDYA SAGAR Assistant Professor, Dept of ECE SKR College of Engineering & Technology Nellore, Andhra Pradesh, India

*Abstract:* The anisotropic weighting model is made to catch more details in horizontal than vertical directions. The filter-based compensation methodology features a Palladian and spatial sharpening filters that are designed to enhance the edge information and lower the blurring effect. Additionally, the hardware cost was effectively reduced by hardware discussing and reconfigurable design techniques. Within this paper, a minimal-complexity color interpolation formula is suggested for that VLSI implementation in tangible-time applications. The suggested novel formula includes an advantage detector, an anisotropic weighting model along with a filter-based compensator. The VLSI architecture from the suggested design achieves 200 MHz with 5.2 K gate counts, and it is core area synthesized with a CMOS process. In contrast to the prior low-complexity techniques, the work not just reduces gate counts or power consumption, but additionally increases the average CPSNR quality by greater than 1.6 dB. By analyzing the parameters of those three eco-friendly color interpolation models, it's clearly the sign of the compensation for eco-friendly color is really a spatial sharpening filter.

*Keywords:* Camera; Charge-Coupled Device (CCD); Color Filter Array (CFA); Color Interpolation; Demo Sacking; Palladian Sharpening Filter

## I. INTRODUCTION

These tools are produced by a CCD or perhaps a CMOS image sensor that may capture images by color filter array (CFA) technique. The red (R), eco-friendly (G), and blue (B) colors are sampled as you color in every pixel. One filters arrays known as Bayer CFA, by which two colors have disappeared in every pixel. An adaptive color interpolation technique that used a couple-D in your area stationary Gaussian process as well as an edge indicator was suggested by Chang et al. A minimal-complexity interpolation way in which used an easy image model was suggested by Pei et al. A gradient-base plan having a Gaussian lowpass filter to boost the performance from the color interpolation was suggested by Yun et al. Our prime-quality color interpolation algorithms, pointed out above made great contributions in CFA images correction [1]. However, extremely highquality color interpolation algorithms possess the characteristics of high complexity and memory requirement. In addition, these algorithms are challenging be recognized using VLSI technique. A competent color interpolation processor according to edge-direction weighting and native gain approach techniques was suggested by Hsia et al. The performance of the design was improved with a pipeline schedule and time-discussing techniques. For VLSI implementation, the nick area was greatly elevated by realizing these dividers and multipliers because of the high complexity and hardware cost. Hence, a manuscript low-cost, highoccasional-memory-requirement quality, and adaptive interpolation edge-enhanced color processor is suggested within this paper. First, a register bank was put in the suggested interpolator to supply 15 CFA pixels in tangible-here we are at one eco-friendly (G) and three red/blue (RB) interpolators processing in every cycle. Second, a minimal-complexity edge detector was produced to boost the advantage information. It used only addition, subtraction, and absolute operations to get edge information. Third, a manuscript the anisotropic weighting model was created for that suggested color interpolator. It may improve the caliber of the interpolated image by obtaining more details in the horizontal direction compared to vertical without adding line-buffer memory. 4th, the suggested filter design is capable of a high quality from the interpolated images since it uses various colors from the original CFA pixels and double interpolated eco-friendly pixels as aspects of filters instead of single color of original CFA pixels and single color pixel to pay the interpolated pixel as presented [2].

# II. PROPOSED METHOD

The suggested novel color interpolation formula consists of a minimal-complexity edge recognition, a eco-friendly color interpolation, along with a redblue color interpolation techniques. Each color is interpolated by different methodologies based on the relative locations and reference neighboring samples. To be able to uncover the advantage information by low-complexity methodology, the main difference within the vertical (DV) and horizontal (DH) directions were utilized. The relative locations and reference neighboring RGB pixels are proven. To be able to improve the caliber of interpolated images, an anisotropic weighting model was produced with this design. To be able to

lessen the computing resource from the suggested color interpolation formula, all division operations were substituted with shift operations. Very much the same, to rebuild the eco-friendly color in CFA format image, there's two different causes for interpolating. Additionally, the of TD, DH, and DV may be used to adaptively select among the three eco-friendly color interpolation models, without edge enhancement, edge enhancement in horizontal direction, and edge enhancement in vertical direction, because the interpolation model based on the edge information neighboring round the pixel [3]. By analyzing the parameters of those three ecofriendly color interpolation models, it's clearly the sign of the compensation for eco-friendly color is really a spatial sharpening filter. This spatial sharpening filter can efficiently lessen the blurring effect. Furthermore, the advantage information could be enhanced efficiently through the suggested adaptive edge enhancement technique. To rebuild the blue and red colors in CFA format image, you should make use of the information from the four neighboring eco-friendly colors. By analyzing the parameters of those interpolation models getting three R and B colors, it may be observed that the options from the compensation for R and B colors are Palladian filters. The parameters from the suggested G, R, and B interpolation equations are made as 1/2, 1/4, 1/8, and threeOr8. It possesses a cost-efficient base for VLSI implementation by replacing the multipliers and dividers using the shifters and adders.

# III. IMPLEMENTATION

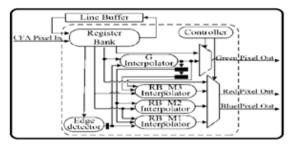

The block diagram from the VLSI architecture for that suggested color interpolation processor, it includes seven primary blocks: a register bank, an advantage detector, a eco-friendly color interpolator (G interpolator), a blue and red colors interpolator model 1 (RB M1 interpolator), blue and red colors interpolator model 2 (RB\_M2 interpolator), a blue and red colors interpolator model 3 (RB\_M3 interpolator), along with a controller. The register bank is built to real-time provide 15 pixels in CFA format for processing the G interpolator and three RB interpolators during each cycle. With the addition of this register bank, the suggested color interpolation processor achieves the memory access through pixel in and pixel out [4]. The architecture from the suggested edge detector, it includes six absolute sub tractors and five adders (Add). The eight input signals receive their inputs in the register bank. Within this paper, a reconfigurable technique was utilized to create the hardware architecture from the ecofriendly color interpolator. It includes eight adders, one subtract or, four multiplexers, and five shifters. utilizing reconfigurable technique, By the suggested eco-friendly color interpolator has got the characteristics of inexpensive, high versatility and performance. To be able to shorten the critical path and enhance the design performance, three registers were put in this architecture. Hence, the reconfigurable technique may be used to design the hardware architecture from the blue and red colors interpolator. The controller is implemented with a finite condition machine (FSM) consecutive circuit. It offers control signals towards the multiplexer for choosing input data for that interpolators and is capable of doing delivering reconfigurable control signals for altering the architecture from the interpolators. Furthermore, the controller must monitor its input and output data access using the memory to suit the performance of pixel-in and pixel-out. Finally, the suggested color interpolation processor achieves high end and throughput. To be able to compare the performance from the previous low-complexity color interpolation algorithms with this particular work, the Mat lab tool was utilized to compute the CPSNR and S-CIELAB values through the original golden images and also the interpolated images [5]. The suggested color interpolation processor was developed using Virology hardware description language (Highdensity lipoprotein) and synthesized while using electronic design automation (EDA) tool Design Vision according to TSMC .18 µm process standard cells.

# IV. CONCLUSION

The controller is implemented with a finite condition machine (FSM) consecutive circuit. It offers control signals towards the multiplexer for choosing input data for that interpolators and is capable of doing delivering reconfigurable control signals for altering the architecture from the interpolators. Within this paper, a manuscript color interpolation formula is suggested to build up a minimal-cost, low-power, high end, and quality color interpolation processor legitimate-time video applications. By analyzing the parameters of those three eco-friendly color interpolation models, it's clearly the sign of the compensation for ecofriendly color is really a spatial sharpening filter. An anisotropic weighting model, an advantage detector, Laplacian and sharpening filters happen to be accustomed to lessen the memory requirement and improve the caliber of the pictures.

#### V. REFERENCES

[1] Y. H. Shiau, P. Y. Chen, and C. W. Chang, "An area-efficient color demosaicking scheme for VLSI architecture," International Journal of Innovative Computing, Information and Control, Vol.7, No.4, pp.1739-1752, Apr. 2011.

[2] K. Hirakawa and T. W. Parks, "Adaptive homogeneity-directed demosaicing algorithm," IEEE Trans. Image Process.,vol. 14, no. 3, pp. 360–369, Mar. 2005.

[3] K. Hirakawa and T. W. Parks, "Adaptive homogeneity-directed demosaicing algorithm," IEEE Trans. Image Process.,vol. 14, no. 3, pp. 360–369, Mar. 2005.

[4] D. Menon and G. Calvagno, "Regularization Approaches to Demosaicking," IEEE Trans. Image Process., vol. 18, no. 10, pp. 2209 - 2220, Oct. 2009.

[5] N. X. Lian, L. Chang, Y. P. Tan, and V. Zagorodnov, "Adaptive filtering for color filter array demosaicking," IEEE Trans. Image Process., vol. 16, no. 10, pp. 2515–2525, Oct. 2007.

## AUTHOR'S PROFILE

Shaik mahaboob basha completed his Btech in Narayana Engineering College Nellore in 2014. Now pursuing Mtech in Electronics & Communication Engineering in SKR College of Engineering & Manubolu

Technology, Manubolu

L Vidya Sagar , received his M.Tech degree, currently He is working as an Assistant Professor in SKR College of Engineering & Technology, Manubolu