# **High-Performed Digital Measurement Strategy To Get Scalable Resolution**

# SEKHAR RAJKUMAR

## **M MASTHANAIAH**

M.Tech Student, Dept of ECE SKR College of Engineering & Technology Nellore, Andhra Pradesh, India

Assistant Professor, Dept of ECE SKR College of Engineering & Technology Nellore, Andhra Pradesh, India

Abstract: Within this paper, we present a minimal-cost, on-nick clock jitter digital measurement plan for top performance microprocessors. It enables in situ jitter measurement throughout the test or debug phase. It offers high measurement resolution and precision, regardless of the possible existence of power noise, at low area and power costs. The achieved resolution is scalable with technology node and may in principle be elevated around preferred, at low additional costs when it comes to area overhead and power consumption. Using ring oscillators (ROs) for PPV measurement is broadly assessed and adopted. We reveal that, for that situation of high end microprocessors employing ring oscillators (ROs) to determine process parameter variations (PPVs), our jitter measurement plan could be implemented by reusing a part of such ROs, thus allowing to determine clock jitter having a limited cost increase in contrast to PPV measurement only, with no effect on parameter variation measurement resolution. The achievement of the more and more great resolution by augmenting the amount of NOT chains is restricted through the difficulty in managing the NOT delays, because of PPV.

Keywords: Clock Jitter; High Performance Microprocessor; Jitter Measurement;

## I. INTRODUCTION

Using the scaling of technology while increasing in clock frequency, it's becoming more and more difficult to be sure the correctness of clock signals, because of the growing probability manufacturing defects, clock jitter, duty-cycle distortion, process parameter variations (PPVs) and power noise (PSN). For top performance microprocessors, the adoption of minimum time margin is desirable, to ensure that on-nick jitter measurement ought to be performed throughout the test or debug phase to validate the look and manufacturing assumptions for that clock [1]. PSN modulating the delay from the clock signal is presently recognized among the primary reasons for clock jitter along with clock jitter, also PPV occurring during fabrication are more and more likely and significant with technology scaling. They might induce either performance degradation, or operating malfunctions. Therefore, also PPV mandate oldie measurement throughout the make sure debug phase to validate design and process, possibly drive speed-binning, and finally dictate enhancements. process measurement schemes happen to be suggested for clock jitter and PPV. Using ring oscillators (ROs) for PPV measurement is broadly assessed and Rather, schemes for clock jitter measurement aren't too established yet, due to the fact of limits within their measurement resolution and precision. Disked buffers can be used to pay for PPV created effect, however their application is usually still restricted to some servings of the entire clock distribution network only because of cost limitations. The suggested approach is dependent on a plan similar, using the following primary

variations: 1) the implementation from the sampling elements 2) using multiple out-of-phase delay lines within our plan to improve resolution and three) the proposal of the sampling technique to steer clear of the impact of PSN on jitter measurement [2]. Our plan could be occur either the PPV measurement mode, or even the clock jitter measurement mode, by functioning on an exterior control signal. The potency of our approach continues to be verified using electrical level simulations, performed thinking about a PSN as much as 50% from the nominal power current.

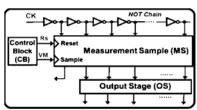

Fig.1.Framework of proposed system

# II. PROPOSED SYSTEM

Jitter may be the deviation of the signal timing event from the ideal position, causing displacements of clock transition occasions. These displacements are classified as either deterministic, random, or both. We make reference to the next jitter definitions: 1) timing jitter, the time distinction between the particular and excellent signal transition 2) period jitter, the time variation from the signal period from the average value and three) cycle-to-cycle jitter, the variation at that time of the signal within two following periods. We appraise the time period of clock high and/or low phase(s) with time, and compare the acquired

results with individuals expected for that situation of jitter-free clock. With regard to brevity, we here present the plan for that clock high phase measurement only, which may be easily extended to determine both clock phases. The NOT chain implements a delay line delaying the input CK, whose jitter needs to be measured, with a given period of time [3]. The outputs from the NOT gates are sampled through the measurement sample (MS) block, once the control block (CB) gives valid measure (VM) = 1. The output stage (OS) creates the measurement encoded with a thermometer code. By looking into making RS = 1, CB resets the measurement following a time lengthy enough to permit the machine to see it. The logic values concurrently present in the outputs of every NOT from the chain following a CK falling and rising edge are proven. The time period of the CK high phase is offered by the amount of NOTs inside the chain the CK rising edge has to feed, prior to the CK falling edge involves the chain input. The PDN characteristic impedance seen from various locations within the PSN topology may exhibit significant variations. Therefore, for evaluation purpose, we've realistically modeled the PSN like a train of narrow triangular pulses, whose width depends upon the amount of switching gates in a single clock period. Furthermore, because the pulse width is definitely really small, the PSN could be modeled being an impulse train having a uniformly distributed random shift. Using electrical level simulations, we've verified that just the NOT propagating the CK edge once the PSN occurs is impacted, as the sampling circuitry isn't. The variation within the delay from the NOT propagating the CK edge determines the outcome of PSN on measurement precision. We've figured that this type of not delay variation impacts the jitter measurement precision in our plan. Following a time lengthy enough to permit the machine to see the performed measure, the plan could be reset by asserting RS, thus which makes it ready for any following measurement. We assume signal Rs is activated almost every other CK cycle. We make use of a periodic signal generated reset (GR) with half the CK frequency to create the RS pulse upon its rising edge. To acquire a resolution greater than the usual NOT delay (t), we switch the fundamental block plan. The helpful bits representing the jitter measurement begin with the creation of the 2nd NOT from the chain, denoted by p1. The output pS, along with its connected signal outS can be used through the control block CB to look for the sampling instant. Our plan samples the outputs from the NOT chain at any given time instant denoted by tS, following the CK rising edge. By doing this, the outputs from the corresponding NOTs of these two chains possess a t/2 phase difference. The achievement of the more and more great resolution by augmenting the amount of NOT

chains is restricted through the difficulty in managing the NOT delays, because of PPV. To resolve this problem, the NOT chains could be implemented using balanced delay lines, or inverters whose delay could be calibrated after fabrication [4]. Two possible implementations in our plan to determine the CK high phase are here described. We think about a standard 65-nm CMOS technology. They're: Implementation Non Reusing ROs: For OS, it buffers the outm signals and encodes them with a thermometer code on signals. The sampled data should be maintained for just one clock cycle only. Therefore, dynamic latches happen to be considered, instead of more pricey static latches, to lessen implementation costs. When Rs is asserted, VM flips to, making all TGs conductive again. Thus, all signals oRm become comparable to 1, thus taking out the previous measurement results. To pay possible PPV occurring during manufacturing, the inverter chains happen to be implemented by NOTs having a programmable delay. PPV might also imbalance the reduced-to-high and-to-low transitions from the NOTs. However, we've verified this negligibly impacts the job-cycle from the clock, whose jitter has been measured. The delay from the NOTs can also be responsive to current and temperature variations. This type of sensitivity might be reduced by using among the techniques which have been suggested within the literature for that on-nick compensation of current and temperature variations. Implementation Reusing ROs: We modified the FUB by connecting multiplexers M1 and M2 towards the input from the NAND gates N1 and N2, correspondingly. By doing this, by externally functioning on the control signal JT, our plan can be simply occur either the PPV measurement mode (JT = 1), or even the clock jitter measurement mode (JT = ). Blocks MS, OS, and CB. When it comes to NOTs from the chains, we can't put them into action having a programmable delay to pay PPV. However, by initially configuring the FUBs within the PPV measurement mode, we are able to determine the variation within the delay from the NOTs from the ROs within the nominal value. This assists you to correct possible clock jitter measurement errors caused by the existence of PPV. When it comes to implementation in our plan reusing ROs, we've verified that: 1) the PPV measurement precision from the original FUB isn't degraded 2) the time jitter measurement precision is equivalent to for that implementation in our plan non reusing ROs. We've evaluated the expense in our suggested plan, implemented with and without reusing ROs, when it comes to additional area and power consumption [5].

### III. CONCLUSION

The plan enables in situ jitter measurement throughout the test or debug phase. It enables achieving an excellent and scalable measurement resolution and precision, despite the existence of PSN. We've suggested an on-nick clock jitter plan performance measurement for top microprocessors. We've also proven that, for that situation of microprocessors employing ROs to determine PPVs, our jitter measurement plan could be implemented by reusing area of the ROs, thus allowing a discount of more area over our plan not reusing the ROs. The achievement of the more and more great resolution by augmenting the amount of NOT chains is restricted through the difficulty in managing the NOT delays, because of PPV. We've proven that, when our plan is carried out to feature exactly the same resolution because the previous approach, it enables a decrease in both area and power consumption. Rather, in contrast to the approaches, our plan needs a significantly lower area overhead, while featuring exactly the same measurement resolution.

#### IV. REFERENCES

- [1] C. Metra, L. Schiano, and M. Favalli, "Concurrent detection of power supply noise," IEEE Trans. Rel., vol. 52, no. 4, pp. 469–475, Dec. 2003.

- [2] M. Omaña, D. Rossi, and C. Metra, "Low cost scheme for on-line clock skew compensation," in Proc. 23rd IEEE VLSI Test Symp., May 2005, pp. 90–95.

- [3] Wavecrest Corporation, Eden Prairie, MN, USA. (2005, Jul. 6). Jitter Fundamentals [Online].

- [4] K. Niitsu, M. Sakurai, N. Harigai, T. J. Yamaguchi, and H. Kobayashi, "CMOS circuits to measure timing jitter using a self-referenced clock and a cascaded time difference amplifier with duty-cycle compensation," IEEE J. Solid-State Circuits, vol. 47, no. 11, pp. 2701–2710, Nov. 2012.

- [5] Y. Tsugita, K. Ueno, T. Asai, Y. Amemiya, and T. Hirose, "On-chip PVT compensation techniques for low-voltage CMOS digital LSIs," in Proc. IEEE ISCAS, May 2009, pp. 1565–1568.

#### **AUTHOR'S PROFILE**

Sekhar Rajkumar completed his Btech in priyadarshini college of engineering and technology Nellore in 2014. Now pursuing Mtech in Electronics & Communication Engineering in SKR

College of Engineering & Technology, Manubolu

M Masthanaiah , received his M.Tech degree, currently He is working as an Assistant Professor in SKR College of Engineering &

Technology, Manubolu