P. Haritha\* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.4, Issue No.6, October – November 2016, 4714-4716.

# An Informative Pipelining With Scheduling Regulator To Support Recovery

P. HARITHA

M.Tech Student, Dept of ECE SKR College of Engineering & Technology Nellore, Andhra Pradesh, India M MASTHANAIAH Assistant Professor, Dept of ECE SKR College of Engineering & Technology Nellore, Andhra Pradesh, India

*Abstract:* Within this work, we apply Razor to hardware accelerators that find growing application in System-on-Nick designs rich in-performance needs that must definitely be delivered under stringent power budgets. We exploit these traits usual for DSP and image-processing accelerators to apply Razor recovery in manner that's amenable to RTL validation and verification. We describe the implementation and plastic measurement is a result of a Razor-based hardware loop-accelerator (RZLA), applying the Sobel edge-recognition formula. Unlike microprocessors, the RZLA pipeline is data path-dominated with statically-scheduled control which has queue-based storage structures that are simply extended to aid check-pointing and recovery. The RFF is deployed along with an amount-sensitive latch-insertion based formula to deal with the minimum-delay constraint contained in all Razor systems. This formula enables using the time period for timing speculation resulting in robust error recognition and correction across a large dynamic current- and frequency-scaling range.

*Keywords:* Low Power Digital Systems; Systems-On-Chip; Variation-Tolerant Design; VLSI Digital Circuits;

### I. INTRODUCTION

SoC designs still take advantage of greater integration levels enabled by technology scaling. However, because of supply voltages remaining effectively constant, technology scaling no more delivers automatic energy-efficiency gains which driven development from have the the semiconductor industry recently. Performance demands increase even while process, current and temperature (PVT) variations still rise, putting further pressure on already-strained power budgets. The traditional approach of design-time margining is showing to become more and more inefficient when confronted with rising variations and runtime adaptation is really a necessity [1]. Traditional adaptive techniques according to so-known as "canary" circuits make amends for certain manifestations of variations by roughly tracking the critical-path delay across variations in plastic-grade and prevailing operating conditions. However, the effectiveness of these techniques is restricted by substantial margining needed for fast-altering and localized variations, for example PLL jitter and inductive current droops. Error-recognition and recovery enables Razor systems to outlive both fast-moving and transient occasions, and adjust to the slow-altering prevailing conditions, allowing excess margins to become reclaimed [2]. The reclaimed margins could be traded-off for perdevice enhancements in energy-efficiency or parametric yield improvement for any batch of devices. Error correction is conducted through the system through either correct-data substitution or instruction replay from the check-pointed condition. Razor-enabled dynamic adaptation has shown substantial enhancements in performance

and-efficiency in micro-processor pipelines. Applying Razor support requires explicit partitioning of pipeline logic into speculative and non-speculative regions. The speculative partition from the pipeline is timing-critical and needs RFFs for timing-error recognition. It's needed to ensure that incorrect and potentially detestable outputs from speculative logic don't corrupt check-pointed architectural condition within the non-speculative partition. Because of these complex control-plane interactions, applying Razor recovery in CPU pipelines is micro-architecturally invasive and incurs significant validation and verification challenges. These accelerators are usually targeted towards compute-intensive kernels in DSP algorithms, wireless communications as well as networking, and graphics processing. Such are covered with tight loops applications processing considerable amounts of streaming data, so it's natural to apply these loops as hardware Loop Accelerators (LA). Hardware LAs favorably trade-off surplus transistors to provide order-ofmagnitude greater efficiency when compared to software-only solution in programmable processors. Within this work, we describe the very first use of Razor to some hardware Loop-Accelerator (henceforth known as the RZLA) enhanced for that dominant loop from the Sobel Edge-Recognition formula. In comparison with microprocessors, LAs really are a type of coprocessors that accelerate a specific function and therefore don't need to maintain an interior architectural condition. Rather, queues are utilized inside a dataflow-like manner to transfer transient data between functional units. This will make the LAs very amenable for applying Razor recovery, as

simply extending existing queues offers the necessary storage for that speculative condition flying, until it's validated using Razor [3].

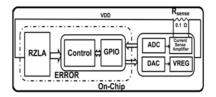

#### Fig.1.Proposed system

### II. PROPOSED SYSTEM

The Sobel edge-recognition formula identifies high-frequency variations in image pixel intensities to acquire sharp edges within the image. The RZLA is really a hardware realization of the modulo scheduled loop. Modulo-scheduling is really a software pipelining technique that achieves high throughput by overlapping successive iterations of the loop. Unlike microprocessors, the doesn't need explicit support RZLA for mechanisms for example exception handling. Therefore, condition is mainly maintained in Shift Register Files (SRF) to become consumed when needed after which immediately discarded. Wires in the SRF to the FU inputs allow bandwidth from producer to consumer. The RZLA begins execution if this gets to be a start signal in the host processor. A Main Register File (CRF) contains constants and configuration information like the input image X- and Y-dimensions and also the Sobel edgerecognition threshold. The neighborhood memory offers the primary input and output data storage. Inside a micro-processor, recovery from timing error engages an intricate recovery mechanism that flushes pipeline condition and reloads the pipeline from the golden architectural condition [4]. In comparison, the RZLA implements check-pointing and recovery simply by extending the shift-register depth. This will make reverting to a previous condition easy and amenable to RTL validation and verification-if the error was detected as the LA is executing, the controller reverts to some condition "R" cycles earlier. Error flags from individual RFF are OR-altogether to generate composite error signal for the whole design. The mistake OR-tree output is double latched to mitigate against potential met stability risk. Whenever a timingerror is detected, the mistake controller asserts the ROLLBACK signal that resets the mistake-states of RFFs within the design and initiates recovery. The RFF augments an optimistic-phase transparent latch having a transition-detector that flags latecoming transitions around the input, D. Risingedge triggered switch-flop operation is enforced by flagging any transition on D, within the clock highphase, like a timing error. Utilizing a pulsed-latch architecture rather of the conventional master-slave for that primary data path consecutive element has two advantages. The transition-detector incorporates explicit generators to produce wide pulses, DPr and DPf, from rising and falling transitions on D. The heart beat-generators use skewed devices so that the increasing transition from the output pulse is favored within the falling transition, therefore establishing a wide pulse in the output. Disambiguating between early- and latecoming transitions imposes the absolute minimumdelay constraint in most Razor systems. The pulsed-latch architecture from the RFF exposes the whole high-phase from the clock because the minimum-delay constraint. Typically, this constraint is content through the insertion of delaybuffers within the violating pathways, which incurs the region and power overhead from the additional switching capacitance. The RZLA addresses the minimum-delay constraint through the explicit instantiation of level-sensitive latches. Each pipeline stage is conditionally retimed in which the logic cone that fans-to a RFF is split into two blocks with roughly equal critical path delay. Negative-phase transparent latches are placed backward and forward logic blocks thus produced. The latches are opaque within the high-phase from the clock and stop short-path computations in the present cycle from updating inputs towards the RFFs before the negative clock-phase, thus satisfying the minimum-delay constraint by construction. Negative-phase logic cannot begin computation until following the falling clock-edge, even if your positive-phase logic (Tpos) completes early within the high-phase. This potentially cuts down on the energy-gains accessible through Razor. However, the efficiency gains through margin elimination are large enough so that the outcome from the latches around the PoFF is basically minimal. Hardware accelerators are usually characterized by high switching activities when enabled. This can lead to considerably greater contribution from the combination logic towards the total power the look, when compared with microprocessors. The suppression-clock pulse requires 11 extra transistors that toggle on every rising-fringe of the time and increase the total power-overhead from the design. The heart beatgeneration could possibly be shared across multiple Brazoria switch-flops, therefore amortizing the ability overhead. However, this design is prone to rising local PVT variations that may adversely change up the generation and distribution from the narrow suppression pulse [5]. Consequently, the RZLA requires less quantity of latches when compared to Bubble Razor plan. In addition, Bubble Razor is implemented inside a microprocessor where consecutive power dominates over combinational power. The latch-insertion formula inserts 709 level-sensitive latches to take into account the minimum delay constraint around the RFFs.

## III. CONCLUSION

We presented the micro-architecture style of the RZLA which makes unique trade-offs within the implementation of Razor recovery, when compared with microprocessors. Within this paper, we presented the look and plastic measurement outcomes of a Razor-enabled hardware loop-accelerator (RZLA). Inside a complex SoC, this design is really a proof-point that Razor could be effectively put on hardware accelerators additionally to application processors. Error-recognition within the RZLA pipeline occurs utilizing a low-overhead pulsed-latch based Razor Switch-flop (RFF) architecture that's deployed along with an amount-sensitive latch-insertion based formula.

### **IV. REFERENCES**

- G. Dasika, S. Das, K. Fan, S. Mahlke, and D. Bull, "DVFS in loop accelerators using BLADES," in Proc. Design Automation Conf., DAC 2008, 2008, pp. 894–897.

- [2] T. Fischer et al., "A 90-nm variable frequency clock system for a powermanaged Itanium architecture processor," IEEE J. Solid-State Circuits, vol. 41, no. 1, pp. 218–228, Jan. 2006.

- [3] H. Esmaeilzadeh et al., "Dark silicon and the end of multicore scaling," IEEE Micro, vol. 32, no. 3, pp. 122–134, May–Jun. 2012.

- [4] D. Ernst, S. Das, S. Lee, D. Blaauw, T. Austin, T. Mudge, N. S. Kim, and K. Flautner, "Razor: Circuit-level correction of timing errors for low-power operation," IEEE Micro, vol. 24, no. 6, pp. 10–20, 2004.

- [5] K. Bowman et al., "A 45 nm resilient microprocessor core for dynamic variation tolerance," IEEE J. Solid-State Circuits, vol. 46, no. 1, pp. 194–208, Jan. 2010.

## AUTHOR'S PROFILE

P. Haritha completed her Btech in Jntu Kakinada in 2014. Now pursuing Mtech in Electronics & Communication Engineering in SKR College of Engineering & Technology, Manubolu

M Masthanaiah , received his M.Tech degree, currently He is working as an Assistant Professor in SKR College of Engineering & Technology, Manubolu