#### FACTA UNIVERSITATIS

Series: Electronics and Energetics Vol. 31, No 1, March 2018, pp. 131 - 140

https://doi.org/10.2298/FUEE1801131P

## MEMORY CHIPS AND UNITS RADIATION TOLERANCE DEPENDENCE ON SUPPLY VOLTAGE DURING IRRADIATION AND TEST

## Andrey G. Petrov, Alexander Y. Nikiforov, Anna B. Boruzdina, Anastasia V. Ulanova, Andrey V. Yanenko

National Research Nuclear University MEPhI (Moscow Engineering Physics Institute), Moscow, Russia

Abstract. In this work we investigate the influence of various memory chips supply voltage on their sensitivity to the radiation environment. The main physical mechanisms responsible for radiation-induced degradation at nominal, increased, and decreased supply voltage values are discussed. It is demonstrated that, depending on supply voltage value during irradiation and subsequent testing, device's tolerance to data corruption effects in memory circuits, single event latch-up (SEL) and hard errors induced by ionizing radiation can vary significantly. We also give some recommendations to perform radiation tests.

**Key words**: space radiation, memory, digital integrated circuits, flash, SRAM, SEU, total dose

### 1. Introduction

The typical variation of allowable supply voltage values for complex digital CMOS integrated circuits (microprocessors, microcontrollers, memory chips, etc.) is within 5 to 10 percent of the nominal one. The device in application can work at any supply voltage within this range. According to data from previous works, the total dose hardness and single event sensitivity can vary significantly depending on the operation conditions [1]-[9]. This fact must be taken into account when assessing radiation tolerance of microcircuits. In this work we concentrated our investigations on radiation tolerance dependence with supply voltage for memory segment of digital ICs. Memory cells or units are a part of the vast majority of digital ICs. In some cases memory is the most critical unit of digital ICs due to its sensitivity to radiation [1], [10]-[11]. Radiation environment (space, various ground sources, etc.) can have a negative impact on electrical parameters of memory chips

Received May 4, 2017; received in revised form September 14, 2017

Corresponding author: Alexander Y. Nikiforov

National Research Nuclear University MEPhI (Moscow Engineering Physics Institute), Kashirskoe shosse 31,

Moscow 115409, Russia

(E-mail: aynik@spels.ru)

and units, such as supply current, output voltage levels, timing parameters, etc. However, the most negative consequences are associated with radiation effects leading to functional failures, such as corruption of data stored in memory or inability to rewrite data. The radiation tolerance level to these functional and parametric failures can significantly depend on the supply voltage of ICs and particularly for memory devices. The radiation behavior of memory devices and units must be taken into account while providing radiation qualification of digital ICs.

The aim of this work is to demonstrate how the influence of supply voltage applied during irradiation and testing can influence the radiation response of memory microcircuits, and to determine the worst-case supply voltages for various critical microcircuit parameters. We will describe the main mechanisms that determine the dependency of radiation response to supply voltage and work out some recommendations for proper selection of supply voltage during radiation tests of various memory devices and digital ICs containing memory units.

# 2. THE INFLUENCE OF SUPPLY VOLTAGE ON TOTAL DOSE HARDNESS OF MEMORY INTEGRATED CIRCUITS

Previous works have shown that total dose hardness levels of complex multifunctional very large scale integration (VLSI) devices strongly depend on operating conditions during radiation tests [12]-[14]. In this work we consider in more detail total dose tolerance dependence of various memory ICs on their supply voltages not only during irradiation but also during functional tests.

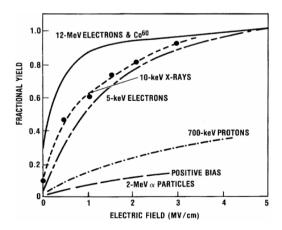

The amount of radiation-generated carriers escaping initial recombination increases with applied electric field, as shown in Figure 1 [15]. The application of supply voltage on the IC during irradiation leads to the presence of a higher electric field in oxides, and induces a higher density of charge trapped in oxides. Thus, applying the maximum allowed supply voltage during irradiation is the most critical parameter for the estimation of total dose tolerance of digital ICs (in particular memory devices) estimation.

**Fig. 1** Experimentally measured fractional hole yield as a function of applied electric field, for a number of incident particles [15]

At the same time, as will be shown below, applying the maximum supply voltage during functional tests after irradiation is not always critical for memory total dose tolerance estimation.

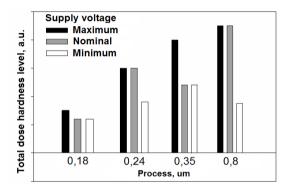

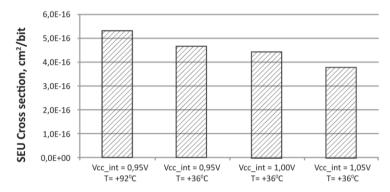

We experimentally compared TID levels when applying minimum, nominal and maximum allowed supply voltages during functional tests of SRAM microcircuits. These SRAMs were manufactured on various CMOS processes, supply voltages vary from 2,7 V to 5,5 V. Device irradiation was performed at maximum supply voltage. This experimental comparison (figure 2) shows that applying the minimum allowed supply voltage during functional test (writing and reading test operations) is the most critical mode for SRAM functional failure total dose level estimations. Such behavior is due to the fact that an IC in this mode exhibits the maximum sensitivity to threshold voltage shift and leakage caused by the trapping of the radiation-induced charge in the oxide.

Fig. 2 Total dose hardness dependence on supply voltage applied during functional tests for various SRAMs

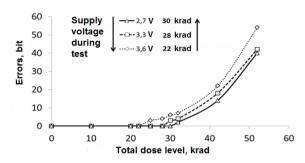

A different behavior was observed for flash and EEPROM memories. We investigated functional failure dependence on supply voltage during test after irradiation for flash memory S29GL064N manufactured on 110 nm CMOS process. Before irradiation, the test pattern was stored into the memory array. During irradiation the device was kept in storage mode at nominal supply voltage. Periodically irradiation was paused and a reading operation was performed on the memory array at minimum, nominal and maximum allowed supply voltages. The first differences between write (stored) and read data were observed for the maximum supply voltage (figure 3).

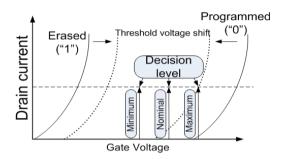

All observed errors were bit upsets from programmed state (charge stored into cell gate, "0" logical level) to erased state (charge removed from cell gate, "1"logical level). Thus, it can be argued that bit upsets were caused by the loss of charge stored into the cell during irradiation. When the radiation-induced charge loss is total, stored information is upset from the programmed state to the erased state. When the loss of charge is only partial, it leads to a threshold voltage shift of the flash memory cell, as illustrated by the dashed curves in Figure 4. During the reading operation of the memory, the voltage on cells gate has the same value as the supply voltage. Therefore, as illustrated in figure 4, applying the maximum supply voltage during irradiation and test will be the most critical for total dose tolerance estimation.

**Fig. 3** Number of flash memory read error bits vs total dose level for various supply voltage applied during test

**Fig. 4** Drain current vs gate voltage for programmed ("0") and erased ("1") cell states and cell with some charge (dotted curve)

# 3. THE INFLUENCE OF SUPPLY VOLTAGE ON SINGLE EVENT SENSITIVITY OF DIGITAL INTEGRATED CIRCUITS

Two main single event effects in digital ICs are single event latchup (SEL) and single event upsets (SEU) in memory units, control and data registers. Single event upsets in registers can cause single event functional interrupt (SEFI). We provide estimation of SEU sensitivity dependence on supply voltage for different types of memory devices and units.

### 3.1. SEU sensitivity dependence on supply voltage for SRAM memory.

In a memory cell, the area sensitive to single event upsets is the drain of off-state transistors in [16]-[21]. According to [21], the critical charge for SRAM cell upset depends on static noise margin of the device and can be estimated as:

$$Q_c = C_{OX} V_{SNM} \tag{1}$$

where  $C_{OX}$  – the capacitance of gate oxide,  $V_{SNM}$  is the static noise margin of memory cell. Static noise margin decreases with supply voltage. Therefore, the sensitivity of SRAM memory ICs and units to single event upsets increases with the decrease in supply voltage. Such behavior was observed for XC7Z020 configuration memory, as shown in the results presented below.

However, the critical charge for cell upset does not always show a linear dependence on supply voltage level. For this reason, experimental results obtained for one supply voltage cannot be extrapolated to another level without experimental estimation [22]. Investigation of single event upsets in SRAM due to neutrons [23] shows that simple cross section estimation based on critical charge in some cases can give underestimated results.

The results of investigation on the XC7Z020 configuration memory are shown in Figure 5, where the SEU cross section increases with the decrease in supply voltage during test. For this type of memory, applying the minimum supply voltage during irradiation is the most critical mode for SEU.

**Fig. 5** SEU cross section dependences vs supply voltage during test and temperature for 120 MeV protons irradiation (cm<sup>2</sup>/bit), (MeVcm<sup>2</sup>/mg)

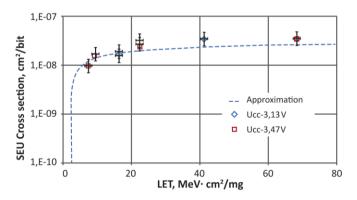

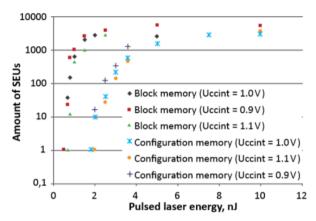

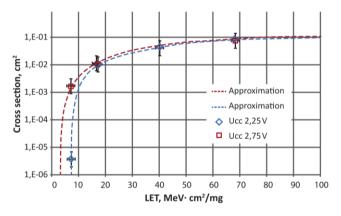

At the same time SEU investigation results for CMOS 0,25  $\mu$ m SRAM 512K×8 (Figure 6) and XC5VLX50 block and configuration memory (Figure 7) show no significant difference in SEU cross section at different supply voltages during irradiation. However, it should be noted that a difference in sensitivity of SRAM at different voltages can be observed in the LET threshold region of the effect. Experimental data for linear energy transfer (LET) values in near-threshold have not been obtained in this case.

**Fig. 6** CMOS 0,25 um SRAM 512K×8. SEU cross section vs heavy ion LET for various supply voltages applied during irradiation

**Fig. 7** Amount of SEUs in block and configuration memory vs pulsed laser energy for various supply voltages

#### 3.2. SEU sensitivity dependence on supply voltage for charge storage memory.

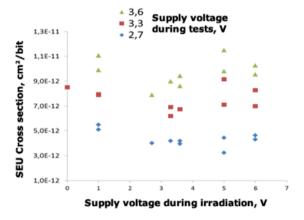

Another dependence of the sensitivity to SEUs is observed for charge storage memories (Flash, EEPROM). We provide data on the irradiation of flash memory S29GL064N manufactured on 110 nm CMOS process by Ne ions with an LET near 7 MeV·cm2/mg at various supply voltages. After irradiation, information stored was read from the array at minimum, nominal and maximum allowed supply voltages for this device (figure 8) and compared with the data written before irradiation. As shown by the experimental results in Figure 8, the device cross section does not depend on supply voltage during irradiation. At the same time, an increase in SEU cross section with supply voltage during test after irradiation has been observed. SEUs in this flash memory result from partial charge loss stored in memory cell [24] and increase in cross section with supply voltage can be explained similarly to total dose. In this case the maximum supply voltage during test will be the most critical mode for SEU sensitivity estimation.

Fig. 8 SEU cross section vs supply voltage during test and irradiation Ne ions at normal incidence for S29GL064N

### 3.3. SEL sensitivity dependence on supply voltage for digital ICs.

Memory ICs and units have no difference in single event latchup mechanisms and sensitivity dependence on supply voltage in comparison with other digital ICs. Our experimental results obtained for CMOS SRAM memories CY62256 (Figure 9) and 90nm CMOS SRAM 1Mx8 (Figure 10) show that the worst-case for SEL sensitivity is to apply the maximum supply voltage during irradiation.

Fig. 9 CY62256. SEL cross section ( $\sigma_{SEL}$ ) vs heavy ions LET for different supply voltages

**Fig. 10** 90nm CMOS SRAM 1Mx8. SEL cross section( $\sigma_{SEL}$ ) vs heavy ions LET for different supply voltages

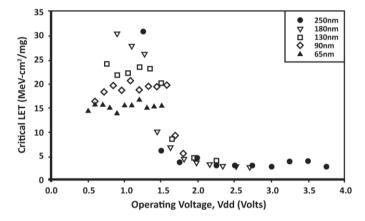

There is no influence of ICs scaling on the parameters of the parasitic thyristor structure at the origin of the SEL mechanism. Switch-on current does not vary significantly for CMOS processes with design rules from 180 nm to 65 nm. Operating temperature and supply voltage mainly affect ICs SEL sensitivity [25]. Sensitivity to SEL decreases with supply voltage, which is explained by a decrease in the gain of the parasitic bipolar transistor and a decrease in the collected charge with a lower electric

field strength [26]. The influence of the supply voltage is mainly manifested near the SEL threshold LET. It can be clearly seen from our experimental results presented above in Figures 9 and 10. The SEL saturation cross section is almost unchanged with supply voltage, while the SEL threshold LET varies significantly. In addition, a higher supply voltage can be more likely to exceed the SEL holding voltage, which increases the probability of maintaining SEL condition. Results presented in work [26] show a sharp increase in sensitivity to SEL at supply voltages greater than 1.5 V (figure 11). Therefore the maximum supply voltage is the most critical mode for SEL sensitivity estimations.

Fig. 11 Dependence of the SEL threshold LET on the supply voltage for various design rules

# 4. RECOMMENDATIONS ON SELECTION OF SUPPLY VOLTAGE FOR DIFFERENT TYPES OF MEMORY INTEGRATED CIRCUITS AND UNITS DURING RADIATION TESTS

When performing radiation qualification of ICs, it is necessary to correctly select the worst-case supply voltage to give conservative estimations of radiation hardness level. Incorrect selection of supply voltage can lead to overestimation of radiation hardness level. It is important to take into account that the worst-case supply voltage to use during test and during irradiation may be different. Based on the results of the investigation and their analysis presented above, we can give recommendations for an appropriate selection of the worst-case supply voltage during certification of memory ICs and units. These recommendations are presented in table 1.

| Type of        | Total dose  |             | Single events |                    |             |

|----------------|-------------|-------------|---------------|--------------------|-------------|

| memory         | During      | During test | SEL           | SEU                |             |

|                | irradiation | _           |               | During irradiation | During test |

| SRAM           | Maximum     | Minimum     | Maximum       | Minimum            | Any         |

| Charge storage | Maximum     | Minimum     | Maximum       | Any                | Minimum     |

| memory         |             | and maximum |               |                    | and maximum |

Table 1 Worst-case supply voltages during ICs radiation certification

#### 5. CONCLUSION

In this work we have shown significant influence of memory ICs and units supply voltage on their sensitivity to total dose and single event upsets. We identified the worst-case supply voltage for total dose and single event upsets memory ICs sensitivity during irradiation and test, and we have shown that they can be different in some cases. Consequently, recommendations are also provided to properly select the supply voltage to use during memory ICs and units radiation qualification.

#### REFERENCES

- [1] P. Nekrasov, A. Demidov, O. Kalashnikov, "Functional checks of microprocessors during radiation tests", *Instruments and Experimental Techniques*, vol. 52, no. 2, pp. 196-199, 2009.

- [2] O. Kalashnikov, A. Demidov, V. Figurov, A. Nikiforov, S. Polevich, V. Telets, S. Maljudin, A. Artamonov "Integrating analog-to-digital converter radiation hardness test technique and results", *IEEE Transactions on Nuclear Science*, 1998, vol. 45, no. 6 (1), pp. 2611-2615, 1998.

- [3] A. Boruzdina, A. Ulanova, N. Grigor'ev, A. Nikiforov, "Radiation-induced degradation in the dynamic parameters of memory chips", Russian Microelectronics, vol. 41, no. 4, pp. 259-265, 2002.

- [4] O. Kalashnikov, "Statistical Variations of Integrated Circuits Radiation Hardness", In Proceedings of the RADECS Conference, 2011, pp. 661-665.

- [5] O. Kalashnikov, "CMOS Integrated Circuits Total Dose Functional Upset Sensitivity to Operation Mode", In Proceedings of the 4<sup>th</sup> Workshop on Electronics for LHC Experiments, 1998, Rome, Italy, pp. 484-485.

- [6] A. Kirgizova, A. Nikiforov, N. Grigor'ev, I. Poljakov, P. Skorobogatov, "Dominant mechanisms of transient-radiation upset in CMOS RAM VLSI circuits realized in SOS technology", *Russian Microelectronics*, vol. 35, no. 3, pp. 162-176, 2006.

- [7] A. Karakozov, O. Korneev, P. Nekrasov, P. Nekrasov, M. Sokolov, D. Zagryadsky, "Bias conditions and functional test procedure influence on PowerPC7448 microprocessor TID tolerance", In Proceedings of the RADECS Conference, 2013. pp. 1-2.

- [8] D. Bobrovsky, O. Kalashnikov, P. Nekrasov, "Functional control technique for FPGA total ionizing dose testing", In Proceedings of the RADECS Conference, 2012.

- [9] O. Kalashnikov, A. Artamonov, A. Demidov, "ADC/DAC Radiation Test Technique", Workshop Record 4th European Conf. "Radiations and Their Effects on Devices and Systems" In Proceedings of the RADECS Conference, Palm Beach-Cannes, France, 1997, pp. 56-60.

- [10] V.A. Marfin, P.V. Nekrasov, and I.O. Loskutov, "Connection of the parametric and functional control for TID testing of complex VLSI circuit," In Proceedings of the 14<sup>th</sup> European Conf. on Radiation and its Effects on Components and Systems, RADECS-2015, Moscow; Russian Federation; Sept. 14 -18, 2015, article number 7365664.

- [11] I.O. Loskutov, A.B. Karakozov, P.V. Nekrasov, and A.Y. Nikiforov, "Automated radiation test setup for functional and parametrical control of 8-bit microcontrollers," In Proceedings of the 2015 International Siberian Conference on Control and Communications, SIBCON 2015 Omsk; Russian Federation; May 21-23, 2015, article number 7147128.

- [12] O.A. Kalashnikov, and A.Y. Nikiforov, "TID behavior of complex multifunctional VLSI devices," In Proceedings of the 29<sup>th</sup> International Conference on Microelectronics, MIEL 2014, Belgrade, Serbia, May 2014, pp. 455-458.

- [13] D. Boychenko, O. Kalashnikov, A. Nikiforov, A. Ulanova, D. Bobrovsky, P. Nekrasov, "Total ionizing dose effects and radiation testing of complex multifunctional VLSI devices", *Facta Universitatis, Series: Electronics and Energetics*, vol. 28, Issue 1, pp. 153-164, 2015.

- [14] A. Sogoyan, A. Artamonov, A. Nikiforov, D. Boychenko, "Method for integrated circuits total ionizing dose hardness testing based on combined gamma- and x-ray irradiation facilities", Facta Universitatis, Series: Electronics and Energetics, vol. 27, Issue 3, pp. 329-338, 2014.

- [15] T.R. Oldham and F.B. McLean, "Total Ionizing Dose Effects in MOS Oxides and Devices", IEEE Transaction on Nuclear Science, vol. 50, no. 3, pp. 483-499, June 2003.

- [16] A.I. Chumakov, A.L. Vasil'ev, A.A. Kozlov, D.O. Kol'tov, A.V. Krinitskii, A.A. Pechenkin, A.S. Tararaksin, and A.V. Yanenko, "Single-event-effect prediction for ICs in a space environment," *Russian Microelectronics*, vol. 39, no. 2, pp. 74-78, 2010.

- [17] A. I. Chumakov, A. A. Pechenkin, D. V. Savchenkov, A. S. Tararaksin, A. L. Vasil'ev, and A. V. Yanenko, "Local laser irradiation technique for SEE testing of ICs", In Proceedings of the 12th European Conf. on Radiation and its Effects on Components and Systems, RADECS-2011, Sevilla; Spain; Sept. 19 -23, 2011, pp. 449-453.

- [18] A.I. Chumakov, "Evaluation of multibit upsets in integrated circuits under heavy charged particles," Russian Microelectronics, vol. 43, no. 2, 2014, pp. 91-95.

- [19] A.B. Boruzdina, A.V. Ulanova, A.G. Petrov, V.A. Telets, P. Reviriego and J.A. Maestro, "Verification of SRAM MCUs calculation technique for experiment time optimization," In Proceedings of the 14<sup>th</sup> European Conf. on Radiation and its Effects on Components and Systems, RADECS-2013, Oxford; United Kingdom; Sept. 23 -27, article number 6937393.

- [20] D.V. Savchenkov, A.I. Chumakov, A.G. Petrov, A.A. Pechenkin, A.N. Egorov, O.B. Mavritskii, and A.V. Yanenko, "Study of SEL and SEU in SRAM using different laser techniques" In Proceedings of the 14th European Conf. on Radiation and its Effects on Components and Systems, RADECS-2013, Oxford; United Kingdom; Sept. 23 -27, article number 6937411.

- [21] Z. Zhang, J Liu, Y. Sun, M. Hou, T. Tong, S. Gu, T. Liu, "Supply voltage dependence of single event upset sensitivity in diverse SRAM devices," In Proceedings of the 10th International Conference on Reliability, Maintainability and Safety (ICRMS), Guangzhou, 2014, pp. 114-119.

- [22] J. Barak, J. Levinson, A. Akkerman, E. Adler, A. Zentner, D. David, Y. Lifshitz, M. Hass, B.E. Fischer, M. Schlogl, M. Victoria, W. Hajdas, "Scaling of SEU mapping and cross section, and proton induced SEU at reduced supply voltage," IEEE Transactions on Nuclear Science, vol. 46, no.6, pp. 1342-1353, Dec. 1999.

- [23] P. Hazucha, K. Johansson, C. Svensson, "Neutron induced soft errors in CMOS memories under reduced bias," IEEE Transactions on Nuclear Science, vol.45, no.6, pp.2921-2928, Dec 1998.

- [24] A.G. Petrov, A.L. Vasil'ev, A.V. Ulanova, A.I. Chumakov, and A.Y. Nikiforov, "Flash memory cells data loss caused by total ionizing dose and heavy ions," Central European Journal of Physics, vol. 12, no. 10, pp. 725-729, 2014.

- [25] G. Boselli, V. Reddy and C. Duvvury, "Latch-up in 65nm CMOS technology: a scaling perspective," In Proceedings of the IEEE International Reliability Physics Symposium (IRPS2005), 2005, pp. 137-144.

- [26] R. Koga, S.J. Hansel, W.R. Crain, K.B. Crawford, S.D. Pinkerton, and J. Quan, "Single Event Upset and Latchup Considerations for CMOS Devices Operated at 3.3 Volts", Aerospace report no. TR-94(4940)-9, 1995.