FACTA UNIVERSITATIS Series: Electronics and Energetics Vol. 29, N° 4, December 2016, pp. 647 - 651 DOI: 10.2298/FUEE1604647L

# TRANSIENT VOLTAGE SUPPRESSOR BASED ON DIODE-TRIGGERED LOW-VOLTAGE SILICON CONTROLLED RECTIFIER

## Xiang Li, Shurong Dong, Zhihui Yu, Jie Zeng, Weihuai Wang

Institute of Photonics and Microelectronics

Department of Information Sciences and Electronic Engineering, Zhejiang University Hangzhou, China

**Abstract**. Transient voltage suppressor (TVS) has been widely used for electronic system ESD protection. A good TVS is usually costive as it needs some special processes and extra masking layers for fabrication. A novel TVS design based on the standard CMOS process will be much more attractive. This work proposes a new TVS device using a CMOS compatible diode-triggered silicon controlled rectifier (DLVTSCR) as the core device. Due to the availability of multiple trigger mechanisms and the dual current paths for bypassing the ESD current, the newly proposed device is able to sink an ESD current of over 10 A. In addition, the holding voltage is promoted up to 6.83 V and the trigger voltage is lowered down to 10.8 V which is well suited for most portable device applications.

Key words: TVS, ESD, LVTSCR

### 1. INTRODUCTION

The integrated circuits (ICs) used in modern mobile electronic devices are faster, more powerful, less power consumptive, and are much smaller than ever before. However, they are more vulnerable to reliability issues, not only due to the small device size and the use of ultrathin gate oxide, but also due to their applications which make the devices more frequently exposed to electrostatic discharge events produced during the frequent human interfacing, and often plugging and disconnecting the USB devices and HDMI port. On-chip protection is now of vital importance for system reliability. However, conventional protection scheme is not only costive and bulky, but also leads to the system performance degradation [1]-[5].

Transient Voltage Suppressor (TVS) diodes have long been used to provide a high robustness system level ESD protection [6-8]. Under normal operating conditions, the TVS diode maintains in a high impedance state. During a transient discharge event, the TVS breaks down electrically and yields a low impedance shunt path to bypass the transient current. A

Corresponding author: Shurong Dong

Institute of Photonics and Microelectronics, Department of Information Sciences and Electronic Engineering, Zhejiang University, Hangzhou, China

Received June 30, 2015; received in revised form March 12, 2016

<sup>(</sup>email: dongshurong@zju.edu.cn)

good TVS protection circuit must be able to divert the transient current and to clamp transient voltage below the threshold value before the failure of the protected IC.

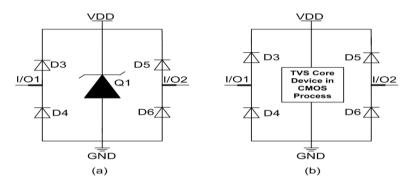

A TVS structure includes a core device and some steer diodes. The clamping voltage usually depends on the core device, and the steer diodes can divert the ESD current to the core device and can reduce the overall capacitance of the structure. However, to obtain a good TVS diode, some special processes, such as deep trench isolation or additional processing masking layers, are required. This work attempts to develop a CMOS compatible TVS device. FIG. 1 shows the conventional TVS based on a Zener diode (a) and the newly proposed TVS structure.

Fig. 1 Conventional TVS structure based on Zener diode and the proposed TVS structure based on the standard CMOS process.

For protecting the interface for data line communications, a good TVS device must possess some special features. First, a low working voltage is crucial for safeguarding the submicron integrated circuits. The maximum reverse working voltage, Vrwm, which is the largest allowable DC voltage that can maintains the TVS in non-conducting state, is the key parameter for specifying the working voltage. When the transient voltage exceeds Vrwm, the TVS turns on quickly and a low impedance path will be established to divert the transient current. Hence, a low working voltage is essential for clamping the transient voltage to a level well below the threshold value. Second, the equivalent capacitance of TVS should be low enough in order to preserve signal integrity at the high-speed interface. If the capacitance of the TVS diodes is too high, it will cause excessive load to the circuit and then signal distortion and data errors will result.

#### 2. STRUCTURE AND PERFORMANCE

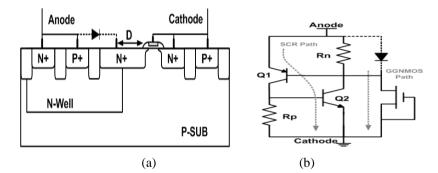

The schematic equivalent circuit and the cross-sectional view of the diode-triggered LVTSCR structure are shown in Fig. 2. LVTSCR, using the gated p-well structure, has been widely used as ESD protection devices because of its suitable values of holding voltage and the low trigger voltage. However, the gate structure also plays an important role in the reliability of the device. By adding an extra diode connecting the anode and cathode of the conventional LVTSCR, the structure can be triggered by an ESD event more easily. When an ESD event occurs, the drain PN junction and the substrate of the GGNMOS will be first driven into an avalanche breakdown and the voltage drop across

the diode increases as the avalanche current increases. Meanwhile, the electrons in the N+ (the one between the N-well and P substrate) will diffuse into the N-well. When the voltage drop across the diode rises above 0.7 V, the bipolar transistor (Q1) will be turned on. And that makes the SCR to be turned on later owing to the positive feedback in the transistors Q1 and Q2.

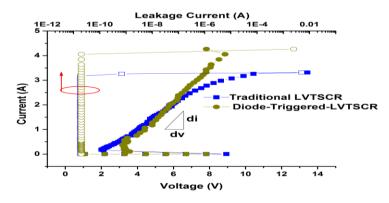

This device has been taped out in 0.18um CMOS process. To study the characteristic of this new structure, transmission line pulse (TLP) measurements using pulses with a rise time of 10 ns and a pulse width of 100 ns were conducted. Fig. 3 shows the comparison of TLP characteristics for conventional and diode triggered LVTSCR. As compared with the conventional LVTSCR, the new diode-triggered LVTSCR structure exhibits a low parasitic resistance (calculated by dv/di), because the current conduction path in the newly proposed structure is now formed by the GGNMOS together with the SCR. As shown in F, the trigger voltage decreases from 8.94 V to 7.82 V; whereas the holding voltage increases from 2.01 V to 3.21 V. In addition, the failure current, It2, also increases from 3.17 A to 4.05 A because of the availability of two current conduction paths.

Fig. 2 Cross-sectional view (a) and the schematic equivalent circuit (b) of diode-triggered LVTSCR.

Fig. 3 TLP results of conventional LVTSCR and diode-triggered LVTSCR.

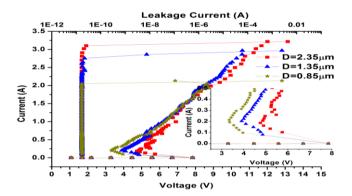

As shown in Fig. 4, when the value of D (the distance between the drain side of gate to contact of gate, see Fig. 2(a)) increases from 0.85  $\mu$ m to 2.35  $\mu$ m, It2 increases from 2.05 A to 3.1 A. When the drain contact is close to the poly gate (when D is small), the heat produced at the drain junction spreads isotropically to the contact metal and results in a lower failure current level [8]. Hence, a larger separation between the contact and the poly gate will help to increase the failure current level. On the other hand, this device behaves liking a diode when adding reverse voltage on it.

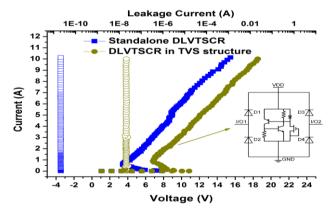

After investigating the standalone DLVTSCR, A TVS using the DLVTSCR as the core device was realized and the TLP test result is shown in Fig. 5. Taking I/O1 as an example, when adding ESD strike on I/O1 to GND, the ESD current will be released by the steer diode D1, through the DLVTSCR and then going to GND. As shown in Fig.5, the TVS structure presents a higher holding voltage of about 6.83 V and an acceptable trigger voltage of about 10.8V. These values should be acceptable for ESD protection applications for high-speed digital interfaces such as USB2.0, HDMI, AVI ports etc, in portable equipments.

Fig. 4 TLP characteristics of diode-triggered LVTSCR as a function of device spacing (D) between the gate and drain contact of GGMOS of the LVTSCR.

Fig. 5 Comparison of TLP characteristics of a standalone DLVTSCR and a TVS device embedded with a DLVTSCR.

Transient Voltage Suppressor Based on Diode-Triggered Low-voltage Silicon Controlled Rectifier 651

### 3. CONCLUSION

This paper attempts to incorporate a diode-triggered low-voltage silicon controlled rectifier into a TVS. The results show that the larger distance between the gate edge and the drain contact, the higher ESD current (It2) can be obtained. The TVS structure was further verified with the standard CMOS process and good robustness was obtained. This structure can be used for system level ESD protections for high speed digital interfaces such as USB2.0, HDMI, AVI ports, and so on.

Acknowledgement: This work was supported by the National Natural Science Foundation of China (No. 61171038, 61204124). The authors thank the Innovation Platform for Micro/Nano Device and System Integration and Cyrus Tang Centre for Sensor Materials and Applications at Zhejiang University.

#### REFERENCES

- C. Ito, K. Banerjee, R.W. Dutton, "Analysis and design of distributed ESD protection circuits for highspeed mixed-signal and RF ICs", *IEEE Trans. Electron Devices*, vol.49, pp.1444-1454, 2002.

- [2] J.-H. Ko, K.-Y. Kim, J.-S. Jeon, C.-H. Jeon, C.-S. Kim, K.-T.Lee, H.-G. Kim, "System-level ESD onchip protection for mobile display driver IC", In Proc. of the Sympo. of Electrical Overstress/ Electrostatic Discharge, 2011, pp.1-8.

- [3] A. Jahanzeb, L. Lou, C. Duvvury, C. Torres, S. Morrison, "TLP characterization for testing system level ESD performance", In Proc. of the Sympo. Electrical Overstress/Electrostatic Discharge, 2010, pp.1-8.

- [4] K. Shrier, T. Truong, and J. Felps, "Transmission line pulse test methods, test techniques and characterization of low capacitance voltage suppression device for system level electrostatic discharge compliance", In Proc. of the Sympo. Electrical Overstress/Electrostatic Discharge, 2004. pp.1-10.

- [5] H. Gossner, W. Simbürger, M. Stecher, "System ESD robustness by co-design of on-chip and on-board protection measures", *Microelectronics Reliability*, vol. 50, no. 9-11, pp.1359–1366, 2010.

- [6] M. Hove, T. O. Sanya, A. J. Snyders, I. R Jandrell and H.C. Ferreira, "The effect of type of transient voltage suppressor on the signal response of a coupling circuit for power line communications", AFRICON, 2011

- [7] S. S. Choi, D. H. Cho, K. H. Shim, "Development of transient voltage suppressor device with abrupt junctions embedded by epitaxial growth technology", *Electron. Mater. Lett.*, vol. 5, pp. 59-62, Jun 2009.

- [8] R. N. Rountree and C. L. Hutchins, "NMOS protection circuitry," *IEEE Trans. Electron Devices*, vol. 32, pp. 910-917, 1985.