#### FACTA UNIVERSITATIS

Series: Electronics and Energetics Vol. 30, No 4, December 2017, pp. 549 - 556

DOI: 10.2298/FUEE1704549S

# HIGH-BANDWIDTH BUFFER AMPLIFIER FOR LIQUID CRYSTAL DISPLAY APPLICATIONS

## Saeed Sadoni, Abdalhossein Rezai

ACECR Institute of Higher Education, Isfahan Branch, Isfahan, Iran

**Abstract.** In this paper, a novel high-bandwidth and low-power buffer amplifier is presented for the liquid crystal display applications. This buffer amplifier consists of a folded cascade differential amplifier in the input and a class-AB amplifier in the output, which are designed carefully. The proposed buffer amplifier utilizes a high-performance feedback circuit to increase the bandwidth. It also utilizes a comparator circuit to avoid wasting power. The designed circuit has been simulated in 180nm technology using HSPICE 2008.3. The simulation results show that the bandwidth, power consumption and power supply of the designed circuit are 1.14MHz, 1.64mW and 1.8V, respectively.

**Key words**: buffer amplifier, liquid crystal displays, low-power amplifier, highbandwidth amplifier

## 1. Introduction

The increasing development of electronics made living in nowadays almost impossible without electronic devices such as cell phone, television, and tablet. Progress in demands of human nature has forced science to grow up in this field [1, 2]. Display is a common factor among these devices, which helps so much in improving the progress of them. The main reason for users and market attractiveness of progress in this field is that the display devices directly interface with the users.

There are several improvements in this field, which can be categorized in two groups: (a) improvement in the circuit components, and (b) improvement in the hardware of displays. Buffer amplifiers are main part of the screens. They directly affect power consumption, settling time, speed, bandwidth and other parameters [3-5].

Developments in integrated circuit technology, particularly circuits related to displays and their improvements, indicate that there is a need to have a high-quality and high-speed circuit under low voltage source and low power consumption [3-5]. Recently, the technology and consumer tendency are portable devices such as cell phone and tablet. In this process, many attempts have been done to improve the circuits to achieve the objectives that

Received November 4, 2016; received in revised form February 20, 2017

Corresponding author: Abdalhossein Rezai

ACECR Institute of Higher Education, Isfahan Branch, Isfahan 84175-443, Iran

(E-mail: rezaie@acecr.ac.ir)

generally focus on parameters such as the slew rate, voltage swing, bandwidth, maximum load current and low power consumption [3-5].

There are many attempts to increase the performance of displays such as [6-10]. In [6], the designed circuit works well in terms of charging and discharging speed of large capacitors, but it has low bandwidth. In [7] and [8], the designed circuits have a good bandwidth, but they do not have the ability to charge large capacitors well. In [9] developed circuit works well in terms of charging and discharging speed for relatively large capacitors, but it has a relatively high power consumption. The developed circuit in [10] works well in terms of charging and discharging speed of large capacitors. The power consumption is also relatively good, but it has low bandwidth.

This paper presents a novel and efficient buffer amplifier. The proposed circuit consists of four parts, which are designed carefully. The proposed circuit has been simulated using HSPICE. The simulation results show that the proposed circuit provides an improvement in terms of bandwidth, slew rate and power consumption compared to other buffer amplifiers.

The remaining of this paper is organized as follows: general description of the proposed buffer amplifier circuit is described in section 2. Circuit design techniques are discussed in section 3. In section 4, the simulation results of the proposed buffer amplifier are compared with other buffer amplifiers. Finally, section 5 concludes this paper.

## 2. Buffer Amplifier

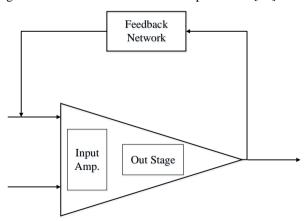

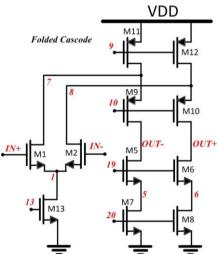

The buffer amplifiers generally consist of several parts: an input amplifier, an intermediate amplifier, a feedback network and output stage for drives capacitive loads [11]. As it is presented in Figure 1, the first block is a differential amplifier. The folded cascade amplifier is a commonly used amplifier in this stage; it is because in this amplifier due to differential inputs and outputs, the noise is eliminated. So, it has a better swing compared to telescopic amplifier. In the next block, in the output stage of class AB, the output circuit in [11] is utilized. Since two comparators are used behind the output transistors, the output efficiency is considerably increased, which prevents the static power dissipation. Figure 2 shows a schematic of the output circuit [11].

Fig. 1 A simplified buffer circuit schematic

Fig. 2 The circuit of the output stage

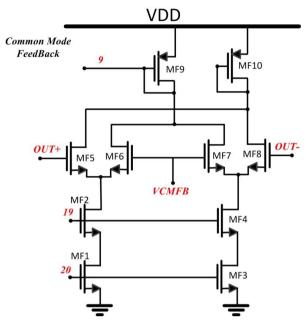

In the third part, a feedback circuit is used. As it is shown in (1), using this feedback network, the bandwidth of the buffer amplifier is increased. Figure 3 shows a schematic of feedback network [8].

Fig. 3 The feedback network schematic

#### 3. CIRCUIT DESIGN

To implement the proposed buffer amplifier circuit, the design must begin by designing circuit of folded cascade differential amplifier. Then, the common mode feedback circuit should be added. Moreover, the  $g_m$  constant circuit and the level shifter should be designed and added. To design the circuit,  $g_m/I_d$  method is used as shown in [11].

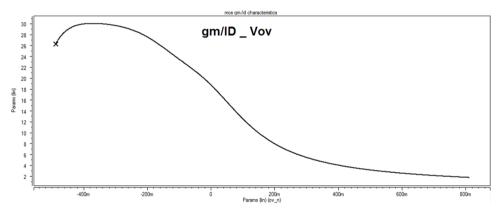

Circuit design is done using the graph of  $g_{m}/I_d$  in relation with  $V_{ov}$  [11]. In  $g_{m}/I_d$  design methodology, the circuit is designed using a curve dependent on the utilized technology. So, the possibility to choose appropriate dimensions of transistors is provided more efficiently. This curve is independent of the dimensions, and it is relevant to all areas of the transistors. In addition, it can be used to design the dimensions of all transistors in the utilized technology. It should be noted that this ratio is directly related to the coefficient of carrier mobility in transistors. According to differences in the n-type transistors, the p-type transistors are used. Thus, in designing swing with respect to transistor and the utilized technology,  $v_{ov}$  must be considered differently.

Figure 4 shows the  $g_m/I_d$  - $v_{ov}$  according to [11] for n-type transistors.

Fig. 4 The simulation results for  $g_m/I_d$  to  $v_{ov}$  for n-type transistors

In this circuit, swing voltage is 1.2Volt. With this limitation, over drive voltages are selected as shown in (2) and (3):

$$V_{ovn} = 0.13 Volt \tag{2}$$

$$V_{ovp} = 0.17 Volt \tag{3}$$

Using the same way, p-type transistors and feedback circuit are designed. In the feedback circuit design, one thing is necessary: the low current branches should be considered. So, the power consumption of the entire circuit does not increase. Feedback circuit is shown in Figure 5.

Fig. 5 The utilized circuit for the feedback in the proposed buffer amplifier

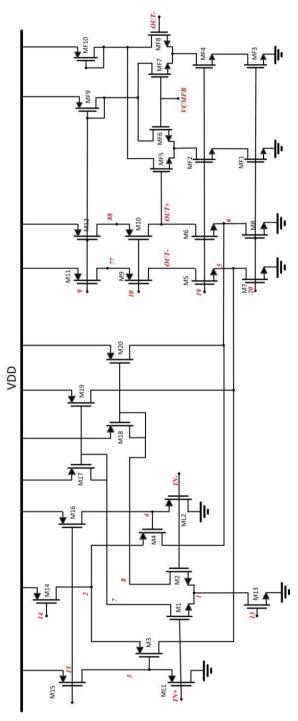

The general circuit of the proposed buffer amplifier without output stage is shown in figure 6. that utilizes two circuits as shown in Figures 2 and 3.

It should be noted that figure 2 depicts output power stage. To ensure the other driving devices MO1 and MO2 to stay off during static operation and to save power consumption, the DC currents of MC1 and MC4 are designed to be slightly lower than the nominal currents of MC2 and MC3, respectively. The above specification is fulfilled by the following design conditions:

$$\frac{\left(\frac{W}{L}\right)_{MC1}}{\left(\frac{W}{L}\right)bias_{p}} = \frac{\left(\frac{W}{L}\right)_{MC2} - \Delta\left(\frac{W}{L}\right)}{\left(\frac{W}{L}\right)bias_{n}} \tag{4}$$

$$\frac{\left(\frac{W}{L}\right)_{MC4}}{\left(\frac{W}{L}\right)bias_n} = \frac{\left(\frac{W}{L}\right)_{MC3} - \Delta\left(\frac{W}{L}\right)}{\left(\frac{W}{L}\right)bias_p}$$

(5)

$\textbf{Fig. 6} \ \text{The general circuit of the proposed buffer amplifier}$

## 4. SIMULATION RESULTS

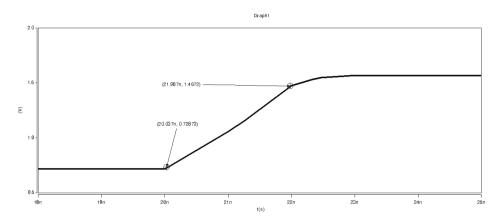

The designed circuit that is shown in figure 6 is simulated in 180nm technology using HSPICE 2008.3 with 1.8 volt power supply. The simulation results for the slew rate and bandwidth are shown in Fig. 7 and Fig. 8, respectively.

Fig. 7 The simulation results for the slew rate of the proposed circuit

Fig. 8 The simulation results for the bandwidth of the proposed circuit

Table 1 summarizes the simulation results of the proposed buffer amplifier in HSPICE in comparison with other buffer amplifiers [6-10].

Based on our simulation results, which are shown in table 1, the developed circuit provides an improvement in comparison with [6-10] in terms of bandwidth, power consumption and slew rate.

Table 1 The comparative table for amplifiers

| Reference  | Power consumption (mw) | Maximum capacitive load (pF) | CMOS<br>technology<br>(nm) | Supply<br>voltage<br>(v) | Bandwidth<br>(MHz) | Slew rate (v/µs) |

|------------|------------------------|------------------------------|----------------------------|--------------------------|--------------------|------------------|

| [6]        | 1                      | 680                          | 600                        | 4                        | 0.1                |                  |

| [7]        |                        | 15                           | 350                        | 2                        | 2.3                |                  |

| [8]        |                        | 200                          | 500                        | 3.3                      |                    |                  |

| [9]        |                        | 20000                        | 130                        |                          | 1                  | 0.083            |

| [10]       | 6.47                   | 1000                         | 500                        | 5                        | 0.503              | 5.7              |

| This paper | 1.64                   | 1000                         | 180                        | 1.8                      | 1.14               | 378              |

### 5. CONCLUSION

Low-power and high-bandwidth design are trends in the circuit design [4-5]. In this paper, a novel buffer amplifier has been proposed to be used in the liquid crystal display applications. The proposed buffer amplifier is composed of four parts, which have been designed carefully. The proposed circuit has been simulated using HSPICE. The simulation results showed that the proposed circuit provides an improvement in terms of bandwidth, power consumption and slew rate compared to [6-10]. Therefore, the proposed buffer amplifier architecture has a huge potential to be an efficient architecture for hardware implementation of buffer amplifier.

#### REFERENCES

- [1] A. Nikolic, N. Neskovic, R. Antic, A. Anastasijevic, "Industrial wireless sensor networks as a tool for remote online management of power transformers heating and cooling process", *Facta Universitatis, Series: Electronics* and Energetics. vol. 30, pp. 107-119, 2017.

- [2] R. Khalilian, A. Rezai, E. Abedini, "An efficient method to improve WBAN security", Adv. Sci. Tech. Let., vol. 64, pp. 43-46, 2014.

- [3] H. M. Obaid, S. M. Chaudhry, "Design of linear high drive class AB differential amplifier in 90 nMOS technology", Natl. Acad. Sci. Lett, vol. 38, pp. 489–492, 2015.

- [4] S. Soltany, A. Rezai, "A novel low power and low voltage bulk-input four-quadrant analog multiplier in voltage mode", Int. J. Multi. Ubiq. Eng., 2016, 16, pp. 159-168.

- [5] S. Soltany, A. Rezai, "A new low power four quadrant analog multiplier", Adv. Sci. Tech. Let., vol. 106, pp. 33-36, 2015.

- [6] C. W. Lu, C. L. Lee, "A low-power high speed class-AB buffer amplifier for flat panel display application", IEEE Trans. Very Large Integ. (VLSI) Syst., vol. 10, pp. 163-168, 2002.

- [7] G. Grasso, S. Pennisi, "High drive and linear CMOS class AB pseudo-differential amplifier", *IEEE Trans. Cir. Syst.: Expree Brifes*, vol. 54, pp. 112-116, 2007.

- [8] P. R. Surkanti, P. M. Furth, "Converting a three stage pseudo-class AB amplifier to a true class AB amplifier", IEEE Trans. Cir. Syst.: Expree Brifes, vol. 59, pp. 229-233, 2012.

- [9] P. Liao, P. Leo, B. Zhang, Zh. Li, "Single capacitor with current amplifier compensation for ultra large capacitive load three stage amplifier", *Microelectr. J.*, vol. 44, pp. 712-717, 2013.

- [10] A. D. Grasso, D. Marano, F. E. Alfaro, A. Martin, G. Palumbo, S. Pennisi, "Self-biased dual path push pull output buffer amplifier for LCD column drivers", *IEEE Trans. Cir. Syst.: Regular Papers*, vol. 61, pp. 663-670, 2014.

- [11] F. Silveira, D. Flandre, P. Jespers, "A gm/Id based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon on insulator micro power OTA", *IEEE J. Solid State Cir.*, vol. 31, pp. 1314-1319, 1996.