brought to you by CORE

Esarajula Anil Kumar\* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.4, Issue No.5, August – September 2016, 3711 – 3713.

# **Protecting Data With Fault Correction Scripts**

ESARAJULA ANILKUMAR M.Tech Student, Dept of ECE Avanthi Institute of Engineering & Technology Hyderabad, T.S, India S.MAHESH REDDY

Assistant Professor, Dept of ECE Avanthi Institute of Engineering & Technology Hyderabad, T.S, India

P.SURESH KUMAR

Associate Professor & HOD, Dept of ECE Avanthi Institute of Engineering & Technology Hyderabad, T.S, India

*Abstract:* A brand new architecture for matching the information protected by having an error-fixing code (ECC) is presented within this brief to lessen latency and complexity. Lately, however, triggered the attraction of increasingly more attentions in the academic field In line with the proven fact that the code word of the ECC is generally symbolized inside a systematic form composed from the raw data and also the parity information produced by encoding, the suggested architecture parallelizes the comparison from the data which from the parity information. To help lessen the latency and complexity, additionally, a brand new butterfly-created weight accumulator (BWA) is suggested for that efficient computation from the Hamming distance. Grounded around the BWA, the suggested architecture examines if the incoming data matches the stored data if your certain quantity of erroneous bits are remedied. For any (40, 33) code, the suggested architecture cuts down on the latency and also the hardware complexity by 32% and 9%, correspondingly, in comparison most abundant in recent implementation. Within the SA-based architecture, the comparison of two code words is invoked following the incoming tag is encoded. Therefore, the critical path includes a number of the encoding and also the n-bit comparison.

*Keywords:* Data Comparison; Error-Correcting Codes (Eccs); Hamming Distance; Systematic Codes; Tag Matching;

#### I. INTRODUCTION

Besides, the information comparison usually resides within the critical road to the constituents which are devised to improve the machine performance, e.g., caches and TLBs, whose outputs determine the flow from the succeeding procedures inside a pipeline. Data comparison is broadly utilized in computing systems to do many procedures like the tag matching inside a cache memory and also the virtual-to-street address translation inside a translation look aside buffer (TLB). Due to such prevalence, you should implement the comparison circuit with low hardware complexity [1]. The circuit, therefore, should be made to have as low latency as you possibly can, or even the components is going to be disqualified from becoming accelerators and also the efficiency from the whole system could be seriously deteriorated. As recent computer systems employ error-fixing codes (ECCs) to safeguard data and improve reliability, complicated deciphering procedure, which must precede the information comparison, elongates the critical path and exacerbates the complexness overhead. Thus, it might be more difficult to satisfy the above mentioned design constraints. Despite the requirement for sophisticated designs as described, the whole shebang that deal with the issue aren't broadly known within the literature since it's been usually treated within industries for his or her items [2]. Therefore, the technique eliminates the complex deciphering in the critical path. In carrying out the comparison, the technique doesn't examine if the retrieved information is exactly like the incoming data. Rather, it inspections when the retrieved data resides within the error correctable selection of the code word akin to the incoming data. The newest solution for that matching issue is the direct compare method, which encodes the incoming data after which compares it using the retrieved data that's been encoded too. Because the checking necessitates yet another circuit to compute the Hamming distance, i.e., the amount of different bits backward and forward code words, the saturate adder (SA) was presented, like a fundamental foundation for calculating the Hamming distance. However, it didn't consider an essential proven fact that may enhance the effectiveness further, an operating ECC code word is generally symbolized inside a systematic form where the data and parity parts are totally separated from one another. Additionally, because the SA always forces its output to not be more than the amount of noticeable errors by several, it plays a role in the rise from the entire circuit complexity. Within this brief, we renovate the SA-based direct compare architecture to lessen the latency and complexity hardware by resolving these drawbacks. More particularly, we think about the qualities of systematic codes in creating the suggested architecture and propose a minimalcomplexity processing element that computes the Hamming distance faster. Therefore, the latency and also the hardware complexity are decreased

significantly even in comparison using the SA based architecture.

### **II. PREVIOUS WORKS**

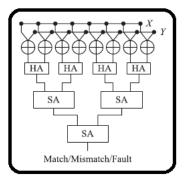

This describes the traditional decode-and-compare architecture and also the encode-and-compare architecture in line with the direct compare method. With regard to concreteness, just the tag matching carried out inside a cache memory is talked about brief: however the suggested within this architecture does apply to similar programs without lack of generality [3]. Observe that deciphering is generally more complicated and takes additional time than encoding because it includes a number of error recognition or syndrome calculation, and error correction. The implementation results, offer the claim. To solve the drawbacks from the decodeand-compare architecture, therefore. the deciphering of the retrieved code word is changed using the encoding of the incoming tag within the encode-and-compare architecture. The next half adders (HAs) are utilized to count the amount of 1's in 2 adjacent bits within the vector. The figures of 1's are accrued by passing with the following SA tree.

## Fig.1. SA-based Structure III. PROPOSED METHOD

This presents a brand new architecture that may lessen the latency and complexity from the data comparison using the qualities of systematic codes. Additionally, a brand new processing element is given to lessen the latency and complexity further. Within the SA-based architecture, the comparison of two code words is invoked following the incoming tag is encoded. Therefore, the critical path includes a number of the encoding and also the n-bit comparison. However, didn't think about it that, used, the ECC code word is of the systematic form where the data and parity parts are totally separated. Because the data a part of an organized code word is exactly like the incoming tag field, it's immediately readily available for comparison as the parity part opens up after the encoding is finished. Within the suggested architecture, therefore, the encoding tactic to create the parity bits in the incoming tag is carried out in parallel using the tag comparison, lowering the overall

latency. The suggested architecture grounded around the data path set it up consists of multiple butterfly-created weight accumulators suggested to enhance the latency and complexity from the Hamming distance computation. The fundamental purpose of the BWA would be to count the amount of 1's among its input bits. It includes multiple stages of has where each output small HA is connected having a weight [4]. The HAs inside a stage are connected inside a butterfly form in order to accumulate the carry bits and also the sum items of top of the stage individually. This connection method results in a property when an output small HA is placed, the amount of 1's one of the bits within the pathways reaching the HA is equivalent to the load from the output bit. Since what we should need isn't the precise Hamming distance however the range it goes to, you'll be able to simplify the circuit. We currently explain the general architecture in greater detail. Each XOR stage creates the bitwise difference vector for either data bits or parity bits, and also the following processing elements count the amount of 1's within the vector, i.e., the Hamming distance. Each BWA in the first level is incorporated in the modified form, and creates an output in the OR-gate tree and many weight bits in the HA trees. Within the interconnection, such outputs are given to their connected processing elements in the second level. The creation of the OR-gate tree is attached to the subsequent OR-gate tree in the second level, and also the remaining weight bits are attached to the second level BWAs based on their weights. More precisely, the items of weight w are attached to the BWA accountable for w-weight inputs. Using the outputs from the preceding circuits, the choice unit finally determines when the incoming tag matches the retrieved code word by thinking about the 4 ranges from the Hamming distance. The choice unit is actually a combinational logic which functionality is per a truth table that can take the outputs from the preceding circuits as inputs. The along with the latency complexness of combinational circuits heavily is dependent around the formula employed. Additionally, because the complexity and also the latency are often conflicting with one another, it's regrettably difficult to derive an analytical and fully deterministic equation that shows the connection between the amount of gates and also the latency for that suggested architecture and for the traditional SA-based architecture. To bypass the problem in analytical derivation, we present rather a manifestation you can use to estimate the complexness and also the latency by using some variables for those non deterministic parts [5]. Among BWAs in the first level finishes sooner than another, some components in the second level may begin earlier. Similarly, some BWAs or even the OR-gate tree in the second level may provide

their output earlier towards the decision unit so the unit can start its operation without waiting its inputs.

### IV. CONCLUSION

The suggested architecture examines if the incoming data matches the stored data if your certain quantity of erroneous bits are remedied. To lessen the latency, the comparison from the information is parallelized using the encoding procedure that creates the parity information. The parallel procedures are enabled in line with the proven fact that the systematic code word has separate fields for that data and parity. To lessen the latency and hardware complexity, a brand new architecture continues to be presented for matching the information protected by having an ECC. Though this brief focuses only around the tag match of the cache memory, the suggested technique is relevant to diverse programs that require such comparison. Additionally, a competent processing architecture continues to be given to further minimize the latency and complexity. Because the suggested architecture helps to reduce the latency along with the complexity significantly, it may be considered like a promising solution for that comparison of ECC-protected data.

### V. REFERENCES

- J. D. Warnock, Y.-H. Chan, S. M. Carey, H. Wen, P. J. Meaney, G. Gerwig,H. H. Smith, Y. H. Chan, J. Davis, P. Bunce, A. Pelella, D. Rodko, P. Patel, T. Strach, D. Malone, F. Malgioglio, J. Neves, D. L. Rude, and W. V. Huott "Circuit and physical design implementation of the microprocessor chip for the zEnterprise system," *IEEE J. Solid-State Circuits*, vol. 47, no. 1, pp. 151–163, Jan. 2012.

- [2] Y. Lee, H. Yoo, and I.-C. Park, "6.4Gb/s multi-threaded BCH encoder and decoder for multi-channel SSD controllers," in *ISSCC Dig. Tech. Papers*, 2012, pp. 426– 427.

- [3] A. Jas, C. V. Krishna, and N. A. Touba, "Hybrid BIST based on weighted pseudorandom testing: A new test resource partitioning scheme," in Proc. 19th IEEE Proc. VLSI Test Symp. (VTS), 2001, pp. 2– 8.

- [4] S. Wang, "Generation of low power dissipation and high fault coverage patterns for scan-based BIST," in Proc. Int. Test Conf. (ITC), 2002, pp. 834–843.

- [5] V. Gherman, H. Wunderlich, H. Vranken, F. Hapke, M. Wittke, and M. Garbers, "Efficient pattern mapping for deterministic

logic BIST," in Proc. Int. Test Conf. (ITC), Oct. 2004, pp. 48–56.

### **AUTHOR's PROFILE**

Esarajula anilkumar Received the bachelor of

degree in Avanthi scientific technological and research academy. Pursuing Mtech Avanthi Institute of Engineering & Technology Hyderabad, T.S, India

S.Mahesh reddy assistant prof. Received the

assistantprof.Received theMasters of Technology degree inECE(Vles) in DRK College ofEngineering From JNTU HYD.He received the Bachelor ofDegree inP.Indra ReddyMemorialEngineeringCollege Hyderabad.He iscurrently working as Assistant

professor of ECE in Avanthi Institute of Engineering and Technology Hyd. Experience 3 Yrs, His interest subjects are LDIC, MPMC, PDC and Academic Projects.etc

P. Suresh Kumar is an Associate Professor. He

completed Bachelor's degree in Electronics and Communications from JNTU, Ananthapuram. And also completed Master's Degree in Digital system & Computer Sciences from Sreenidhi Institute of Science and Technology,

Hyderabad. His favourite subjects are EDC,DC,ECA, Digital Systems.