K. Srinivasulu\* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.4, Issue No.4, June – July 2016, 3273 – 3274.

# Designing A 10-Pin Integrated Circuit That Uses Reduced Switching Time

Dr. K.SRINIVASULU Professor & HOD, Dept of ECE Narsimha Reddy Engineering College Hyderabad, T.S, India K.MANASA Assistant Professor, Dept of ECE Narsimha Reddy Engineering College Hyderabad, T.S. India

*Abstract:* The primary goal of VLSI designers is low current and occasional power for the man-made circuits. Although the power consumption is low the unit speed should to become high. VLSI- Large Integration Technology where countless transistors which may be integrated on one nick or single die. However these that have the mixture of both digital and analog function. An SPST switch includes a single pole and may connect just one line with other network. The switching performance is dependent around the switching some time and power dissipation inside it. This paper signifies just one pole single through (SPST) analog switch designed using VLSI. SPST (Single Pole Single Throw) is a straightforward on-off switch: The 2 terminals are generally connected together or disconnected from one another. Once the two terminals are connected the input signal is passed towards the output terminal. This research is completed to create a brand new SPST switch that disappears really low power and also the switching time can also be really low. Initially design from the switch continues to be developed whose output will be given to some refresh circuit. Just one MOSFET could be a fix for your problem. But other problem comes from it. A pad frame was created where the original circuit is imported to create a 10 pin integrated circuit (IC). The refresh circuit can be used to reshape the signal because it altered because of switching effect. The creation of the refresh circuit is located in inverted and non-inverted form.

Keywords: SPST, VLSI, Power Dissipation, Refresh Circuit, Layout, Pad Frame.

### I. INTRODUCTION

A switch might be directly altered with a human like a control signal to some system, like a key pad button, in order to control power flow inside a circuit, like a light switch. Instantly-operated switches may be used to control the motions of machines, for instance, to point that the garage doors has arrived at its full open position or that the machine tool is capable of accept another work piece [1]. Switches might be run by process variables for example pressure, temperature, flow, current, current, and pressure, serving as sensors inside a process and accustomed to instantly control a method. N electronics, a switch is definitely an electrical ingredient that can break an electric circuit, stifling the present or diverting it in one conductor to a different. Probably the most familiar type of switch is really a by hand operated electromechanical device with a number of teams of electrical contacts. Each group of contacts could be in 1 of 2 states: either 'closed' meaning the contacts are touching and electricity can flow together, or 'open', meaning the contacts are separated and non-performing. SPST (Single Pole Single Throw) is a straightforward on-off switch: The 2 terminals are generally connected together or disconnected from one another. Once the two terminals are connected the input signal is passed towards the output terminal. The diode, BJT or MOSFETs can be used the SPST switch. However the problems from the diode and BJT switches are that they're slow functioning and dissipate greater power. Just one MOSFET could be a fix for your

problem. But other problem comes from it. The output sheds by some threshold current. So, the SPST switch is implemented with CMOS technology. You can use it to simplify digital logic circuits in order to switch analog signals, and thus is also referred to as an analog switch. It's produced by the parallel mixture of an nMOS along with a pMOS transistor using the input in the gate of 1 transistor being complementary towards the input in the gate from the other. So, if these switches are cascaded, then your logic level sheds after a little stage. To resolve this, a pass gate can be used. The pass gate could be implemented using diode logic and transistor logic, but when offers reduced operation and greater power dissipation [2]. It might appear that the transmission gate might be built using just a single pMOS or nMOS transistor. If perhaps a person nMOS transistor may be used, there would be a high current around the OUT along with a low current around the IN which is attempted to deliver the zero towards the OUT, then your nMOS will drain a few of the current but not every one of it departing the OUT somewhere within the "no man's land" current region of digital circuits. Adding the pMOS gate in parallel enables all of the current to empty following the nMOS turns off prior to the current is drained. To get rid of the distortion from the output signal a refresh circuit has been utilized to apply a complete SPST switch [3]. This solves the issue when transmitting a higher current to OUT. Even though the current level is retrieved the thermal noise distorts the signals.

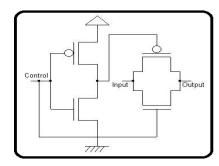

Fig.1.Block diagram of SPST Switch

### **II. IMPLEMENTATION**

The main objective of VLSI designers is low current and periodic power for those man-made circuits. Even though the power consumption is low the system speed should to get high. Thus the dynamic and static logic styles are employed in which the static logic families to evaluate the output whenever there is a port variation. The circuit diagram using only one pass gate plus an inverter is proven inside the figure. When Control is HIGH both NMOS and PMOS is ON, as well as the input is passed for the output terminal. Otherwise, both MOSFETs are OFF as well as the input and output terminals are disconnected. The essential cell or unit cell was produced while using the pass transistors. The pass transistors are employed to make sure that both logic levels can pass precisely and fully. Design diagram from the unit cell is proven inside the figure. The recommendations of layout diagram are maintained to provide the system with minimum area. The development of the cell might have thermal noise inside the device. For this reason a refresher circuit is cascaded within the output finish from the aforementioned figure. Thus the diagram of unit cell is altered by utilizing unit cell in figure2. In this particular method the output is situated in inverted and non-inverted form. OUT is at inverted form and INVOUT is at inverted form. Transistors are generation x of vacuum tubes [4]. Vacuum tubes, consumes 100s of volts of anode current and handful of watts of power. But transistors needed only mill watts of power. Generation x this can be IC which has very less power dissipation. Powered by batteries application that's known as low power electronics- for instance electronic hands hand calculators. Thus power requirement reduction is probably the liable characteristics for microelectronics technology. You'll find three reasons for power dissipation. The foremost is due to signal transitions, second arises from short circuit power, as well as the third is because of leakage power [5]. Many circuit techniques are recommended which reduces dissipated power in VLSI circuit design. Some techniques are choose Static along with a couple of techniques are choose dynamic. In CMOS, where dissipated power is because of logic transition in switching activity

logic transitions are predominant. Thus, another way of having an influence on delay from the CMOS circuit is modifying W/L ratio.

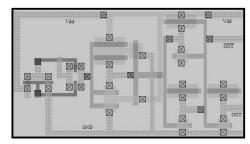

## Fig.2.Framework of the SPST Switch with refresh circuit

### III. CONCLUSION

To create any logic circuits for complex selection of products inverter is within need. It's important for rebuilding logic levels for NAND, NOR gates, for consecutive and memory circuits. IC includes layers of insulating semi performing and performing region. They are layers that are put together create transistors. They to are interconnected to make a certain preferred electrical function. The designed switch works correctly as described in result analysis and also the power dissipation is .00251nW that is really low. The aim of this paper ended up being to design a SPST switch and also to minimize the ability dissipation through it. The look could be licensed to become correct, because all of the design rules were maintained and there wasn't any DRC (Design Rule Check) error found. Further analysis can be achieved to lessen the ability increasingly more. Additionally, it works extremely fast. The switch does apply to power routing, audio/video signal routine, communication circuits, modems etc.

### **IV. REFERENCES**

- [1] L.M. Brackendury, Design of VLSI system: A practical introduction, 2nd edition, McMillan Education Ltd., 2002

- [2] D.A. Pucknell and K. Eshraghian, Basic VLSI design, 2nd ed., Tata McGraw Hill, 2001

- [3] B. Razavi, Design of analog CMOS integrated circuits, 1st ed., Tata Mcgraw Hill, 2001

- [4] N.H.E. Weste, D. Harris, A. Banerjee, CMOS VLSI design: A circuits and systems perspective, 3rd ed., Pearson education, 2006.

- [5] D.A. Bell, Solid state pulse circuits, 4th edition, Pearson Educaion, 2007.