Vemuri.Guravaiah\* et al. (IJITR) INTERNATIONAL JOURNAL OF INNOVATIVE TECHNOLOGY AND RESEARCH Volume No.2, Issue No. 4, June – July 2014, 1160 – 1163.

# Scheming of Resourceful Carry Select Adder for Supporting VLSI System

VEMURI.GURAVAIAH M.Tech Student Dept of ECE Anurag Engineering College Kodad, T.S, India Mr. M.BASHA Associate Professor Dept of ECE Anurag Engineering College Kodad, T.S, India Dr.M.V.SIVA PRASAD Professor Dept of ECE Anurag Engineering College Kodad, T.S, India

*Abstract:* Designing of area as well as power proficient high speed systems of data logic are one of the major considerable areas of exploration in VLSI system design. Carry Select Adder is a speedy adder used in data processing processors for carrying out speedy arithmetic functions and are categorized as Linear Carry select adder as well as Square-root Carry select adder. The fundamental proposal of this work is to make use of Binary to Excess-1 converter (BEC) rather than ripple carry adders with carry in 1 in normal Carry select adder system to accomplish inferior area. Introduction of a multiplexer based add one circuit was projected to decrease area with insignificant speed penalty. The analysis illustrate that the modified linear carry select adder system as well as modified square-root carry select adder system. The main advantage of Binary to Excess-1 converter comes from the minor number of logic gates than n-bit Full Adder. In designing of Integrated circuits, area occupancy plays a fundamental responsibility since rising requirement of portable systems. For dropping area, CSLA is put into practice by means of a single RCA as well as an add-one circuit as opposed to using dual RCA. The Modified CSLA design is consequently, low area, uncomplicated and well-organized for VLSI hardware performance.

Keywords: Ripple carry adders, Carry Select Adder, Multiplexer, Binary to Excess-1 converter.

#### I. INTRODUCTION

In applications concerning electronics adders are mainly used. In digital adders, speed of adding is restricted by time which is necessary to transmit a carry all the way through adder [4]. The sum in support of each bit arrangement in elementary adder is produced successively merely subsequent to preceding bit position were summed and a carry transmitted into subsequent position. Instead of using dual ripple carry adders a carry select adder system by means of add one circuit was used to restore one ripple carry adders. Carry select adder system is used in numerous computational systems to alleviate the difficulty of carry propagation delay by autonomously making numerous carries and subsequently select a carry to produce the sum [8]. Carry select adder system is not area resourceful since it make use of numerous pairs of ripple carry adders to make partial sum and transmit by taking into consideration carry in 0 as well as carry in 1, subsequently the concluding sum with carry are selected by multiplexers. The fundamental proposal of this work is to make use of Binary to Excess-1 converter (BEC) rather than ripple carry adders with carry in 1 in normal Carry select adder system to accomplish inferior area [1]. The main advantage of Binary to Excess-1 converter comes from the minor number of logic gates than n-bit Full Adder. When comparing regular linear carry select adder system by way of regular square-root carry select adder system, it has condensed area in addition to

evaluating modified linear carry select adder system with modified square-root carry select adder system; the modified square-root carry select adder system has condensed area [11]. The analysis illustrate that the modified linear carry select adder system as well as modified square-root carry select adder system make available enhanced outcomes than regular linear carry select adder system and regular square-root carry select adder system correspondingly.

### II. METHODOLOGY

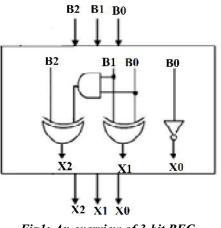

Designing of area as well as power proficient high speed systems of data logic are one of the major considerable areas of exploration in VLSI system design [3]. Addition typically impacts extensively the general performance of digital systems as well as an arithmetic function. The carry select adders are categorized as Linear Carry select adder as well as Square-root Carry select adder [14]. The difficulty of carry propagation impediment is prevailed over by autonomously producing multiple radix carries as well as usage of carries to select among concurrently generated sums. Introduced a multiplexer based add one circuit was projected to decrease area with insignificant speed penalty. A structure of 3-bit BEC is revealed in fig1. An area efficient Square-root CSLA system was introduced based on a novel first zero detection logic [9]. In designing of Integrated circuits, area occupancy plays a fundamental responsibility since rising requirement of portable systems. Carry

Select Adder is a speedy adder used in data processing processors for carrying out speedy arithmetic functions [7]. From construction of Carry Select Adder, the extent is to decrease the region of Carry Select Adder based on competent modification. Introduction gate-level and comparison of 128 bit Regular Linear carry select adder system, Modified Linear carry select adder system, Regular Square-root carry select adder system as well as Modified SQRT CSLA designing were developed and compared [12]. Regular CSLA is area-consuming due to dual Ripple Carry Adder construction. For dropping area, CSLA is put into practice by means of a single RCA as well as an add-one circuit as opposed to using dual RCA. The linear carry select adder is build by chaining numeral of equivalent stages of length adder [2]. For an n-bit adder, it may possibly be executed by equivalent length of carry select adder and is known as linear carry select adder. The square-root carry select adder is build by balancing the impediment all the way through two carry chains as well as block multiplexer signal from preceding phase and it is known as non-linear carry select adder. The basic square-root Carry Select adder encompass a dual ripple carry adder by 2:1 multiplexer, the major difficulty of regular carry select adder system is huge area due to multiple pairs concerning ripple carry adder [16]. The arrangement of the 16-bit regular Linear CSLA encompasses 4 groups of similar size ripple carry adders. Every group holds dual ripple carry adders as well as multiplexer. It achieves the adding up by accumulation of small portions of bits and remains for carry to complete computation. Sum as well as carry is intended for both promising solutions [5]. The linear carry select adder is build by chaining number of equivalent length adder stages. Equal size of inputs is specified to every block of adder. The steps leading towards assessment are specified. In regular linear carry select adder system, the group3 contain two sets of 4-bit ripple carry adders [15]. The approximated region of previous groups in regular linear carry select adder system is assessed. The construction of 16-bit regular Square-root CSLA includes 5 groups of dissimilar size ripple carry adders. Every group hold dual ripple carry adders as well as multiplexer. The linear carry select adder has single main difficulty that is elevated area usage. This difficulty can be put right by Square-root CSLA consequently it is an enhanced one of linear CSLA. The time stoppage of linear adder can reduce through containing one more input into every set of adders than in preceding set and is known as Square-root CSLA [10]. In regular Square-root CSLA, the group3 encompass two sets concerning 3-bit ripple carry adders. The construction of projected 16-bit Linear and Square-root CSLA by means of BEC in support of ripple carry adders to optimize the area

is made known. The 16-bitmodified Linear CSLA contains 4 groups of comparable size ripple carry adders. Every group hold one ripple carry adders, one BEC and multiplexer [6]. The approximated region of previous groups in modified Linear CSLA is assessed. The structure of 16-bit modified Square-root CSLA contains 5 groups of dissimilar size RCA as well as BEC [13]. Every group hold one ripple carry adders, one BEC and multiplexer.

Fig1: An overview of 3-bit BEC

## III. RESULTS

The analysis illustrate that the modified linear carry select adder system as well as modified square-root carry select adder system make available enhanced outcomes than regular linear carry select adder system and regular square-root carry select adder system correspondingly. It is obvious that area of 16-bit, 32-bit, 64-bit as well as 128-bit projected modified SQRT CSLA is condensed when evaluated with area of previous CSLAs. The condensed numbers of gates recommend immense benefit in decrease of area. From result analysis 128-bit Modified square-root carry select adder system has condensed area compared with Regular Linear carry select adder system, Regular SQRT carry select adder system as well as Modified Linear carry select adder system. The area of projected design illustrates a reduction in support of 16-bit, 32-bit, 64-bit as well as 128-bit sizes which point towards the achievement of method and not a simple trade-off of impediment for area. The Modified CSLA design is consequently, low area, uncomplicated and well-organized for VLSI hardware performance.

## IV. CONCLUSION

In applications concerning electronics adders are mainly used. Addition typically impacts extensively the general performance of digital systems as well as an arithmetic function. Carry select adder system is used in numerous computational systems to alleviate the difficulty of carry propagation delay by autonomously making numerous carries and subsequently select a carry to produce the sum. It is not area resourceful since it

makes use of numerous pairs of ripple carry adders to make partial sum. The fundamental proposal of this work is to make use of Binary to Excess-1 converter (BEC) rather than ripple carry adders with carry in 1 in normal Carry select adder system to accomplish inferior area. Instead of using dual ripple carry adders a carry select adder system by means of add one circuit was used to restore one ripple carry adders.

An area efficient Square-root CSLA system was introduced based on a novel first zero detection logic. From construction of Carry Select Adder, the extent is to decrease the region of Carry Select Adder based on competent gate-level modification. The main advantage of Binary to Excess-1 converter comes from the minor number of logic gates than n-bit Full Adder. The difficulty of carry propagation impediment is prevailed over by autonomously producing multiple radix carries as well as usage of carries to select among concurrently generated sums. The linear carry select adder is build by chaining numeral of equivalent stages of length adder. The analysis illustrate that the modified linear carry select adder system as well as modified square-root carry select adder system make available enhanced outcomes than regular linear carry select adder system and regular square-root carry select adder system correspondingly. The square-root carry select adder is build by balancing the impediment all the way through two carry chains as well as block multiplexer signal from preceding phase.

### REFERENCES

- [1] "Enhanced Area Efficient Architecture for 128 bit Modified CSLA", R.Priya, J.Senthil Kumar, 2013

- [2] P. Sreenivasulu, K. Srinivasa rao, Malla Reddy and A. Vinay Babu, "Energy and area efficient carry select adder on a reconfigurable hardwware", International Journal of Engineering Research and Applications, vol. 2, Issue. 2, pp. 436-440, Mar 2012.

- [3] Y. He, C. H. Chang, and J. Gu, "An area efficient 64-Bit square Root carry-select adder for low powerApplications, " in Proc. IEEE Int. Symp.Circuits Syst.,vol. 4, pp. 4082-4085, 2005.

- [4] I-Chyn Wey, Cheng-Chen Ho, Yi-Sheng Lin and Chien-Chang Peng, "An area efficient carry select adder design by sharing the common boolean logic term", Proceedings on the International Multiconference of Engineering and computer scientist, IMECS 2012

- [5] Padma Devi, Ashima Girdher and Balwinder Singh"Improved Carry Select Adder with Reduced Areaand Low Power Consumption, "International Journalof Computer Applications, Vo1.3, No.4, pp. 14-18,1998.

- [6] Edison A. J and C. S. Manikanda babu, "An efficient CSLA architecture for VLSI hardware implementation", Interanational Journal for Mechanical and Industrial Engineering, vol. 2, Issue 5, 2012

- [7] B. Ramkumar, H.M. Kittur, and P. M. Karman, "ASIC implementation of modified faster carry save adder, "Eur. J. Sci. Res., vol. 42, no. 1, pp.53-58, 2010

- [8] He, Y. Chang, C. H. and Gu, J. "An Area Efficient 64-Bit Square Root Carry-Select Adder For Low PowerApplications, " in Proc. IEEE Int. Symp. Circuits Syst., Vol.4, pp. 4082-4085, 2005

- [9] B. Ramkumar and Harish M Kittur, "Low power and area efficient carry select adder", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 20, no. 2, pp. 371-375, Feb 2012.

- [10] J. M. Rabaey, Digital Integrated Circuits-A Design Perspective, Upper Saddle River, NJ: Prentice-Hall, 2001

- [11] R. Priva and J. Senthilkumar. "Implementation and comparision of effective area efficient architecuture for CSLA", Proceedings of IEEE InternationalConference on Emerging trends in Computing, Communicaton and Nano Technology, pp. 287-292, 2013

- [12] T. Y. Ceiang and M. 1. Hsiao, "Carry-select adder usingsingle ripple Carry adder, " Electron. Lett, vol. 34, no.22, pp. 2101-2103, Oct. 1998

- [13] Akhilesh Tyagi, "A Reduced-Area Scheme for CarrySelectAdders," IEEE Transactions on Computers, Vol.42, No.1 0, pp.1163-1170, 1993.

- [14] B. Ramkumar, Harish M Kittur and P. M. Kannan, "ASIC implementation of modified faster carry save adder", Eur. J. Sci. Res., vol. 42, no. 1, pp. 53-58, Jun 2010.

- [15] Y. Kim and L.-S. Kim, "64-bit carry-select adder withreduced area," Electron. Lett. vol. 37, no. 10, pp. 614-615, May 2001

- [16] T. Y. Ceiang and M. J. Hsiao, "Carry select adder using single ripple carry adder", Electron. Lett, vol. 34, no. 22, pp. 2101-2103, Oct 1998.

V.Guravaiah is a under graduate in Electronics &

communication in The vazir sulthan college of engineering, Khammam from Kakatiya University.

Mr. M.Basha is a Post graduate in Electronics &

communicationfrom JNTU Ananthapur. He has 7 Years of UG&PG Levels in Teaching Experience. Ratified as Assistant Professor by the JNTU-HYD.

Dr.M.V.Siva Prasad is a post graduate in Computer Science & Engineering from Nagarjuna University, Guntur. He has 20 Years of UG & PG Levels Teaching experience. Ratified as Assistant Professor by the JNTU-HYD on 29-12-1999. Life member of ISTE M.No. :LM 53293 / 2007.