# Performance Improvements Using Dynamic Performance Stubs

PhD Thesis Peter Trapp

Software Technology Research Laboratory De Montfort University

This thesis is submitted in partial fulfillment of the requirements for the Doctor of Philosophy.

July 2011

To my family.

# Abstract

If you think performance is expensive, try using a paralyzed system. . . .

This thesis proposes a new methodology to extend the software performance engineering process. Common performance measurement and tuning principles mainly target to improve the software function itself. Hereby, the application source code is studied and improved independently of the overall system performance behavior. Moreover, the optimization of the software function has to be done without an estimation of the expected optimization gain. This often leads to an under- or over-optimization, and hence, does not utilize the system sufficiently.

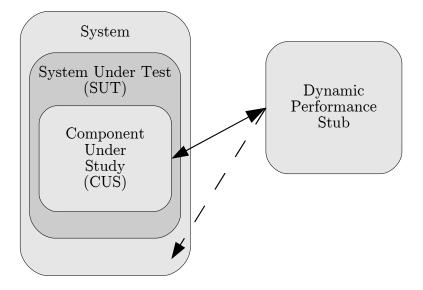

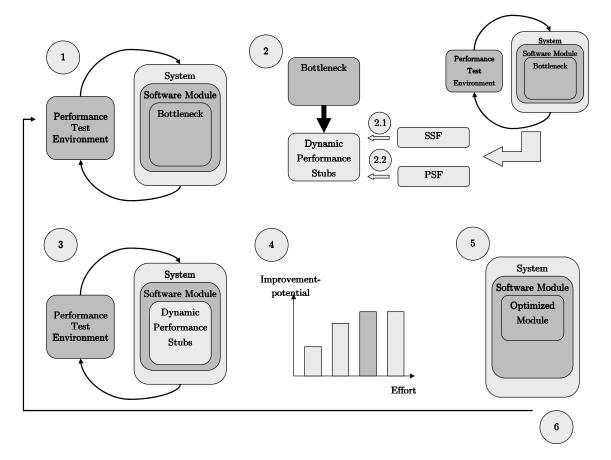

The proposed performance improvement methodology and framework, called dynamic performance stubs, improves the before mentioned insufficiencies by evaluating the overall system performance improvement. This is achieved by simulating the performance behavior of the original software functionality depending on an adjustable optimization level prior to the real optimization. So, it enables the software performance analyst to determine the systems' overall performance behavior considering possible outcomes of different improvement approaches. Moreover, by using the dynamic performance stubs methodology, a cost-benefit analyses of different optimizations regarding the performance behavior can be done.

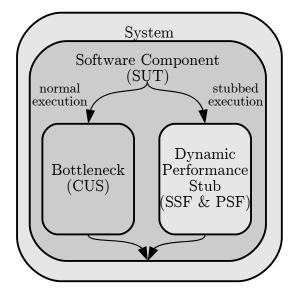

The approach of the *dynamic performance stubs* is to replace the software bottleneck by a stub. This stub combines the simulation of the software functionality with the possibility to adjust the performance behavior depending on one or more different performance aspects of the replaced software function. A general methodology for using *dynamic performance stubs* as well as several methodologies for simulating different performance aspects are discussed. Finally, several case studies to show the application and usability of the *dynamic performance stubs* approach are presented.

# Declaration

I hereby declare that this thesis is my own work undertaken by me between July 2007 and July 2011 for the degree of Doctor of Philosophy. It is submitted at the Software Technology Research Laboratory (STRL), De Montfort University, United Kingdom. I have not used any sources or aids other than those stated and marked verbatim and indirect quotations as such.

# Publications

- Dynamic Performance Stubs:

- Journals:

- Peter Trapp, Markus Meyer, Christian Facchi, Helge Janicke, and François Siewe. Building CPU Stubs to Optimize CPU Bound Systems: An Application of Dynamic Performance Stubs. International Journal on Advances in Software, 4(1&2), 2011. (accepted paper)

- Conferences and Workshops:

- Markus Meyer, Helge Janicke, Peter Trapp, Christian Facchi and Marcel Busch. *Performance Simulation of a System's Parallelization*. In ICSEA '11: Proceedings of the International Conference on Software Engineering Advances. 2011. (accepted paper)

- Peter Trapp, Markus Meyer and Christian Facchi. Dynamic Performance Stubs to Simulate the Main Memory Behavior of Applications. In SPECTS '11: Proceedings of the International Symposium on Performance Evaluation of Computer and Telecommunication Systems. IEEE Communications Society, 2011.

- Peter Trapp, Markus Meyer and Christian Facchi. Using CPU Stubs to Optimize Parallel Processing Tasks: An Application of Dynamic Performance Stubs. In ICSEA '10: Proceedings of the International Conference on Software Engineering Advances. IEEE Computer Society, 2010. (Best Paper Award)

- Peter Trapp and Christian Facchi. Main Memory Stubs to Simulate Heap and Stack Memory Behavior. In Computer Measurement Group 2010: International Conference Proceedings. Computer Measurement Group, Orlando (FL), 2010.

- Peter Trapp, Christian Facchi and Markus Meyer. Echtzeitverhalten durch die Verwendung von CPU Stubs: Eine Erweiterung von Dynamic Performance Stubs. In Workshop "Echtzeit 2009 - Softwareintensive Verteilte Echtzeitsysteme". Springer-Verlag, Boppart (Germany), 2009.

- Peter Trapp, Christian Facchi and Sebastian Bittl. The Concept of Memory Stubs as a Specialization of Dynamic Performance Stubs to Simulate Memory Access Behavior. In Computer Measurement Group 2009: International Conference Proceedings. Computer Measurement Group, Dallas (TX), 2009.

- Peter Trapp and Christian Facchi. How to Handle CPU Bound Systems: A Specialization of Dynamic Performance Stubs to CPU Stubs. In Computer Measurement Group 2008: International Conference Proceedings, pages 343-353. Computer Measurement Group, Las Vegas (NV), 2008.

- Technical Reports:

- Peter Trapp, Markus Meyer and Christian Facchi. How to Correctly Simulate Memory Allocation Behavior of Applications by Calibrating Main Memory Stubs. Technical Report 20, Ingolstadt University of Applied Sciences, May 2011.

- Peter Trapp and Christian Facchi. Performance Improvement Using Dynamic Performance Stubs. Technical Report 14, Ingolstadt University of Applied Sciences, August 2007.

- Software Performance Engineering:

- Workshops:

- Christian Facchi, Peter Trapp and Jochen Wessel. Metrics and SCRUM in Real Life – Enemies or Friends? In SMEF 2011 (Software Measurement Europe Forum). Rome, Italy.

- Christian Facchi, Peter Trapp and Jochen Wessel. Enhancing Continuous Integration by Metrics and Performance Criteria in a SCRUM Based Process - Metrics and SCRUM in an Industrial Environment: A Contradiction? In EPIC 2010 (Workshop on Leveraging Empirical Research Results for Software Business Success). Bolzano, Italy.

# Acknowledgements

First of all, I like to thank Christian Facchi for his continuing support, advises and contributions during my studies and in all matters.

I would like to thank my supervisors François Siewe and Hussein Zedan for their guidance and critical analysis for the completion of this thesis. Many thanks go to Lynn Ryan and Lindsey Trent for their ongoing support.

Special thanks go to my friends and colleagues Helge Janicke, Markus Meyer, Sebastian Röglinger and Alexander Ost. They contributed in so many ways. Thank you for that.

My gratitude is to my family. This thesis would not have been possible without them. I love you.

I like to thank our industrial partner for their ongoing and thoroughly support for this thesis. They provided an industrial environment for validating our approaches. Especially, I like to thank: Rudi Bauer, Oliver Korpilla, John Mackenzie, Karl Mattern, Jörg Monschau, Florian Oefelein, Marco Seelmann, Helmut Voggenauer and Jochen Wessel.

#### Thank you!

# Contents

| List of Figures |       |                                                                                                 |                                                   |  |    | vii  |

|-----------------|-------|-------------------------------------------------------------------------------------------------|---------------------------------------------------|--|----|------|

| List of Tables  |       |                                                                                                 |                                                   |  |    | viii |

| Li              | st of | Listin                                                                                          | gs                                                |  |    | ix   |

| 1               | Intr  | roduction                                                                                       |                                                   |  |    | 1    |

| <b>2</b>        | Lite  | erature                                                                                         | e Review on Performance Engineering               |  |    | 6    |

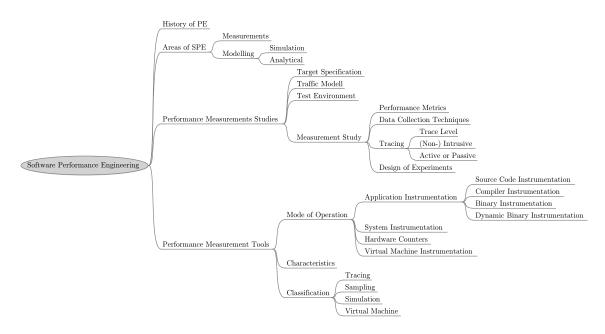

|                 | 2.1   | Introd                                                                                          | luction to Performance Engineering                |  |    | 7    |

|                 | 2.2   | Histor                                                                                          | y of Performance Engineering                      |  |    | 7    |

|                 | 2.3   | Areas                                                                                           | of Software Performance Engineering               |  |    | 8    |

|                 |       | 2.3.1                                                                                           | Performance Measurements                          |  |    | 9    |

|                 |       | 2.3.2                                                                                           | Performance Modeling                              |  |    | 9    |

|                 | 2.4   | Perfor                                                                                          | mance Measurements Studies                        |  |    | 10   |

|                 |       | 2.4.1                                                                                           | Performance Target Specification                  |  |    | 11   |

|                 |       | 2.4.2                                                                                           | Traffic Model                                     |  |    | 11   |

|                 |       | 2.4.3                                                                                           | Performance Test Environment                      |  |    | 12   |

|                 |       | 2.4.4                                                                                           | Measurement Study                                 |  |    | 13   |

|                 | 2.5   | Perfor                                                                                          | mance Measurement Tools                           |  |    | 16   |

|                 |       | 2.5.1                                                                                           | Mode of Operation                                 |  |    | 16   |

|                 |       | 2.5.2                                                                                           | Characteristics                                   |  |    | 19   |

|                 |       | 2.5.3                                                                                           | Classification                                    |  |    | 19   |

| 3               | Lite  | erature                                                                                         | e Review in the Area of Dynamic Performance Stubs |  |    | 22   |

|                 | 3.1   | Dynar                                                                                           | nic Performance Stubs                             |  |    | 23   |

| 3.2 CPU Stubs   |       | Stubs $\ldots$ |                                                   |  | 23 |      |

|                 |       | 3.2.1                                                                                           | Related Work                                      |  |    | 23   |

|                 |       | 3.2.2                                                                                           | Basic Literature                                  |  |    | 24   |

|          | 3.3  | Main I  | $Memory Stubs \dots \dots$ |

|----------|------|---------|----------------------------------------------------------------------------------------------------------------------------------|

|          |      | 3.3.1   | Related Work                                                                                                                     |

|          |      | 3.3.2   | Basic Literature                                                                                                                 |

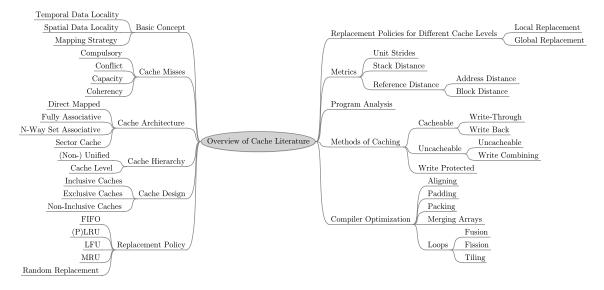

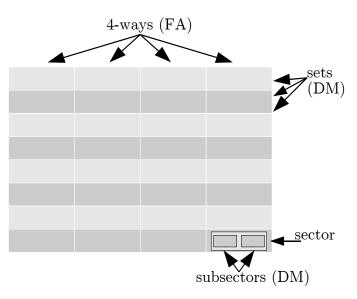

|          | 3.4  | Data (  | Cache Memory Stubs                                                                                                               |

|          |      | 3.4.1   | Related Work                                                                                                                     |

|          |      | 3.4.2   | Basic Literature                                                                                                                 |

|          | 3.5  | Simula  | tted Software Functionality $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 42$                                         |

|          |      | 3.5.1   | Related Work                                                                                                                     |

|          |      | 3.5.2   | Basic Literature                                                                                                                 |

| 4        | Dyr  | namic 1 | Performance Stubs 46                                                                                                             |

|          | 4.1  | Basic   | Design Decisions                                                                                                                 |

|          | 4.2  | Conce   | pt                                                                                                                               |

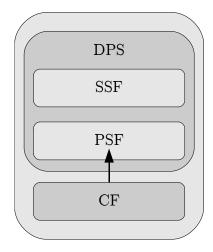

|          | 4.3  | Frame   | work                                                                                                                             |

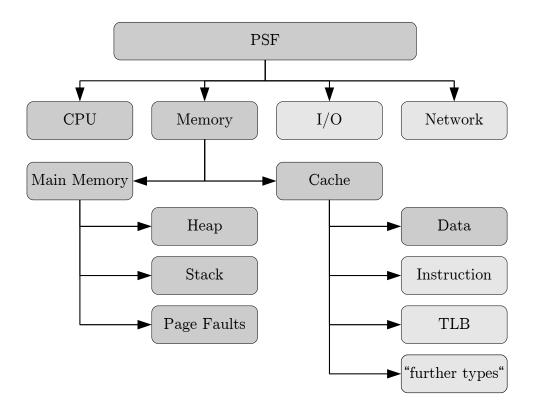

|          | 4.4  | Perfor  | mance Simulation Functions                                                                                                       |

|          |      | 4.4.1   | CPU PSF                                                                                                                          |

|          |      | 4.4.2   | Memory PSF                                                                                                                       |

|          |      | 4.4.3   | I/O PSF                                                                                                                          |

|          |      | 4.4.4   | Network PSF                                                                                                                      |

|          |      | 4.4.5   | Calibration Functions                                                                                                            |

|          | 4.5  | Simula  | ted Software Functionality $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 53$                                   |

|          | 4.6  | Definit | tion of a General Methodology                                                                                                    |

|          | 4.7  | Extens  | sions to the Methodology $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 56$                              |

|          |      | 4.7.1   | Mixture of PSF                                                                                                                   |

|          |      | 4.7.2   | Full and Partial Stubs                                                                                                           |

|          |      | 4.7.3   | Idealized Measurements                                                                                                           |

|          |      | 4.7.4   | Load and Stress Tests                                                                                                            |

|          |      | 4.7.5   | Hidden Bottlenecks Detection by Zero Bound CUS 57                                                                                |

|          |      | 4.7.6   | System Bounds                                                                                                                    |

|          |      | 4.7.7   | Global vs. Local Stubs                                                                                                           |

|          | 4.8  | Advan   | tages $\ldots \ldots 59$              |

|          | 4.9  | Restrie | $etions \dots \dots$       |

|          | 4.10 | Summ    | ary                                                                                                                              |

| <b>5</b> | CP   | U Stub  | 62 62                                                                                                                            |

|          | 5.1  | Requir  | $ements \dots \dots$       |

|          |      |         |                                                                                                                                  |

Peter Trapp

|   | 5.2 | Realization of the CPU Performance Simulation Functions                                 | 63  |

|---|-----|-----------------------------------------------------------------------------------------|-----|

|   | 5.3 | Calibration Functions                                                                   | 65  |

|   | 5.4 | Methodology                                                                             | 67  |

|   | 5.5 | Case Study                                                                              | 73  |

|   |     | 5.5.1 Evaluation Environment                                                            | 73  |

|   |     | 5.5.2 Original Function                                                                 | 74  |

|   |     | 5.5.3 CPU Stubs                                                                         | 74  |

|   | 5.6 | Summary                                                                                 | 76  |

| 6 | Mai | in Memory Stubs                                                                         | 78  |

|   | 6.1 | Requirements                                                                            | 79  |

|   | 6.2 | Realization of the Main Memory Performance Simulation Functions $% \mathcal{A}^{(n)}$ . | 80  |

|   |     | 6.2.1 Simulation Data File                                                              | 82  |

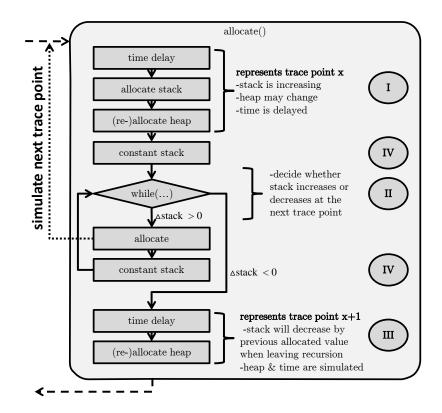

|   |     | 6.2.2 Algorithm                                                                         | 83  |

|   | 6.3 | Calibration Functions                                                                   | 85  |

|   |     | 6.3.1 Measurement Tools                                                                 | 85  |

|   |     | 6.3.2 Overhead Determination                                                            | 85  |

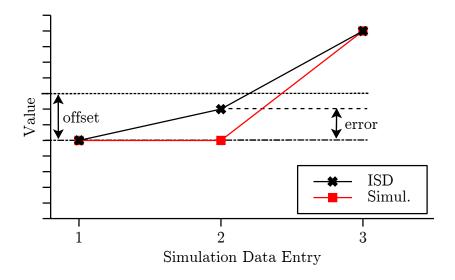

|   | 6.4 | Simulation Data File Generation                                                         | 90  |

|   |     | 6.4.1 Requirements                                                                      | 90  |

|   |     | 6.4.2 Algorithm                                                                         | 91  |

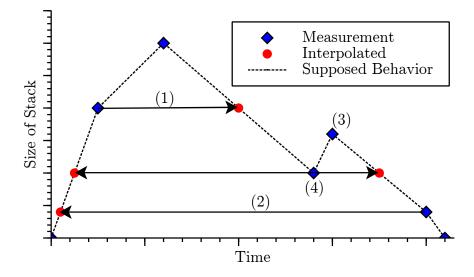

|   |     | 6.4.3 Simulation Data Point Calculation                                                 | 93  |

|   | 6.5 | Methodology                                                                             | 99  |

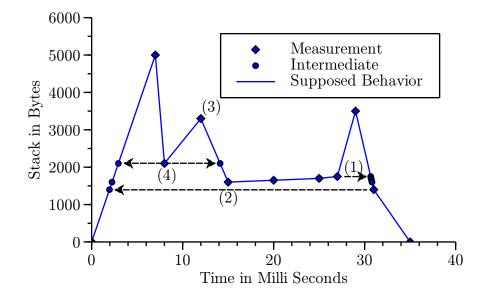

|   | 6.6 | Case Study                                                                              | .01 |

|   |     | 6.6.1 Evaluation Environment                                                            | 01  |

|   |     | 6.6.2 Original Function                                                                 | 02  |

|   |     | 6.6.3 Main Memory Stubs                                                                 | 02  |

|   | 6.7 | Summary                                                                                 | .09 |

| 7 | Dat | a Cache Memory Stubs 1                                                                  | 11  |

|   | 7.1 | Requirements                                                                            | 12  |

|   | 7.2 | Realization of the Data Cache Memory Performance Simulation Func-                       |     |

|   |     | tions                                                                                   | 13  |

|   |     | 7.2.1 Architecture Description File                                                     | 14  |

|   |     | 7.2.2 Simulation Data File                                                              | 15  |

|   |     | 7.2.3 Algorithm                                                                         | 16  |

|   |     | 7.2.4 Discussion                                                                        | .22 |

|   |     |                                                                                         |     |

Peter Trapp

|   |                | 7.2.5                                                                          | Replacement Policies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 124 |

|---|----------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|

|   | 7.3            | Calibra                                                                        | tion Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 128 |

|   | 7.4            | $Methodology  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 130 |

|   | 7.5            | Case Study                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 133 |

|   |                | 7.5.1                                                                          | Evaluation Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 133 |

|   |                | 7.5.2                                                                          | Original Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 134 |

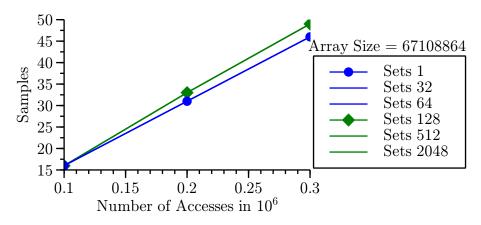

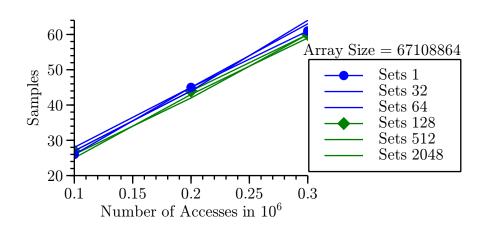

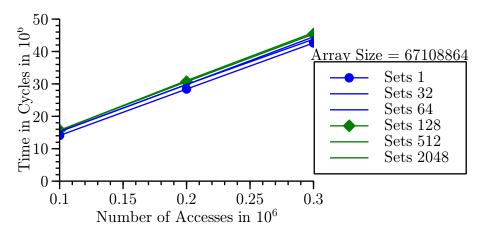

|   |                | 7.5.3                                                                          | Data Cache Memory Stubs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 135 |

|   | 7.6            | Summa                                                                          | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 138 |

| 8 | $\mathbf{Sim}$ | ulated                                                                         | Software Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 139 |

|   | 8.1            | Require                                                                        | ements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 140 |

|   | 8.2            | Method                                                                         | dology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • | 142 |

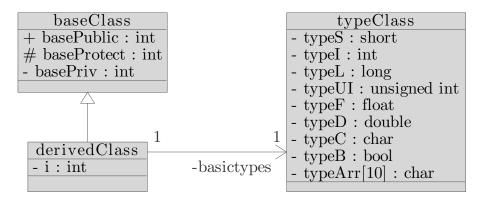

|   | 8.3            | Realiza                                                                        | tion $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • | 143 |

|   |                | 8.3.1                                                                          | Generate Header File (Serialization Specification) $\ . \ . \ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | 144 |

|   |                | 8.3.2                                                                          | Record Functional Behavior (Binary Format) $\hfill \hfill \hfill$ | • | 145 |

|   |                | 8.3.3                                                                          | Restore Functional Behavior (Deserialization) $\ \ . \ . \ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • | 147 |

|   | 8.4            | Case St                                                                        | $\operatorname{tudy}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • | 148 |

|   |                | 8.4.1                                                                          | Evaluation Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • | 149 |

|   |                | 8.4.2                                                                          | Application of the Methodology $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • | 149 |

|   |                | 8.4.3                                                                          | Performance Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 152 |

|   | 8.5            | Discuss                                                                        | sion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | 153 |

| 9 | Vali           | idation                                                                        | of the Performance Simulation Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 157 |

|   | 9.1            | Test Er                                                                        | $nvironment \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • | 158 |

|   | 9.2            | CPU P                                                                          | Performance Simulation Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | • | 158 |

|   |                | 9.2.1                                                                          | Simulation of the Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 158 |

|   |                | 9.2.2                                                                          | Open Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 161 |

|   |                | 9.2.3                                                                          | Closed Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 163 |