# A Novel Low-Temperature Growth Method of Silicon Structures and Application in Flash Memory

# Thomas Attia Mih

B.Sc., M.Sc. (Physics)

A Thesis Submitted to De Montfort University, Leicester for the Degree of

# Doctor of Philosophy (PhD)

Emerging Technologies Research Centre, De Montfort University, Leicester, UK

August 2011

To My Beloved Mother (Ze-Attia)

Francisca Mbong

# And

My Eternally Resting Father

Simon Mih

After climbing a great hill, one only finds that there are many more hills to climb (Nelson Mandela)

## Declaration

This thesis contains results of research undertaken solely by the author between October 2007 and March 2011 in the Emerging Technologies Research Centre of the Faculty of Technology, De Montfort University, Leicester, under the supervision of Drs. Shashi Paul and Richard Barrie Michael Cross. The research is entirely the original work of the author and contains nothing done in collaboration with another person or institution except where explicit acknowledgement is given.

The work has not been submitted in whole or in part for any other University degree or diploma.

Permission to copy or use whole or part of the work contained herein must be solicited except for the purpose of private study or academic purposes in which case the author must be explicitly acknowledged.

Signature of Author:\_\_\_\_\_

Thomas Attia Mih Leicester, August 2011

## Abstract

Flash memories are solid-state non-volatile memories. They play a vital role especially in information storage in a wide range of consumer electronic devices and applications including smart phones, digital cameras, laptop computers, and satellite navigators. The demand for high density flash has surged as a result of the proliferation of these consumer electronic portable gadgets and the more features they offer – wireless internet, touch screen, video capabilities.

The increase in the density of flash memory devices over the years has come as a result of continuous memory cell-size reduction. This size scaling is however approaching a dead end and it is widely agreed that further reduction beyond the 20 nm technological node is going to be very difficult, as it would result to challenges such as cross-talk or cell-to-cell interference, a high statistical variation in the number of stored electrons in the floating gate and high leakage currents due to thinner tunnel oxides.

Because of these challenges a wide range of solutions in form of materials and device architectures are being investigated. Among them is three-dimensional (3-D) flash, which is widely acclaimed as the ideal solution, as they promise the integration of long-time retention and ultra-high density cells without compromising device reliability. However, current high-temperature (>600 °C) growth techniques of the Polycrystalline silicon floating gate material are incompatible with 3-D flash memory; with vertically stacked memory layers, which require process temperatures to be  $\leq 400$  °C. There already exist some low-temperature techniques for producing polycrystalline silicon such as laser annealing, solid-phase crystallization of amorphous silicon and metal-induced crystallization. However, these have some short-comings which make them not suitable for use in 3-D flash memory, e.g. the high furnace annealing temperatures (700 °C) in solid-phase crystallization of amorphous silicon which could potentially damage underlying memory layers in 3-D flash, and the metal contaminants in metal-induced crystallization which is a potential source of high leakage currents. There is therefore a

need for alternative low-temperature techniques that would be most suitable for flash memory purposes.

With reference to the above, the main objective of this research was to develop a novel low temperature method for growing silicon structures at  $\leq 400$  °C. This thesis thus describes the development of a low-temperature method for polycrystalline silicon growth and the application of the technique in a capacitor-like flash memory device.

It has been demonstrated that silicon structures with polycrystalline silicon-like properties can be grown at  $\leq 400$  °C in a 13.56 MHz radio frequency (RF) plasmaenhanced chemical vapour deposition (PECVD) reactor with the aid of Nickel Formate Dihydrate (NFD). It is also shown that the NFD coated on the substrates, thermally decomposes in-situ during the deposition process forming Ni particles that act as nucleation and growth sites of polycrystalline silicon. Silicon films grown by this technique and without annealing, have exhibited optical band gaps of ~ 1.2 eV compared to 1.78 eV for films grown under identical conditions but without the substrate being coated. These values were determined from UV-Vis spectroscopy and Tauc plots. These band gaps correspond to polycrystalline silicon and amorphous silicon respectively, meaning that the films grown on NFD-coated substrates are polycrystalline silicon while those grown on uncoated substrates remain amorphous. Moreover, this novel technique has been used to fabricate a capacitor-like flash memory that has exhibited hysteresis width corresponding to charge storage density in the order of  $10^{12}$  cm<sup>-2</sup> with a retention time well above 20 days for a device with silicon films grown at 300 °C. Films grown on uncoated films have not exhibit any significant hysteresis, and thus no flash memory-like behaviour. Given that all process temperatures throughout the fabrication of the devices are less than 400 °C and that no annealing of any sort was done on the material and devices, this growth method is thermal budget efficient and meets the crucial process temperature requirements of 3-D flash memory. Furthermore, the technique is glass compatible, which could prove a major step towards the acquisition of flash memory-integrated systems on glass, as well as other applications requiring low temperature polycrystalline silicon.

## Acknowledgement

Foremost, I would like to acknowledge with gratitude De Montfort University for financial assistance over 36 months of this research. Besides the University, my utmost thanks go to my Supervisors Drs. Shashi Paul and Richard Barrie Michael Cross for their advice, encouragement and patience throughout my research period and for painstakingly and critically reading over my written works with invaluable suggestions; Dr. Konstantin Vershinin for his support and encouragement and critical examination of my work throughout all stages of my research years, Dr. Iulia Salaoru for her support on polymer dielectrics, Dr. Dominic Charles Prime for his support and advice on AFM, Mr. Paul Taylor, the EMTERC Senior Technician for taking care of malfunctioning equipment in the research centre throughout my research period, Prof. Anjana Devi for organizing the growth of zirconia dielectric films in her laboratory.

My appreciation also goes to Dr. Divine Ngwashi Khan, Dr. David Black and Miss Nare Gabrielyan for the light-hearted moments we shared in the research centre.

It is a great opportunity for me to express my profound gratitude to my entire family, especially to my mother Mama Francisca Mbong for all her love and care; my brother, Prof. Afui Mathias Mih for his continuous encouragement and financial assistance; my sister, Angela Yuoh Mih who accepted God's call to eternity and did not live to see the end of what she had encouraged me to undertake; all my sisters Emilia, Christina, Grace for their love and encouragement; my nephews and nieces and all other family members whose names have not been mentioned for their love.

A special thank you to my wife, Loveline Ekei Mih for her love and support.

I would sincerely like to thank every other person not mentioned who has contributed in any way to the successful realization of this work.

Above all, I thank God Almighty and give Him glory for everything.

## **Table of Contents**

| Declaration       |                                                            | ii          |

|-------------------|------------------------------------------------------------|-------------|

| Abstract          |                                                            | iv          |

| Acknowledgement   |                                                            | vi          |

| Table of Contents |                                                            | vi          |

| Table of Figures  |                                                            | _ <i>xi</i> |

| Chapter 1. An (   | Dverview of Research                                       | 1           |

| 1.1 In            | troduction                                                 | 1           |

| 1.2 Re            | esearch Objectives                                         | 5           |

| 1.3 Th            | nesis structure                                            | (           |

| 1.4 Pu            | blications and Conferences                                 | (           |

| 1.4.1             | Referenced Works                                           | 6           |

| 1.4.2             | Oral and Poster Presentations                              | 7           |

| 1.4.3             | Submitted Journals                                         | 7           |

| Chapter 2. Flas   | h Memory and Related Emerging Storage Devices              | 9           |

| 2.1 In            | troduction                                                 | 9           |

| 2.1.1             | Hard Disc Drive and Solid-State Drive                      | _ 10        |

| 2.1.2             | Random Access Memory (RAM)                                 | 12          |

| 2.1.3             | Read Only Memory (ROM)                                     | 13          |

| 2.1.4             | Non-Volatile RAM                                           | _ 14        |

| 2.2 Br            | ief Historical Evolution of Floating Gate Non-Volatile Mem | ory         |

| 15                |                                                            |             |

| 2.3 Fl            | ash Memory Overview                                        | _ 20        |

| 2.3.1             | Flash Memory Cell Structure                                | _ 21        |

| 2.3.2             | The Capacitor Model and Equations of the FG MOS Device_    | _ 22        |

| 2.3.3             | Working Mechanisms of Flash Memory Cell                    | _ 26        |

| 2.3.              | 3.1 Channel Hot Electron Injection                         | 27          |

| 2.3.3.2 Fowler-Nordheim Tunnelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 2.3.3.3 Reading Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31                                                             |

| 2.3.4 Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 31                                                             |

| 2.3.4.1 Write/Erase Cycle Endurance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32                                                             |

| 2.3.4.2 Retention                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33                                                             |

| 2.3.4.3 Cell Disturb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34                                                             |

| 2.4 Flash Memory Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _ 36                                                           |

| 2.5 Emerging Universal Memory Technologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                                                             |

| 2.5.1 Phase Change Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                             |

| 2.5.2 Magnetoresistive Random Access Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43                                                             |

| 2.5.3 Ferroelectric RAM (FeRAM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45                                                             |

| 2.5.4 Organic Memory Devices (OMD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 48                                                             |

| 2.6 Three-Dimensional Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _ 50                                                           |

| 2.6.1 Different 3-D Memory Cell Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _ 51                                                           |

| 2.7 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 56                                                             |

| <b></b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                |

| Chapter 3. Overview of Low-Temperature Methods of Obtaining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                |

| Chapter 3. Overview of Low-Temperature Methods of Obtaining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57                                                             |

| Chapter 3. Overview of Low-Temperature Methods of Obtaining<br>Polycrystalline Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 57<br>57                                                       |

| Chapter 3. Overview of Low-Temperature Methods of Obtaining Polycrystalline Silicon 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57<br>57<br>57                                                 |

| Chapter 3.       Overview of Low-Temperature Methods of Obtaining         Polycrystalline Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57<br>57<br>57<br>60                                           |

| Chapter 3.       Overview of Low-Temperature Methods of Obtaining         Polycrystalline Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57<br>57<br>57<br>60<br>62                                     |

| Chapter 3.       Overview of Low-Temperature Methods of Obtaining         Polycrystalline Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57<br>57<br>60<br>62<br>63                                     |

| Chapter 3.       Overview of Low-Temperature Methods of Obtaining         Polycrystalline Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57<br>57<br>60<br>62<br>63<br>65                               |

| Chapter 3. Overview of Low-Temperature Methods of Obtaining         Polycrystalline Silicon         3.1 Introduction         3.2 Structure and Electronic Properties of Polycrystalline silicon         3.3 Growth Methods of Polycrystalline silicon         3.4 Plasma-enhanced Chemical Vapour Deposition (PECVD)         3.4.1 The Capacitively Coupled RF PECVD Reactor Design         3.5 Deposition of a-Si or a-Si:H                                                                                                                                              | 57<br>57<br>60<br>62<br>63<br>65<br>66                         |

| Chapter 3.       Overview of Low-Temperature Methods of Obtaining         Polycrystalline Silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57<br>57<br>60<br>62<br>63<br>65<br>66<br>67                   |

| Chapter 3. Overview of Low-Temperature Methods of Obtaining         Polycrystalline Silicon         3.1 Introduction         3.2 Structure and Electronic Properties of Polycrystalline silicon         3.3 Growth Methods of Polycrystalline silicon         3.4 Plasma-enhanced Chemical Vapour Deposition (PECVD)         3.4.1 The Capacitively Coupled RF PECVD Reactor Design         3.5 Deposition of a-Si or a-Si:H         3.6 Conversion of a-Si and a-Si:H to Polycrystalline silicon         3.6.1 Solid-Phase Crystallization                               | 57<br>57<br>60<br>62<br>63<br>65<br>66<br>67<br>68             |

| Chapter 3. Overview of Low-Temperature Methods of Obtaining         Polycrystalline Silicon         3.1 Introduction         3.2 Structure and Electronic Properties of Polycrystalline silicon         3.3 Growth Methods of Polycrystalline silicon         3.4 Plasma-enhanced Chemical Vapour Deposition (PECVD)         3.4.1 The Capacitively Coupled RF PECVD Reactor Design         3.5 Deposition of a-Si or a-Si:H         3.6 Conversion of a-Si and a-Si:H to Polycrystalline silicon         3.6.1 Solid-Phase Crystallization         3.6.2 Laser Annealing | 57<br>57<br>60<br>62<br>63<br>65<br>65<br>66<br>67<br>68<br>71 |

viii

| 3.7 Summary                                                         | 74      |

|---------------------------------------------------------------------|---------|

| Chapter 4. Characterization Methods of Silicon Films and Memory De  | evices  |

| 75                                                                  |         |

| 4.1 Introduction                                                    | 75      |

| 4.2 Physical Characterization                                       | 75      |

| 4.2.1 Film Thickness Measurement                                    |         |

| 4.2.1.1 Ellipsometry                                                |         |

| 4.2.1.2 Step Profilometry                                           |         |

| 4.2.2 Fourier Transform Infrared Spectroscopy (FTIR)                | 81      |

| 4.2.3 Ultra-Violet Visible (UV-Vis) Spectroscopy                    | 84      |

| 4.2.4 Atomic Force Microscopy (AFM)                                 | 87      |

| 4.3 Electrical Characterisation                                     | 90      |

| 4.3.1 Dark- and Photoconductivity                                   |         |

| 4.3.2 Electrical Characterization of MIS and MIM Devices            | 92      |

| 4.4 Summary                                                         | 93      |

| Chapter 5. Dip-Coating and FTIR Investigation of Nickel Formate dil | hvdrate |

| 95                                                                  | iyu.uc  |

| 5.1 Introduction                                                    | 95      |

|                                                                     |         |

| 5.2 Basic Properties of Nickel Formate Dihydrate                    | 96      |

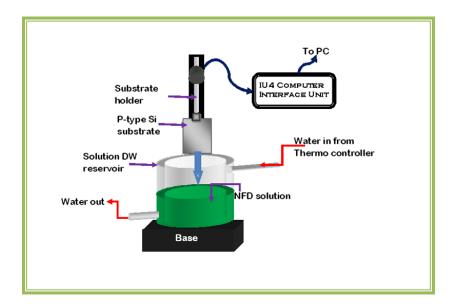

| 5.3 Dip-Coating of NFD                                              | 97      |

| 5.3.1 The Nima Dip-Coater System                                    | 98      |

| 5.3.2 Preparation of Precursor Solution                             | 99      |

| 5.3.3 Choosing the Better Solvent                                   | 100     |

| 5.3.3.1 Spin coating                                                | 100     |

| 5.3.3.2 Squirting                                                   | 101     |

| 5.3.3.3 Complete Submersion Coating                                 | 101     |

| 5.3.3.4 Results                                                     | 102     |

| 5.4 The Dip Coating Process                                         | 104     |

ix

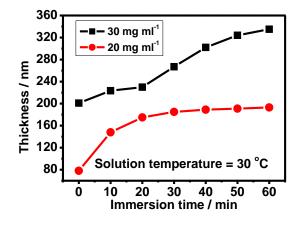

|            | 5.4.1   | Effect of Immersion Time on the Thickness of NFD Coating of | on    |

|------------|---------|-------------------------------------------------------------|-------|

| Substrat   | e       | 106                                                         |       |

|            | 5.4.2   | Variation of Thickness with Withdrawal Speed                | _ 107 |

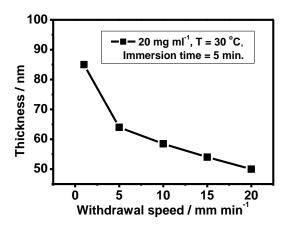

|            | 5.4.3   | Variation of Thickness with NFD Solution Temperature        | _ 108 |

|            | 5.4.4   | Discussion on Observed Effects of Coating Parameters on     |       |

| Thickne    | ss of C | oating                                                      | _ 108 |

| 5.         | 5 F1    | FIR of Nickel Formate Dihydrate                             | _ 111 |

| 5.         | 6 Su    | ımmary                                                      | 113   |

|            |         | on Structures: PECVD Growth and Optimization                |       |

| -          |         |                                                             |       |

| 6.         | 1 In    | troduction                                                  | _ 115 |

| 6.         | 2 Si    | licon Films Growth Procedure                                | _ 116 |

| 6.         | 3 Ef    | fects of Deposition Parameters on Silicon Films Properties  | _ 118 |

|            | 6.3.1   | Temperature Effects                                         | _ 118 |

|            | 6.3.    | 1.1 Band Gap                                                | 119   |

|            | 6.3.    | 1.2 Hydrogen Content                                        | 120   |

|            | 6.3.    | 1.3 Photo- and Dark Conductivity                            | 121   |

|            | 6.3.    | 1.4 Film Surface Roughness and surface grain size           | 122   |

|            | 6.3.2   | Effect of RF Power Variation                                | _ 124 |

|            | 6.3.3   | Effects of Changes in Silane Flow Rate                      | _ 126 |

| 6.         | 4 Co    | ontamination                                                | _ 127 |

| 6.         | 5 De    | eposition of Silicon Nitride Dielectric                     | _ 130 |

| 6.         | 6 Su    | mmary of Chapter 6                                          | _ 134 |

| Chapter 7. | Men     | nory Behaviour of NFD-assisted Grown Silicon Structure      | 25    |

| enapter /  | 135     | iony Denariour of 111 D assisted Grown Stateon Structure    | 20    |

|            |         |                                                             |       |

| 7.         | 1 In    | troduction                                                  | _ 135 |

| 7.         | 2 Fa    | brication of MIS Devices                                    | _ 135 |

|            | 7.2.1   | Deposition of Gate Insulator                                | _ 136 |

|            | 7.2.    | 1.1 Polystyrene and Polyvinyl Acetate                       | 137   |

|            | 7.2.    | 1.2 Silicon Nitride                                         | 137   |

| 7.2.2 Evaporation of Gate Electrodes                           | 137 |

|----------------------------------------------------------------|-----|

| 7.3 Charge storage in MIS Devices                              | 139 |

| 7.4 Memory Characteristics                                     | 145 |

| 7.4.1 Leakage Current                                          | 145 |

| 7.4.2 Memory Window                                            | 146 |

| 7.4.3 Programme/Erase, Retention and Endurance                 | 147 |

| 7.5 Summary                                                    | 150 |

| Chapter 8. Conclusion and Recommendations for Further Research | 151 |

| 8.1 Introduction                                               | 151 |

| 8.2 Major Results                                              | 151 |

| 8.3 Recommendation for Further Studies                         | 153 |

| 8.3.1 Dip-coating of NFD                                       | 153 |

| 8.3.2 Contamination of Si Films                                | 153 |

| 8.3.3 Memory                                                   | 154 |

| References                                                     | 155 |

| Appendices                                                     | 181 |

| Appendix 1: Substrate Cleaning                                 | 181 |

| 8.3.4 Corning Glass Substrates                                 | 181 |

| 8.3.5 Crystalline Silicon                                      | 181 |

| 8.3.6 Plasma Cleaning of Substrates                            | 181 |

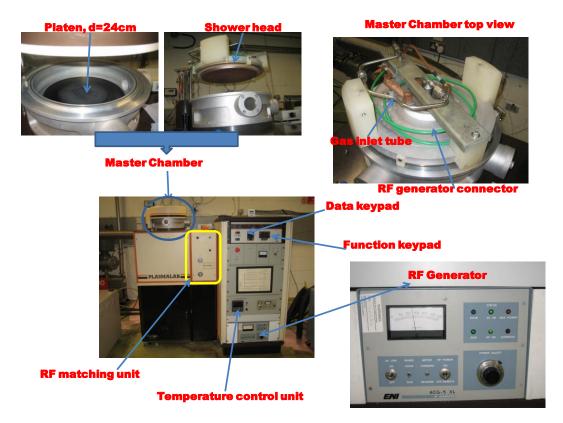

| Appendix 2: The PECVD System                                   | 183 |

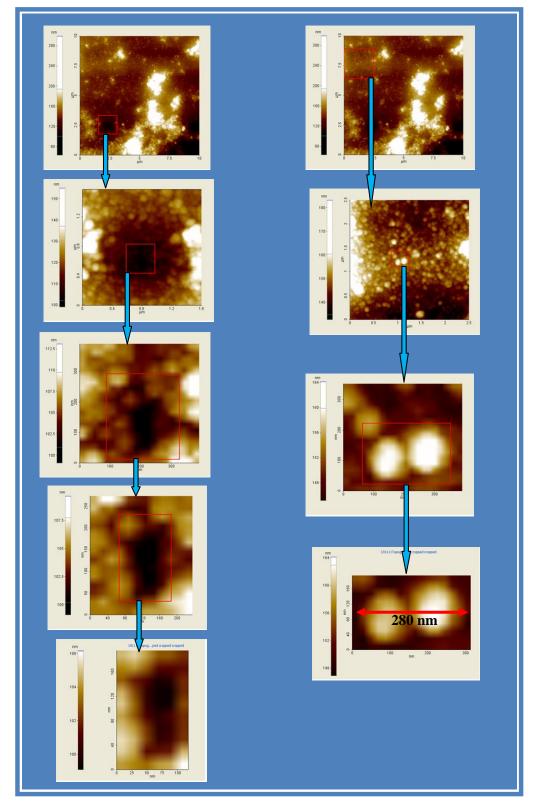

| Appendix 3: Supplementary AFM DATA                             | 184 |

## **Table of Figures**

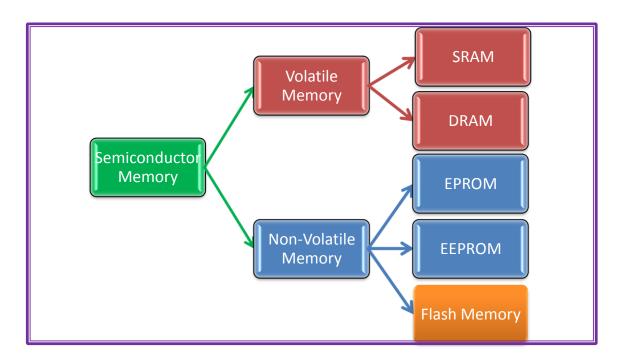

| Figure 2-1: Semiconductor memory tree9                                               |

|--------------------------------------------------------------------------------------|

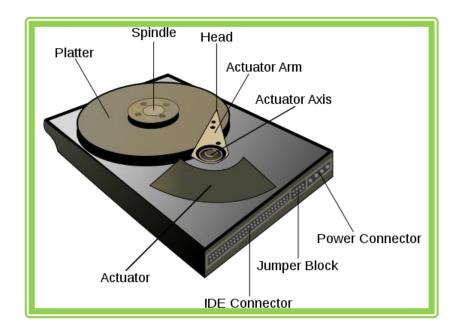

| Figure 2-2: The hard disc drive (HDD)[62]10                                          |

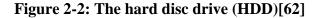

| Figure 2-3: Illustration of (a) DRAM and (b) SRAM[66]13                              |

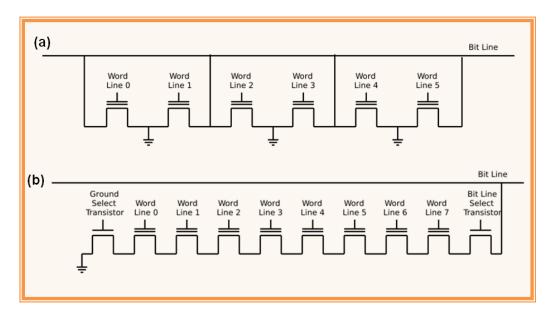

| Figure 2-4: Cell connections in (a) NOR flash and (b) NAND flash memory devices      |

|                                                                                      |

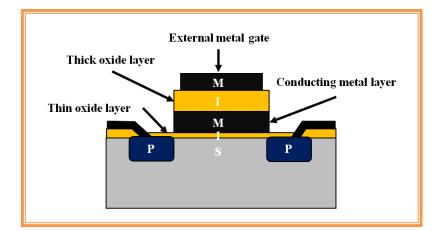

| Figure 2-5: metal-insulator-metal-insulator-semiconductor (MIMIS) FG device16        |

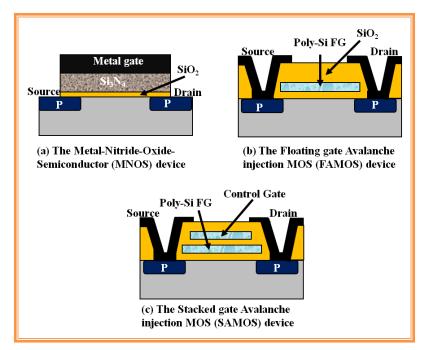

| Figure 2-6: Diagrammatic representation of (a) The MNOS cell, (b) the FAMOS          |

| cell and (c) the SAMOS cell17                                                        |

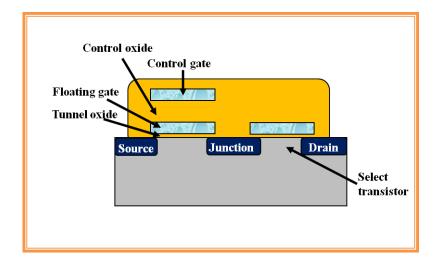

| Figure 2-7: The Electrically Erasable programmable ROM (EEPROM) with a               |

| select transistor18                                                                  |

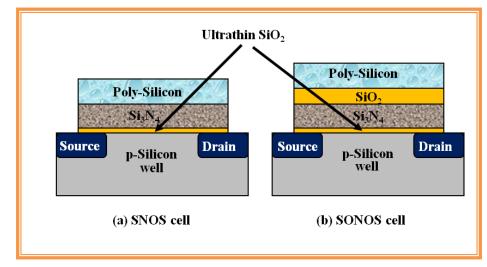

| Figure 2-8: Cell structure of the (a) Silicon-Nitride-Oxide-Semiconductor (SNOS)     |

| and (b) Silicon-Oxide-Nitride-Oxide-Semiconductor (SONOS) devices. The               |

| MOS select transistor is not shown20                                                 |

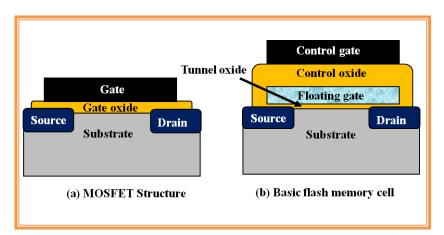

| Figure 2-9: The basic cell structure of (a) the MOSFET and (b) the FG flash          |

| memory cell22                                                                        |

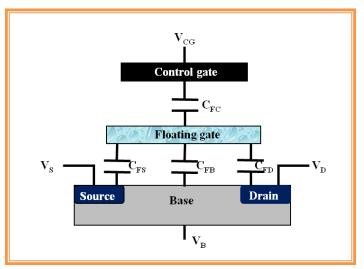

| Figure 2-10: Illustration of the capacitance model of the FG memory cell22           |

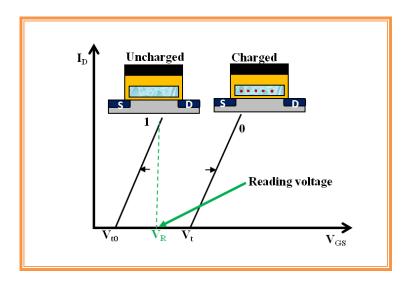

| Figure 2-11: I-V characteristics of the FG MOS device at the neutral "1" and         |

| charged "0" states. The threshold voltage shift $\Delta V_t$ is proportional to the  |

| charge stored in the FG. $\Delta V_t$ is also known as the memory window25           |

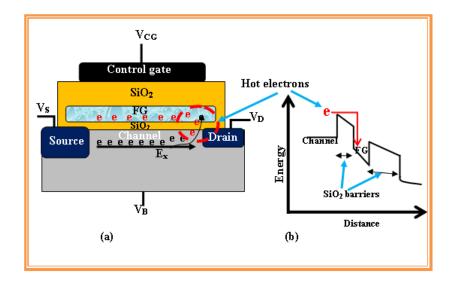

| Figure 2-12: (a) Schematic illustration of channel hot electron (CHE) injection      |

| programming and (b) the potential energy diagram of CHE versus vertical              |

| distance from control gate27                                                         |

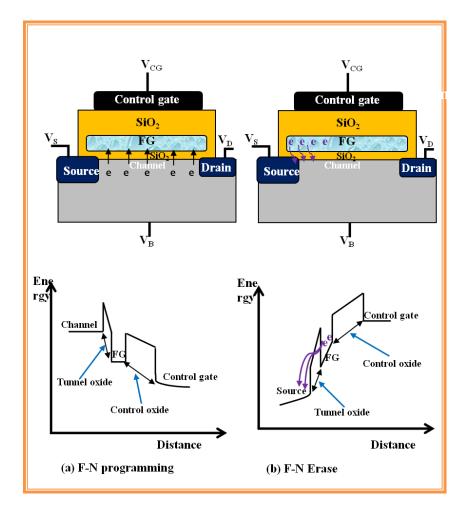

| Figure 2-13: Schematic illustration of Fowler-Nordheim (F-N) tunnelling (a)          |

| Programming and (b) Erase with corresponding electron energy diagrams                |

| against vertical distance from control gate30                                        |

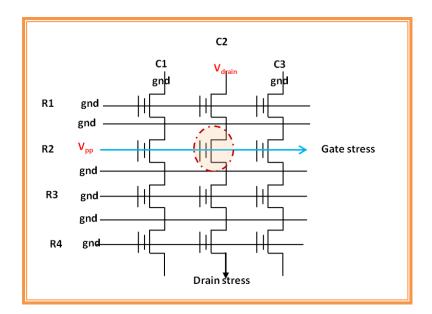

| Figure 2-14: An illustration of cell disturbs in an array of flash memory cells. The |

| shaded cell is being programmed while cell disturb occurs in the other cells in      |

| the same wordline (row) and bitline (column)35                                       |

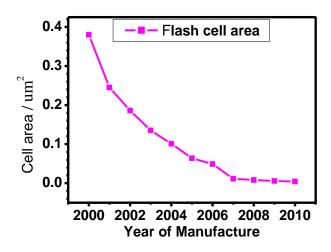

| Figure 2-15: Graph of flash memory cell area achieved within the decade 2000-        |

| 2010, illustrating flash memory scaling                                              |

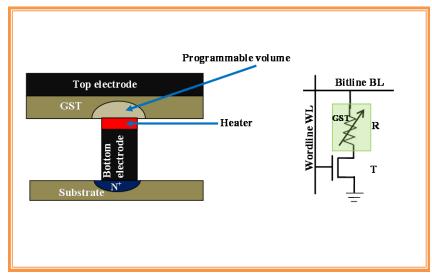

| Figure 2-16: An illustration of the phase change random access memory with the                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| coresponding schematic 1T1R circuit representation42                                                                                                                                                                                                                                                          |

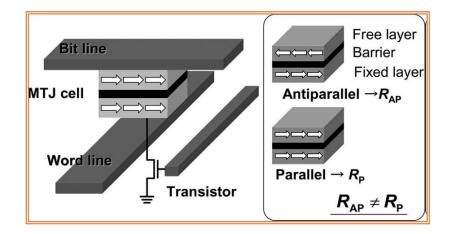

| Figure 2-17: Illustrations of the 1T1R Magnetoresistive RAM showing the                                                                                                                                                                                                                                       |

| magnetic tunnel junction MTJ in the antiparallel (high resistance "1" state)                                                                                                                                                                                                                                  |

| and parallel states (low resistance "0" state)[141]44                                                                                                                                                                                                                                                         |

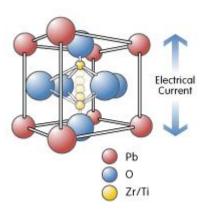

| Figure 2-18: Illustration of the lead zirconate titanate (PZT) structure[150]46                                                                                                                                                                                                                               |

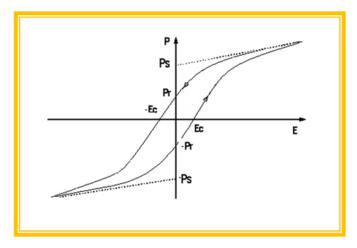

| Figure 2-19: Illustration of the polarization behaviour of the ferroelectric PZT                                                                                                                                                                                                                              |

| with applied electric field47                                                                                                                                                                                                                                                                                 |

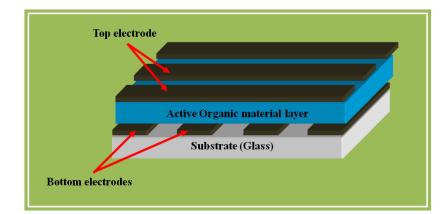

| Figure 2-20. Schematic diagram of organic memory devices                                                                                                                                                                                                                                                      |

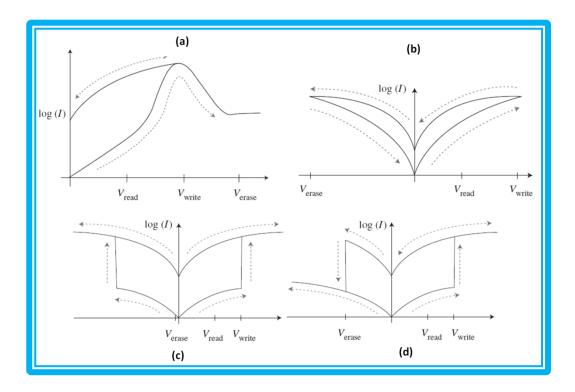

| Figure 2-21: Illustration of different shapes of I-V characteristics of polymer                                                                                                                                                                                                                               |

| memory devices: (a) N-Shaped, (b) O-shaped, (c) Symmetric S-Shaped and (d)                                                                                                                                                                                                                                    |

| asymmetric S-Shaped [29]50                                                                                                                                                                                                                                                                                    |

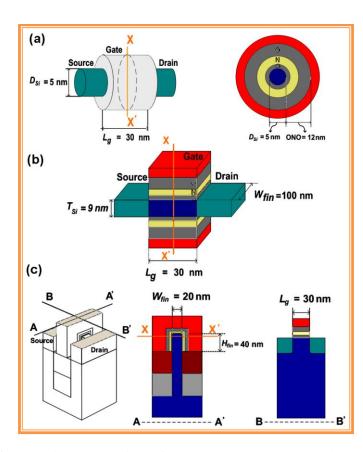

| Figure 2-22. Illustrations of the TCAT, P-BICS, VSAT and VG 3-D-type flash                                                                                                                                                                                                                                    |

| memories[178]52                                                                                                                                                                                                                                                                                               |

| Figure 2-23 : Schematic Illustration of the 3-D cell array transistors (3-D CAT) (a)                                                                                                                                                                                                                          |

| Gate all around (GAA-CAT), (b) Double Gate (DG-CAT) (c) FinFET (Fin-                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                               |

| CAT)[179]                                                                                                                                                                                                                                                                                                     |

| CAT)[179]                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                               |

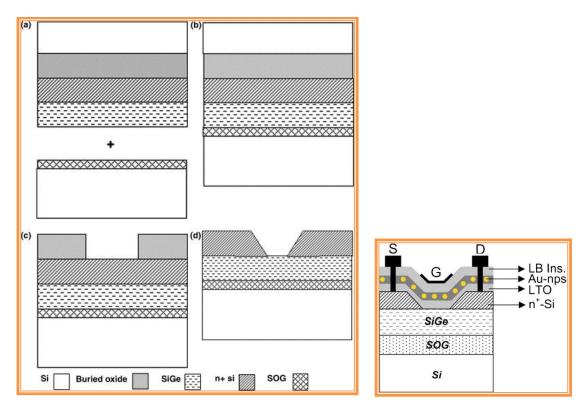

| Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process                                                                                                                                                                                                                             |

| Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si                                                                                                                                                   |

| Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process<br>flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si<br>removal and texturing of buried oxide; (d) Si anisotropic etching and buried                                                                |

| Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process<br>flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si<br>removal and texturing of buried oxide; (d) Si anisotropic etching and buried<br>oxide stripping. (II) V-groove 3-D NVM transistor           |

| <ul> <li>Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si removal and texturing of buried oxide; (d) Si anisotropic etching and buried oxide stripping. (II) V-groove 3-D NVM transistor</li></ul> |

| <ul> <li>Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si removal and texturing of buried oxide; (d) Si anisotropic etching and buried oxide stripping. (II) V-groove 3-D NVM transistor</li></ul> |

| <ul> <li>Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si removal and texturing of buried oxide; (d) Si anisotropic etching and buried oxide stripping. (II) V-groove 3-D NVM transistor</li></ul> |

| <ul> <li>Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si removal and texturing of buried oxide; (d) Si anisotropic etching and buried oxide stripping. (II) V-groove 3-D NVM transistor</li></ul> |

| <ul> <li>Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si removal and texturing of buried oxide; (d) Si anisotropic etching and buried oxide stripping. (II) V-groove 3-D NVM transistor</li></ul> |

| <ul> <li>Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si removal and texturing of buried oxide; (d) Si anisotropic etching and buried oxide stripping. (II) V-groove 3-D NVM transistor</li></ul> |

| <ul> <li>Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si removal and texturing of buried oxide; (d) Si anisotropic etching and buried oxide stripping. (II) V-groove 3-D NVM transistor</li></ul> |

| <ul> <li>Figure 2-24: (I) An illustration of the V-groove MOSFET transistor device process flow: (a) handling and device wafers; (b) low temperature bonding; (c) Si removal and texturing of buried oxide; (d) Si anisotropic etching and buried oxide stripping. (II) V-groove 3-D NVM transistor</li></ul> |

| Figure 4-3: Schematic illustration of the step profilometry showing the direction in |

|--------------------------------------------------------------------------------------|

| which measurements were performed and the expected step profile81                    |

| Figure 4-4: Illustration of the Michelson Interferometer, an important component     |

| in FTIR                                                                              |

| Figure 4-5: Inner view of the UV-Vis spectrophotometer (model: Evolution 300).       |

| The red lines are the beam of light[297]86                                           |

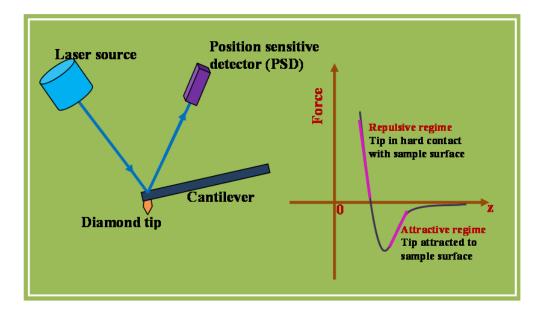

| Figure 4-6: Illustration of the beam deflection system of the AFM. A position        |

| sensitive photodiode is used to measure the position of the beam. On the right       |

| is the Force against distance z of probe from the sample surface                     |

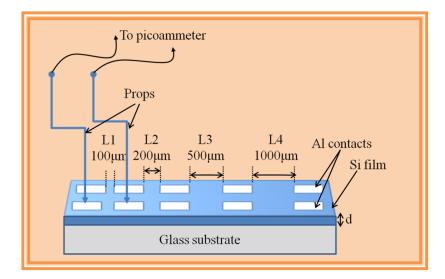

| Figure 4-7: Schematic diagram of gap-cell device for measuring photo- and dark       |

| conductivity. The Al electrodes were evaporated onto the silicon films grown         |

| on glass substrates using gap-cell shadow masks with gap lengths shown on            |

| diagram                                                                              |

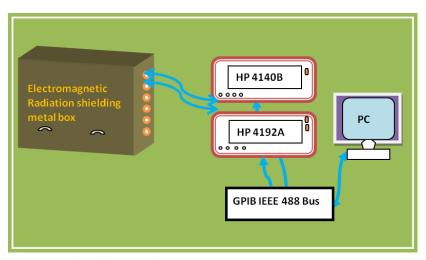

| Figure 4-8: Set up of the electrical measurement system                              |

| Figure 5-1: An illustration of the Nima precision dip-coater system                  |

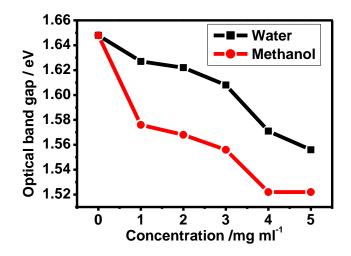

| Figure 5-2: Optical band gap variation with concentration of NFD in methanol and     |

|                                                                                      |

| in water                                                                             |

|                                                                                      |

| in water103                                                                          |

| in water                                                                             |

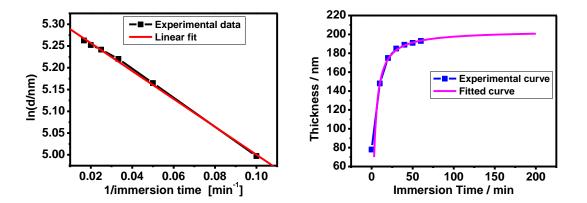

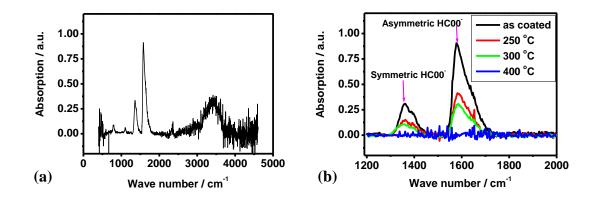

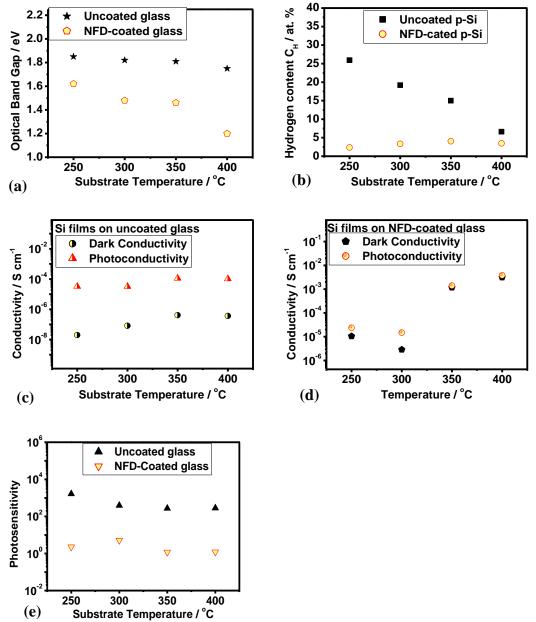

| <ul> <li>in water</li></ul>                                                          |

| <ul> <li>in water</li></ul>                                                          |

| in water                                                                             |

| <ul> <li>in water</li></ul>                                                          |

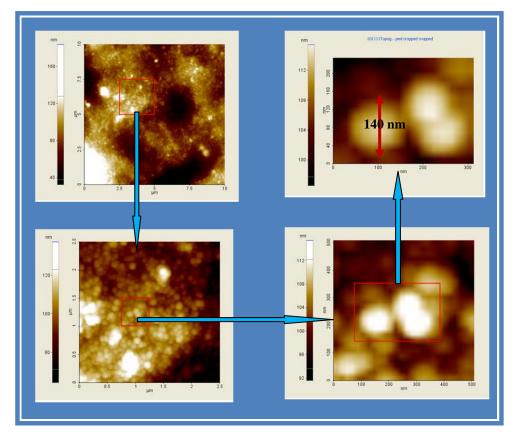

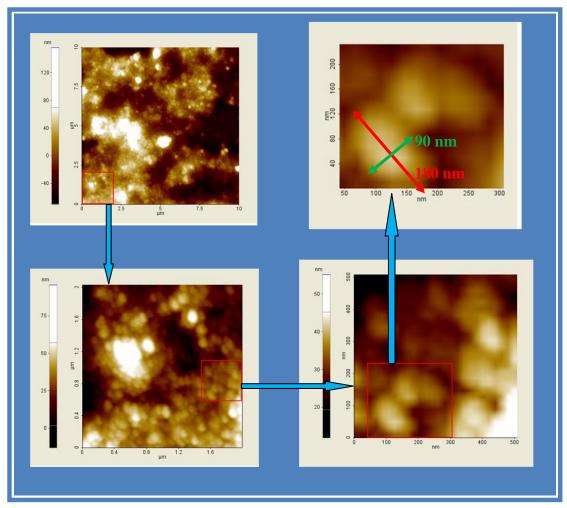

| Figure 6-2: AFM micrographs of Silicon structures showing surface grains grown                             |

|------------------------------------------------------------------------------------------------------------|

| at 400 $^{\circ}\text{C}$ on NFD-coated substrates123                                                      |

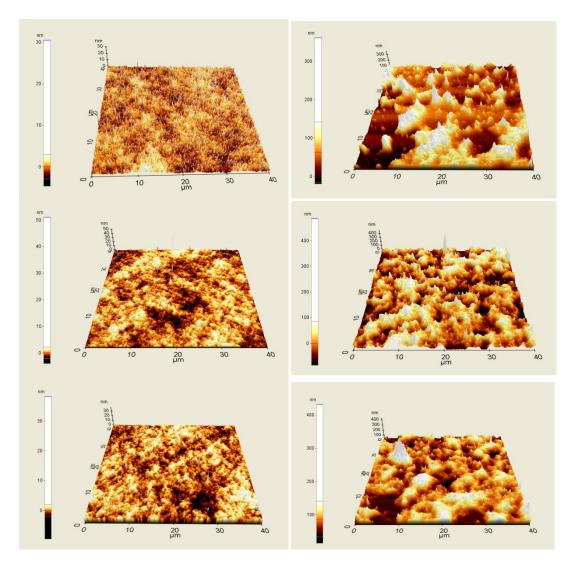

| Figure 6-3: AFM 3-D topography micrographs showing films grown at different                                |

| temperatures. The left column is for micrographs of films on uncoated p-Si                                 |

| substrates while the right column is for NFD-coated substrates. Rows 1-3                                   |

| running from top to bottom are for films grown at 250, 300 and 400 $^\circ \mathrm{C}$                     |

| respectively124                                                                                            |

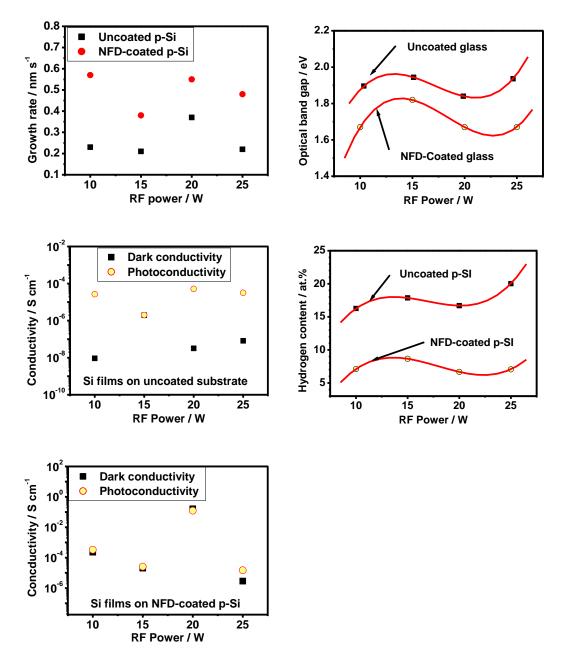

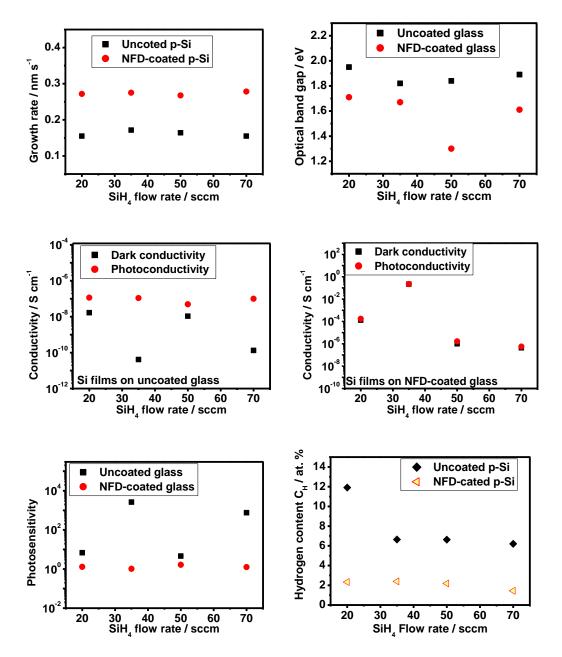

| Figure 6-4: Graphs showing variation of film properties with RF power125                                   |

| Figure 6-5: Variation of film properties with changes in silane flow rate127                               |

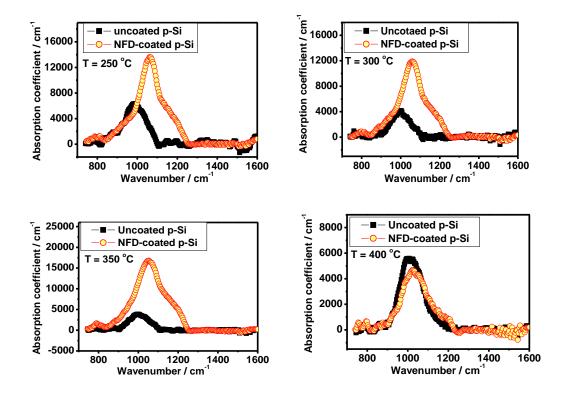

| Figure 6-6: FTIR spectra illustrating the effect of film deposition temperature on                         |

| the oxygen content of the film. Films were grown at a pressure of 200 mtorr,                               |

| RF power of 5W and silane flow rate of 50 sccm                                                             |

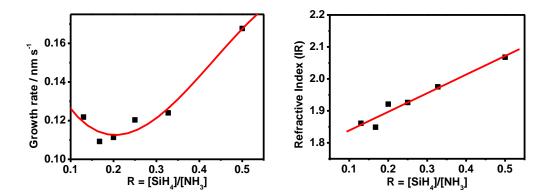

| Figure 6-7: Variation in growth rate and index of refraction for silicon nitride                           |

| films with changes in the ratio R of silane flow rate to ammonia flow rate.                                |

| Films were grown at a temperature of 300 $^\circ C$ , RF power of 50W, nitrogen                            |

| flow of 100 sccm and ammonia flow of 40 sccm while silane flow was changed                                 |

| to change R                                                                                                |

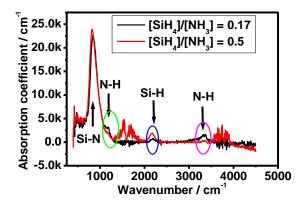

| Figure 6-8: FTIR spectra to show the effects on absorption peak heights of the N-H                         |

| and Si-H vibration modes for different R values                                                            |

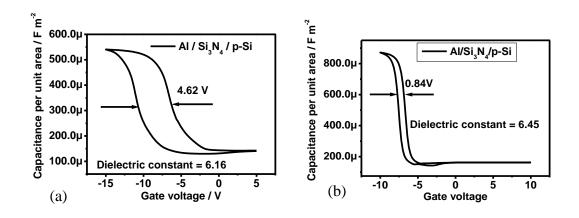

| Figure 6-9: C-V curves of Si <sub>3</sub> N <sub>4</sub> MIS for films grown at (a) high silane to ammonia |

| flow ratio of 0.275 and (b)low silane to ammonia flow ratio of 0.165133                                    |

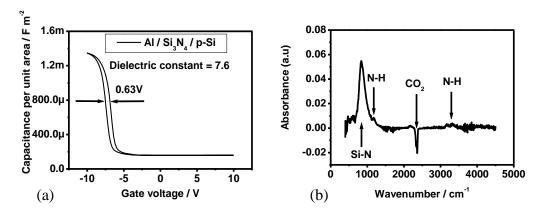

| Figure 6-10: Graphs showing (a) C-V characteristics and (b) FTIR spectra of                                |

| silicon nitride films deposited at T = 300 °C, RF power = 20W, SiH <sub>4</sub> flow = 6.6                 |

| sccm, $NH_3$ flow = 40 sccm, $N_2$ flow = 100 sccm and pressure of 350 mtorr133                            |

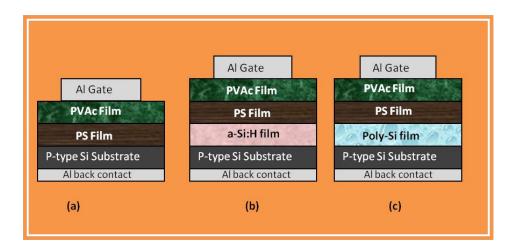

| Figure 7-1: MIS devices (a) containing only PS + PVAc, (b) incorporating a-Si:H                            |

| and (c) incorporating Polycrystalline silicon films grown on NFD-coated                                    |

| substrate138                                                                                               |

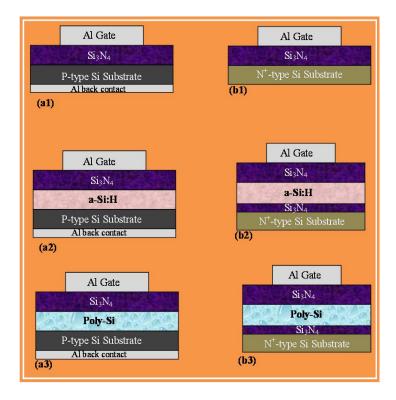

| Figure 7-2: Schematic diagrams of (a1-a3) MIS and (b1-b3) MIM devices139                                   |

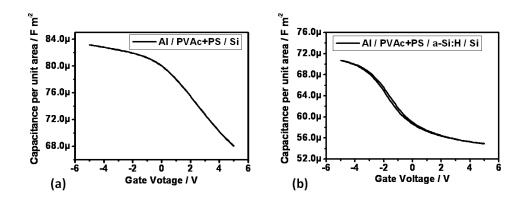

| Figure 7-3: C-V characteristics of metal-insulator-semiconductor reference devices                         |

| (a) containing only the insulator PVAc+PS and (b) containing a-Si. No                                      |

| hysteresis is observed in both140                                                                          |

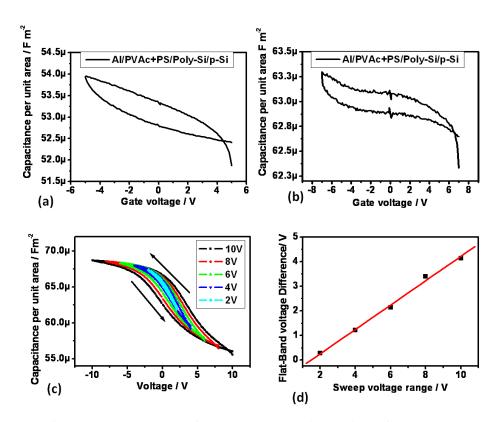

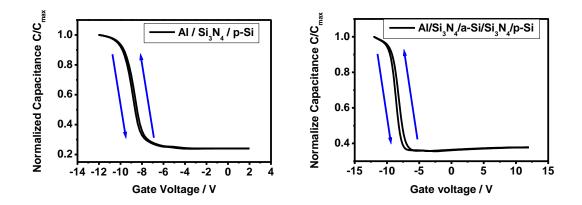

- Figure 7-5: Normalized C-V curves of MIS devices with (a) ~50nm silicon nitride only, (b) silicon nitride and a-Si. The thicknesses (in nm) of films in the device in (b) were Al/50/100/15/p-Si, for the configuration Al/Si3N4/a-Si/Si3N4/p-Si. The small hysteresis can be attributed to charge traps in the nitride......143

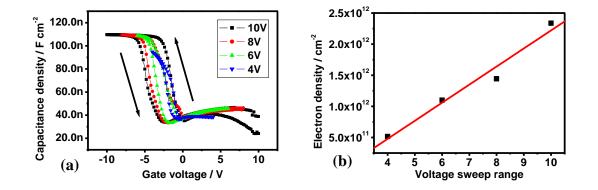

Figure 7-6: C-V curves of MIS devices with (a) silicon nitride + Polycrystalline silicon at various sweep voltage ranges. 5b shows the charge density variation with sweep voltage range. The Polycrystalline silicon thickness in the device is ~ 100 nm and the top and bottom nitride layers are ~50 and 15 nm

respectively......144

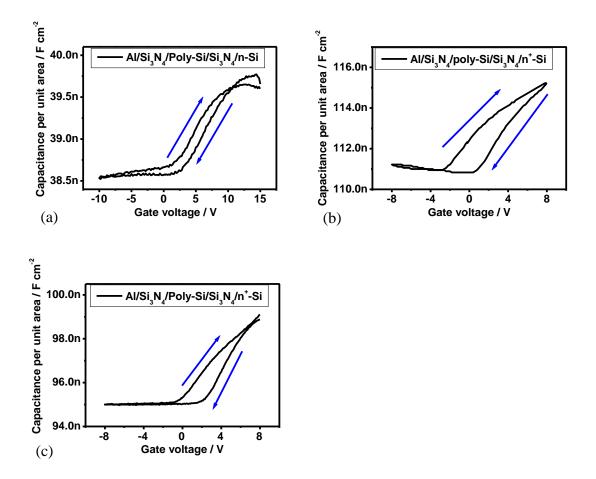

- Figure 7-8: Capacitance-voltage characteristic of MIM devices containing Si films grown on NFD-coated substrates at (a) 250 °C, (b) 300 °C and (c) 400 °C. .. 147

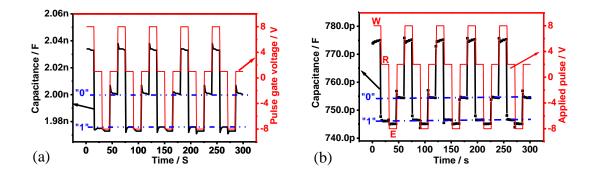

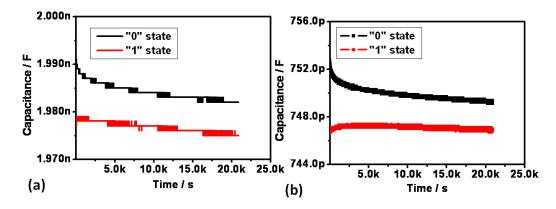

- Figure 7-9: Capacitance-time graphs showing device switching behaviours between states "on" and "off" or "0" and "1" when different voltage pulses for write, erase and read are applied, (a) 300 °C device and (b) 400 °C device......148

Figure 7-10: Capacitance-time variation at the written ("0") and erased ("1") state of devices at (a) 300 °C and (b) 400 °C......149

## Chapter 1. An Overview of Research

### **1.1 Introduction**

The outstanding growth and success of the semiconductor non-volatile memory (NVM) market is a direct consequence of the widespread presence of cellular phones and other types of portable equipments such as laptop computers, palm tops, MP3, iPods, digital cameras, and so on. Moreover, the proliferation of the aforementioned electronic devices and others has spawned demand for ultrahigh-density semiconductor NVM.

Until the mid 90s, the relevance of semiconductor NVM was mostly related to the key role they played in electronic systems and their cell concepts and less to the economic size of their market segment. The introduction of flash memories ushered in a dramatic increase in the semiconductor NVM market in 1995 and has continued to increase even though with some valleys and peaks.

Before flash memory, the main semiconductor electrically programmable NVM were the Erasable Programmable Read Only Memory (EPROM) and Electrically Erasable PROM (EEPROM). EPROMs offered the possibility of obtaining high density and cost effectiveness due to their small memory cell size of 1 transistor but could only be erased by ultra-violet (UV) radiation. On the other hand, EEPROM offered electrical erase ability with good endurance of 10<sup>6</sup> write/erase cycles, but because of the complex structure of their memory cell, (whose size cannot be scaled,) they were quite expensive. It is in the combination of the advantages of EPROM and EEPROM in flash memory i.e., the electrical erase ability of EEPROMs and cost effectiveness and high density advantages of EPROMs[1] that made flash memory an attractive technology. Indeed in 2009, the total revenue for flash memory in the 1<sup>st</sup> quarter was \$3.179billion which rose to \$4.247billion in the 2<sup>nd</sup> quarter with a growth of 33.6% [2]. Further forecasts by isuppli suggest that the flash memory card market will grow from 530 million units in 2010 to 9.5 billion units by 2013, which will be worth US \$26.5billion[3].

With the rise in Smart phones, the more features these phones offer - wireless internet, touch-screens, video capabilities- the more storage they would require. This leaves more room for the market of high density chips to grow[3]. For example, the market for solid-state drives (SSD) which utilize NAND flash memory has surged in recent years, even making inroads to the hard drive market[4]

The driving force behind the great success of flash memory has been the continuous cell-size reduction with corresponding cost reduction following Moore's law[5]. Scaling-down flash memory cell size enables higher cell density in a chip to be obtained, which is particularly critical for SSD to compete with hard disc drives (HDD)[6] Flash size scaled down by a factor of 30 in 1992-2002 specifically from  $4.2\mu m^2$  for the 0.6- $\mu m$  technological node to 0.16 $\mu m^2$  at the 0.13- $\mu m$  node[7]. The first generation flash (1990-1997) had memory density increase from 256 kb to 2 Mb, while from 1995-2000 (second generation), memory size increased from 1 Mb to 16 Mb[7]. From 2000-2010, there has been an enormous increase, with Samsung, the world largest producer of flash, releasing a new 64Gb moviNAND embedded flash memory chip and a 32Gb microSD removable memory card for mobile devices, both created with the 30nm technological node in early 2010[3]. According to the ITRS 2009 edition, flash cell area for 2010 was projected to be  $0.0041 \mu m^2$  and is expected to decrease further to 0.0026µm<sup>2</sup> by 2012[8]. Thus, compared to the cell-size in 2002, the flash memory cell would scale by a factor of about 62 in 2012, which is more than double the factor for the first decade (1992-2002).

Despite the success of flash memory, it faces some technological challenges in the near future, notably the continuous down-scaling of its cell size[9]. Lateral scaling which is one way of achieving high density is confronted with challenges such coupling (cell-to-cell interference), patterning, cross talk ratio and as manufacturability[10]. This cell-size reduction is approaching a dead-end ( $\leq 20$ nmtechnological node) where data retention and endurance will reduce due to thinner tunnel oxide as well as the statistical fluctuations of the number of stored electrons in the floating gate[11, 12]. Leakage currents will also increase significantly due to much thinner oxide layers. Coupled with the requirements of dielectric quality[12], these challenges resulting from the down-scaling of flash memory cell may result in less integration and less performance gains as well as seriously degraded reliability as a consequence.

Attempts are being made at many levels to solve these impending challenges of flash. In this regard, different alternative memory concepts and cell architecture are being explored by industry and academia with the aim of remedying the limitations of flash memory and other existing semiconductor memories like dynamic random access memory (DRAM) and static random access memory (SRAM). The main goal of these alternative emerging memory devices being explored is for them to be non-volatile, (i.e., hold content even without being powered), and are expected to have the speed and random access capabilities of the DRAM and SRAM, which are the main memory and cache memory in today's computers. For example, the Phase Change RAM does not utilize electrons and thus offers good scalability, and excellent endurance of  $10^{12}$ [13], therefore a promising solution to the scalability and endurance limitations of flash. Ferroelectric RAM have much higher write speeds than flash and so could be a solution to the programming speeds, while nanocrystal memory[14-16] and other charge trap devices like the silicon-oxide-nitride-oxide-silicon (SONOS), Band gap Engineered SONOS (BE-SONOS), TaN/Al<sub>2</sub>O<sub>3</sub>/SiN/SiO<sub>2</sub> (TANOS)[9] offer discrete charge storage nodes isolated from each other and they fulfil the functions of the continuous floating gate in flash. In the event of a pinhole in the tunnel oxide, the memory cell is not completely discharged as is the case with flash. Other alternative memories being explored are the Magneto resistive RAM (MRAM) [17-28], organic memory devices[29-31] and various 3-D cell architectures [32-36].

Among all the solutions being sort to solve the scaling problem and boost the performance of flash memory devices, three dimensional (3-D) flash is thought to be the ultimate solution[35, 37]. 3-D flash is highly attractive as it permits the integration of long-retention and ultra-high density cells without compromising device reliability [38, 39]. Furthermore, 3-D flash cells promise better endurance, longer retention times, lower power consumption as well as better energy efficiency than conventional flash memory. Moreover, the prospects for SSD to compete with, and even overtake HDD are greater with 3-D cells. It is expected that with 3-D memory, further scaling will be

possible [40, 41]. However, 3-D memory architecture has its own challenges; mainly the thermal processing of memory layers.

The vertically-stacked cell requires single-crystal silicon or polycrystalline silicon as floating gate or as channel, and it is also required that process temperatures be low so as not to damage underneath device layers. This is challenging because the most common techniques (Atmospheric Pressure Chemical Vapour Deposition (APCVD) or Low Pressure Chemical Vapour Deposition (LPCVD)) to produce single-crystal or polycrystalline silicon require very high process temperature  $\geq 600^{\circ}$ C. These high temperatures are not favourable with vertically stacked 3-D memory layers as they stress device structures- especially at interfaces between different materials. Furthermore, apart from increasing the thermal budget, they also cause the migration of dopants from their desired locations, consequently decreasing the doping density and possibly resulting in device leakage[42]. Thus, lowering processing temperatures conserves the thermal budget allowable during processing, and also permits the use of low thermal resistance materials like glass and some flexible plastics for use as substrates especially where the integration of memory in system-on-panel or system-on glass would be beneficial.

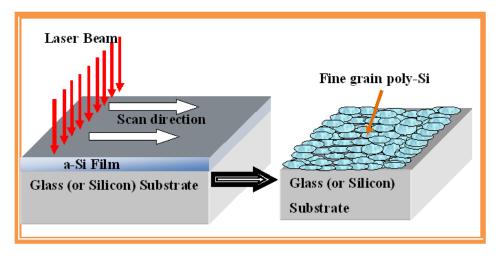

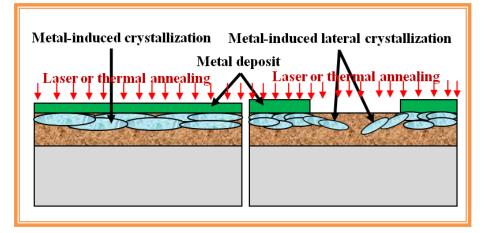

Various low temperature methods are used to deposit the polycrystalline silicon floating gate (FG) layers in conventional flash memory and Polycrystalline silicon channel in transistors. These include the deposition of amorphous silicon (a-Si) or hydrogenated amorphous silicon (a-S:H) at < 500 °C followed by the well known solidphase crystallization (SPC) [43-45], the excimer laser annealing (ELA) of a-Si or a-Si:H [46, 47], metal-induced-crystallization (MIC)[48-50] and metal-induced lateral crystallization (MILC)[51, 52]. These crystallization methods all require multiple steps to attain the quality of polycrystalline silicon necessary. The precursor material a-Si or a-Si:H is first grown using a PECVD reactor or other CVD methods from siliconcontaining source gases [53]. In SPC for instance, furnace annealing of the a-Si or a-Si:H is performed at high furnace temperatures (550-900 °C) for long hours[54] or rapid thermal annealing at  $\approx$ 700°C for few minutes[55]. The ELA method is expensive and the laser beam diameter is small. MIC and MILC crystallize the a-Si by using particles of metals that can form a eutectoid with silicon and often also require annealing. The resulting films exhibit low field effect mobility and high leakage currents due to the formation of sillicides [56-60]. The process also has many complex steps to attain the final Polycrystalline silicon film.

The question one can ask is whether it is possible to grow high quality polycrystalline silicon from silane gas only at temperatures  $\leq 400^{\circ}$ C using RF PECVD and without annealing, or whether it is possible to produce the polycrystalline silicon FG flash memory devices with all process temperatures  $\leq 400^{\circ}$ C and omitting annealing steps. If these questions can be answered in the affirmative, that would go a long way to reduce costs further and move closer to achieving 3-D flash memory.

### **1.2 Research Objectives**

The main objective of this project was to develop a novel low temperature technique for growing polycrystalline silicon films at temperatures  $\leq 400^{\circ}$ C and to investigate the possibility of using these films as the FG charge storage medium in flash NVM; in addition to examine the possibility of extending their use in 3-D flash memory.

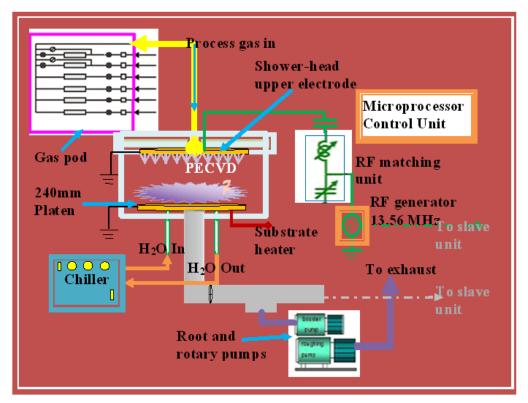

In order to attain these objectives, a source of material that would aid nucleation and growth of polycrystalline silicon at temperatures  $\leq 400$  °C was selected, which was nickel formate dihydrate, henceforth referred to in this thesis as NFD. Using a dip-coater, glass and silicon substrates were coated with NFD and the coatings studied by Fourier transform infra-red spectroscopy (FTIR). Silicon thin films were deposited on the coated substrates from silane as the only precursor gas, using the 13.56 MHz RF. PECVD reactor. The properties of the silicon films grown have been studied using various characterization techniques that include current-voltage (I-V) and capacitance-voltage (C-V) electrical measurements, ultra-violet visible spectroscopy (UV-Vis), FTIR and atomic force microscopy (AFM). The properties of these Si films have been compared with properties of Si films grown on uncoated substrates, grown alongside those on NFD-coated substrates. The memory behaviour of these films is investigated mainly by electrical measurements on capacitor-like devices using the LCR Bridge and the picoammeter. These devices contain a stack of an insulator and the silicon films obtained by the investigated novel technique and thermally evaporated metal electrode.

#### **1.3 Thesis structure**

The thesis is organized thus: In chapter 2 a brief historic evolution of the FG NVM and an overview of flash memory are presented. Additionally, alternative memory devices currently being considered as possible alternatives to flash memory are also discussed. Chapter 3 treats some commonly employed methods of obtaining polycrystalline silicon material, their merits and demerits while chapter 4 deals with the experimental methods employed in the research. The dip-coating of NFD on substrates and the FTIR investigation of NFD are reported in chapter 5 while the growth and characterization of silicon structures and charge storage in the films are treated in chapter 6. Chapter 7 discusses the fabrication of memory devices and investigation of memory characteristics such as retention and endurance. Finally, the summary of the research findings with original contribution made and recommendation for further studies is presented in chapter 8.

### **1.4 Publications and Conferences**

Some of the work described in this thesis has been published and/or presented at conferences and seminars.

#### **1.4.1 Referenced Works**

- Mih, T. A., Paul, S. and Cross, R. B. M., "Low Temperature Growth of Silicon Structures for Application in Flash Memory Devices", in *Materials and Physics of Nonvolatile Memories*, edited by C. Bonafos, Y. Fujisaki, P. Dimitrakis, E. Tokumitsu (Mater. Res. Soc. Symp. Proc. Volume 1250, pp 9-14, Warrendale, PA, 2010)

- Mih, T.A., Paul, S., Milanov, A.P., Bhakta, R., Devi, A., "Capacitance-Voltage Analysis of ZrO2 Thin Films Deposited by Thermal MOCVD Technique", ECS Transactions 25 (8 PART 2), pp. 901-907 (2009)

- Mih, T.A., Cross, R.B., Paul, S., "A Novel Method for The Growth of Low Temperature Silicon Structures for 3-D Flash Memory Devices, in Materials Research Society Symposium Proceedings 1112, pp. 265-269, Boston 2008

### 1.4.2 Oral and Poster Presentations

- Mih, T. A. and Paul, S., Towards Glass Compatible Memory- Charge Storage Non-Volatile Capacitive Memory Device with Silicon Structures from a New Type of Seeding Material, UK Semiconductor Conference, Sheffield 6<sup>th</sup>-7<sup>th</sup> July 2011;

- Mih, T. A. and Paul, S., Structural and Electrical Properties of Silicon Films Deposited by a Novel Low Temperature Technique, *Nanomaterials Conference*, London, June 2010

- Mih, T. A., Paul, S. and Cross, R. B. M, Low temperature Growth of Silicon Structures for applications in Flash Memory, *Materials and Physics of Nonvolatile Memories* Symposium G07-04, MRS spring Meeting, San Francisco April 2010

- Mih, T. A., Evolution of Storage Devices, Laboratory of Research on Advanced Materials and Nonlinear Sciences (LARAMANS) seminars, Buea-Cameroon, December 2009

- Mih, T. A., Paul, S., Milanov, A.P., and Devi, A., "Capacitance-voltage Analysis of ZrO2 Thin Films Deposited by Thermal MOCVD Technique", in *EuroCVD17/CVDXVII*, Vienna 2009.

- Mih, T. A., Cross, R. B. M., Paul, S., "A Novel Method for The Growth of Low Temperature Silicon Structures for 3-D Flash Memory Devices, in *Materials Research Society Symposium*, MRS Fall Meeting, Boston December 2008.

### 1.4.3 Submitted Journals

- Mih, T. A. and Paul, S., "Rewritable Memory Behavior of Polycrystalline silicon Films Grown by a Low Temperature Method", *Applied Physics Letters* (Submitted, 2011)

- Mih, T. A. and Paul, S., "Dip-Coating of Nickel Formate Dihydrate and the Effects of Dip-Coating Parameters on the Resulting Films Thicknesses", *Materials Science and Engineering B* (Submitted 2011)

Mih, T. A. and Paul, S., "Poly-Si Non-Volatile Memory on Glass from a Novel Low-Temperature Technique", Advanced Materials Communications, (Submitted 2011)

# Chapter 2. Flash Memory and Related Emerging Storage Devices

### 2.1 Introduction

Semiconductor memories can be broadly classed into two main categories namely Volatile Memories (VM), and Non-Volatile Memories (NVM). The former retains data only as long as a power supply is switched on. This class of memory are mainly used in the execution of code, where fast access to data is necessary due to their high execution speed but they have the disadvantage that their storage density is low and need a power supply to operate. The SRAM and DRAM fall in this class of memory. On the other hand, NVM are memory devices that can retain stored data even when power is switched off. This ability is very attractive for portable device electronics since these require a field update of code or data and the user's ability to update information in real time. In this class of memory, we have EPROM, EEPROM and Flash memory. Figure 2-1 shows the different classes of semiconductor memories.

Figure 2-1: Semiconductor memory tree

This chapter aims at giving a thorough overview of conventional flash memory cells; their structure and their basic operation mechanism in order to provide an understanding of the underlying physics so as to better appreciate the different device structures and processing technologies. Additionally, the current challenges faced by conventional flash memory are reviewed as well as solutions suggested of some emerging memory devices and architecture. However, to give a complete picture of how flash memory is related to other class memories, like SRAM and DRAM, these will be introduced briefly, beginning with the hard disc drive which, though not a semiconductor memory, stands as a reference to solid-state drives composed of arrays of flash memory cells.

#### 2.1.1 Hard Disc Drive and Solid-State Drive

The hard disk drive (HDD) invented by IBM in 1956[61], is a direct access storage device for digital data. Figure 2-2 shows the diagram of the HDD. It contains one or more rigid platters on a spindle driven by electric motors and is enclosed in a metal case.

Above the platter is a read/write head, floating on a cushion of air. The read/write heads are held by the access arm also (known as the actuator arm). They are moved by the actuator radially across the platters as they spin about the spindle at very high speeds (4200 to 15000 rpm). The platters are made of nonmagnetic material usually aluminium alloys or glass, which are coated with a very thin (10-20nm) layer of magnetic material, e.g. cobalt-based alloys. The magnetic surfaces are divided into sub-micrometer regions that are used to encode a single binary digit of information into each region. Each region is composed of a few hundreds of magnetic grains and each grain about 10 nm in size

forms a magnetic domain. Each submicron region then forms a magnetic dipole which generates a highly localized magnetic field nearby.

In a HDD, a write head is used to write data by directionally magnetizing a ferromagnetic material to represent a binary digit 0 or 1. This is done by generating a very strong local magnetic field. Data is read by detecting the magnetization of the material. In today's heads, the read and write elements are in close proximity, and made of magneto-resistive and thin-film inductive materials respectively.

A solid-state drive (SSD) is a flash memory-based storage device. It is nonvolatile just like HDD, but unlike HDD, which is an electromechanical device with moving parts (spinning disc and movable read/write heads), SSD contains no moving parts and it uses NAND-based flash memory microchips. Early SSDs were RAM-based 16Kb introduced in 1978 by Texas Memory Systems that would have cost \$1million per Gb[63], but very recently very high density storage flash memory-based SSD of up to 256GB have been released, with lowest prices hitting \$1.05 per Gb on a particular day in June 2010[64]. That is a tremendous drop in price over the years. More consumers are now turning away from HDD in preference of SDD for the following advantages[65]:

- 1. They have premium input/output (I/O) performance for data access operations over their HDD rivals, typically more than 100 times better;

- They save power better than HDD; typically they use 0.51% of the power HDDs would use for a given IOPS implementation. This is due to the fact that they have no moving parts and they require fewer drives for the same operation compared to HDDs;

- The entire SDD is utilized for each intended purpose while the usable capacity of HDD is significantly reduced to less than 50% by shortstroking in order to increase the input/output performance per second (IOPS);

- Enterprise SSDs (savers and storage applications SDDs) occupy far less space than HDDs;

- Service life of SSD is longer (10years) than advertised service life of HDD (5years). This is so because the moving parts of HDD wear out with time.

Despite these advantages, and the fact that SSD prices have dropped tremendously, they are still more expensive than HDD for similar or equal capacity. For instance, Higginbotham of priceG2 Inc reported that in mid 2010, the lowest price tracked for a 2.5 inch internal portable 250GB HDD was \$0.16/GB while the price was \$1.05/GB for 256GB SSD, showing SSD costs about 7 times HDD[64]. However, SSD prices are dropping and it may be possible to get an 80GB SDD for approximately \$23 by 2012[64]. With the advent of 3-D flash, situations may improve further.

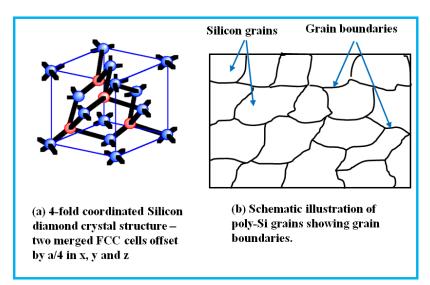

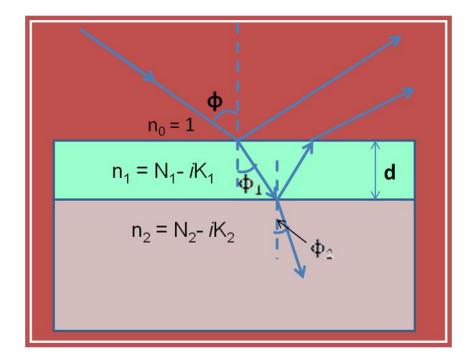

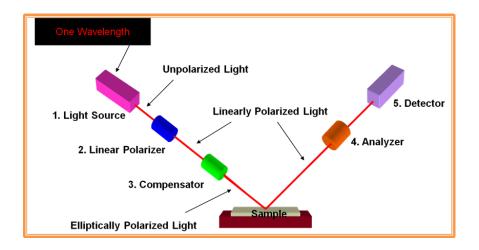

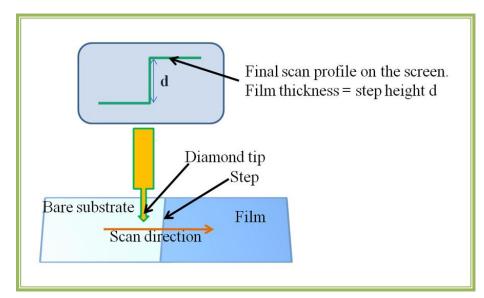

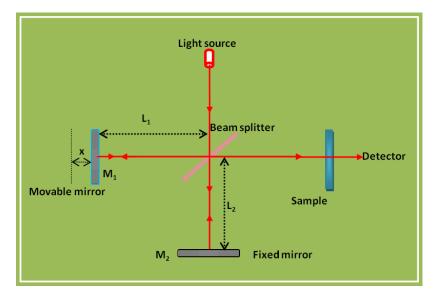

#### 2.1.2 Random Access Memory (RAM)