The 9th International Conference on Power Electronics, Machines and Drives (PEMD 2018)

# Novel PLL for power converters under unbalanced and distorted grid conditions

eISSN 2051-3305 Received on 22nd June 2018 Accepted on 27th July 2018 E-First on 14th May 2019 doi: 10.1049/joe.2018.8100 www.ietdl.org

Jianguo Wang<sup>1</sup> ⋈, Jihong Wang<sup>1</sup>, Xing Luo<sup>1</sup>

¹School of Engineering, University of Warwick, UK

⋈ E-mail: j.wang.60@warwick.ac.uk

**Abstract:** A novel phase-locked loop (PLL) with simple structure is proposed in the present work for three-phase power converters under adverse grid conditions. Based on a synchronous rotating frame PLL (SRF-PLL), multi-resonant harmonic compensators with the ability of accommodating frequency deviations are employed in the feedback path of a pre-filter. As a result, the negative-sequence component and harmonic distortions of grid voltage can be attenuated. Different from existing methods, only classical regulators are used, avoiding complicated networks for the decoupling of unbalance and harmonics and thus greatly simplifying the control algorithm. The proposed method is analysed and designed in both the continuous s-domain and discrete z-domain, whereby stable, fast, accurate, and robust responses are achieved. Simulation results have been obtained to show the improved performance of the proposed PLL compared with two widely used methods.

### 1 Introduction

Grid synchronisation is crucial for a number of power conversion devices, e.g. grid-connected inverters, active power filters, and static synchronous compensator etc. [1, 2]. In particular, grid-connected power converters form an indispensable bridge for the integration of distributed power generation and energy storage such as compressed air energy storage with power network [3–5]. Synchronisation with the grid is essential for the power converters to achieve proper control of the power delivered to the grid, even under adverse conditions with unbalance and harmonic distortions [6, 7].

Among different synchronisation strategies such as zero crossing methods and filter algorithms, phase-locked loop (PLL) is most widely used [8]. PLLs should be able to accurately detect the phase signal of the positive sequence component of grid voltage at fundamental frequency [9]. While working in the balanced three-phase grid voltage condition, a basic synchronous reference frame (SRF) PLL is able to track accuracy phase information. However, under non-ideal conditions, for example with unbalanced grid faults and/or harmonic distortions, improvements to the SRF-PLL or novel PLLs are necessary.

A number of advanced three-phase PLLs have been reported, for instance a widely used decoupled double SRF-PLL (DDSRF-PLL) [10] and dual second-order generalised integrator-based PLL (DSOGI-PLL) [11], which have demonstrated the improved performance. However, the methods are very complicated due to the decoupling units for unbalance and harmonics. A hybrid PLL with the combination of the DDSRF and a stationary frame PLL was reported to tackle unbalanced faults [12], but apparently at the expense of increased complexity. Delayed signal cancellation PLLs were proposed in [13-16], which demonstrated good harmonics filtering capability. However, a number of cascaded signal cancellation blocks are needed in order to achieve satisfactory performance. As a result, the bandwidth is severely decreased and the implementation complexity dramatically increased, and the method is sensitive to frequency deviations [14]. A decoupling strategy with a fixed sampling period sliding discrete Fourier transform and an instantaneous symmetrical components method was proposed in [17], which involved complex intricate mathematical calculations. Moving average filter-based PLLs have been designed, but the phase delay is increased and the stability is weaken which degrades transient responses [12, 18, 19]. Carugati et al. [20] proposed a variable sampling period filter-based PLL using the sliding Goertzel transform, which also resulted in

complicated mathematical derivations. A repetitive learning-based PLL in which a Lyapunov technique was used to improve the performance was proposed in [21], but it occupied extra computation space and burden. Many other strategies such as modified SRF-based digital PLL [22], two-phase stationary frame enhanced PLL [23], and rotor PLL [24] have been reported, to name but a few. However, most of these methods are rather sophisticated in structure, which significantly increases the complexity of implementation and the computation burden of microcontrollers such as DSP and Opal-RT, increasing the possibility of time delay and overruns [25].

In order to address the limitations, a novel PLL with simple structure is proposed in the present work. Based on the SRFPLL, multi-resonant harmonic compensators [7, 25] with the ability of accommodating frequency deviations are employed in the feedback path of a pre-filter stage. As a result, the negative-sequence component and harmonic distortions of grid voltage can be eliminated. Compared with those existing methods, complicated unbalance and harmonics decoupling network is not needed, which greatly simplifies the control algorithm. The proposed method is described and analysed in detail in both the continuous *s*-domain and discrete *z*-domain. Simulated results have been obtained which show the advantages of the simple but novel PLL.

### 2 Proposed PLL

The PLL proposed in the presented work is based on the SRF. The advantage in the SRF is that the fundamental positive sequence component of grid voltage can be transformed into DC signals while harmonics at two different frequencies could result in the same frequency, which facilitates the realisation of closed-loop regulators [8]. Multi-resonant harmonic compensators are employed to form a pre-filter that mitigates the negative sequence component and harmonics.

# 2.1 Grid voltage and transformation

Under adverse conditions, the grid voltage may be unbalanced and distorted. For the purpose of simplicity and demonstration, the voltage in the present work is assumed to contain fundamental negative sequence component and 5th and 7th balanced harmonics, given as:

$$\begin{bmatrix} v_{a} \\ v_{b} \\ v_{c} \end{bmatrix} = V^{+} \begin{bmatrix} \cos\omega t \\ \cos(\omega t - \frac{2}{3}\pi) \\ \cos(\omega t + \frac{2}{3}\pi) \end{bmatrix} + V^{-} \begin{bmatrix} \cos(\omega t + \theta_{1}) \\ \cos(\omega t + \frac{2}{3}\pi + \theta_{1}) \\ \cos(\omega t - \frac{2}{3}\pi + \theta_{1}) \end{bmatrix} + V_{5} \begin{bmatrix} \cos(5\omega t + \theta_{5}) \\ \cos(5\omega t + \frac{2}{3}\pi + \theta_{5}) \\ \cos(5\omega t - \frac{2}{3}\pi + \theta_{5}) \end{bmatrix} + V_{7} \begin{bmatrix} \cos(7\omega t + \theta_{7}) \\ \cos(7\omega t - \frac{2}{3}\pi + \theta_{7}) \\ \cos(7\omega t + \frac{2}{3}\pi + \theta_{7}) \end{bmatrix},$$

$$(1)$$

where  $\omega$  is the fundamental angular frequency,  $V^+$ ,  $V^-$ ,  $V_5$ , and  $V_7$  are the amplitudes of each component, and  $\theta_{1,5,7}$  the initial phases.

Using the Clarke and Park transformations, the grid voltage (1) is transformed into:

$$\begin{bmatrix} v_d \\ v_q \end{bmatrix} = V^{+} \begin{bmatrix} \cos(\omega t - \hat{\theta}) \\ \sin(\omega t - \hat{\theta}) \end{bmatrix} + V^{-} \begin{bmatrix} \cos(-\omega t - \theta_1 - \hat{\theta}) \\ \sin(-\omega t - \theta_1 - \hat{\theta}) \end{bmatrix} + V_{5} \begin{bmatrix} \cos(-5\omega t - \theta_5 - \hat{\theta}) \\ \sin(-5\omega t - \theta_5 - \hat{\theta}) \end{bmatrix} + V_{7} \begin{bmatrix} \cos(7\omega t + \theta_7 - \hat{\theta}) \\ \sin(7\omega t + \theta_7 - \hat{\theta}) \end{bmatrix},$$

(2)

where  $\hat{\theta}$  is the phase signal detected by the PLL. Assuming the detection is accuracy, i.e.  $\hat{\theta} = \omega t$ , (2) is yielded as:

$$\begin{bmatrix} v_d \\ v_q \end{bmatrix} = V^+ \begin{bmatrix} 1 \\ 0 \end{bmatrix} + V^- \begin{bmatrix} \cos(2\omega t + \theta_1) \\ -\sin(2\omega t + \theta_1) \end{bmatrix}

+ V_5 \begin{bmatrix} \cos(6\omega t + \theta_5) \\ -\sin(6\omega t + \theta_5) \end{bmatrix} + V_7 \begin{bmatrix} \cos(6\omega t + \theta_7) \\ \sin(6\omega t + \theta_7) \end{bmatrix}.$$

(3)

As can be seen, the positive sequence is transformed into DCc signals and the negative sequence into 2nd harmonics, while both the 5th and 7th harmonics become 6th order. Therefore, in order to extract clean phase signals, the 2nd and 6th harmonics should be supressed in the pre-filtering stage which will be introduced in the following.

# 2.2 Proposed PLL

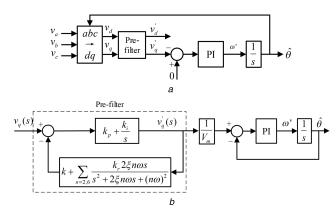

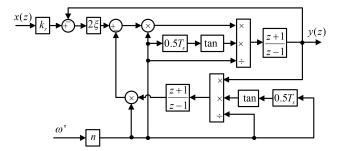

The structure of the proposed PLL is shown in Fig. 1a, and its linearised control loop block diagram in the q-axis is given in Fig. 1b. The pre-filter is placed before a standard SRF-PLL [8]. Different from the aforementioned sophisticated PLLs with complicated pre-filters, the proposed method only employs classical regulators: a proportional integral (PI) in the forward path, and a proportional term k and resonant compensators in the feedback path.

The closed-loop transfer function of the pre-filter is obtained as:

$$G_{cl}(s) = \frac{v'_{dq}(s)}{v_{dq}(s)}$$

$$= \frac{k_p + \frac{k_i}{s}}{1 + \left(k_p + \frac{k_i}{s}\right)\left(k + \sum_{n=2,6} \frac{2k_r \zeta n\omega s}{s^2 + 2\zeta n\omega s + (n\omega)^2}\right)},$$

(4)

where  $v_{dq}(s) = v_d(s) + jv_q(s)$ ,  $v_{dq}'(s) = v_d'(s) + jv_q'(s)$  As can be seen, the PI is used to track the DC signals, and the resonant terms are able to supress the 2nd and 6th harmonics because of large magnitude gains at the specific frequencies [7, 26].

It should be noted that resonant terms at other frequencies can be added to attenuate other order harmonics that may exist in the grid voltage. Therefore, the proposed PLL can be adjusted according to the components of grid voltage, increasing the flexibility and simplicity.

Fig. 1 Block diagram of the proposed PLL

(a) Structure, (b) Linearised control loop with the pre-filter

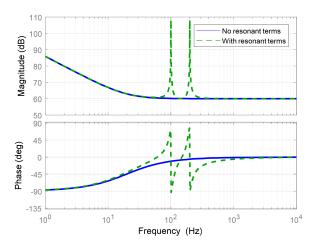

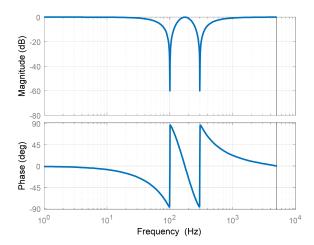

Fig. 2 Bode diagrams of open-loop transfer function

# 3 Analysis and design

In this section, the PLL is analysed and designed in both the continuous *s*-domain and discrete *z*-domain. The digital implementation in *z*-domain is particularly discussed to achieve frequency adaptability to avoid frequency warping. Detailed analyses of the SRF-PLL can be found in [8, 10], hence it will not be discussed in the paper. The pre-filter is analysed in the following.

# 3.1 Analysis in the s-domain

Bode diagrams of the open-loop transfer function, with and without the resonant terms, are shown in Fig. 2. It is apparent that the resonant terms only influence the response at the resonant frequencies by introducing abrupt magnitude ripples and  $\pm 90^{\circ}$  phase jumps. Furthermore, the phase responses never cross  $-180^{\circ}$ ; therefore, the system is always stable even with the insertion of other resonant terms at higher harmonic frequencies [25, 27]. Therefore, sufficient large  $k_p$  and  $k_i$  can be used so that the closed-loop transfer function (4) in steady state can be approximated as:

$$G_{\rm cl}(s) \simeq \frac{k_p s + k_i}{(1 + k k_p) s + k k_i} \simeq \frac{1}{k} \,. \tag{5}$$

In order to achieve zero steady-state error in tracking the d- and q-axes voltages, k should be 1.

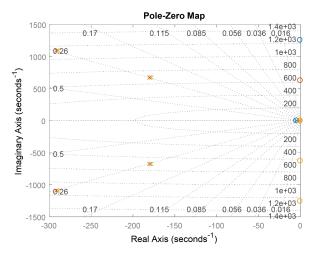

Closed-loop pole-zero maps, with fixed  $k_r$  and  $\xi$  and different values of  $k_p$  and  $k_i$ , are shown Fig. 3. It can be seen that the PI has a negligible influence on the position of the poles. Thus, the transient responses are mainly determined by the resonant terms.  $k_p = 100$  and  $k_i = 500$  are used in this case.

Regarding the resonant terms in the pre-filter, the gain  $k_r$  should be a large value to gain a high attenuation of harmonics, whereas the damping factor  $\xi$  should be low so that a low bandwidth is

Fig. 3 Pole-zero maps with different parameters

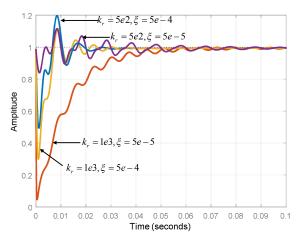

Fig. 4 Step responses of the pre-filter with different parameter values of the resonant terms

obtained to achieve effective harmonic compensation [7]. The step responses of the pre-filter with different values of  $k_r$  and  $\xi$  are illustrated in Fig. 4.  $k_r = 1000$  and  $\xi = 0.0005$  are chosen to obtain a fast and relatively smooth response.

#### 3.2 Implementation in the z-domain

In order to implement the proposed method in a digital controller such as DSP, the PLL needs to be discretised. The PI controller can be discretised using the Tustin's method [2]. With respect to the resonant terms, the Tustin's method with pre-warping is adopted to avoid frequency warping and thus to effectively eliminate the harmonics, by replacing the Laplace variable 's' with [25]

$$s = \frac{n\omega}{\tan(0.5n\omega T_s)} \frac{z-1}{z+1} \,. \tag{6}$$

As a result, the resonant terms are discretised to

$$\sum_{n=2,6} \frac{2k_r \xi n\omega s}{s^2 + 2\xi n\omega s + (n\omega)^2} \left| s = \frac{n\omega}{\tan \frac{n\omega T_s}{2}} \frac{z - 1}{z + 1} \right|$$

$$= \sum_{n=2,6} \frac{2k_r \xi \tan \frac{n\omega T_s}{2} (z^2 - 1)}{(z - 1)^2 + 2\xi \tan \frac{n\omega T_s}{2} (z^2 - 1) + \tan^2 \frac{n\omega T_s}{2} (z + 1)^2} .$$

(7)

To make the PLL frequency adaptive, the resonant terms are implemented as Fig. 5, where  $\omega'$  is the angular frequency detected by the PLL (see Fig. 1), x(z) denotes the input and y(z) the output.

The resultant closed-loop Bode diagram is shown in Fig. 6 (a sampling frequency of 10 kHz is used). It is obvious that the pre-

Fig. 5 Digital implementation of the resonant terms

Fig. 6 Closed-loop Bode diagram of the pre-filter

filter is able to accurately track DC signals with zero steady-state error and successfully mitigate the harmonics without frequency warping.

#### 4 Results

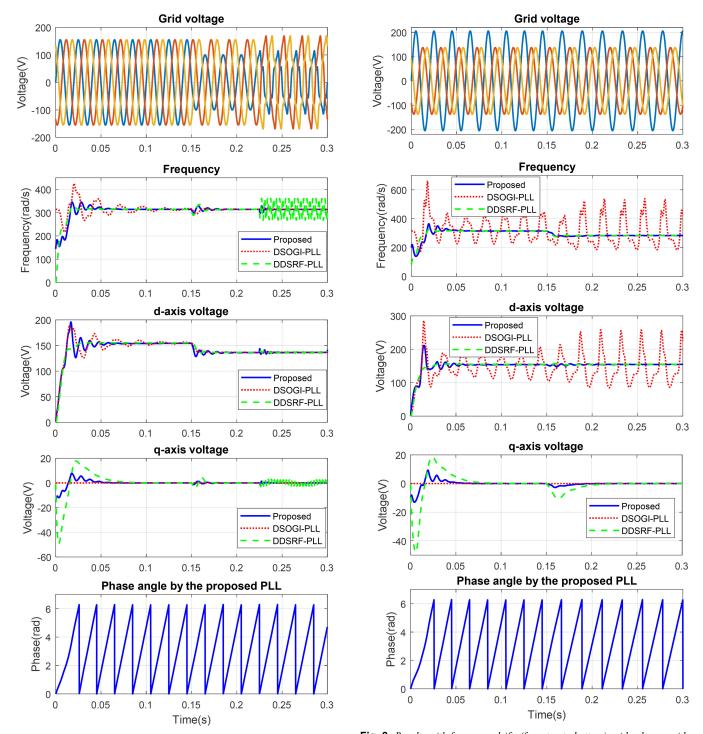

Simulations in Matlab/Simulink have been carried out to validate the proposed PLL and also to verify the advantages over two widely used method: DDSRF-PLL [10] and DSOGIPLL [11] which contains complicated decoupling units for unbalance and harmonics. The 5th and 7th harmonics decoupling units are included in the DSOGI-PLL according to the design in [11]. Identical SRF-PLL has been used in these three strategies for a fair comparison.

In the first scenario, the fundamental frequency is fixed at 50 Hz. The amplitude of single-phase grid voltage is set to 155 V. At the first 0.15 s period, the grid voltage is balanced, from 0.15 s the A-phase voltage amplitude is decreased to 100 V, from 0.225 s 5th ( $V_5 = 15$ ,  $\theta_5 = -25^{\circ}$ ) and 7th ( $V_7 = 10$ ,  $\theta_7 = 35^{\circ}$ ) harmonics are added to the grid voltage. The results are demonstrated in Fig. 7. It can be seen that the DSOGI-PLL has a relatively slow response in tracking the frequency and fundamental positive sequence d-axis voltage (= V<sup>+</sup>) although the dynamic error in tracking the fundamental positive sequence q-axis voltage is ignorable, while the DDSRF-PLL is able to resist the unbalance but fails to mitigate the harmonics. By comparison, the proposed PLL is able to accurately and quickly extract clean positive-sequence signals.

In the second scenario, the frequency adaptive capability is tested. The grid voltage in this case consists of a fundamental positive-sequence ( $V^+$  = 155) and negative-sequence ( $V^-$  = 50,  $\theta_1$  = 0°), the fundamental frequency is changed from 50 to 45 Hz at 0.15 s. The results are presented in Fig. 8. Both the proposed method and DDSRF-PLL can fast and accurately detect the signals of the positive-sequence component, even when the grid frequency deviates from its nominal value. The DSOGI-PLL, on the other hand, generates significant fluctuations in the frequency and d-axis voltage signals. As a matter of fact, it takes more than 1 s for the DSOGI-PLL to achieve zero steady-state error. Therefore, the robustness of the DSOGI-PLL against frequency deviations is proved to be very weak.

**Fig. 7** Results with fixed frequency: (from top to bottom) grid voltage, grid frequency, fundamental positive-sequence d-axis voltage, fundamental positive sequence q-axis voltage, and the positive sequence phase angle detected by the proposed PLL

The simulated results confirm the advantages of the proposed PLL. In brief, the DDSRF-PLL is sensitive to harmonic distortions and the DSOGI-PLL has slow dynamic response leading to a weak robustness against frequency deviations. The proposed PLL, with a much simpler structure, is immune to grid unbalance and harmonics and at the same time is adaptive to frequency drifts with fast response.

## 5 Conclusion

Here, a novel PLL has been proposed for three-phase power converters under unbalanced and distorted grid conditions. Based on the SRF-PLL, a pre-filtering stage with multi-resonant harmonic compensators has been designed. The method is analysed and

**Fig. 8** Results with frequency drift: (from top to bottom) grid voltage, grid frequency, fundamental positive-sequence d-axis voltage, fundamental positive-sequence q-axis voltage, and the positive sequence phase angle detected by the proposed PLL

tuned in both the continuous s-domain and discrete z-domain. In particular, the digital implementation in z-domain has been discussed in order to avoid frequency warping. In comparison with existing methods, the proposed PLL is frequency adaptive and is able to fast and accurately detect clean phase signals with significantly reduced control complexity and computation burden due to its simpler structure. The advantages of the proposed strategy have been validated by simulated results in different scenarios.

### 6 Acknowledgments

The authors would like to thank the funding support from Engineering and Physical Science Research Council (EPSRC), UK (EP/K002228/1 and EP/L019469/1).

#### 7 References

- Blaabjerg, F., Teodorescu, R., Liserre, M., et al.: 'Overview of control and grid synchronization for distributed power generation systems', IEEE Trans. Ind. Electron., 2006, **53**, (5), pp. 1398–1409 Wang, J., Yan, J.D., Jiang, L.: 'Pseudo-derivative feedback current control for

- [2] three-phase grid-connected inverters with LCL filters', IEEE Trans. Power Electron., 2016, 31, (5), pp. 3898–3912

- Wang, J., Lu, K., Ma, L., et al.: 'Overview of compressed air energy storage [3] and technology development', *Energies*, 2017, **10**, (7), p. 991 Luo, X., Wang, J., Dooner, M., et al.: 'Overview of current development in

- [4] electrical energy storage technologies and the application potential in power system operation', *Appl. Energy*, 2015, **137**, pp. 511–536 Wang, J., Yan, J.D.: 'Using virtual impedance to analyze the stability of LCL-

- [5] filtered grid-connected inverters'. Proc. IEEE Int. Conf. Ind. Technol., Seville, Spain, 2015, pp. 1220-1225

- [6] Timbus, A., Liserre, M., Teodorescu, R., et al.: 'Synchronization methods for three phase distributed power generation systems-An overview and evaluation'. Proc. IEEE 36th PESC, Recife, Brazil, 2005, pp. 2474–2481 Castilla, M., Miret, J., Matas, J., et al.: 'Control design guidelines for single-

- [7] phase grid-connected photovoltaic inverters with damped resonant harmonic compensators', IEEE Trans. Ind. Electron., 2009, **56**, (11), pp. 4492–4501

- Chung, S.-K.: 'Phase-locked loop for grid-connected three-phase power [8] conversion systems', Proc. Inst. Elect. Eng. -Electron. Power Appl., 2000, **147**, (3), pp. 213–219

- Golestan, S., Guerrero, J.M., Vasquez, J.C.: 'Three-phase PLLs: a review of [9] recent advances', IEEE Trans. Power Electron., 2017, 32, (3), pp. 1894–1907

- [10] Rodríguez, P., Pou, J., Bergas, J., et al.: 'Decoupled double synchronous reference frame PLL for power converters control', IEEE Trans. Power Electron., 2007, 22, (2), pp. 584-592

- Rodríguez, P., Luna, A., Candela, I., et al.: 'Multiresonant frequency-locked [11] loop for grid synchronization of power converters under distorted grid conditions', *IEEE Trans. Ind. Electron.*, 2011, **58**, (1), pp. 127–138 Golestan, S., Guerrero, J.M., Abusorrah, A.M., *et al.*: 'Hybrid synchronous' stationary reference-frame-filtering-based PLL', *IEEE Trans. Ind. Electron.*, 2011, 620–630.

- [12] 2015, **62**, (8), pp. 5018–5022

- Golestan, S., Ramezani, M., Guerrero, J.M., et al.: 'dq-frame cascaded delayed signal cancellation-based PLL: analysis, design, and comparison with moving average filter-based PLL', IEEE Trans. Power Electron., 2015, 30, (3), pp. 1618–1632

- [14] Huang, Q., Kaushik, R.: 'An improved delayed signal cancellation PLL for fast grid synchronization under distorted and unbalanced grid condition', IEEE Trans. Ind. Appl., 2017, 53, (5), pp. 4985-4997

- Wang, Y.F., Li, Y.W.: 'Three-phase cascaded delayed signal cancellation PLL [15] for fast selective harmonic detection', IEEE Trans. Ind. Electron., 2013, 60, (4), pp. 1452-1463

- Hamed, H.A., Abdou, A.F., Bayoumi, E.H., et al.: 'Frequency adaptive [16] CDSC-PLL using axis drift control under adverse grid condition', IEEE Trans. Ind. Electron., 2017, 64, (4), pp. 2671–2682

Subramanian, C., Kanagaraj, R.: 'Rapid tracking of grid variables using

- prefiltered synchronous reference frame PLL', *IEEE Trans. Instrum. Meas.*, 2015, **64**, (7), pp. 1826–1836

- Golestan, S., Ramezani, M., Guerrero, J.M., et al.: 'Moving average filter based phase-locked loops: performance analysis and design guidelines', IEEE Trans. Power Electron., 2014, 29, (6), pp. 2750-2763

- Golestan, S., Guerrero, J.M., Vidal, A., et al.: 'PLL with MAF-based prefiltering stage: small-signal modeling and performance enhancement',

- IEEE Trans. Power Electron., 2016, 31, (6), pp. 4013–4019 Carugati, I., Maestri, S., Donato, P.G., et al.: 'Variable sampling period filter PLL for distorted three-phase systems', IEEE Trans. Power Electron., 2012,

- 27, (1), pp. 321-330 Sahoo, S., Prakash, S., Mishra, S.: 'Power quality improvement of grid connected DC microgrids using repetitive learning based PLL under abnormal grid conditions', *IEEE Trans. Ind. Appl.*, 2018, **54**, (1), pp. 82–90 da Silva, C.H., Pereira, R.R., da Silva, L.E.B., *et al.*: 'A digital PLL scheme

- [22] for three-phase system using modified synchronous reference frame', *IEEE Trans. Ind. Electron.*, 2010, **57**, (11), pp. 3814–3821

- Wu, F., Zhang, L., Duan, J.: 'A new two-phase stationary-frame-based enhanced PLL for three-phase grid synchronization', IEEE Trans. Circuits Syst. II Exp. Briefs, 2015, 62, (3), pp. 251-255

- [24] Rani, M.A., Nagamani, C., Ilango, G.S.: 'An improved rotor PLL (R-PLL) for

- enhanced operation of doubly fed induction machine', *IEEE Trans. Sustain. Energy*, 2017, **8**, (1), pp. 117–125

Wang, J., Yan, J.D., Jiang, L., *et al.*: 'Attenuation of low-order current harmonics in three-phase LCL-filtered grid-connected inverters'. Proc. 41st [25] Annu. Conf. IEEE Ind. Electron. Soc., Yokohama, Japan, November 9-12, 2015, pp. 1982-1987

- Zhang, X., Spencer, J.W., Guerrero, J.M.: 'Small-signal modeling of digitally [26] controlled grid-connected inverters with LCL filters', *IEEE Trans. Ind. Electron.*, 2013, **60**, (9), pp. 3752–3765

- Wang, J., Yan, J.D., Jiang, L., et al.: 'Delay-dependent stability of single-loop controlled grid-connected inverters with LCL filters', IEEE Trans. Power Electron., 2016, 31, (1), pp. 743-757