publisher prior to publication. The final version is available at http://dx.doi.org/10.1109/LASCAS.2017./948102

# Design of Experiments Implementation towards Optimization of Power Distribution Networks

Felipe de Jesús Leal-Romo Intel Corp. Zapopan, Jalisco, 45019 Mexico felipe.de.jesus.leal.romo@intel.com José E. Rayas-Sánchez

Department of Electronics, Systems, and Informatics

ITESO – The Jesuit University of Guadalajara

Tlaquepaque, Jalisco, 45604 Mexico

erayas@iteso.mx

Jiangqi He Intel Corp. Chandler, AZ 85226, U.S.A. jiangqi.he@intel.com

Abstract— Modern computer servers require cutting edge technologies to meet their expected high performance. Among several relevant disciplines, power delivery (PD) is a key player in this regard. Efficient and reliable statistical methods to reduce cost while keeping adequate server's performance are highly demanded from the PD perspective. This paper addresses a feasible statistical methodology based on design of experiments (DoE) for evaluating platform's power delivery ingredients. Our methodology explores voltage regulator's intrinsic parameters, compensation networks, non-linear compensation parameters, and the amount of bulk capacitors. Our statistical approach aims at identifying those variables with the largest impact on computer server's PD performance, as well as optimizing them at the system level while achieving cost reduction.

Keywords— design of experiments; laboratory correlation; power delivery simulation; statistics control; voltage regulator

## I. INTRODUCTION

Server's performance imposes severe demands for higher bandwidths, low cost power solutions, and high computing performance. Thus, modern computer servers require cutting edge technologies to meet all the above expectations. In this regard, power delivery (PD) requires some tradeoff decisions to select an adequate voltage regulator, a suitable and affordable decoupling solution, and a robust stack up design to handle sharp load current demands, while keeping silicon under expected performance.

Several authors have explored different PD methodologies, such as establishing target impedance across a wide frequency range to select the decoupling capacitor solutions needed by the power distribution network (PDN) [1, 2], as well as time domain approaches [3] and jitter analysis [4, 5] for estimating voltage drop and voltage margins to come up with robust design solutions.

Industrial PD design is still considered an "art"; as it is a heavily heuristic process and very dependent on engineer's expertise. Identifying which variables are most impactful to the PDN space is a highly complex task, usually performed in practice by parametric sweeps, exhaustive enumeration, and engineering knowledge and experience. To the best of our knowledge, formal statistical methodologies based on design of experiments (DoE) for the optimization of the PDN have never been reported. Our contribution in this papers aims at filling that gap. In particular, our paper focuses on solving computer server's PD system by optimizing voltage regulator's (VR) tuning parameters as well as its bulk capacitors solution.

In Section II, we conceptually describe how design of experiments (DoE) can be exploited to develop PD behavioral models. Section III presents a DoE simulation approach identifying the most important variables impacting the whole VR solution. Section III follows the same DoE methodology but as applied to the physical VR implementation incorporating laboratory measurements. Section IV makes a comparison simulation and between both scenarios, physical implementation, with the aim of performing system optimization using response surface methods (RSM). Finally, Section V makes conclusions from the experimental work, and sets future directions to improve PD design.

### II. MODELING POWER DELIVERY BY DOE

DoE has been adopted in some disciplines closely related to PDN design, such as I/O's electrical validation and verification [6] and signal integrity (SI) analysis [7, 8], where designers statistically assess cases to find the best channel configuration with the best equalization recipe to avoid loss of information from one buffer to another. However, PD has not taken full advantage of such methodologies.

Similarly to the SI and electrical validation realm, PD designers are looking for the best power channel's recipe capable to maintain its voltage level within expected ratings

under any loading circumstance. PD engineers typically require complex and detailed PDN simulation models to predict with sufficient accuracy the power channel's behavior, which makes simulation very computationally intensive, taking up to several days to obtain a PDN behavior.

From the above perspective, classical parametric sweeps and exhaustive enumeration are usually prohibitive. Here we propose using advanced DoE techniques, such as fractional factorial design (FFD) [9], Taguchi, etc., that can reduce significantly the amount of simulations needed, enabling PD engineers to efficiently identify the most impactful variables within the PDN. In DoE, the objective is to efficiently obtain a behavioral model for a certain output of interest, such it describes with sufficient accuracy the actual system's behavior. This behavioral approximation is typically implemented by a linear regression model

$$y(x) = \beta_0 + \beta_1 x_1 + \beta_2 x_2 + \beta_{12} x_1 x_2 + \dots + \varepsilon \tag{1}$$

where y(x) is system's output of interest,  $\beta$ 's are parameters to be determined during the DoE analysis,  $x_1$ ,  $x_2$ , etc., are the model variables that represent the selected system factors A, B, etc., and  $\varepsilon$  is the statistical error. Variables  $x_1$  and  $x_2$  are defined in a coded scale from -1 to +1 (low and high corner levels, respectively, for A and B), and  $x_1x_2$  represents the interaction between  $x_1$  and  $x_2$ .

#### III. DOE FOR POWER DELIVERY: SIMULATION APPROACH

To illustrate our methodology, we select a similar VR design to that one in [10] as the test vehicle to meet some voltage requirements: silicon's  $V_{\min} = 1.5$  V and  $V_{\max} = 2$  V, under any loading condition (di/dt).

Based on the VR design described in [10], parameters investigated in the simulation are given in Table I. We consider not only intrinsic VR compensation parameters but also some VR-external factors. For the first set, we focus our study on the proportional-integral-derivative (PID) controller's variables ( $k_i$ ,  $k_d$ ,  $k_p$ ), non-linear coefficients (NL-C), adaptive transient response (ATR), and auto-phasing schemes enabling and disabling VR's phases at some point in time ( $A_{Ph}$ ). On the second set we consider the quantity of bulk capacitors (BlkC) and the slew rate (SR) (here defined as the di/dt slope of the

TABLE I. Variables used to Build the FFD for Simulation Scenario

| Factor      | Equivalent Variable | (-1) | (+1) |

|-------------|---------------------|------|------|

| $A = (x_1)$ | $k_p$               | 100  | 250  |

| $B=(x_2)$   | $k_d$               | 250  | 450  |

| $C = (x_3)$ | $k_i$               | 100  | 250  |

| $D=(x_4)$   | $k_{fp}$            | 100  | 250  |

| $E=(x_5)$   | $A_{Ph}$            | no   | yes  |

| $F = (x_6)$ | NL-C                | no   | yes  |

| $G=(x_7)$   | ATR                 | no   | yes  |

| $H = (x_8)$ | BlkC                | 29%  | 100% |

| $J = (x_9)$ | SR (1-1000 A/µs)    | slow | fast |

transition from minimum current  $(I_{\min})$  to maximum current  $(I_{\max})$ ).

From Table I, there are nine factors to investigate, requiring a total of  $2^9 = 512$  simulations to find system's most significant factors. However, we use the FFD technique to reduce the number of simulations by "confounding" some of these factors.

Returning to our simulation's test bench scenario, we selected a  $2_{IJ}^{(9-4)} = 32$  experiments. We use resolution IV since it suitable for designs in which none of the main effects is an alias of another main effect or neither two factor interactions, but two factor interactions are aliases between them. Typically, it receives the name of "confusion of factors". Additionally, we use a factorial  $2^{(9-4)}$  because only five of the main factors are not confounded, and they correspond to Yates order for generating the test bench, while the remaining four factors are generated by the following confounded factors [9]:  $F = \pm BCDE$ ,  $G = \pm ACDE$ ,  $H = \pm ABDE$ , and  $J = \pm ABCE$ .

We use only time domain simulations in SIMetrix/Simplis<sup>2</sup> simulator to obtain test bench results under different VR and PD settings. Once results are collected, an analysis of variance (ANOVA) is performed to get some linear regression equations at the output of interest including its effects. The, from Pareto's analysis, it is possible to identify what variables are more important and hence simplify the equations obtained from ANOVA, yielding

$$V_{\min} \approx 0.960 + 0.001722x_2 \tag{2}$$

$$V_{\text{max}} \approx 2.791 - 0.0026x_2 - 0.0806x_8 \tag{3}$$

It is interesting to note that both model equations are depending on a derivative parameter ( $x_2 = k_d$ ), while  $V_{\text{max}}$  adds one more dependency with the quantity of bulk capacitors ( $x_8 = BlkC$ ).

#### IV. DOE FOR POWER DELIVERY: PHYSICAL APPROACH

Based on our findings obtained in Section III, a laboratory verification with the same PD design on a physical platform implementation is conducted to validate if the dependencies are the same. Since the physical VR module has more factors available for configuration, we focus our interest on those factors similar to the ones used in the simulation approach. Table II shows the codification for each factor.

Following exactly the same DoE procedure used in Section II, the resulting model equations describing system's behavior for Vmin and Vmax are:

$$V_{\min} \approx 1.3676 + 0.001826x_8 \tag{4}$$

$$V_{\text{max}} \approx 2.019 - 0.000047x_1 - 0.000297x_2 \tag{5}$$

<sup>&</sup>lt;sup>2</sup>SIMetrix/Simplis 7.20e (x64), Copyright © 2014 Simplis Technologies Ltd, 78 Chapel Street, Thatcham, Berkshire, RG18 4QN, UK, http://www.simetrix.co.uk/site/index.html

TABLE II. VARIABLES USED TO BUILD THE FFD FOR PHYSICAL IMPLEMENTATION

| Factor         | Equivalent Variable | (-1) | (+1) |

|----------------|---------------------|------|------|

| $A=(x_1)$      | $k_p$               | 100  | 250  |

| $B=(x_2)$      | $k_d$               | 250  | 450  |

| $C = (x_3)$    | $k_i$               | 100  | 250  |

| $D=(x_4)$      | $k_{fp}$            | 100  | 250  |

| $E=(x_5)$      | $ATR_{h1}$          | no   | yes  |

| $F = (x_6)$    | $ATR_{h2}$          | no   | yes  |

| $G=(x_7)$      | $ATR_{\_kp}$        | 0    | 56   |

| $H = (x_8)$    | $K_{j\_atrl}$       | 0    | 56   |

| $J=(x_9)$      | BlkC                | 29%  | 100% |

| $K = (x_{10})$ | SR (1-1000 A/μs)    | slow | fast |

where  $x_8 = k_{j\_atrl}$  is one of the non-linear factors, while from PID's side, some compensation factors like  $x_1 = k_p$  and  $x_2 = k_d$  resulted meaningful. It should be highlighted that the quantity of bulk capacitors is not too relevant among the factors of the physical implementation. This fact indicates that it would be possible to look into a favorable scenario that reduces the quantity of capacitors needed. To validate that, we expanded our model to incorporate this additional factor, as follows

$$V_{\text{min}} \approx 1.3676 + 0.001826x_8 + 0.0198e^{-6}x_9$$

(6)

$$V_{\text{max}} \approx 2.019 - 0.000047x_1 - 0.000297x_2 + 0.0091e^{-6}x_9$$

(7)

It is seen that this new DoE model is now dependent on the number of bulk capacitors,  $x_9$ .

#### V. SYSTEM OPTIMIZATION: SIMULATION AND LABORATORY

In the previous two sections we described the methodology to find the most significant factors of a PD system for both scenarios: simulation and its physical implementation. As it is observed that there are some coincidences and discrepancies on the model equations obtained from the simulation and laboratory measurements.

Both scenarios indicate that a good PID compensation recipe is needed ( $k_{\rm p}$  and  $k_{\rm d}$  resulted significant factors), while the laboratory approach added one more non-linear parameter that needs fine tuning ( $k_{\rm j\_atrl}$ ). Also, in the case of the laboratory, the quantity of bulk capacitors was initially not too relevant, indicating a great opportunity to reduce costs. We adjusted our DoE linear regression model to include bulk capacitors as one more factor to consider in the physical PD optimization.

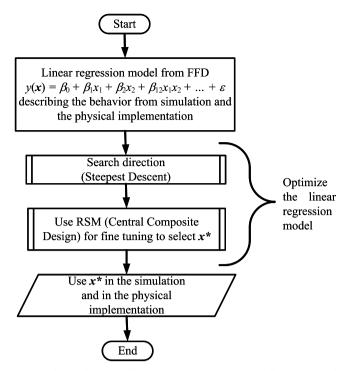

To optimize power delivery's system response from simulation and from the laboratory, we solve an optimization problem that minimizes a suitable objective function u(x) with respect to variables x, exploiting our response surface model y(x) [9] (see flow diagram in Fig. 1), as follows:

$$\mathbf{x}^* = arg \, min_x \, u(\mathbf{x}) \tag{8}$$

Fig. 1. Flow diagram illustrating the sequence followed in the implementation of RSM optimization technique.

$$u(x) = [V_{\min} - y(x)] + [y(x) - V_{\max}]$$

(9)

Central composite design (CCD) [9] is one of various RSM techniques. CCD consists on a factorial design  $2^k$  or a FFD with  $n_F$  runs,  $2^k$  axial runs or star and  $n_c$  central runs. The fundamental deployment of a CCD is based on sequential experimentation, *i.e.*, it is used a  $2^k$  design to adjust the first order model. Since such model usually presents lack of adjustment, then, axial runs are added to incorporate some quadratic terms in the model. In this work we selected CCD as the method to develop the RSM models.

From Fig. 1, the first optimization step uses steepest descent to establish the direction that maximizes the system. Finally, the second step consists on applying the CCD technique to enhance the model around the optimal solution.

Table III, summarizes results before and after optimization for both scenarios (PD simulation and physical PD implementation). As it is observed in Table III, physical power delivery implementation needs 14% more capacitors than the simulation, although, still making feasible a 29% reduction of capacitors needed. Both scenarios (simulation and physical implementation) are evaluated under fast SR conditions before and after optimization.

From Table III, it is clear that silicon's  $V_{\rm min}$  and  $V_{\rm max}$  requirements are met, although, we need to ensure these results are valid from the VR's perspective. To ensure whether these results meet VR's voltage boundaries, it is needed to estimate maximum and minimum VR output voltage allowed.

The following equations estimate these requirements:

TABLE III. DOE RESULTING VOLTAGE LEVELS AND PEAK TO PEAK COMPARISON FOR SIMULATION AND PHYSICAL IMPLEMENTATION SCENARIOS BEFORE AND AFTER OPTIMIZATION

| Environment's s | scenario | $k_p$ | $k_d$ | $kj_{\_atrl}$ | BlkC | SR   | $V_{min}\left(\mathbf{V}\right)$ | $V_{max}\left(\mathbf{V}\right)$ | Peak to peak (mV) |

|-----------------|----------|-------|-------|---------------|------|------|----------------------------------|----------------------------------|-------------------|

| Simulation      | before   | 135   | 330   | N/A           | 100% | fast | 1.64                             | 1.85                             | 209.95            |

|                 | after    | 135   | 275   | N/A           | 57%  | fast | 1.57                             | 1.89                             | 313.80            |

| Laboratory      | before   | 180   | 420   | 0             | 100% | fast | 1.62                             | 1.82                             | 196.80            |

|                 | after    | 124   | 450   | 38.5          | 71%  | fast | 1.58                             | 1.88                             | 300.00            |

$$VR_{\text{minb}} = V_{\text{nom}} - (I_{\text{max}} * LL) - VR_{\text{AC\_DC}}$$

(10)

$$VR_{\text{maxb}} = V_{\text{nom}} + (I_{\text{max}} * LL) + VR_{\text{AC DC}}$$

(11)

where  $VR_{\rm minb}$  and  $VR_{\rm maxb}$  are VR output voltage boundaries,  $V_{\rm nom}$  is the nominal voltage given for the power rail's channel, Imax is the maximum current load, LL is the load line or equivalent resistance seeing by the system³, and  $VR_{\rm AC\_DC}$  is the AC plus DC tolerance the VR can support, for this particular case  $\pm 22$  mV. Using (11) and (12), the calculated output voltage boundaries are  $VR_{\rm minb} = 1.58$  V and  $VR_{\rm maxb} = 1.98$  V. Hence, from Table III, it is observed that the optimization results are marginally meeting minimum and maximum VR's voltage boundaries.

#### VI. CONCLUSION

DoE proved to be an effective technique to find the most significant factors for PD analysis and design, as well as to perform PDN optimization. Our simulations and physical laboratory measurements showed sufficiently good agreement for the optimized PDN. With this methodology, it is possible to reduce costs, since, from our physical platform implementation it was possible to remove 29% of the capacitors at the expense of a finding better VR's tuning recipe. As further step, a detailed DoE study on the frequency domain is desirable to ensure acceptable VR's stability criteria and bandwidth. more computationally efficient optimization techniques, such as those based on space mapping approaches, will be addressed in future work to enhance our power delivery design process.

# ACKNOWLEDGEMENT

This work was supported in part by CONACYT (*Consejo Nacional de Ciencia y Tecnología*, Mexican Government) through a scholarship granted to F. J. Leal-Romo.

We thank our colleagues from Intel Corp. Victor Lopez, Jorge Velazquez, and Ivan Méndez, who greatly assisted this research.

#### REFERENCES

- L. D. Smith, R. E. Anderson, D. W. Forehand, T. J. Pelc, and T. Roy, "Power distribution system design methodology and capacitor selection for modern CMOS technology," *IEEE Trans. Adv. Packag.*, vol. 22, no. 3, pp. 284-291, Aug. 1999.

- [2] P. Siming, B. Achkir, "Optimization of power delivery network design for multiple supply voltages," in *IEEE Int. Symp. Electromag. Comp.*, Denver, CO, Aug. 2013, pp. 333-337.

- [3] T. Rahal-Arabi, G. Taylor, M. Ma, and C. Webb, "Design and validation of the Pentium®III and Pentium®4 processors power delivery," in *IEEE Symp. VLSI Circuits Digest of Tech. Papers*, Honolulu, HI, June 2002, pp. 220-223.

- [4] K. S. Oh and X. C. Yuan, High-Speed Signaling: Jitter Modeling, Analysis, and Budgeting. Westford, MA: Prentice Hall, 2011.

- [5] M. Swaminathan, C. Daehyun, S. Grivet-Talocia, K. Bharath, V. Laddha, and X. Jianyong, "Designing and modeling for power integrity," *IEEE Trans. Electromag. Compat.*, vol. 52, no. 2, pp. 288-310, May 2010.

- [6] A. Norman, D. Shykind, M. Falconer and K. Ruffer, "Application of design of experiments (DOE) methods to high-speed interconnect validation," in *IEEE Conf. on Electrical Perf. of Electronic Packag. and Systems*, Princeton, NJ, Oct. 2003, pp. 15-18.

- [7] E. Matoglu, N. Pham, D. N. de Araujo, M. Cases and M. Swaminathan, "Statistical signal integrity analysis and diagnosis methodology for highspeed systems," *IEEE Trans. Adv. Packag.*, vol. 27, no. 4, pp. 611-629, Nov. 2004.

- [8] HCL. (2012). Signal Integrity Analysis Using Statistical Methods [Online]. Available: http://www.hcltech.com/white-papers/engineering-rd-services/signal-integrity-analysis-using-statistical-methods.

- [9] D. C. Montgomery, Design and Analysis of Experiments. 8th Edition, John Wiley & Sons, 2012.

- W. Xu, J. Fang, J. He, and T. Kim, "Switching voltage regulator modeling and its applications in power delivery design," in *IEEE Int. Symp. Electromag. Comp.*, Raleigh, NC, Aug. 2014, pp. 855-860.

$<sup>^3</sup>$  The specific values of  $V_{\rm nom},$   $I_{\rm max},$  and LL, are proprietary information from Intel Corporation.