# **Evaluation of Metal-Organic Frameworks in Electronic Devices for Gas Sensing**

der Fakultät für Elektrotechnik und Informatik der Gottfried Wilhelm Leibniz Universität Hannover zur Erlangung des akademischen Grades Doktor der Naturwissenschaften

Dr. rer. nat.

genehmigte Dissertation von

### M.Sc. Liz Margarita Montañez Huamán

Geboren am 29.01.1989 in Huancayo (Perú)

Hannover 2019

1. Referenten: Prof. Dr. H. Jörg Osten

2. Referenten: Prof. Dr. J. Caro

Tag der Promotion:22.08.2019

To my family Basilio Montañez, Rufina Huamán, Kevin, Geraldine, Nancy and Edith

# Kurzfassung

Die Integration von nanoporösen Metall-organischen Gerüstverbindungen (engl. metalorganic frameworks, MOFs) in elektronischen Bauelementen wie z.B. Kondensatoren, Transistoren und Memristoren, ermöglicht durch Adsorption von Gastmolekülen eine Anwendung in der Sensorik. Dünne MOF-Schichten in einem Metall-Isolator-Halbleiter (engl. metal-insulator-semiconductor, MIS) als Kondensatorenstruktur erlauben auf Grund niedriger Spannungen konkrete Anwendungen. MIS-Kondensatoren bieten auch eine Analyse der Grenzflächendefekte wie z.B. Grenzflächenzuständen (interface traps) und Ladungen nahe der Grenzfläche (border traps). Elektronische Bauteile erfordern eine geringe Konzentration von Grenzflächendefekten, um so Schwellwertinstabilitäten zu verkleinern. Diese Arbeit liefert eine detaillierte Untersuchung von Ladungen und Defekten in MOFbasierten MIS-Kondensatoren durch Impedanzspektroskopie. Der MOF Cu<sub>3</sub>(BTC)<sub>2</sub> wurde direkt auf einer Si- und auf einer SiO2-Oberfläche durch Layer-by-layer-Methoden aufgebracht. Die Schichtdicke konnte durch die Variation der Sprüh- bzw. Tauchzyklen leicht eingestellt werden. Des Weiteren wurden Si/SiO2/Al-MIS-Kondensatoren zum Vergleich untersucht. Das erfolgreiche Wachstum von ultra-dünnen Cu<sub>3</sub>(BTC)<sub>2</sub>-Schichten auf Si-Substraten wurde durch Experimente mit Röntgenbeugung (engl. X-ray diffraction, XRD) verifiziert. Die Funktion von MOFs in MIS-Kondensatoren wurde mit Kapazitäts-Spannungs (C-V) und Leitfähigkeits-Spannungs (G-V) Messungen bei verschiedenen Frequenzen und Temperaturen untersucht.

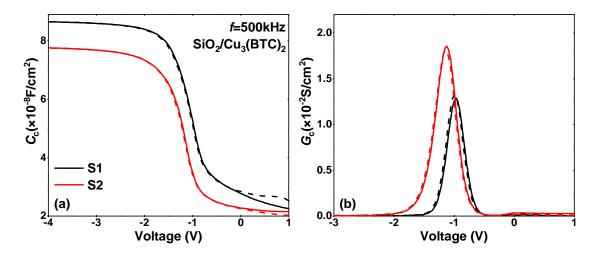

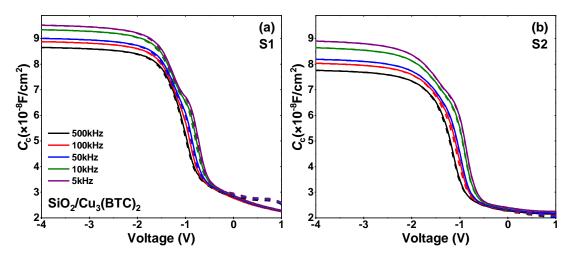

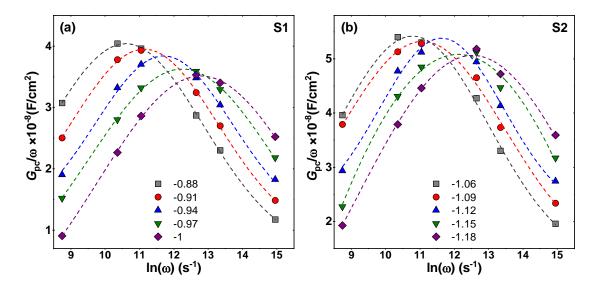

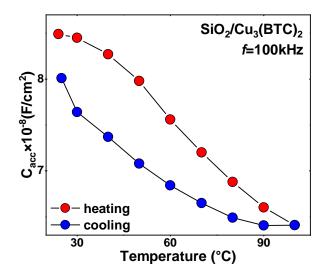

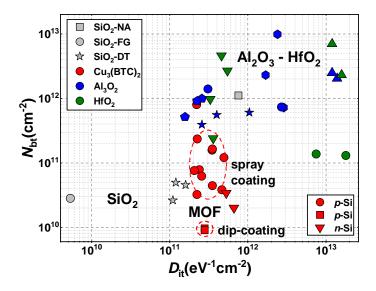

Die Ergebnisse belegen positive und negative feste Ladungen in den dielektrischen  $Cu_3(BTC)_2$ -Schichten, wie auch das Vorhandensein von Ladungen an/in der Grenzschicht, die eine Hysterese in den *C-V*-Messungen verursachen. Hinweise auf Grenzflächenzustände können durch einen Peak in der *G-V*-Messung beobachtet werden. Die Analyse der Daten beweist, dass MOF-Schichten - hergestellt ohne Ultraschall (US) - eine relativ geringe Dichte von Ladungen an der Grenzschicht (~10<sup>11</sup>cm<sup>-2</sup>) und geringe Grenzflächenzustände (~10<sup>11</sup>eV<sup>-1</sup>cm<sup>-2</sup>) bei einer Ansprechzeit von wenigen µs besitzen. Temperaturabhängige Messungen zeigten eine Degradation der elektrischen Eigenschaften von MOFs. Durch zusätzliche US-Behandlungen während der Beschichtung verringerte sich die ohnehin geringe Dichte von Ladungen nahe der Grenzschicht deutlich, die der Grenzflächenzustände blieb unverändert. Außerdem sind die Schichten thermisch stabiler und erreichen bei Abkühlung nahezu ihren Anfangszustand. Die experimentellen Ergebnisse belegen, dass MOF-basierte Kondensatoren eine Grenzflächenqualität vergleichbar mit anorganischen Materialien besitzen und sie für Anwendungen in der Sensorik nutzbar sind.

## Abstract

Integrating nano-porous metal-organic frameworks (MOFs) in electronic devices such as capacitors, transistor or memristor enables sensing applications for a wide variety of guest molecules. Particularly, the incorporation of thin MOF films in metal-insulatorsemiconductor (MIS) capacitor structures allows real-life applications because of its low voltage operation. Additionally, MIS capacitors offer a thorough study of interfacial defects such as interface traps and border traps distributed within the device. In electronic devices, a low concentration of interfacial defects is required to avoid threshold-voltage instabilities. This fact guarantees good stability and performance of electrical devices. This research work provides detailed investigation about charges and defects in MOFs-based MIS capacitors by impedance spectroscopy. Cu<sub>3</sub>(BTC)<sub>2</sub> was coated directly on silicon, and on thermally grown silicon dioxide surfaces in a layer-by-layer fashion. The layer thickness was easily handled by varying the number of spray cycles in the coating process. In addition, Si/SiO<sub>2</sub>/Al MIS capacitors were investigated for comparison reasons. The successful growth of ultra-thin Cu<sub>3</sub>(BTC)<sub>2</sub> films on silicon substrates was verified via X-ray diffraction (XRD) experiments. The function of MOFs within MIS capacitors was investigated via capacitance-voltage (C-V) and conductance-voltage (G-V) characteristics measured at different frequencies and temperatures.

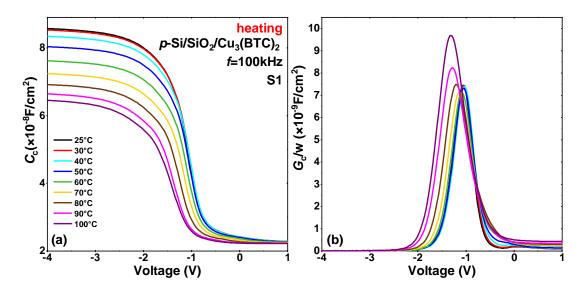

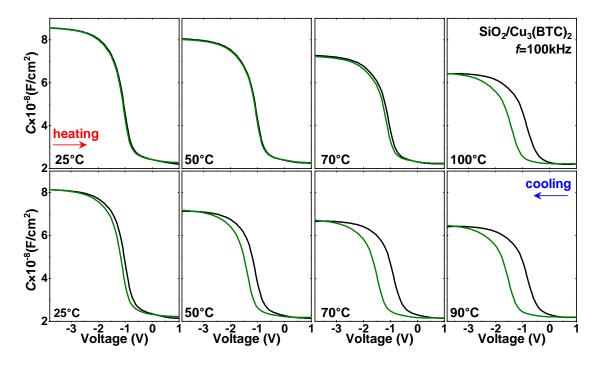

The results show evidence of positive and negative fixed charges in the  $Cu_3(BTC)_2$  dielectric layer as well as of the presence of border traps which cause hysteresis in the *C-V* characteristics. Evidence of interface traps is directly observed by the peak on the conductance curve. Analysis of the data demonstrates that ultra-thin  $Cu_3(BTC)_2$  films prepared without ultrasonication exhibit a relatively low density of border traps (~10<sup>11</sup>cm<sup>-2</sup>), interface traps (~10<sup>11</sup>eV<sup>-1</sup>cm<sup>-2</sup>) and time response in the order of  $\mu$ s. Temperature-dependent measurements degrade the electrical quality of the MOFs. The addition of ultrasonication steps on the coating process decreases considerably the density of border traps. Additionally, the layers are more stable under heating experiments, and after cooling they almost recover the initial state. The experimental results show that MOF-based capacitors exhibit interface quality comparable to inorganic materials, making them suitable for sensing applications.

Keywords: interfacial defects, metal-insulator-semiconductor capacitor,  $Cu_3(BTC)_2$  metal-organic framework

$\label{eq:schlagworter:Grenzflächendefekte, Metall-Isolator-Halbleiter-Kondensator, Cu_3(BTC)_2 \\ Metall-organische Gerüstverbindung$

# Contents

| Acknowledgments |                                                                             |  |

|-----------------|-----------------------------------------------------------------------------|--|

| Al              | obreviationsii                                                              |  |

| No              | otationiii                                                                  |  |

| 1               | Introduction                                                                |  |

|                 | 1.1 Metal-Organic Frameworks in Electronic Devices 1                        |  |

|                 | 1.2 Metal-Insulator-Semiconductor Capacitors as Sensors                     |  |

|                 | 1.3 Motivation and Structure of the Thesis                                  |  |

| 2               | Basics                                                                      |  |

|                 | 2.1 Metal-Insulator-Semiconductor (MIS) Capacitor                           |  |

|                 | 2.1.1 Ideal MIS Capacitor                                                   |  |

|                 | 2.1.2 Real MIS Capacitor12                                                  |  |

|                 | 2.2 Metal-Organic Frameworks (MOFs) 18                                      |  |

|                 | 2.2.1 Properties of Cu <sub>3</sub> (BTC) <sub>2</sub>                      |  |

|                 | 2.2.2 Integration of MOFs in Electronic Devices                             |  |

| 3               | Experimental Details                                                        |  |

|                 | 3.1 Device Processing                                                       |  |

|                 | 3.1.1 Thermal Oxidation                                                     |  |

|                 | 3.1.2 Metallization                                                         |  |

|                 | 3.1.2 Spray of Thin Cu <sub>3</sub> (BTC) <sub>2</sub> Layers               |  |

|                 | 3.2 Fabrication of SiO <sub>2</sub> -Based MIS Capacitors                   |  |

|                 | 3.3 Fabrication of Cu <sub>3</sub> (BTC) <sub>2</sub> -Based MIS Capacitors |  |

|                 | 3.4 Characterization Techniques                                             |  |

|                 | 3.4.1 Structural and Morphological Characterization                         |  |

|                 | 3.4.2 Electrical Characterization                                           |  |

| 4<br>Do | Methods for Characterizing Interface and Border Trap Density in M<br>evices                                                    |    |

|---------|--------------------------------------------------------------------------------------------------------------------------------|----|

| De      |                                                                                                                                |    |

|         | 4.1 Series Resistance Correction.                                                                                              |    |

|         | 4.2 Determination of the Dielectric Capacitance                                                                                |    |

|         | 4.3 Determination of Interface Trap Density                                                                                    |    |

|         | 4.3.1 Conductance Method                                                                                                       |    |

|         | 4.3.2 Hill-Coleman Method                                                                                                      |    |

|         | 4.4 Determination of Border Trap Density                                                                                       | 42 |

| 5       | Effect of Trimesic Acid (TMA) in Si/SiO <sub>2</sub> MIS Capacitors                                                            | 44 |

|         | 5.1 Introduction                                                                                                               | 44 |

|         | 5.2 C-V and G-V Characteristics of Si/SiO <sub>2</sub> MIS Capacitors                                                          | 45 |

|         | 5.2.1 Impact of TMA Treatments and Forming Gas Annealing                                                                       | 45 |

|         | 5.2.2 Frequency Effects                                                                                                        |    |

|         | 5.3 Summary                                                                                                                    | 50 |

| e<br>Me | ethod                                                                                                                          | 53 |

|         | 6.1 Introduction                                                                                                               |    |

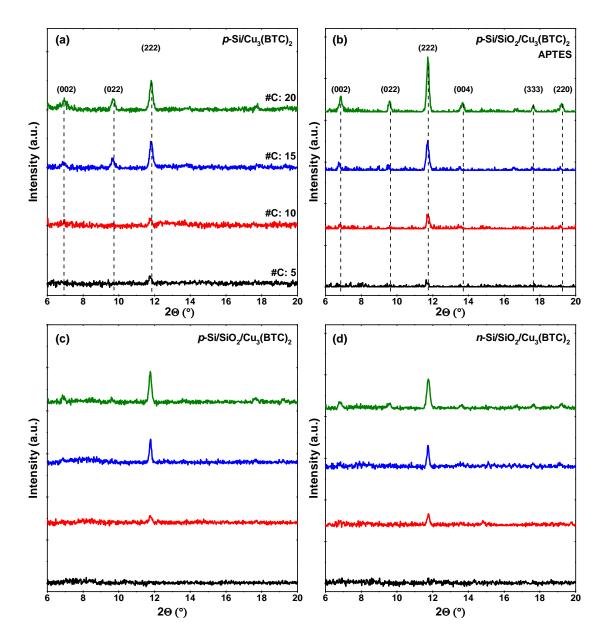

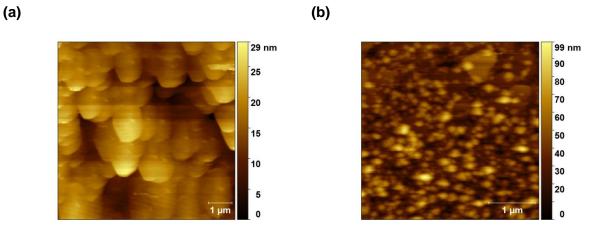

|         | 6.2 Structural and Morphological Properties of Cu <sub>3</sub> (BTC) <sub>2</sub> on Si and SiO <sub>2</sub> Surfaces          |    |

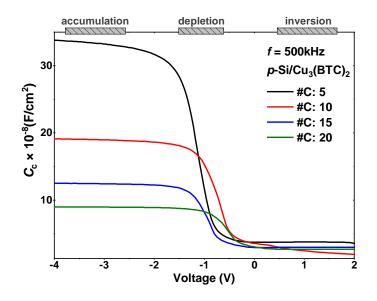

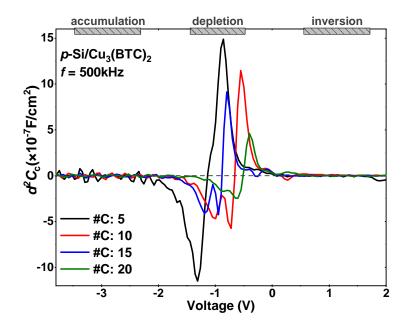

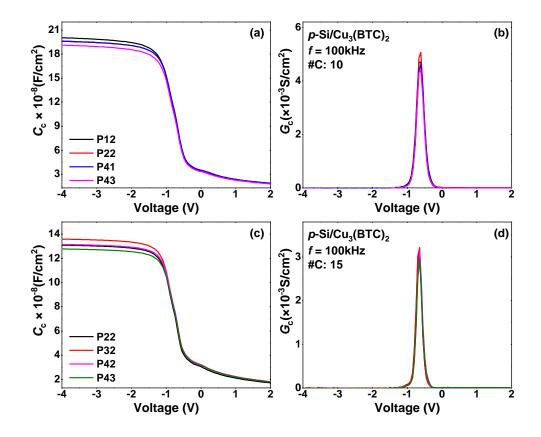

|         | 6.3. Impedance Characteristics of $Cu_3(BTC)_2$ on <i>p</i> -type Silicon                                                      |    |

|         | 6.3.1 Effect of Layer Thickness                                                                                                |    |

|         | 6.3.2 Effect of Frequency                                                                                                      |    |

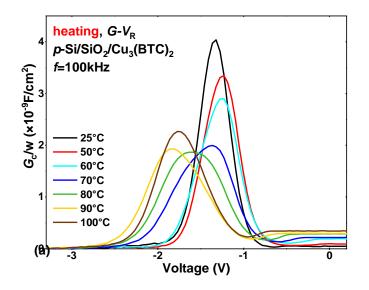

|         | 6.3.3 Effect of Temperature                                                                                                    |    |

|         | 6.4. Impedance Characteristics of $Cu_3(BTC)_2$ on <i>n</i> -type Silicon                                                      |    |

|         | 6.5 Summary                                                                                                                    | 76 |

| 7<br>Ar | Ultra-Thin Cu <sub>3</sub> (BTC) <sub>2</sub> Films Based MIS Capacitors: Layer-by-Laye<br>pproach Assisted by Ultrasonication |    |

| μ       | 7.1 Introduction                                                                                                               |    |

|         |                                                                                                                                |    |

|         | 7.2 Structural and Morphological Properties of $Cu_3(BTC)_2$ -Based MIS Capacitors                                             |    |

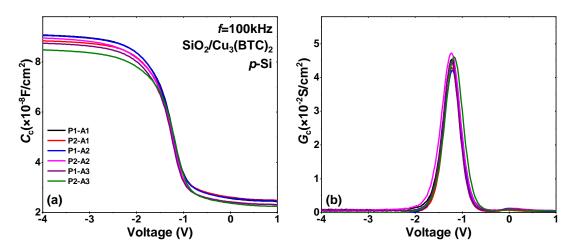

|         | 7.3 Impedance Characteristics of $Cu_3(BTC)_2$ -Based MIS Capacitors                                                           |    |

|         | 7.3.1 C-V and G-V Characteristics: Effect of Frequency                                                                         |    |

|         | 7.3.2 C-V and G-V Characteristics: Effect of Temperature                                                                       |    |

|         | 7.4 Summary                                                                                                                    | 8/ |

| 8  | Conclusions        | . 88 |

|----|--------------------|------|

| Aj | ppendix            | . 91 |

| Bi | bliography         | . 94 |

| Li | st of Figures      | 106  |

| Li | st of Tables       | 111  |

| Li | st of Publications | 112  |

| Cu | urriculum Vitae    | 115  |

# Acknowledgments

First of all, I would like to thanks to my supervisors Prof. Dr. H. Jörg Osten and Prof. Dr. J. Caro for giving me the opportunity to perform my Ph.D. thesis at the Institut für Materialien und Bauelemente der Elektronik (MBE) in Hannover and for providing me support and motivation during the exciting and challenge period that I spent working on my Ph.D. topic. I would like to thanks to Prof. Wietler, who guided me during the first months at the MBE institute. Special thanks to Guido Glowatzki and Raymond Zieseniß for technical support with the fabrication of the capacitors. To my students Merve Cakmak and Ali Fawaz. To Dr.-Ing. Jan Krügener for correcting the thesis. Finally, thanks to all the members of the institute who support me with different experimenters: Prof. Dr. Robby Peibst, Prof. Dr. Andreas Fissel, Jan Schmidt, Yvo Barnscheidt, Philipp Gribisch, Gustav Wetzel, Andrea Lissel, Hartmut Schwarz, Detlef Zech, Bernd Koch, and Sabina Galle.

I am very thankful for the support of all our cooperation partners: To Ina Strauß, for the coating of the MOFs layers and XRD-measurements at the Institut für Physikalische Chemie und Elektrochemie (LUH). To Kai Müller and Dr. Lars Heinke for the coating of the MOFs layers and XRD-measurements at the Institut für Funktionelle Grenzflächen (IFG) in Karlsruhe. To Malte Schäfer for the construction of the MOF structures depicted in chapter 2. I would like to thanks to Prof. Stefan Zimmermann for accepting to be a member of the committee.

I gratefully acknowledge the funding that I received from the Georg-Christoph-Lichtenberg-Scholarships of the Hannover School of Nanotechnology (HSN). Thanks to the Director Dr. Fritz Wischeler and Ms. Christine Sabisch for the good organization of the Ph.D. program.

Last but not least, I would like to thanks to all people that make me feel at home in Germany, to Peter and Reiner Fischer, Adelheid Gottschlich, Amalia Gonzales, and Max Correa.

# Abbreviations

| AFM                                                           | atomic force microscopy                                                                                                                                                                                                                                                 |  |  |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| APTES                                                         | aminopropyltriethoxysilane                                                                                                                                                                                                                                              |  |  |

| BDC                                                           | 1,4-benzenedicarboxylate acid                                                                                                                                                                                                                                           |  |  |

| BET                                                           | Brunauer-Emmett-Teller                                                                                                                                                                                                                                                  |  |  |

| BTC                                                           | 1,3,5 benzenetricarboxylate acid                                                                                                                                                                                                                                        |  |  |

| CV                                                            | capacitance-voltage                                                                                                                                                                                                                                                     |  |  |

| ESR                                                           | electron spin resonance                                                                                                                                                                                                                                                 |  |  |

| FET                                                           | field-effect transistor                                                                                                                                                                                                                                                 |  |  |

| FG                                                            | forming gas annealing                                                                                                                                                                                                                                                   |  |  |

| GV                                                            | conductance-voltage                                                                                                                                                                                                                                                     |  |  |

| HFCV                                                          | high-frequency capacitance-voltage                                                                                                                                                                                                                                      |  |  |

| OFET                                                          | organic field-effect transistors                                                                                                                                                                                                                                        |  |  |

| FWHM                                                          | full width at half maximum                                                                                                                                                                                                                                              |  |  |

| HID                                                           | hydrogen induced drift                                                                                                                                                                                                                                                  |  |  |

| HKUST-1                                                       | Hong Kong University of Science and Technology                                                                                                                                                                                                                          |  |  |

| IRMOF                                                         | isoreticular metal framework                                                                                                                                                                                                                                            |  |  |

| LBL                                                           | layer-by-layer                                                                                                                                                                                                                                                          |  |  |

| LFCV                                                          | low-frequency capacitance-voltage                                                                                                                                                                                                                                       |  |  |

| MIL                                                           |                                                                                                                                                                                                                                                                         |  |  |

| MIL                                                           | Materials of Institute Lavoisier                                                                                                                                                                                                                                        |  |  |

| MIS                                                           | Materials of Institute Lavoisier<br>metal-insulator-semiconductor                                                                                                                                                                                                       |  |  |

|                                                               |                                                                                                                                                                                                                                                                         |  |  |

| MIS                                                           | metal-insulator-semiconductor                                                                                                                                                                                                                                           |  |  |

| MIS<br>MOF                                                    | metal-insulator-semiconductor<br>metal-organic framework                                                                                                                                                                                                                |  |  |

| MIS<br>MOF<br>NA                                              | metal-insulator-semiconductor<br>metal-organic framework<br>non-annealed sample                                                                                                                                                                                         |  |  |

| MIS<br>MOF<br>NA<br>NDC                                       | metal-insulator-semiconductor<br>metal-organic framework<br>non-annealed sample<br>1,4-naphthalenedicarboxylate acid                                                                                                                                                    |  |  |

| MIS<br>MOF<br>NA<br>NDC<br>RTP                                | metal-insulator-semiconductor<br>metal-organic framework<br>non-annealed sample<br>1,4-naphthalenedicarboxylate acid<br>rapid thermal annealing processing                                                                                                              |  |  |

| MIS<br>MOF<br>NA<br>NDC<br>RTP<br>SAM                         | metal-insulator-semiconductor<br>metal-organic framework<br>non-annealed sample<br>1,4-naphthalenedicarboxylate acid<br>rapid thermal annealing processing<br>self-assembly monolayer                                                                                   |  |  |

| MIS<br>MOF<br>NA<br>NDC<br>RTP<br>SAM<br>SURMOF               | metal-insulator-semiconductor<br>metal-organic framework<br>non-annealed sample<br>1,4-naphthalenedicarboxylate acid<br>rapid thermal annealing processing<br>self-assembly monolayer<br>surface-mounted metal-organic framework                                        |  |  |

| MIS<br>MOF<br>NA<br>NDC<br>RTP<br>SAM<br>SURMOF<br>TMA        | metal-insulator-semiconductor<br>metal-organic framework<br>non-annealed sample<br>1,4-naphthalenedicarboxylate acid<br>rapid thermal annealing processing<br>self-assembly monolayer<br>surface-mounted metal-organic framework<br>trimesic acid                       |  |  |

| MIS<br>MOF<br>NA<br>NDC<br>RTP<br>SAM<br>SURMOF<br>TMA<br>UIO | metal-insulator-semiconductor<br>metal-organic framework<br>non-annealed sample<br>1,4-naphthalenedicarboxylate acid<br>rapid thermal annealing processing<br>self-assembly monolayer<br>surface-mounted metal-organic framework<br>trimesic acid<br>University of Oslo |  |  |

# Notation

| Α                  | area of the metal contact, cm <sup>2</sup>                             |

|--------------------|------------------------------------------------------------------------|

| С                  | capacitance, F/cm <sup>2</sup>                                         |

| $C_{ m A}$         | accumulation capacitance, F/cm <sup>2</sup>                            |

| $C_{ m c}$         | corrected capacitance, F/cm <sup>2</sup>                               |

| $C_{d}$            | dielectric capacitance, F/cm <sup>2</sup>                              |

| $C_{ m F}$         | capacitance in forward direction, F/cm <sup>2</sup>                    |

| $C_{ m HF}$        | high-frequency capacitance, F/cm <sup>2</sup>                          |

| $C_{\mathrm{it}}$  | interface trap capacitance, F/cm <sup>2</sup>                          |

| $C_{ m LF}$        | low-frequency capacitance, F/cm <sup>2</sup>                           |

| $C_{ m m}$         | measured capacitance, F/cm <sup>2</sup>                                |

| $C_{ m ma}$        | measured capacitance in accumulation, F/cm <sup>2</sup>                |

| $C_{R}$            | capacitance in reverse direction, F/cm <sup>2</sup>                    |

| $C_{\rm s}$        | semiconductor capacitance, F/cm <sup>2</sup>                           |

| $C_{ m tot}$       | total capacitance, F/cm <sup>2</sup>                                   |

| $D_{ m it}$        | density of interface traps, eV <sup>-1</sup> cm <sup>-2</sup>          |

| Ε                  | trivalent silicon centers located at the Si/SiO <sub>2</sub> interface |

| <i>E</i> '         | center in SiO <sub>2</sub> associated with oxygen vacancies            |

| $E_{\rm c}$        | energy of conduction band-edge, eV                                     |

| $E_{ m g}$         | energy band gap, eV                                                    |

| $E_{ m i}$         | intrinsic level                                                        |

| $E_{ m v}$         | energy of valence band-edge, eV                                        |

| f                  | signal frequency, Hz                                                   |

| G                  | conductance, S/cm <sup>2</sup>                                         |

| $G_{ m c}$         | corrected conductance, S/cm <sup>2</sup>                               |

| $G_{ m cp}$        | Equivalent parallel conductance, S/cm <sup>2</sup>                     |

| $G_{ m m}$         | measured conductance, S/cm <sup>2</sup>                                |

| $G_{ m ma}$        | measured conductance in accumulation, S/cm <sup>2</sup>                |

| k                  | Boltzmann's constant, 1.3805×10 <sup>-23</sup> J/K                     |

| $L_{\rm D}$        | extrinsic Debye length, m                                              |

| $N_{ m A}$         | acceptor concentration in silicon, cm <sup>-3</sup>                    |

| $N_{ m bt}$        | density of border traps, cm <sup>-2</sup>                              |

| n <sub>i</sub>     | intrinsic carrier concentration in silicon, cm <sup>-3</sup>           |

| q                  | elementary charge, 1.6021×10 <sup>-19</sup> C                          |

| $Q_{ m bt}$        | border-trapped charges, cm <sup>-2</sup>                               |

| $Q_{\mathrm{fix}}$ | fixed charges, cm <sup>-2</sup>                                        |

| $Q_{ m in}$        | charges in inversion layer, Ccm <sup>-2</sup>                          |

| $Q_{ m it}$        | Interface-trapped charges, cm <sup>-2</sup>                            |

| $Q_{ m m}$         | charges in the metal, Ccm <sup>-2</sup>                                |

|                    | iii                                                                    |

| $Q_{ m mob}$       | mobile charges, cm <sup>-2</sup>                      |

|--------------------|-------------------------------------------------------|

| $Q_{ m ox, eff}$   | effective oxide charges, cm <sup>-3</sup>             |

| $Q_{ m ot}$        | oxide-trapped charges, cm <sup>-2</sup>               |

| $Q_{\rm s}$        | total charges in the semiconductor, Ccm <sup>-2</sup> |

| $Q_{ m sc}$        | space charge density                                  |

| R <sub>s</sub>     | series resistance, $\Omega$                           |

| $V_{ m FB}$        | flat-band voltage, V                                  |

| $V_{ m FB,exp}$    | experimental flat-band voltage, V                     |

| $V_{ m FB, theor}$ | theoretical flat-band voltage, V                      |

| $V_{ m g}$         | gate voltage, V                                       |

| W                  | angular frequency, s                                  |

| $W_{ m m}$         | surface depletion region, cm                          |

| Y <sub>it</sub>    | admittance of interface traps                         |

| Y <sub>ma</sub>    | admittance in accumulation                            |

| $Z_{\rm ma}$       | impedance in accumulation                             |

|                    |                                                       |

| З                    | permittivity of vacuum, $8.8542 \times 10^{-12}$ F/m |

|----------------------|------------------------------------------------------|

| <i>E</i> d           | permittivity of the dielectric material              |

| $\xi_s$              | electric field, V/cm                                 |

| χ                    | electron affinity, V                                 |

| χ'                   | effective electron affinity, V                       |

| $\Phi_{\mathrm{F}}$  | Fermi potential, V                                   |

| $\Phi_{\rm m}$       | work function of the metal, eV                       |

| $\Phi'_{\mathrm{m}}$ | effective work function of the metal, V              |

| $\Phi_{\rm s}$       | work function of the semiconductor, V                |

| $\Phi_{t}$           | surface potential, V                                 |

| $	au_{ m it}$        | response of interface traps, s                       |

| $\psi_{ m s}$        | band bending, V                                      |

|                      |                                                      |

## **1** Introduction

### **1.1 Metal-Organic Frameworks in Electronic Devices**

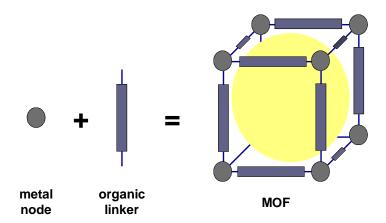

Metal-organic frameworks are porous hybrid materials composed of metal nodes that are connected by organic linker molecules. They exhibit extraordinary properties such as porosity, large surface area, and tailorable chemistry that can be tuned by adapting the functionality of its components. Because of these properties, MOFs are suitable for a wide variety of applications including gas storage [1], separation [2], sensing [3], catalysis [4], and drug delivery [5]. In the last years, the integration of MOFs as an integral component of electronic devices has received extensive attention [6,7]. The microelectronic industry requires the production of homogeneous thin films directly on substrates with controllable thickness, composition, and microstructure [6]. In order to attach thin MOF films on substrates, the deposition protocol of the conventional solvothermal process was modified [8], and new deposition techniques were developed [9,10]. Hermes et al. used the solvothermal synthesis to growth  $Zn_4O(BDC)_3$  with BDC=1,4-benzenedicarboxylate on Au(111) substrates functionalized by COOH-terminated self-assembly monolayer (SAM).  $Zn_4O(BDC)_3$  was grown with a layer thickness of ~5 µm and crystallites sizes between 100 nm to 500 nm [8]. By controlled layer-by-layer (LBL) synthesis, resulting in surfacemounted MOFs also referred to as SURMOFs, the layer thickness was considerably reduced to the nanometer scale [11]. Later, the chemical vapor deposition approach has emerged as a promising solvent-free synthesis which consists of two steps: first, the metal oxide is deposited on the substrate and then the substrate is exposed to a vapor-solid reaction [10].

Although significant progress has been made on the growth of thin MOF films on substrates, only a few reports address the integration of MOFs in electronic devices. For example, it was shown that ZIF-8 with ZIF=zeolitic imidazolate framework exhibits good adhesion to the support, elastic modulus higher than 36 GPa and low dielectric constant of  $2.33(\pm 0.05)$  at 100 kHz, therefore, this MOF is a promising candidate to separated copper interconnects on microelectronic chips [12]. The assembly of semiconducting or insulating MOFs in organic field-effect transistors (OFET) also has been investigated. Wu *et al.* fabricated the first microporous field-effect transistor using Ni<sub>3</sub>(2,3,6,7,10,11-hexaiminotriphenylene)<sub>2</sub> as the active channel material. The semiconducting MOF exhibits high hole mobility (~48.6 cm<sup>2</sup>V<sup>-</sup> <sup>1</sup>s<sup>-1</sup>) owing to its full charge delocalization [13]. Gu *et al.* coated Cu<sub>3</sub>(BTC)<sub>2</sub> with BTC=1,3,5

benzenetricarboxylate on silicon dioxide surfaces in order to improve the performance of the OFET by modifying the SiO<sub>2</sub> dielectric layer. Incorporation of  $Cu_3(BTC)_2$  in SiO<sub>2</sub>-based transistors improves the hole mobility and decrease the threshold voltage to values lower than 10 V [14]. The present research work reported the feasible integration of ultra-thin  $Cu_3(BTC)_2$  films within MIS capacitor structures and demonstrated that the MOF layer exhibits an interface quality comparable to inorganic materials [15,16].

### **1.2 Metal-Insulator-Semiconductor Capacitors as Sensors**

Sensors compatible with integrated circuits technology consist of MIS structures such as MIS capacitor or transistor. Gas sensitivity of these devices is measured as the change in the work function of the metal gate when a dipolar layer is formed at the metal/insulator interface [17,18]. Sensitivity of the devices under exposure to hydrogen gas consists of three steps: (1) dissociation of hydrogen molecules on the catalytic metal surface, (2) then hydrogen atoms diffuse toward the metal/insulator interface, and (3) the adsorbed hydrogen atoms are polarized giving rise a dipole layer that shifts the flat-band voltage ( $V_{FB}$ ) of the devices [17]. Lundström *et al.* demonstrated the potential of Si/SiO<sub>2</sub>/Pd transistors as a leak detector and gas alarm sensor [19]. Sensing experiments were performed at 150 °C to speed up the time response of the device. They show that the sensor detects hydrogen in air and the sensitivity increases under nitrogen atmosphere and even more under argon atmosphere. Under oxygen or nitrogen atmospheres chemical reactions take place on the metal surface leading a reduction of available hydrogen atoms. In an inert atmosphere, only dissociation/association of hydrogen occurs, therefore, the sensitivity is higher.

Nylander et al. investigated the flat-band voltage shift of Si/SiO<sub>2</sub>/Pd capacitors upon exposure of hydrogen. They found that the  $V_{\rm FB}$  shift occurs not only due to change in work function of the metal but also due to hydrogen-induced drift (HID). HID is only related to the silicon dioxide layer but takes place close to the SiO2/Pd interface and it is associated with the presence of SiO<sup>-</sup>Na<sup>+</sup> that acts as weak binding sites for protons via ion-dipole interaction [20]. HID effects were improved by the incorporation of thin oxidized layers such as alumina, tantalum pentoxide, and silicon nitride between the SiO<sub>2</sub> and Pd. Improvement of HID is associated with the structure that the metal adopts on the top of different insulating materials [21]. On the other hand, Dwivedi et al. found that after dissociation of hydrogen on the catalytic metal, some of them can tunnel the insulator layer and reach the  $SiO_2/Si$  interface [22]. At the interface, hydrogen atoms react with interface traps leading to the formation of hydrogen-induced interface traps, thus affecting seriously the electrical characteristics of the sensor [23]. The layer thickness of the insulator material also influences the sensitivity of the devices because interface trap density increases for thicker layers. Aval et al. found this dependence in Si/SiO<sub>2</sub>/Ni capacitors with an oxide layer thickness between 28 nm to 53 nm [24]. Increase in layer thickness leads to an increment of interface trap density from  $4.4 \times 10^{-1}$

<sup>10</sup> Ccm<sup>-2</sup> (28 nm) to  $6.9 \times 10^{-10}$  Ccm<sup>-2</sup> (53 nm) thus the response speed and recovery time of the devices decreases. A response of 87.5 % was achieved for the thinnest oxide layer. In addition to SiO<sub>2</sub>, many oxide layers have been investigated for hydrogen sensing application [25]. For instance, it was demonstrated that Si/TiO<sub>2</sub>/Pd sensors detect hydrogen at room temperature in ambient or hydrogen atmospheres. The sensitivity depends on the deposition method of the insulator material. TiO<sub>2</sub> prepared by electron beam evaporation shows higher sensitivity of 84 % in ambient air and 90 % in nitrogen atmosphere [26].

### **1.3 Motivation and Structure of the Thesis**

MOFs are potential candidates for electronic applications because of its tunable chemistry, porosity, and high surface area. The first applications of MOFs in transistors were reported in 2017 by Wu *et al.* [13] and Gu *et al.* [14]. However, little is known about the interface quality of the devices which can lead to threshold voltage instabilities and thus the performance of the devices can be degraded. Therefore, the aim of this thesis is the integration of metal-organic frameworks within metal-insulator-semiconductor capacitors and the investigation of interfacial properties by impedance spectroscopy. Generally, a large number of MOFs with good sensing characteristics and insulating properties are available [27]. In particular,  $Cu_3(BTC)_2$  also known as HKUST-1 (Hong Kong University of Science and Technology) [28], exhibits excellent chemical and physical properties such as porosity, large surface area, large optical bandgap of 3.6 eV [29] and stable crystalline structure under post-annealing treatments [30]. Besides, it was demonstrated that  $Cu_3(BTC)_2$  can be grown on silicon dioxide surfaces with low surface roughness and high crystalline quality [29,31]. Nevertheless,  $Cu_3(BTC)_2$  possess a low dielectric constant. The theoretical k value is equal to 1.7 while the experimental one after deposition is ~2.3 [30].

Conventional metal-oxide-semiconductors capacitors were fabricated using  $Cu_3(BTC)_2$  MOF as insulating material. Thin  $Cu_3(BTC)_2$  films were prepared in a layer-by-layer fashion directly on silicon wafers and on silicon dioxide surfaces. Interfacial properties and charge transport mechanisms of the devices were evaluated through capacitance and conductance characteristics measured at different voltages and frequencies. The major benefit in comparison to the already reported MOF-based-FET electronic devices, which require relatively high voltages, is that the MOF-MIS-device can be operated with less than 10 V. The low-voltage-operation and thus the low-energy-consumption could enable real-life applications.

This research work was developed in cooperation between the Laboratorium für Nano- und Quantenengineering (LNQE) of the Leibniz University (LUH) and the Institut für Materialien und Bauelemente der Elektronik (MBE). Deposition of ultra-thin Cu<sub>3</sub>(BTC)<sub>2</sub> films were done at the Institut für Physikalische Chemie und Elektrochemie (LUH) and at the Institut für Funktionelle Grenzflächen (IFG) in Karlsruhe. The thesis is divided into eight sections. Chapter 2 provides a theoretical background about the physics and work principles of metalinsulator-semiconductor capacitors with an emphasis on the different charges that can be present in the devices, and the growth of thin films of metal-organic frameworks on substrates. In chapter 3, the fabrication of the capacitors and analytical techniques will be described. Chapter 4 summarizes the different methods used for the determination of interfacial properties of MIS capacitors from impedance measurements such as the conductance method and the Hill-Coleman approximation. Chapter 5 discusses the effect of trimesic acid (TMA) and forming gas (FG) annealing on SiO<sub>2</sub>-based MIS capacitors. After that, the results of Cu<sub>3</sub>(BTC)<sub>2</sub>-based MIS capacitor will be presented. First, the analysis of samples prepared by the spray-method (Chapter 6) and then the samples prepared by the layer-by-layer approach assisted by ultrasonication (Chapter 7). Finally, conclusion and outlook are presented in Chapter 8.

### **2** Basics

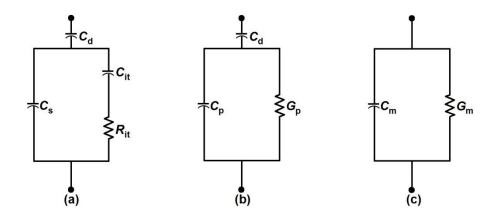

The metal-insulator-semiconductor capacitor is formed by a dielectric material deposited or grown on top of a semiconductor wafer and followed by a metal electrode that serves as a voltage source. The MIS capacitor is the basic building block for several integrated devices such as transistors [32–34]. Additionally, they offer detailed information about the electrical quality of the semiconductor/insulator interface. The reliability of MIS structures is affected by charges, also known as defects, generated during the manufacture of the device. Five types of charges can be found in an MIS device: mobile ionic charges  $(Q_{mob})$ , oxide-trapped charges  $(Q_{\text{ot}})$ , fixed charges  $(Q_{\text{fix}})$ , interface-trapped charges  $(Q_{\text{it}})$ , and border-trapped charges  $(Q_{bt})$  [35,36]. These charges are distributed within the insulator layer and at the insulator/semiconductor interface. Particularly,  $Q_{it}$  and  $Q_{bt}$  are located in traps which have energy levels within the silicon bandgap [37]. High amount of charges and traps leads to voltage threshold instabilities degrading the performance of the capacitors. Therefore, understanding the nature of defects is of great importance in order to improve the performance of the devices. The following section comprises the basics of MIS structures with an emphasis on the effect of charges on capacitance-voltage characteristics of the Si-SiO<sub>2</sub>-Al system.

Metal-organic frameworks, a new class of porous materials composed of metal clusters and organic linkers have been used in a wide variety of applications because of its extraordinary properties such as high surface area, porosity, and tunable functionality [38]. In the last years, several efforts were made to integrate MOFs into electronic devices [13,14]. For instance, many methods were developed in order to attach MOFs on various substrates [9,39]. The present section will present the potential of MOFs in microelectronics with special attention on the properties of  $Cu_3(BTC)_2$  MOF and deposition techniques that deliver thin film MOFs.

### 2.1 Metal-Insulator-Semiconductor (MIS) Capacitor

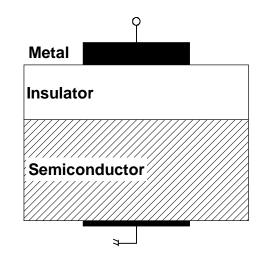

Figure 2.1 depicts a cross-section illustration of a metal-insulator-semiconductor capacitor consisting of a semiconductor, an insulating material, and a metal gate. The MIS structure is the simplest device for the study of semiconductor surfaces because it has only two terminals: the gate electrode and the silicon substrate that has to be connected by an Ohmic contact [34]. The most important and widely studied system is composed of Si-SiO<sub>2</sub>-Al. In this system, the insulator layer is formed by thermal oxidation process leading defects distributed within the insulator material and at the Si/SiO<sub>2</sub> interface. The density of defects depends on the oxidation conditions such as atmosphere, temperature, and cooling. Additionally, they depend strongly on the characteristics of the wafer such as orientation, resistance, and doping concentration.

Figure 2.1 Cross-section illustration of a metal-insulator-semiconductor capacitor consisting of two electrodes (the metal gate and the silicon) separated by an insulator.

#### Defects near and at the Si/SiO<sub>2</sub> interface

Interfacial defects have been extensively investigated and characterized by their spin concentrations and spectroscopic g values obtained by electron spin resonance (ESR) [40–43]. Defects also termed as centers in the Si/SiO<sub>2</sub> system are classified into two groups: (1) *E* center or trivalent silicon center located at the Si/SiO<sub>2</sub> interface. They consist of silicon-bonded to three other silicon atoms  $\cdot$ Si=Si<sub>3</sub> and (2) *E*' center or trivalent silicon center located in SiO<sub>2</sub> but close to the Si/SiO<sub>2</sub> interface. These defects consist of silicon-bonded to three oxygen atoms  $\cdot$ Si=O<sub>3</sub> [40,42]. *E* centers were detected first by Nishi [44] on Si(111) substrates and they were classified as  $P_A(g=\sim 2.000)$ ,  $P_B(g=\sim 2.000)$  to  $\sim 2.010$ ) and  $P_C$

(g=~2.06 to ~2.07) paramagnetic centers. The centers were associated with the growth of SiO<sub>2</sub> layer in dry atmosphere and the heating/cooling process from room temperature to elevated process temperature and return.  $P_A$  and  $P_C$  centers were associated with trapped electrons in the oxide, while  $P_B$  center to trivalent Si centers in the broken Si-O network, respectively. Later Caplan and Pointdexter termed the *E* centers as  $P_b$  center and found a good correlation between the spin concentration of  $P_b$  centers and density of interface traps measured at the midgap position [40]. On the other hand, they associate the *E*' center to oxygen vacancies with unpaired silicon spin (O<sub>3</sub>=Si·) and striped positively charges (<sup>+</sup>Si=O<sub>3</sub>). On Si(100) substrates, 2 sub-groups of  $P_b$  center were found  $P_{b0}$  (·Si=Si<sub>3</sub>) and  $P_{b1}$  (·Si=SiO<sub>2</sub>) as is shown in Figure 2.2 [45].

Figure 2.2 Structure and location of  $P_{b0}$  and  $P_{b1}$  centers generated in oxidized (100) silicon wafers based on electron spin resonance anisotropy.  $P_{b0}$  center is assigned to  $\cdot$ Si $\equiv$ Si<sub>3</sub> back-bonded in the silicon surface while  $P_{b1}$  is associated with  $\cdot$ Si $\equiv$ SiO<sub>2</sub> [45].

Defects at the  $Si/SiO_2$  system capacitors can be quantified by several techniques such as impedance, deep-level transient spectroscopy, electron spin resonance, photocurrent-voltage, and others. The present research work will be focused on impedance spectroscopy which provides information of both, capacitance and conductance characteristics. Capacitance measures the change of charges in the capacitor produced due to the change of voltage. Conductance measures the energy loss due to change in occupancy of traps.

#### 2.1.1 Ideal MIS Capacitor

The following part will address the ideal MIS capacitors, a perfect device without defects. The ideal MIS capacitor is a very simple system that facilitates the understanding of the structure and physics of the device. It is defined assuming the following suppositions [32,46,47]:

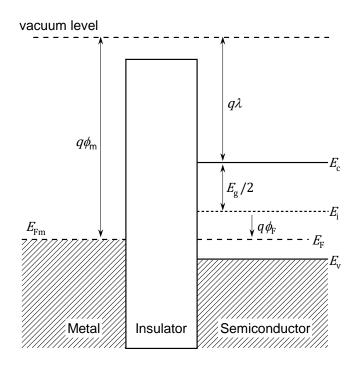

Figure 2.3 Energy-band diagram for an ideal MIS capacitor on p-type Si substrate. At zero voltage ( $V_g=0$ ) the bands of the semiconductor are flat (flat-band condition) [46].

*i)* At thermal equilibrium conditions, the work function difference between the metal and the semiconductor is zero ( $\Phi_{ms}=0$  at  $V_g=0$  V):

$$\Phi_{ms} = \Phi_m - \left(\chi + \frac{E_g}{2q} + \Phi_F\right) = 0 \quad \text{for } p\text{-type Si}$$

(2.1)

where  $\Phi_{\rm m}$  and  $\Phi_{\rm s}$ , are the work function of the metal and the semiconductor,  $\chi$  is the electron affinity,  $E_{\rm g}$  is the energy bandgap, q is the elementary charge and  $\Phi_{\rm F}$  is the Fermi potential.

*ii)* There are no charges in the insulator layer as well as at the insulator/semiconductor interface ( $Q_{\text{mob}}=0$ ,  $Q_{\text{ot}}=0$ ,  $Q_{\text{fix}}=0$ ,  $Q_{\text{it}}=0$ ,  $Q_{\text{bt}}=0$ ). The only charges that exist are located in the semiconductor ( $Q_{\text{s}}$ ) in equal amount but with opposite sign that in the metal ( $Q_{\text{m}}$ ), where  $\pm Q_{\text{m}}=\mp Q_{\text{s}}$ .

*iii)* The dielectric material is a perfect insulator (carrier transport under DC bias from the metal to the semiconductor is not allowed).

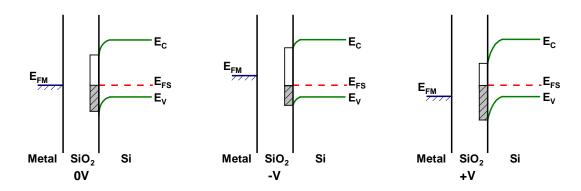

Energy-band diagram for the ideal MIS capacitor is shown in Figure 2.3. The insulator material has a large bandgap in comparison to the semiconductor, ~8.8 eV for SiO<sub>2</sub> and ~1.12 eV for silicon. Thus the flow of free carriers from the metal to the gate is prevented. Under no biasing conditions ( $V_g=0$  V), the bands in the semiconductor are flat and the Fermi level of the semiconductor coincide with the Fermi level of the metal. This condition is known as the Flat-band condition. When voltage is applied through the metal gate, an electric field is established in the insulating layer and three situations can happen:

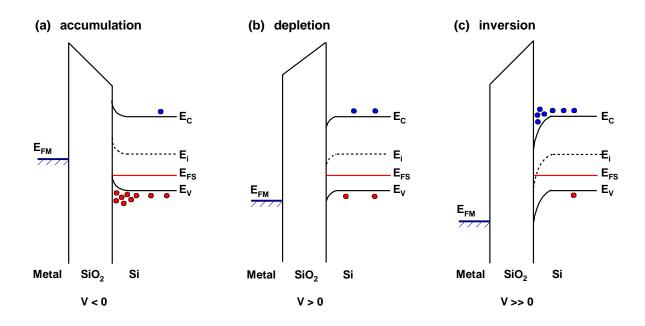

#### a) Accumulation

When the capacitor is biased with a negative voltage (V<0), the bands in the semiconductor bend upward (see Figure 2.4a). Note that bending occurs only at the semiconductor surface. Band-bending leads an exponential increase of majority carrier (holes) density near the SiO<sub>2</sub>/Si interface that compensates the negative potential in the metal gate. The charge distribution of the semiconductor is equal to the metal,  $\pm Q_m = \mp Q_s$ .

#### b) Depletion

When the capacitor is biased with a small positive voltage (V>0), the bands in the semiconductor bend downward (see Figure 2.4b) and the majority carrier are depleted from the surface. In this case, the charge distribution of the semiconductor is known as space charge per unit area ( $Q_{sc}$ ) and is proportional to the width of the surface depletion region ( $W_m$ ) and the acceptor impurity ( $N_A$ ),  $Q_s=Q_{sc}=-qN_AW_m$ .

Figure 2.4 Energy-band diagram for an ideal p-Si/SiO<sub>2</sub>/Al MIS capacitor under bias condition showing the accumulation (a), depletion (b) and inversion (c) cases. Upon bias condition, the bands in the semiconductors bend upward/downward and accumulation of holes/electrons occurs depending on the polarity of the applied voltage. Note that accumulation of carrier occurs only at the semiconductor surface [32].

#### c) Inversion

Once the negative voltage increases the bands in the semiconductor continue bending until the intrinsic level reach the Fermi level. This position is known as the midgap condition. When the capacitor is biased with a larger positive voltage (V>>0), the bands in the semiconductor bend downward even more that minority carrier is pushed out from the surface and the minority carrier (electrons) accumulates at the surface (see Figure 2.4c). In this case, the electron concentration is larger than the hole concentration, thus the surface behaves like an *n*-type Si semiconductor. This is known as the inversion region. The charge distribution of the semiconductor is the contribution of the space charge per unit area and the charge in the inversion layer  $Q_s=Q_{in}+Q_{sc}$ .

In the ideal case, the total charge in the semiconductor per unit area in the semiconductor is defined by the following equation [46]:

$$Q_s = -\epsilon_s \xi_s = \mp \sqrt{2} \frac{\varepsilon_s \Phi_t}{L_D} F(\psi_s, N_A)$$

(2.2)

where  $Q_s$  is the total charge per unit area in the semiconductor,  $\varepsilon_s$  is the permittivity of the semiconductor,  $\xi_s$  is the electric field,  $\Phi_t$  is surface potential,  $\psi_s$  is the band bending, and  $N_A$  acceptor concentration.

The differential capacitance of the semiconductor is proportional to the charge distribution and is defined by the following equation [46]:

$$C_{s} \equiv \frac{\partial Q_{s}}{\partial \psi_{s}} - \xi_{s} = \frac{\epsilon_{s}}{\sqrt{2}L_{D}} \frac{\left|1 - e^{-\psi_{s}/\Phi_{t}} + \left(\frac{n_{i}}{N_{A}}\right)^{2} \left(e^{\psi_{s}/\Phi_{t}} - 1\right)\right|}{F(\psi_{s}, N_{A})}$$

(2.3)

where  $C_s$  is the differential capacitance,  $L_D$  is the extrinsic Debye length, and  $n_i$  is the intrinsic carrier concentration.

The total capacitance ( $C_{tot}$ ) of the MIS system is a series combination of the dielectric capacitance ( $C_d$ ) and the semiconductor capacitance ( $C_s$ ) given by:

$$C_{tot} \equiv \frac{C_d C_s}{C_d + C_s}$$

,  $C_d \equiv \frac{\varepsilon_d}{d}$  (2.4)

where  $C_d$  and  $C_s$  are the dielectric and semiconductor capacitance, respectively.  $\varepsilon_d$  and *d* are the permittivity and thickness of the dielectric layer, respectively. In strong accumulation, the capacitance is equal to the dielectric capacitance,  $C_d$ .

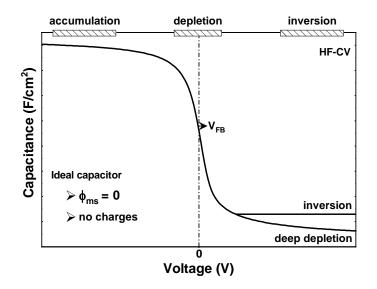

High-frequency capacitance-voltage (HF-CV) curves measured from accumulation to inversion (acc-inv, solid curve) and back from inversion to accumulation (inv-acc, dashed curve) directions for an ideal *p*-Si/SiO<sub>2</sub>/Al MIS capacitor are shown in Figure 2.5. The *C-V* curve exhibits the characteristic accumulation, depletion, and inversion regimes described above. When the DC sweep is high the inversion layer is not reached and then the deep depletion regime appears. At high frequencies (f > 100 kHz), minority carrier cannot follow

the alternating current and, therefore, the capacitance in inversion does not increase. In the ideal case, the flat-band voltage ( $V_{\text{FB}}$ ) is located at 0 V and the accumulation region is reached by applying a negative voltage to the metal gate. Furthermore,  $C-V_{\text{acc-inv}}$  and  $C-V_{\text{inv-acc}}$  curves are identical.

Figure 2.5 High-frequency capacitance-voltage curves for an ideal  $Si/SiO_2/AI$  MIS capacitor on *p*-type Si substrate. In the ideal case, the *C*-*V* curves in forward and reverse mode are equal and, therefore, no hysteresis is observed. In addition, the flat-band voltage is located at 0 V. The dashed areas represent the accumulation, depletion, and inversion regimes.

#### 2.1.2 Real MIS Capacitor

The assumptions made for the ideal capacitor are invalid for the real case. In a real p-Si/SiO<sub>2</sub> system, the  $\Phi_{ms}$  difference depends on the work function of the metal and the doping concentration of the substrate. The capacitor exhibits also charges and traps centers generated during the manufacture of the devices.

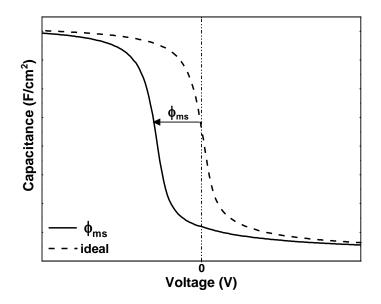

#### a) Effect of $\phi_{ms}$ in the C-V Curve

In the real case, the work function of the metal is different from that of the semiconductor,  $\Phi_{ms}\neq 0$ . Thus, in contrast to the ideal case ( $V_{FB}=0$ ), the flat-band voltage is equal to the  $\Phi_{ms}$  difference.  $V_{FB}$  due to  $\Phi_{ms}$  difference is not influenced by charges, therefore, it will be considered as the theoretical flat-band,  $V_{FB,theor}$ . For a real MIS capacitor  $V_{FB,theor}$  can be determined using the Equation (2.5). The effect of  $\Delta \Phi_{ms}$  on capacitance measurements is shown in Figure 2.6. Note that  $\Delta \Phi_{ms}$  produces only a parallel shift of the whole *C-V* curve toward the negative voltage axis.

Figure 2.6 Capacitance-voltage curve for *p*-Si/SiO<sub>2</sub>/Al MIS structure for the ideal case (black curve) and including the effect of work function difference between the metal and the semiconductor (red and purple curves).  $\Delta \Phi_{ms}$  induces a parallel shift of the whole capacitance curve.

$$\Phi_{ms} = K - \frac{kT}{q} \ln\left(\frac{N_A}{n_i}\right) and \quad K = \Phi'_m - \chi' - \frac{E_c - E_i}{q}$$

(2.5)

where  $N_A$  is the acceptor concentration,  $n_i$  is the intrinsic concentration,  $\Phi'_m$  is the effective work function of the metal,  $\chi'$  is the effective electron affinity, q is the elementary charge, and  $E_c$  and  $E_i$  are the conduction band edge and the intrinsic level. According to the doping concentration of the substrate,  $V_{FB,theor}$  for p-Si/SiO<sub>2</sub>/Al MIS capacitor can be varied from ~-0.89 V ( $N_A$ =1×10<sup>15</sup> cm<sup>-3</sup>) to ~-1.01 V ( $N_A$ =1×10<sup>17</sup> cm<sup>-3</sup>).

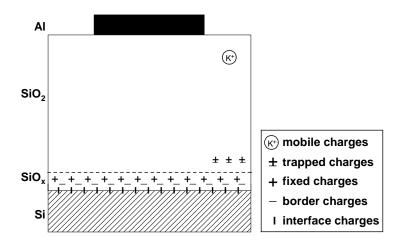

#### b) Effect of Oxide Charges in the C-V Curve

Real MIS capacitors contain charges distributed in the dielectric bulk and at the dielectric/semiconductor interface. In the *p*-Si/SiO<sub>2</sub>/Al MIS system, the oxidation process leads to a non-stoichiometric SiO<sub>x</sub> layer as is shown in Figure 2.7. This layer is occupied by fixed charges and defects that can interact with the semiconductor. Therefore, these defects can respond to capacitance-voltage measurements. In 1979, Bruce Deal classified the charges in MIS capacitors in four groups: fixed charges ( $Q_{fix}$ ), mobile ionic charges ( $Q_{mob}$ ), interface-trapped charges ( $Q_{it}$ ), and oxide trapped charges ( $Q_{ot}$ ) [35]. Later, Fleetwood introduced the concept of border traps [36].

Figure 2.7 Charges and their location between the *p*-Si/SiO<sub>2</sub>/Al structure according to the classification of Bruce Deal [35] and Fleetwood [36]. Charges located between the non-stoichiometric SiO<sub>x</sub> layer can be measured by capacitance-voltage. The oxidation process leads to a non-stoichiometric SiO<sub>x</sub> region occupied by charges that can be measured by impedance spectroscopy.

Mobile charges and oxide trapped charges are distributed within the bulk of the insulator.  $Q_{\text{mob}}$  are ionic impurities such as Li<sup>+</sup>, Na<sup>+</sup>, K<sup>+</sup>, H<sup>+</sup>. These charges are generated by contamination and became mobile at high temperature.  $Q_{\text{ot}}$  are positive (holes) or negative (electrons) charges generated by ionization radiation, avalanche injection, or similar process. The amount of  $Q_{\text{ot}}$  can be reduced by annealing treatments below 500 °C. Oxide trapped charges are not affecting *C-V* measurements, and mobile charge can be prevented by avoiding contamination during the manufacturing process of the device. Therefore, only the effect of fixed charges, interface charges, and border charges on the *C-V* characteristics will be analyzed.

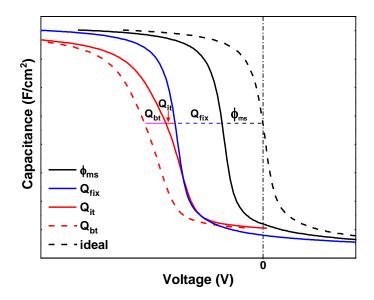

#### a) Fixed Charges, Q<sub>fix</sub>:

Fixed charges are distributed within the non-stoichiometric SiO<sub>x</sub> region. They are fixed in position and cannot interact with the semiconductor.  $Q_{fix}$  are created during the oxidation process and can be either positive or negative. In *p*-Si/SiO<sub>2</sub>/Al MIS capacitor,  $Q_{fix}$  is positive [48,49] while for *p*-Si/Al<sub>3</sub>O<sub>2</sub>/Al is negative [50,51]. Similar to  $\Delta \varphi_{ms}$ , fixed charges induce a parallel shift of the whole *C*-*V* curve (see Figure 2.8). The density of fixed charges is determined in the following way: first, the theoretical flat-band voltage ( $V_{FB,theor}$ ) is subtracted from the measured capacitance ( $V_{FB,exp}$ ) curve and then  $Q_{fix}$  is calculated using Equation 2.6 [52]:

$$Q_{fix} = \frac{\Delta V}{q} C_d \text{ and } \Delta V = V_{FB,theor} - V_{FB,exp}$$

(2.6)

where  $C_d$  is the dielectric capacitance and q is the elementary charge.  $V_{FB,theor}$  and  $V_{FB,exp}$  are the theoretical and experimental flat-band voltages values, respectively.

At the flat-band position, Equation (2.6) contains information of  $Q_{\text{fix}}$  alone only if the capacitor does not contain border and interface charges. When these charges are taken into account, Equation (2.6) gives information of effective oxide charges ( $Q_{\text{fix,eff}} = Q_{\text{fix}} + Q_{\text{bt}} + Q_{\text{it}}$ ).

#### b) Interface Trapped Charges, $Q_{ii}$ :

Interface traps charges are located at the insulator/semiconductor interface (see Figure 2.7). There are three sources of  $Q_{it}$ : (1) oxidation-induced defects, (2) metal impurities, and (3) radiation or similar process that produces bond breaking. Interface trap charge density can be measured by charging interface traps levels. Interface traps levels are defects associated with trivalent silicon centers at the Si/SiO<sub>2</sub> interface distributed within the silicon bandgap and can interact with the silicon band edges by capture and emission of carriers with time response between 5 µs to 50 µs [53]. Interface traps are classified in two types: (1) acceptor-like interface traps, that are negatively charged after trapping electrons and neutral when empty and (2) donor-like interface traps are positively charged when donating electrons and neutral when filled [46]. Interface trapped charge stretches out the *C-V* curve along the depletion region and shifts the capacitance curve except at the midgap position (see Figure 2.8). Additionally, they contribute to the total differential capacitance.

Figure 2.8 Capacitance voltage curve for a real p-Si/SiO<sub>2</sub>/Al MIS capacitor showing the effect of  $\phi$ m and the different charges that can be present in the device. Fixed charges induce a parallel shift of the whole capacitance curve. In addition to a small parallel shift interface charges contributed to the accumulation capacitance. In contrast, border-trapped charges generate hysteresis in the *C*-*V* curve.

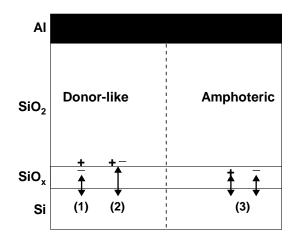

#### c) Border-Trapped Charges, Q<sub>bt</sub>:

Border-trapped charges are located in the dielectric layer but close to the insulator/semiconductor interface (see Figure 2.7) and can be measured by charging border trap levels [54]. Similar to interface traps, border traps communicate with the underlying silicon substrate by exchanging charges predominantly via tunneling process [55] but with lower time response in comparison to interface traps (50  $\mu$ s to 500  $\mu$ s) [53]. The origin of border traps can be associated with *E*' centers within the insulator layer. Border traps yield the formation of hysteresis in the *C-V* curve and frequency dispersion in the accumulation region of the capacitance at low frequencies [54]. Figure 2.9 shows the three types of centers associated with border traps. Donor-like traps type (1) and (2) are positive trapped charges in the insulator layer which can exchange electron with the silicon. The location of traps type (2) are further than type (1), therefore, the charge exchange is lower for traps type (2). Type (3) is an amphoteric border trap center and similar to interface traps can exchange either electrons of holes with the semiconductor. These three types of traps contribute to the *C-V* hysteresis.

Figure 2.9 Schematic representation of border traps in MIS capacitors. Donor-like traps type (1) and (2) are associated with holes trapped near the interface while amphoteric traps (3) can exchange electrons or charge with the silicon band-edges. The dashed region in the insulator layer represents the non-stoichiometric SiO<sub>2</sub> [56].

In general, fixed charges are known as fixed states because they do not communicate with the semiconductor on the measurement time scale. In contrast, interface traps and border traps are switching states because they communicate electrically with the silicon band edges by capture and emission of carriers. Interface traps are associated with trivalent silicon center at the SiO<sub>2</sub>/Si interface due to silicon dangling bonds while border traps are associated with trivalent silicon center in SiO<sub>2</sub> but close to the SiO<sub>2</sub>/Si interface due to oxygen vacancies. Amount of fixed and switching states must be controlled since they significantly affect the long-term reliability of MIS-based electronic devices [56]. Defects in SiO<sub>2</sub>-based MIS capacitors are reduced by post-annealing treatments under forming gas atmosphere. At high temperatures (~450 °C), hydrogen atoms diffuse easily through the oxide layer and saturate the dangling bonds [57].

### 2.2 Metal-Organic Frameworks (MOFs)

Metal-organic frameworks are highly ordered crystalline materials consisting of metal ions interconnected to organic linkers yielding a three-dimensional network with well-defined pores as is shown in Figure 2.10 [38,58,59].

Figure 2.10 Schematic illustration of the construction of MOFs: the connection of the metal node with the organic linker leads a cubic structure [60]. The topology of MOFs is tuned by interconnecting different organic and inorganic components.

There are a large diversity of inorganic components such as  $Al^{+2}$ ,  $Cu^{+2}$ ,  $Fe^{+2}$ ,  $Zn^{+2} Zr^{+2}$ , and lanthanides (Ln= La, Ce, Pr, Nd, Sm, Eu, Gd, Tb, Dy, Ho, Er, and Tm). The organic component typically consists of amines, carboxylates, nitrides, phosphates or sulfonates [61]. The topology and functionality of metal-organic frameworks can be tuned by connecting the inorganic component with different linkers resulting in a large number of MOFs with different geometries and properties suitable for many applications. Table 2.1 summarizes the structural features including metal unit and organic ligand of the different MOFs covered in this section.

| ·             |            |                                       |

|---------------|------------|---------------------------------------|

| MOF acronym   | Metal unit | Organic ligand                        |

| Co-NDC        | Zinc       | NDC=2,6-naphthalenedicarboxylic acid  |

| $Cu_3(BTC)_2$ | Cooper     | BTC=1,3,5 benzenetricarboxylate acid  |

| IRMOF-M2c     | Zinc       | naphtacene                            |

| NDC-Y-fcu MOF | Yttrium    | NDC=1,4-naphthalenedicarboxylate acid |

| MIL-1         | Iron       | nicotinate molecules                  |

| MOF-5         | Zinc       | 1,4-benzodicarboxylic acid            |

| MOF-74        | Magnesium  | 2,5-dihydroxyterephthalic acid        |

| MOF-210       | Zinc       | 2,6-naphthalenedicarboxylic acid      |

| MOF-246       | Zinc       | DMF=N,N-dimethylformamide acid        |

| UiO-66        | Zirconium  | 1,4-benzodicarboxylic acid            |

| ZIF-8         | Zinc       | 2-methylimidazole                     |

Table 2.1 Acronym of metal-organic frameworks and their composition: metal unit + organic ligand. IRMOF: Isoreticular metal framework, MIL: Materials of Institute Lavoisier, ZIF: Zeolitic imidazolate frameworks, UiO: University of Oslo.

MOFs can host a wide variety of molecules on their inner surface because of its exceptional properties including ultra-high porosity and large surface area. In the case of MOF-210, the pore size and the Brunauer-Emmett-Teller (BET) surface area can be varied up to 48Å and 10.400 m<sup>2</sup>g<sup>-1</sup>, respectively [62]. They exhibit low (1.21 for IRMOF-M2c [63]) and high (14.17 for MOF-246 [64]) dielectric constant values. The optical bandgap can be varied up to 5.5 eV for ZIF-8 [65]. Metal-organic frameworks are affected by different types of defects such as point and extended defects [66]. Point defects are vacancies associated with missing linkers or unsaturated ion metals. On the other hand, extended defects are associated with imperfection in the crystal structure such as dislocations, and heterogeneity [67]. UiO-66 (Zr), MOF-74, and Cu<sub>3</sub>(BTC)<sub>2</sub> exhibit unsaturated metal sites that serve as host centers for gases or molecules, however, they can degrade under high temperature and humidity conditions (40 °C, 90 % for Cu<sub>3</sub>(BTC)<sub>2</sub>) [68].

MOFs have lots of potential applications including gas storage, separation, catalysis and sensors [38]. In catalysis, UiO-type MOFs have been widely studied because of its chemical stability and defects resulting from the deficiency of linkers that act as active sites for acid-catalyzed reactions [4]. The amount of defects can be easily modulated during the synthesis process. In photovoltaic, Cu-BTC [69] and Co-NDC [70,71] have been investigated as a sensitizing layer in TiO<sub>2</sub> liquid junction solar cells. The conductivity and charge transfer

reaction across the TiO<sub>2</sub>/MOF/FTO interface were enhanced by iodine doping. Energy conversion efficiency values of 0.26 % and 1.12 % were attained for Cu-BTC [69] and Co-NDC [71] MOFs, respectively. In biomedicine, MOFs are attractive for the delivery of bioactive molecules such as nicotinic acid (vitamin B3). Particularly, the BioMIL-1 built up of non-toxic iron units via nicotinate molecules degrades within a few hours allowing the release of the biomolecule [5,72]. MOFs can sense different vapors, gases, and molecules [73]. For example, rare earths (RE) based MOFs were incorporated on interdigitated electrodes for sensing of ammonia (NH<sub>3</sub>). Particularly, NDC-Y-fcu MOF with face-centered cubic lattice containing yttrium nodes and 1,4-naphthalenedicarboxylate (NDC) linker was prepared by the solvothermal method on SiO<sub>2</sub> surfaces functionalized by 11-mercaptoundecanoic acid. NDC-Y-fcu MOF exhibits excellent chemical stability with time and humidity conditions and can detect ammonia at concentrations down to ~1 ppm. Additionally, the MOF offers remarkable sensitivity toward NH<sub>3</sub> versus, CH<sub>2</sub>, NO<sub>2</sub>, and H<sub>2</sub> [74].

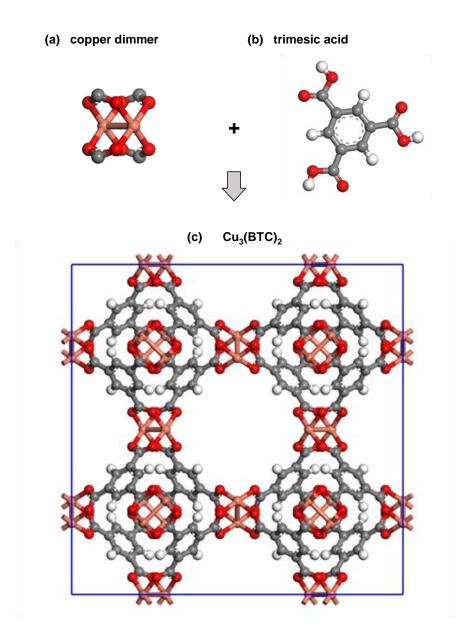

#### 2.2.1 Properties of $Cu_3(BTC)_2$

$Cu_3(BTC)_2$  also known as HKUST-1 consist of Cu(II) dimers linked to 1,3,5 benzenetricarboxylate nodes. The framework was first prepared by Pech-Pickardt [62] and further investigations were performed by Chui *et al.* [28]. 1,3,5 benzenetricarboxylate is also known as trimesic acid (TMA), it comprises a benzene ring connected with three carboxylic groups (Figure 2.11b). The secondary building unit of  $Cu_3(BTC)_2$  contains two copper ions (Figure 2.11a) bridged with four BTC units in a paddle wheel arrangement yielding a cubic structure with a lattice constant of 2.68 Å as is shown in Figure 2.11c. The crystal structure involves three pores with different diameters, 5 Å, 11 Å, and 13.5 Å [28].

$Cu_3(BTC)_2$  MOF exhibits the following properties: Brunauer-Emmett-Teller surface area of 1511 m<sup>2</sup>g<sup>-1</sup> [75], large optical bandgap of 3.6 eV [29], a low dielectric constant of 2.3 [30]. Additionally, partial positive charges exist on the copper atoms that are compensated by partial negative charges from the carboxylate units [28]. The unsaturated Cu<sup>+2</sup> sites can act as absorption, sensing or storage of guest molecules.

Figure 2.11 Schematic representation of  $Cu_3(BTC)_2$  MOF which consist of copper ions (a) and benzene-1,3,5-tricarboxylate units (b) giving rise a cubic structure with a lattice constant of 2.68 Å (c). Cu(orange atoms), O(red atoms), C(gray atoms), and H(white atoms). Image constructed using BIOVIA Materials Studio [76].

#### 2.2.2 Integration of MOFs in Electronic Devices

In the past years, extensive studies demonstrated the potential of metal-organic frameworks obtained as a powder in a wide variety of application [27,61]. Currently, the research is focused on the applications of MOFs in the electronics industry [13,14]. Integration of metal-organic framework into electronic devices requires the deposition of high quality and homogeneous MOFs on substrates with a layer thickness in the nanometer scales (d<100 nm) [6,7,77]. Several deposition methods were developed in order to achieve thin film MOFs on substrates including the solvothermal and the layer-by-layer methods.

#### a) Solvothermal Method

In this method, the solvents, metal salts and the organic linker are heated in a sealed vessel under pressure and at elevated temperatures. The crystalline structure can be modulated by temperature, pressure, and concentration of the metal and linker solutions. The crystallization process takes place between days or weeks. Additionally, the attachment of MOFs onto substrates supports require surface functionalization [78]. For instance, it was demonstrated that self-assembly monolayers, ultra-thin organic films with high structural quality, allow a direct binding of different materials onto a substrate [79]. One of the firsts deposition of MOFs on substrates was achieved by Hermes *et al.* [8]. They deposited MOF-5 on gold substrates by carboxylic acid-terminated SAM. The complete deposition process was performed in four days (72 hours for solution preparation and 24 hours for growth of the MOF). The solvothermal synthesis offers good control of the crystalline structure by using different functionalized SAMs. For instance, Biemmi *et al.* [80] demonstrated that the orientation of MOF crystals on gold substrates depend strongly on the molecular functionalization of the SAM. Cu<sub>3</sub>(BTC)<sub>2</sub> grown on COOH-SAM is oriented along the (100) direction while the growth on OH-SAM is oriented along the (111) direction.

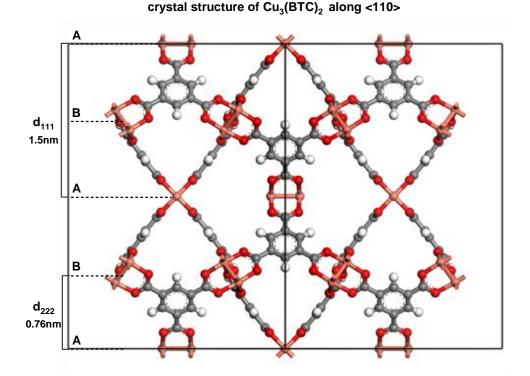

Figure 2.12 Crystal structure for  $Cu_3(BTC)_2$  viewed along the  $\langle 110 \rangle$  orientations showing the growth of the MOFs in step highs of 1.5 nm  $d_{111}$  and 0.76 nm  $d_{222}$ . Cu(orange atoms), O(red atoms), C(gray atoms), and H(white atoms). Image constructed using BIOVIA Materials Studio [76].

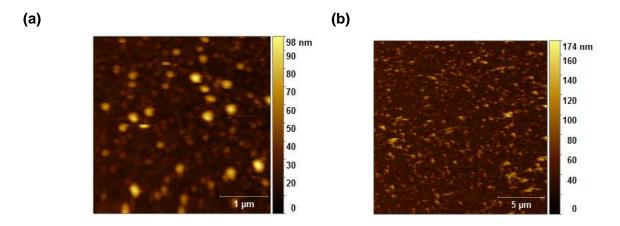

Figure 2.12 shows a cross-sectional analysis of the step-growth for Cu<sub>3</sub>(BTC)<sub>2</sub> along the (110) direction. Cu<sub>3</sub>(BTC)<sub>2</sub> can growth along the  $d_{222}$  or  $d_{111}$  crystal spacings with steps heights of 0.76 nm and 1.5 nm, respectively. The  $d_{222}$  step high consist of one layer of dimeric copper connected to four TMA units while the  $d_{111}$  is formed by two sublayers [81]. Surface termination at the layer of the octahedra A will leave one vacancy per Cu atom or one CO<sub>2</sub> group per trimesic moiety. Surface termination at the layer of the octahedra B leaves two vacancies per Cu atom or two CO<sub>2</sub> groups per trimesic moiety [81,82]. Atomic force microscopy (AFM) measurements reveal that Cu<sub>3</sub>(BTC)<sub>2</sub> obtained by solvothermal method grows on steps highs of 1.5±0.1 nm in accordance with the 1.5 nm  $d_{111}$  crystal spacing. Additionally, steps highs of 0.8 nm, 2.2 nm, and 3 nm in accordance with the 0.76 nm  $d_{222}$  crystal spacing were found [81].

23

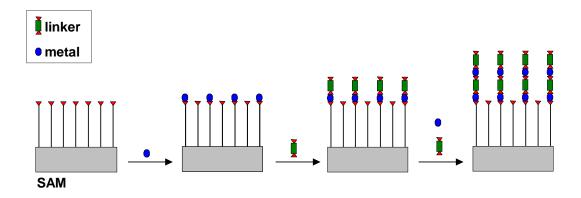

#### a) Layer-by-Layer (LBL) Growth

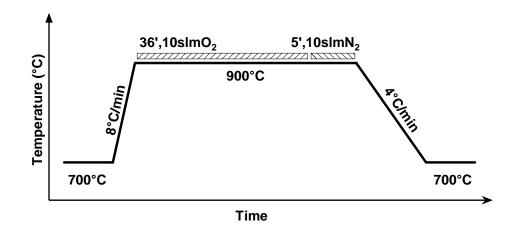

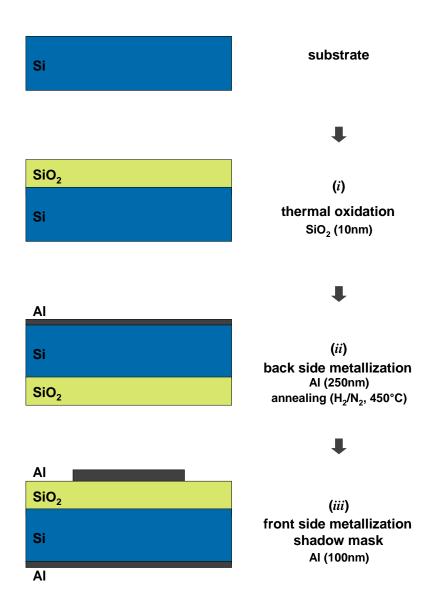

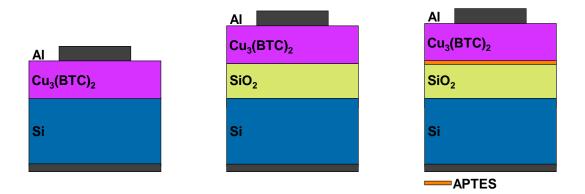

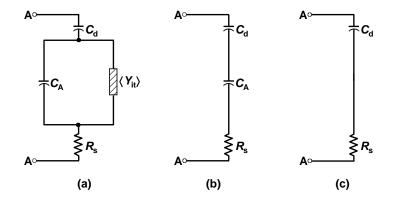

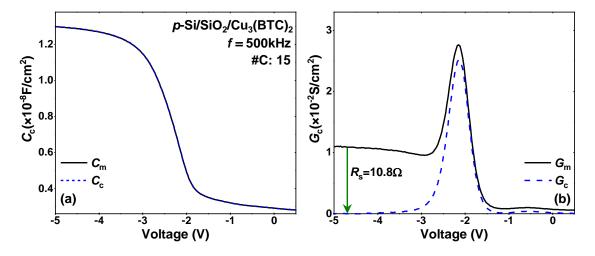

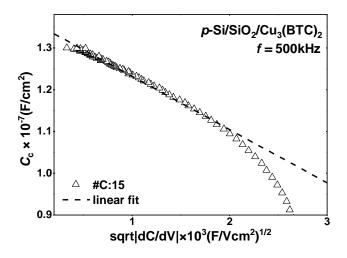

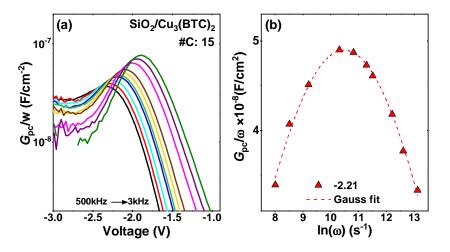

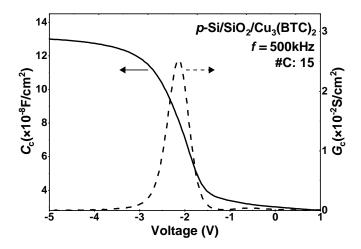

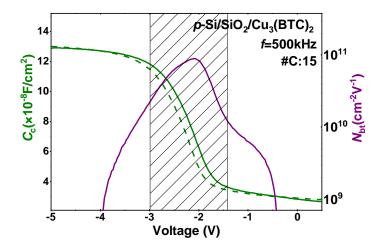

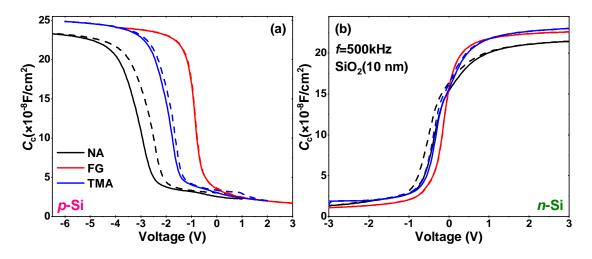

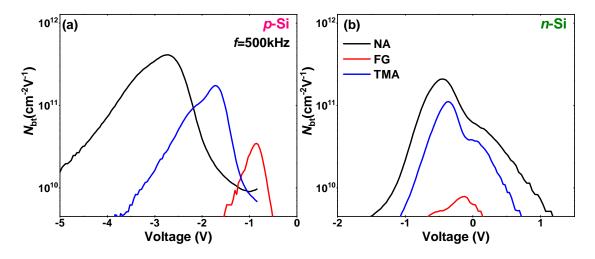

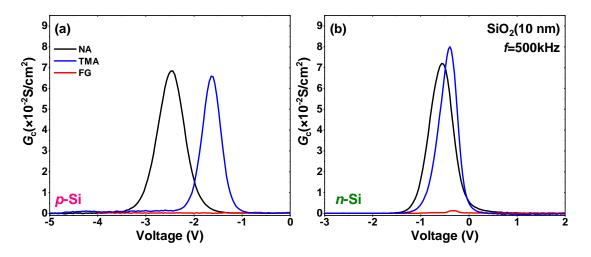

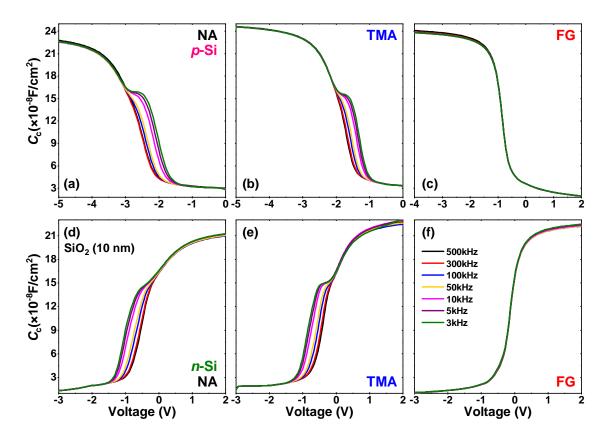

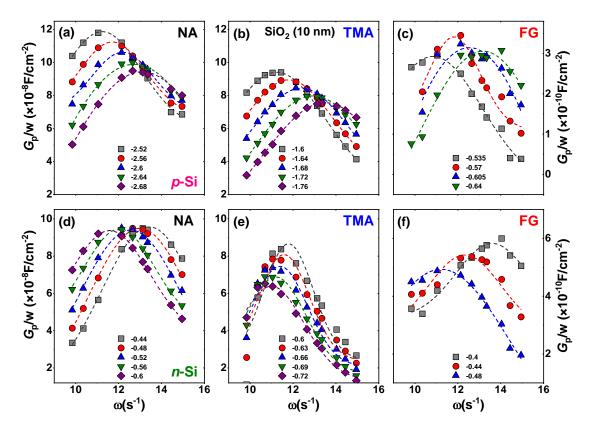

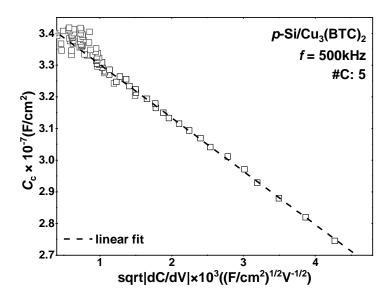

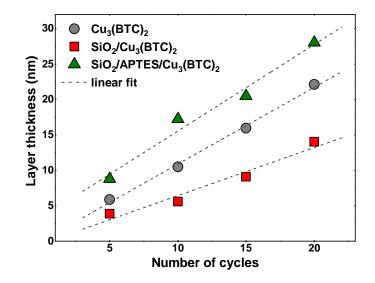

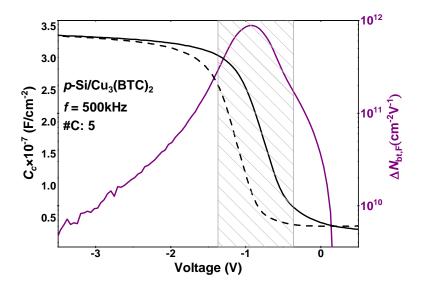

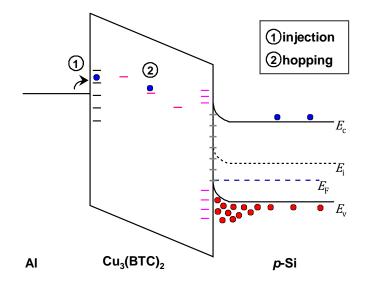

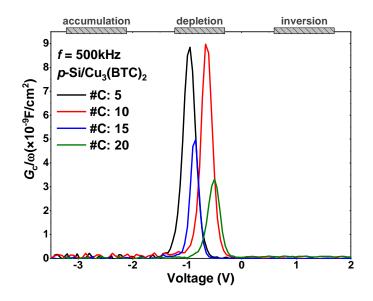

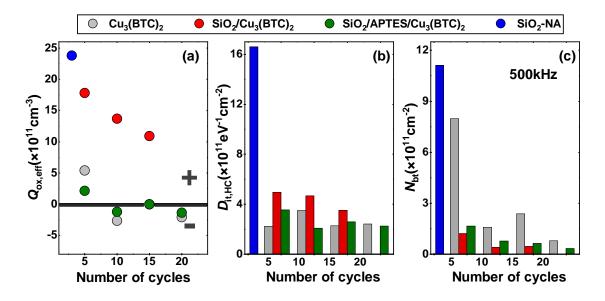

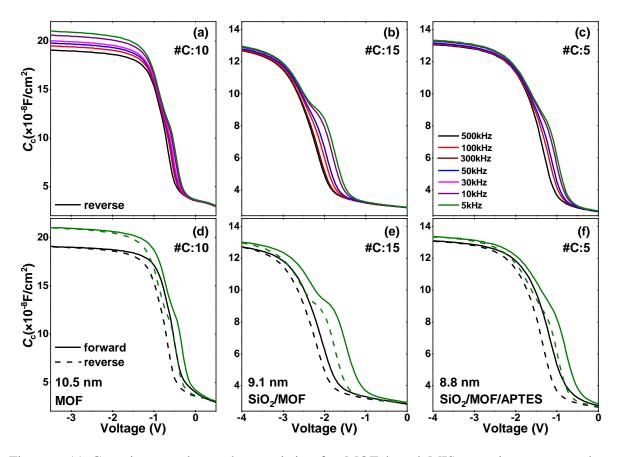

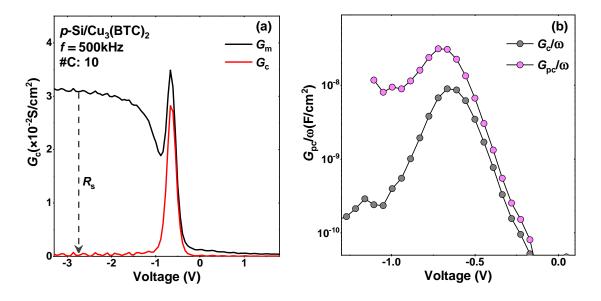

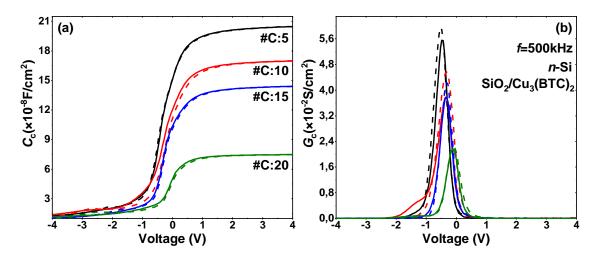

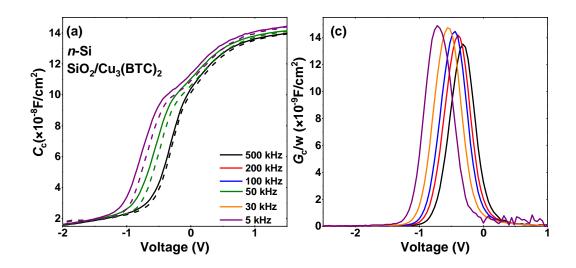

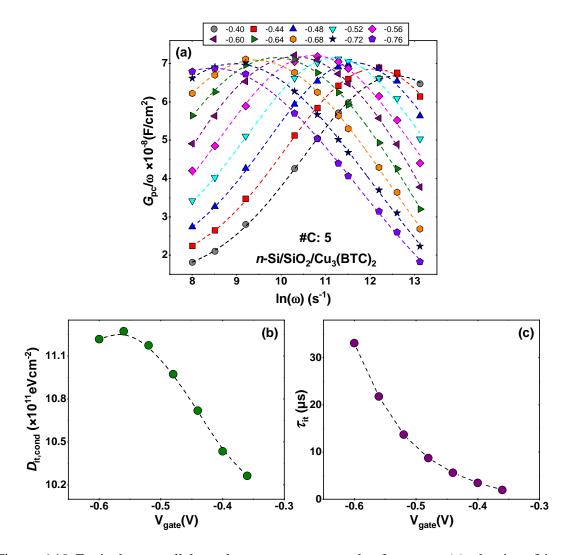

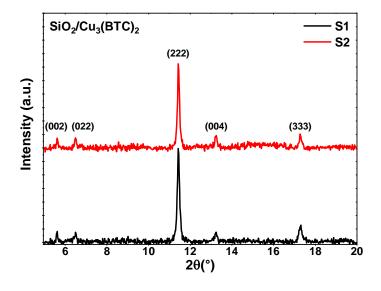

In the solvothermal method, the metal and linker precursors are mixed and sealed in a vessel for more than ~18 hours, after that the growth of MOFs takes place between days. In contrast, in the layer-by-layer growth, the metal and linker solutions are applied separately and in sequential order. In addition, pre-treatment of the precursors are not needed, therefore, the deposition process is reduced to hours. The layer-by-layer growth also known as step-by-step deposition was developed by Shekhah et al. [9] for the deposition of thin films of Zn(CH<sub>3</sub>CO<sub>2</sub>)<sub>2</sub> on COOH-terminated organic surfaces. The growth was made in a layer-bylayer fashion by repeated immersion of the substrate into a solution of Zn(II) acetate and then in the BTC solution. The MOF was characterized by infrared reflection adsorption spectroscopy which shows the characteristics bands of the carboxylic groups bonded to the Zn(II) ion. Besides, the MOF shows high stability under heating up to 100 °C. Nevertheless, no crystallographic information was obtained. Later Cu<sub>3</sub>(BTC)<sub>2</sub> was grown on 200 nmAu/Si substrates functionalized by COOH-SAM. XRD and scanning electron microscopy measurements revealed the growth of homogeneous and highly oriented crystalline structures [11]. Deposition details are shown in Figure 2.13. First, the SAM functionalized substrate is immersed in a copper acetate solution for 30 seconds. Then the layer is rinsed with ethanol and dried in nitrogen atmosphere. After that, the substrate is immersed in the TMA solution for one hour and then rinsed in ethanol again.