# Open-Access Silicon Photonics Platforms in Europe

Abdul Rahim, Jeroen Goyvaerts, Bertrand Szelag, Jean-Marc Fedeli, Philippe Absil, Timo Aalto, Mikko Harjanne, Callum Littlejohns, Graham Reed, Georg Winzer, Stefan Lischke, Lars Zimmermann, Dieter Knoll, Douwe Geuzebroek, Arne Leinse, Michael Geiselmann, Michael Zervas, Hilde Jans, Andim Stassen, Carlos Domínguez, Pascual Muñoz, David Domenech, Anna Lena Giesecke, Max C. Lemme, Senior Member, IEEE and Roel Baets, Fellow, IEEE, Fellow, OSA

Abstract—Offering open-access silicon photonics-based technologies has played a pivotal role in unleashing this technology from research laboratories to industry. Fabless enterprises rely on the open-access of these technologies for their product development. In the last decade, a diverse set of open-access technologies with medium and high technology readiness levels have emerged. This paper provides a review of the open-access silicon and silicon nitride photonic IC technologies offered by the pilot lines of European research institutes and companies. The

Abdul Rahim, Jeroen Goyvaerts and Roel Baets are with the Photonics Research Group, Department of Information Technology, Ghent University imec and Center for Nano- and Biophotonics, Ghent University, Ghent B-9000, Belgium (e-mail: abdul.rahim@ugent.be, jeroen.goyvaerts@ugent.be, roel.baets@ugent.be).

Bertrand Szelag and Jean-Marc Fedeli are with the Commissariat à l'Energie Atomique et aux Energie Alternatives, University Grenoble Alpes and CEA, LETI, MINATEC Campus, F-38054 Grenoble Cedex, France (e-mail: bertrand.szelag@cea.fr, jean-marc.fedeli@cea.fr).

Philippe Absil is with Imec, Kapeldreef 75, 3001 Leuven (e-mail: absilp@imec.be).

Timo Aalto and Mikko Harjanne are with VTT, Tietotie 3, Espoo, Finland (e-mail: timo.aalto@vtt.fi, mikko.harjanne@vtt.fi).

Callum Littlejohns and Graham Reed are with Optoelectronics Research Centre, University of Southampton, Southampton, SO17 1BJ, UK (e-mail: c.littlejohns@soton.ac.uk, g.reed@soton.ac.uk).

Georg Winzer, Stefan Lischke and Dieter Knoll are with IHP Leibniz-Institut für innovative Mikroelektronik, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany (e-mail: winzer@ihp-microelectronics.com, lischke@ihp-microelectronics.com).

Lars Zimmermann is with IHP Leibniz-Institut für innovative Mikroelektronik, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany and Siliziumphotonik, Institut für Hochfrequenz- und Halbleiter - Systemtechnologien, Fakultät IV, Einsteinufer 25, 10587 Berlin, Germany (e-mail: lzimmermann@ihp-microelectronics.com).

Douwe Geuzebroek and Arne Leinse are with LioniX International BV, Hengelosestrat 500, Enschede the Netherlands (email: d.h.geuzebroek@lionix-int.com, a.leinse@lionix-int.com).

Michael Geiselmann and Michael Zervas are with LIGENTEC, EPFL Innovation Park C,1015 Lausanne, Switzerland (e-mail: michael.geiselmann@ligentec.com, michael.zervas@ligentec.com).

Hilde Jans and Andim Stassen are with Imec, Kapeldreef 75, 3001 Leuven (e-mail: hilde.ians@imec.be, andim.stassen@imec.be)

Carlos Domínguez is with Instituto de Microelectrónica de Barcelona (IMB-CNM, CSIC). Campus UAB. 08193-Bellaterra, Spain (e-mail: carlos.dominguez@imb-cnm.csic.es).

Pascual Muñoz is with Photonics Research Labs, Universitat Politécnica de Valencia, c/ Camino de Vera s/n, 46021 Valencia, Spain (e-mail: pascual.munoz@upv.es).

David Domenech is with VLC Photonics S.L., c/ Camino de Vera s/n, 46021 Valencia, Spain (e-mail: jose.domenech@vlcphotonics.com).

Anna Lena Giesecke is with AMO GmbH, Otto-Blumenthal-Str. 25, 52074 Aachen, Germany (e-mail: giesecke@amo.de).

Max C. Lemme is with RWTH Aachen University, Otto-Blumenthal-Str. 2, 52074 Aachen and AMO GmbH, Otto-Blumenthal-Str. 25, 52074 Aachen, Germany (e-mail: lemme@amo.de).

Roel Baets and Abdul Rahim coordinate ePIXfab, the European Silicon Photonics alliance.

Manuscript received December 21, 2018; revised Month xx, 20xx.

paper also highlights upcoming features of these platforms and discusses how they address the long-term market needs.

*Index Terms*—Silicon photonics, Silicon-on-Insulator, Silicon Nitride, CMOS, foundry, open-access, photonic integrated circuits, photonic manufacturing

#### I. INTRODUCTION

THE key asset of silicon photonics stems from its ability to provide compact form-factor, high-performance and low-cost *Photonic Integrated Circuits* (PICs) [1], [2]. Silicon photonics uses high-index contrast material systems for PIC manufacturing to provide dense and large-scale integration of complex photonic functions. Such high-index contrast materials require a manufacturing process that can ensure nm-scale process control to deliver high-performance PICs [3]–[5]. This allows silicon photonics to benefit from the existing and well-established *Complementary Metal-Oxide Semiconductor* (CMOS) manufacturing technology, which results in the low-cost manufacturing of PICs through economics of scale [7], [9]. The cost-effectiveness of silicon photonics even holds for modest volumes by using the existing CMOS-fabs that are fully loaded with electronics CMOS manufacturing [6].

The public and private investment in R&D has led to a rapid development of silicon photonics technologies in the last two decades. CMOS pilot lines and advanced research institutes [10]–[17] have played a pivotal role by: (a) continuously evolving and maturing the technology platforms to reach a high *Technology Readiness Level* (TRL)<sup>1</sup>; and (b) making these platforms accessible with minimal restriction and at low-cost to third parties for validating their design innovations. This open-access model enables an economically viable and low-barrier access to fabless companies where such companies bank on the off-the-shelf *Intellectual Property* (IP) and technology processes of pure-play foundries for PIC prototyping and manufacturing.

The open-access foundry model is one of the success stories of semiconductor electronics [18]. In Europe, CMOS pilot lines of advanced research institutes imitated this model for silicon photonics-based technologies. For example, ePIXfab – a joint initiative by imec in Belgium and CEA-LETI in France – hosted from Ghent University in Belgium, pioneered openaccess silicon photonics technologies in 2006 [7]. Later on this initiative expanded to include other European research

<sup>1</sup>The TRL-level of various open-access silicon photonics platforms discussed in this paper follows the definitions provided in the Appendix.

institutes [8]<sup>2</sup>. Followed by that, similar initiatives such as Optoelectronic Systems Integration in Silicon (OpSIS) [19], A\*STAR Institute of Microelectronics (IME) [16] and American Institute for Manufacturing Integrated Photonics (AIM Photonics) [13] have emerged to strengthen the open-access foundry model for silicon photonics.

Open-access silicon photonics technologies are offered in different modes of access. The type of access-mode can depend on: (a) the nature of innovation (i-e, academic or industrial) or (b) the phase of the design innovation (i-e, a proof-of-concept, prototyping or scale-up for manufacturing). For example, the Multiproject Wafer (MPW) approach is the mode where a user shares the design area with various other users. The sharing of the mask and fabrication cost among these users make MPW an excellent low-cost path for proofof-concept experiments at academic or industrial early stage R&D [6], [19], [20]. The platforms offered by MPW are versatile to address demands from a broad range of applications. Typically in MPW mode, each user gets a few tens of chips fabricated by using the generic baseline technology offered by the fab. On the other hand, through (customized) dedicated engineering runs an end-user gets the full reticle on a full lot of wafers (typically 20 to 25 wafers) with the optional flexibility to have customized processes to meet targeted specifications. Though considerably more expensive than MPW, they provide a large number of chips to determine the maturity of the design and fabrication process. As the PIC design meets the performance specifications, the customer may seek routes for low-, medium-, or high-volume manufacturing, depending on the needs of the application<sup>3</sup>. In some cases, CMOS pilot lines provide low- and medium-volume manufacturing of silicon PICs, typically up to several hundred wafers per order. With the growing industrial interest in high-volume manufacturing of silicon photonics products for telecommunication/datacommunication applications, which is the biggest driver for this technology since its inception, pure-play fabs have started developing open-access silicon photonics technologies [21]. In certain cases, the CMOS pilot lines and research institutes partner with pure-play CMOS fabs for the seamless translation from prototyping towards high-volume manufacturing [22].

While originally silicon photonics was synonymous for PIC-platforms based on *Silicon-on-Insulator* (SOI) wafers with waveguides with a silicon core, the field has diversified to some extent to include other material stacks that can be processed on silicon wafers in a CMOS-environment. Most noteworthy is the emergence of *Silicon Nitride* (SiN) platforms, in which the waveguide core is made of silicon nitride. More generally we see strong interest in heterogeneous platforms in which a variety of materials (III-V semiconductors, LiNbO<sub>3</sub>, polymers etc) are combined with SOI or SiN either through

front-end or through backend processes. The key unifying feature of silicon photonics is the capability to process PICs in a silicon technology environment on large wafers, typically 200 or 300 mm in diameter.

CMOS pilot lines and research institutes have acted as the gateway for the technological innovation in the field of silicon photonics. This paper provides a brief description of the various open-access technology platforms offered by European silicon photonics research institutes and companies<sup>4</sup>, the routes to access these technologies and the current status of these technology platforms. Each technology platform has features, which make it unique when compared with the other technologies. This diversity enables the uptake of silicon photonics technology for various emerging applications such as sensing and biophotonics [23], [24], light detection and ranging (LiDAR) for automotive industry [25], neuromorphic computing [26]–[28], machine learning [29], [30], quantum information processing [31], [32] and many more. The paper also highlights upcoming features in these technology platforms and how they are evolving to address the upcoming market needs.

#### II. SILICON-ON-INSULATOR TECHNOLOGY PLATFORMS

This section mentions the salient features of the open-access SOI-based technology platforms offered by various European fabs. The described platforms are diverse in terms of TRL ranging from 5 and upwards, access mechanism (i-e, directly from the fab or through a technology broker), the technology used for the fabrication of PICs (i-e., e-beam, Ultra Violet (UV), Deep Ultra Violet (DUV)) and the SOI material stack used (i-e, thin SOI with a thickness of the guiding layer ranging 220 nm to 500 nm and thick SOI with a thickness of more than 1  $\mu$ m). The turnaround time for these technology platforms through MPW runs depends on the type of the process flow and type of the fab. A full process flow, which includes monolithically integrated (high-speed) modulators, (high-speed) detectors and the back end of line process, in a CMOS pilot line typically takes at least six months from design submission to chip delivery. Design submission to chip delivery for a passive process flow in a CMOS pilot line takes around three months. A comparable process flow through rapid prototyping services takes two to three weeks delivery time. All fabs are striving continuously towards bringing down the turnaround time to meet the end- user expectations. Therefore, the above mentioned turnaround times may evolve to shorter times in the near future.

## A. imec's silicon photonics platform

imec, in collaboration with Ghent University, was among the first to demonstrate the power of DUV lithography for silicon

<sup>4</sup>ST Microelectronics' manufacturing platform, which is based on submicron SOI material system and has an integrated SiN layer, is not discussed in this review. The platform uses 193 nm immersion lithography and features high-performance passive devices, high-speed active devices and a capability for electronic IC and photonic 3D IC integration using a micropillar technology. ST Microelectronics does not provide open-access to its technology. It only provides restricted access to customers that align well with ST Microelectronics' business strategy.

<sup>&</sup>lt;sup>2</sup>Since 2015, the MPW services offered by ePIXfab have been transferred to Europractice IC Service. ePIXfab represents the European silicon photonics ecosystem and has transformed itself into the European Silicon Photonics Alliance with the mission to promote silicon photonics science, technology and applications (http://epixfab.eu).

<sup>&</sup>lt;sup>3</sup>The definition of manufacturing volume used here for silicon PICs is as follows: up to 50 wafers per order is termed as low-volume manufacturing, up to 500 wafers per order is termed as medium volume and beyond this is considered as high-volume manufacturing.

photonic ICs [3]. imec's ISIPP50G technology is based on a 130 nm CMOS node toolset. It uses SOI wafers with 220 nm thick guiding silicon layer with 2  $\mu$ m BOX in its 200 mm R&D pilot line. The technology includes 193 nm lithography for high fidelity patterning of a variety of passive devices possible due to the provision of three etch levels (one full and two partial etch levels). The technology uses optimized *Inductively* Coupled Plasma - Reactive Ion Etching (ICP-RIE) dry etch processes. It offers a poly-silicon overlay layer for highefficiency coupling to and from SOI chips. To achieve active functionalities, such as (high-speed) modulation, ISIPP50G platform offers four levels of P-type and N-type doping each. Photodetection is enabled by a low-defect epitaxially grown Germanium on silicon. The technology provides various features at the Back-End-Of-Line (BEOL) such as local removal of the dielectric stack for improving the coupling efficiency of the grating couplers and access to the Front-End-Of-Line (FEOL) and a deep etch through the full stack into the silicon substrate for fiber edge coupling.

imec's ISIPP50G technology finds a wide range of applications ranging from optical communication, sensing to spectroscopy. The technology has a high TRL of ≥7. The access to the technology is possible via MPW service provided by Europractice IC (http://www.europractice-ic.com/), which offers at least three MPW runs in a year. Moreover, imec also provides dedicated engineering runs as well as low-volume manufacturing.

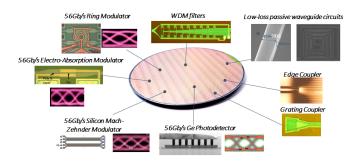

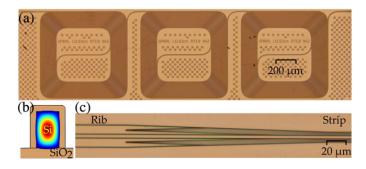

The components library of imec includes a wide variety of passive and active devices for O- and C-band applications. The three etch levels support strip waveguides (typical loss of 1.6 dB/cm for C-band) and rib waveguides (for C-band, typical loss of 1.1 dB/cm and 0.7 dB/cm for deep and shallow etched waveguides, respectively). A variety of grating couplers (1D, curved and high-efficiency grating couplers) are part of the component library. It also includes low-loss and broadband edge couplers. For splitting and combing of light, the library includes directional couplers and MMI couplers  $(1\times2 \text{ and } 2\times2)$  with a negligible power imbalance, good phase accuracy and small excess loss over the C-band. The key feature of imec's silicon photonics technology is the availability of 50G modulators and detectors for datacom/telecom applications operating in O- and C-band. The components library provides carrier depletion-based lateral PN junction Mach-Zehnder modulator (MZM) and ring modulator with an integrated thermal heater to tune the operating wavelength of the modulator. Recently, a compact Germanium Electro-Absorption Modulator (EAM) using the Franz-Keldysh effect is included in the component library. It provides up to 100 Gb/s modulation speed. The technology offers low dark current photodiodes with either high responsivity or high bandwidth to support up to 100 Gb/s data rates [33], [34]. An overview of the components offered by imec's ISIPP50G tecnology is shown in Fig. 1.

The capability to imec's ISIPP50G platform is illustrated by an ultra-dense  $16\times56$  Gb/s NRZ transceiver. It uses a multicore fiber to implement a short-reach optical link with a transmission capacity of 896 Gb/s. The transceiver has a form factor of  $1.47~\mathrm{mm}^2$  highlighting the dense photonic integration

Fig. 1. imee's fully integrated silicon photonics platform for 1310 nm/1550 nm wavelengths comprising low-loss passive waveguide devices, efficient fiber I/O and >50 Gb/s modulators and detectors.

using silicon photonics technology. The transceiver uses the GeSi waveguide electro-absorption device as a modulator and a photodetector. The 16-channels of the demonstrator are driven at 56 Gb/s and are tested sequentially. An open eye diagram with an SNR of 3.05 to 3.92 dB has been recorded at 1565 nm (L-band) when driven with 2.5  $V_{p-p}$  RF signal and -2.5 V reverse bias for the photodiode [35].

The *Process Design Kit* (PDK) is available via various EDA software vendors. The PDK contains the static GDS files, maturity levels and variability statistics of the library components. The PDK aids the designers for custom component designs by providing details of the technology, typical process tolerances, layer specifications and design rules. The future versions of the PDK will contain *Layout vs. Schematic* (LVS) verification to reduce design errors and *Lithography Friendly Design* (LFD) to improve the patterning predictability.

For the future, imec is developing efficient thermo-optic phase shifting elements by substrate undercutting. Such heaters can reduce the power consumption by a factor of 4. Furthermore, imec is developing technology to improve the performance of passive waveguide circuits through the integration of SiN in its technology platform.

To address the long-term market needs, imec, in collaboration with Ghent University, is actively engaged in developing technologies for low-cost integration of laser sources on its silicon photonics platform. As an example, transfer printing is developed for simultaneous transfer of multiple (semi-)processed III-V lasers from the source III-V wafer to the target silicon photonics wafer [36]. The technology promises massive richness of functionality and performance and allows for efficient use of III-V material.

# B. CEA-Leti's laser-integration compatible silicon photonics platform

Leti has developed a fabrication platform for silicon photonics-based circuits allowing large-scale integration of active and passive devices in a flexible CMOS compatible process. This platform provides more than silicon with the integration of a SiN layer and is compatible with III-V bonded epilayer on the same wafer, offering the advantages of each material. This convergence of different photonic platforms in this multi-materials process allows addressing various application needs with in the same platform.

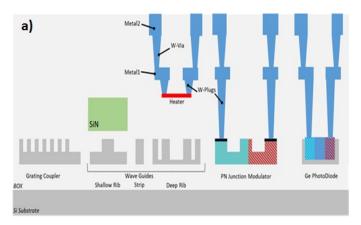

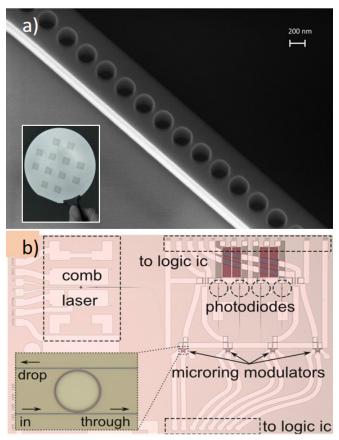

The silicon core process is based on an SOI wafer with a silicon film thickness of 305 nm. This thickness enables improved performance of passive devices as compared to the former 220 nm technology [37]. A modular approach is used to build the process flow that supports various sets of devices. Multi-level silicon patterning module allows the fabrication of waveguide with different slab heights, leading to different optical characteristics, which can be mixed inside the same die. A DUV 193 nm lithography mask level defines the most critical patterns. Up to eight levels of implantation are available in order to define the various type of lateral PNbased phase modulators. Modulation of up to 64 Gb/s has been demonstrated with this core silicon process [38]. Selective Germanium epitaxy is used to form the absorbing section of the device. The integrated photodiode is based on a SiGeSi architecture leading to a better light confinement compared to a full-Ge device [39]. A second optical layer made of SiN is integrated on top of the silicon. This layer can be used to design specific SiN-based devices or hybrid SiN/Si devices [40]. A two metal level BEOL is available with an integrated heater for thermal wavelength tuning of devices. Figure 2 (a) presents the cross section of the overall platform.

InP-based epitaxial layer can be integrated on top of the silicon layer of LETI's platform. Wafer or die bonding is available depending on the level of integration needed. Post-bonding fabrication is performed without downsizing the initial SOI wafer and using "CMOS-friendly" processes and materials allowing the large-scale integration of III-V based device on the mature silicon photonic platform (see Fig. 2 (b)).

The PDK supporting this platform proposes two device libraries containing a large set of devices to address O-band and C-band applications. The technology is accessible through the broker CMP (https://mycmp.fr/) with two MPW runs/year (without III-V integration) and has a TRL of ≥7.

The current focus of developments is on optimized hybrid laser designs taking into account the new capabilities offered by the CMOS compatible processes. Technology transfer to LETI's 300 mm fabrication line is ongoing. Advanced EIC/PIC integration solutions based on 50  $\mu$ m pitch microbumps are available for dedicated customers and projects. Furthermore, TSV integration on silicon photonic platform is under development. The overall platform is becoming versatile enough to address more than telecom/datacom applications. Application diversification is a crucial issue for the sustainability of the silicon photonics. New markets such as advanced computing, 3D sensing or cryptography can be targeted with LETI's silicon photonics platform.

## C. IHP's Monolithic Electronic-Photonic Platform

The goal of IHP's monolithic electronic-photonic integration platform is to deliver the integration of the basic components of electro-optic transceiver (i-e, modulator, driver, amplifier, photo-detector,...) on a single chip, which has SiGe *Hetero-Junction Bipolar Transistors* (HBTs) and PICs. IHP uses 200 mm SOI wafers with 220 nm guiding layer thickness on 2  $\mu$ m BOX for a platform providing monolithic *Electronic-Photonic Integrated Circuits* (EPICs). The platform uses DUV

Fig. 2. CEA-Leti's silicon photonics platform: (a) Cross section of the overall platform. (b) III-V die bonded on patterned silicon

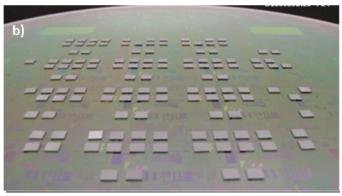

(KrF) and i-line 250 nm CMOS-baseline technology. The technology has a mixed electronic-photonic frontend with five metal layers at the backend (three thin and two thick) and cointegration with high-performance HBTs as shown in Fig.3.

The technology is developed for C- and O-band applications and has a TRL of  $\geq 7$ . IHP's high performance BiCMOS technology SG25H5-ePIC is available to academic and industrial users in MPW mode through Europractice IC. IHP also provides direct access to its technology through dedicated engineering runs. Key building blocks in IHP's EPIC technology are:

(i) nano-waveguides (etch depth 220nm, 120nm, 70nm) with loss between 1-3.5 dB/cm, (ii) *Standard Single Mode Fiber* (SSMF) compatible 1D grating couplers with a typical insertion loss of 4.5 dB, (iii) MMI based splitters/combiners (1×2, 2×2, 4×4), (iv) Carrier dispersion based phase shifters (lateral PN, lateral PIN), (v) linear lateral PN with  $V_{\pi}L = 2.8$  V.cm and 1.2 dB/mm @-1 V, (vi) thermal phase shifters, (vii) Waveguide coupled Germanium PIN detectors with responsivity = 0.9 A/W (internal), OE-S<sub>21</sub>3dB >60 GHz, dark current <200 nA @ room temperature, -2 V, (viii) HBTs with BV<sub>CEO</sub> = 1.65 V, f<sub>T</sub> = 220 GHz and f<sub>max</sub> = 290 GHz [12], [41], [42]. Figure 3 shows the cross section of IHP's EPIC technology.

Recently, IHP's technology has been used to demonstrate a novel Mach-Zehnder modulator that is monolithically integrated with drivers in a photonic BiCMOS technology. The MZM consists of two 6 mm long parallel phase shifting

Fig. 3. Cross-section of IHP's EPIC technology platform (image of the first generation EPIC technology with 30 GHz photo detector). Locally reconstructed bulk Silicon by using epi+CMP enables frontend-of-line integration approach of SiGe electronics with state-of-the-art SOI-based photonics.

elements. They are divided into 16 segments that are based on waveguide diodes and utilize the carrier dispersion effect to induce phase changes. The overall  $V_\pi$  of the modulator is 3.9 V at 1 V reverse bias and a fiber-to-fiber optical loss of 18 dB. The modulator driver is monolithically integrated with the modulator. The combined electro-optical  $S_{21}$  spectrum of the driver and modulator exhibits a slow roll-off with 3 dB and 6 dB bandwidth of 11 GHz and 36 GHz, respectively. The monolithically integrated modulator with a driver is used to demonstrate data transmission of net 300 Gb/s over 120 km SSMF. [43].

The PDK of the technology is developed for Cadence as well as TexEDA with fully featured electronic PDK, fundamental optical cells, electronic-photonic Design Rule Check (DRC), photonics-enabled LVS and script-based filler generation. Moreover, the PDK provides parametric building blocks and optical circuit simulation (optical S-Parameter + transient) using IPKISS. The upcoming features of the technology include higher performance HBT module integration, low-loss edge coupling and on-chip polarization management. In the long-term, IHP is striving to provide an integrated laser source on its EPIC platform. Regarding hybrid integration of other platforms, IHP collaborates with commercial partners. Solder bumping and copper pillars are available with 120  $\mu$ m and 70  $\mu$ m pitch, respectively. As for the photonic-electronic integration roadmap, IHP plans to provide co-integration with HBT performance of  $f_t/f_{max}$  of 300/500 GHz in the midterm future.

## D. VTT's Thick-SOI platform

The foundation for VTT's Thick-SOI technology platform is the Micronova clean room facility where the first silicon photonics components were designed in 1997, and fabricated a few years later. Today, the main technology platform is based on 3  $\mu$ m thick SOI where light is almost fully confined inside the Si core. The combination [44] of single-mode rib waveguides and multi-mode strip waveguides offers a unique combination of low losses ( $\sim$ 0.1 dB/cm), dense integration (bend radii 1-30  $\mu$ m) and small polarization dependence in effectively single-mode PICs. In addition to fully passive components, also thermo-optic phase modulators, plasma dispersion modulators and Ge photodiodes have been developed. Compared to the performance of similar devices in sub-micron

SOI, the performance of passive and thermo-optic components is often better, while the bandwidth of high-speed active components is much lower (well below 10 GHz).

Silicon photonics has become the most important driver for VTT to develop the Micronova clean room facility. 3  $\mu$ m SOI forms the basis for silicon photonics research and related small-volume manufacturing in Micronova. Continuous platform development covers TRL range 1-9. There is additional development on 12  $\mu$ m SOI for optical interposers between SSMF arrays and PIC chips.

VTT offers up to two MPW runs/year in 3  $\mu$ m SOI. Dedicated runs and other R&D services from design and process development to hybrid integration, packaging and chip/wafer level testing are carried out for customers around the world. They range from small university groups to large-scale companies. Contract manufacturing in Micronova is offered by VTT Memsfab, a separate company within the VTT group. Also, technology transfer and IP licensing are available. VTT provides direct access to its technology platform (www.vtt.fi/siliconphotonics).

The key building blocks in MPW technology are singlemode rib waveguides (~0.1 dB/cm), multi-mode strip waveguides (~0.15 dB/cm including bends), rib-strip converters (<0.05 dB) [44], Euler bends  $(<0.01 \text{ dB for } >20 \mu\text{m radius})$ [45], TIR mirrors (0.1-0.3 dB), thermo-optic phase modulators (<0.01 dB, >10 kHz, <25 mW/ $\pi$ ), PIN modulators  $(>1 \text{ MHz}, <5 \text{ mW/}\pi)$ , MMI couplers (0.1-0.2 dB), Mach-Zehnder interferometers, echelle gratings (1-4 dB), Arrayed Waveguide Gratings (AWGs) (2-5 dB) and dry-etched I/O facets with anti-reflection coatings ( $\sim 0.5$  dB coupling loss to lensed fibers). Dedicated runs also include up-reflecting mirrors with either 55° or 45° mirror angle (0.5-2 dB) and Ge photodiodes (<10 GHz). Hybrid integration mounts (with end-fire coupling) can be fabricated for various optoelectronic chips that are obtained either from the customer or from other service providers.

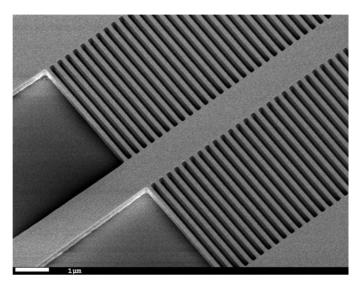

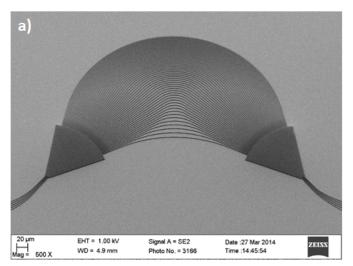

One key capability of the thick-SOI platform is to realize long and low-loss waveguide spirals in ultra-small footprint (see Fig. 4). They can be used to measure precisely the propagation loss of the waveguides and they have been used, for example, to demonstrate demodulators for phase-shift-keying [46], Faraday rotation [47] and *Instantaneous Frequency Measurement* (IFM). In particular, IFM has been demonstrated in collaboration with the University of Sydney and the results were reported in [48]. The 35 cm long waveguide spiral used in this demonstration is shown in Fig. 4 and it allowed to efficiently harness Kerr non-linearity and to demonstrate the first on-chip four-wave mixing-based IFM system. Achieved measurement bandwidth was 40 GHz and the frequency estimation error (root mean square) was as low as 0.8% of the full bandwidth.

Design support for 3  $\mu$ m SOI includes software-independent documents (platform overview, process description, design instructions and design rules) and software-specific PDKs for both Synopsys (up-to-date) and IPKISS (older version), as well as layer/technology setup files for KLayout and a GDSII example file with some model designs for key building blocks.

VTT is planning to add up-reflecting waveguide mirrors

Fig. 4. (a) Top view of a 35 cm long waveguide spiral. (b) Simulation of the fundamental mode for the 3  $\mu$ m  $\times$  1.875  $\mu$ m silicon strip waveguide. (c) Rib-to-strip converter for coupling to the fundamental mode [48].

$(45^{\circ})$  and Ge photodiodes as basic building blocks in future MPW runs. These enable wafer-level testing, VCSEL integration and on-chip power/signal monitoring. The present Au-Au thermal compression bonding will be complemented with solder-based flip-chip bonding to support a wider variety of optoelectronic and electronic chips to be hybrid integrated on 3  $\mu$ m SOI. In VTT's long-term vision, the plan is to extend the MPW offering to also include athermal multiplexers, fast modulators/photodetectors (>25 GHz), monolithic isolators/circulators and wafer-level (or chip-scale) packaging.

The most important functionalities that are frequently requested by the customers and not yet offered in the open access 3  $\mu$ m SOI platform are modulators and photodiodes with high bandwidth. These should reach at least >25 GHz and preferably >40 GHz. Different concepts for these are being developed in public-funded projects and some work has been done in industrial projects. Other frequently asked functionalities are low-loss coupling to large arrays of standard SM fibers with passive alignment and low-loss (1-2 dB), athermal multiplexing, polarization splitters, polarization rotators, isolators, circulators and various light sources. Some of these have already been demonstrated, but none of them is yet mature enough to be included as a standard building block in MPW runs.

# E. AMO's Silicon Photonics Platform: Full Custom Rapid Prototyping Services

AMO provides a rapid prototyping silicon photonics platform for passive and active devices based on SOI substrates. Process flows are individually adaptable to the customers needs (etch depths, cladding thickness etc.). The main fabrication line is based on 150 mm SOI wafers and includes passive photonic devices with low-loss cladding options and up to four different implantation steps, up to two metal layers including i.e. heaters and contacts (see Fig. 5). The devices can be either optimized for O- (1310 nm) or Cband (1550 nm). The photonic layer is highly customizable as its fabrication is based on electron-beam lithography. Active devices can be realized in a Mix & Match approach, i.e., high-resolution photonic layers are defined with e-beam and larger feature sizes for implantations, vias or metal are defined with projection lithography via i-line stepper. The silicon platform reaches TRL of up to 7 on full-wafer prototyping

Fig. 5. AMO's Full Custom Silicon Photonic Rapid Prototyping Platform: Flexible process flows; (a): High resolution photonic device layer (inset: finalized photonic wafer before dicing). (b) transmitter module for active optical cable application.

for ICT devices like transceivers [49], lab on a chip sensors or for hybrid integration of novel materials (i.e. graphene [50], [51]). AMO provides direct access (www.amo.de) to its silicon photonics technology platform and provides support in design and process flow to the end-users.

AMO's standard components are fabricated on SOI wafers with 220 nm top silicon layer on 3  $\mu$ m BOX. Passive building blocks are waveguides (strip, rip, slot), grating couplers, ring resonators, Mach Zehnder interferometers, directional couplers and spot size converters. Waveguide losses for strip waveguides lie between 0.5 dB/cm and 1.5 dB/cm depending on dimensions and cladding. Grating couplers have losses of around 2.5 dB (cladding dependent).

AMO is specialized in advanced prototyping targeting new device concepts and fabrication methods. High-speed transmitter modules have been fabricated [49], see Fig. 5(b), as well as ring resonator based 16  $\times$  1 packaged MUX/DEMUX for optical networks [52], high-speed graphene photodetectors [50] and many more. Device development resulted in ultraefficient silicon-based modulators with record low efficiency-loss products  $V_\pi L * \alpha$  [53]. This is enabled by mixing the standard fabrication processes for waveguides etc. with novel implantation strategies and by combining process simulation and fabrication results.

In the future, AMO is striving to develop more efficient fiber

Fig. 6. A suspended waveguide for mid-infrared applications using CORNERSTONE's silicon photonics technology.

to chip coupling options. This is key to broaden the fields of application of the silicon photonics technologies. New features may also be introduced through research contracts due to the high flexibility of the pilot line. Specific process steps can be realized to obtain targeted device performance, as AMO can develop the corresponding technology.

On a medium to long-term timescale efficient packaging technologies are necessary to bring the revolution of integrated photonic devices into more market segments. AMO is active to develop devices and platform interfaces which enable effective packaging in the future.

#### F. CORNERSTONE: Versatile wafer-scale prototyping

CORNERSTONE is a rapid prototyping MPW capability that utilizes industrially-compatible tools (e.g., deep-UV lithography), to enable seamless scaling-up of production volumes, whilst also retaining device level innovation capability using high-resolution lithography (e-beam) and versatile processes. The TRL 5 technology platform is a collaboration between the Universities of Southampton, Glasgow and Surrey in the UK, with the majority of the processing taking place in the Optoelectronics Research Centre's cleanrooms at the University of Southampton, where a 248 nm Nikon Scanner is installed. Lower TRL opportunities are also available for researchers and innovators to test experimental designs. Presently, CORNERSTONE offers three different SOI platforms (220 nm Si / 2  $\mu$ m BOX, 340 nm Si / 2  $\mu$ m BOX and 500 nm Si / 3  $\mu$ m BOX), enabling a plethora of applications including telecommunication, mid-infrared sensing (see Fig 6) etc. The unique hybrid processing (DUV projection lithography and e-beam lithography) capability renders the CORNERSTONE platform attractive to both academia and industry and can mimic advanced industrial processes.

CORNERSTONE is an open-access technology, which offers up to six MPW calls per year. In addition to that, dedicated fabrication batches are also available on demand. CORNERSTONE provides direct access to its

technology platform through the CORNERSTONE website: www.cornerstone.sotonfab.co.uk.

Utilizing patented self-alignment processing technology, the CORNERSTONE team have designed silicon carrier depletion modulators with data rates of beyond 56 Gb/s [54], [55]. With four implant layers, three Si etch depths and metallization steps, these designs are available in the active device MPW calls. Additionally, more frequent passive, or passive-withheaters, MPW calls enable the fabrication of complex silicon photonics circuits [56], with single-mode rib waveguide propagation losses as low as 2.5 dB/cm, and using the hybrid high-resolution e-beam lithography layer, high-efficiency grating couplers with insertion losses <1 dB [57]. The CORNER-STONE PDK is available using Luceda's IPKISS platform.

Additional capability will be added to the CORNERSTONE platform as it matures via other research projects within the consortium. Consequently, CORNERSTONE is continually adding more functionality for designers to exploit e.g. Ge photodetectors and silicon nitride.

The vision of the CORNERSTONE platform is to offer designers device level innovation capability using industrially compatible processes, at a rapid turn-around and an affordable cost. CORNERSTONE strives to introduce the latest research into its MPW capabilities by transferring technology currently under development as part of the significant number of ongoing research projects within the CORNERSTONE consortium.

#### III. SILICON NITRIDE TECHNOLOGY PLATFORMS

SOI is the most prominent material system for silicon photonics PICs. However, it is not transparent for wavelengths below 1.1  $\mu$ m and above 4  $\mu$ m. The success of SOI and the emergence of applications operating at visible and very-nearinfrared wavelengths triggered a growing interest in SiN-based "silicon photonics". SiN has a moderately high index contrast as compared to SOI. As a result, SiN-based silicon photonics out-competes SOI in the performance of passive devices in terms of propagation loss. Also, the thermal sensitivity and nonlinear properties of SiN outperform those of SOI. Even though low-speed active functions such as heaters are available in open-access SiN-platforms, they lack monolithically integrated high-speed devices, such as modulators and detectors, and thus rely on the integration of other materials for demonstrating these functions. Typically the turnaround time of SiN-based MPW takes up to three months from design submission to the delivery of chips. Generally, rapidprototyping fabrication services take shorter turnaround time than the CMOS pilot lines.

In the next sub-sections, SiN-based open-access platforms offered by various European institutes and companies are discussed.

#### A. Ligentec's thick SiN platform

LIGENTEC is a SiN photonics foundry. The Ligentec process is based on an all-nitride-core technology and designed from the bottom-up for photonics and modularity. In the all-nitride-core, most of the optical mode energy is in the waveguide material, which reduces loss (<0.1 dB/cm) and

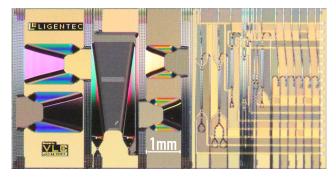

makes small bending radii ( $<10 \mu m$ ) possible. There are two processes available: the AN800 for the IR and the AN150 for visible and near-infrared wavelengths. Both processes are complemented by modules extending the integrated functionality. Those modules are (i) M1 for metal-based heaters, (ii) LoCA for local window opening facilitating sensing and bonding applications (sub-nm flatness for bonding area), (iii) X2 for multi-level nitride integration (<20 nm overlay accuracy), realizing true 3D photonic circuits and (iv) ExSpot a spot converter for single mode fiber coupling with 0.5 dB loss per facet. All-nitride-technology is using optical grade LPCVD SiN and oxide cladding materials. LIGENTEC is using DUV stepper technology for 150 nm applications in combination with etch techniques developed to improve the optical losses of the waveguides. LIGENTEC is capable of providing TRL 8-9 prototyping and low-volume fabrication services and has a fabrication partner to address high-volume customers.

LIGENTEC is an open-access foundry offering its all-nitride-core technology in MPWs and dedicated runs. Access is provided directly through LIGENTEC or through VLC Photonics, a strategic partner and a technology broker. In MPW runs both processes AN150 and AN800 are offered, but X2 and ExSpot modules are only available in dedicated runs. Main application areas are quantum and nonlinear integrated photonics, high-power LiDAR, bio-sensing as well as microwave photonics, datacom and laser metrology.

Key building blocks include the standard passive components such as ring resonators with Q-factors well above 1 Million (loaded), splitters with high accuracy, Mach-Zehnder interferometers, mode converters for SMF fibers or customized mode field diameters and 4-channel arrayed waveguide gratings with a footprint of only 1mm². Heaters are used for tuning of resonances of the resonators and phase modulation of Mach-Zehnder interferometers with efficiencies for a  $\pi$ -phase shift of around 100 mW. In addition to that, LIGENTEC offers the LoCA module, which enables cladding opening for accessing the evanescent field of the SiN waveguide for bonding or sensing applications.

Recently, a Chip Scale Optical Resonator Enabled Synthesizer (CORES) showed frequency synthesis with PIC components [58]. Several PIC components, ranging from laser, passive components and detectors are used to dial in the frequency of a tunable laser with the precision of less than one Hz. A LIGENTEC chip was used to generate a THz frequency comb in combination with an interposer function to integrate other materials such as Lithium Niobate and to connect different PIC components [59]. It has a first thick SiN circuit where high Q resonators enable nonlinear frequency generation [60]. On the same chip, the light is transferred to the second layer of thinner SiN, where the signals are routed to different outputs. Additionally, a bonding window is etched to allow for evanescent field coupling between the SiN and the bonded material. Heater elements could still be integrated for tuning.

Both LIGENTEC processes, AN800 and AN150, have a PDK. The PDK for the AN800 is designed for operation at 1550 nm, while for AN150 is designed for VIS-NIR operation. The PDKs are implemented in Synopsys and Luceda IPKISS,

Fig. 7. Two chips examples from LIGENTEC. The upper chip shows five compact AWGs (left) and PDK building blocks with heaters for 1550 nm operation. The lower chip shows spirals with losses below 0.05 dB/cm used as compact delay lines.

whereas DRC file is available in Mentor Graphics Calibre. Both PDKs are updated frequently with extended measurement data.

The integration of active elements with a low-loss platform is one of the most commonly required functionalities. The most common request is the integration of a light source and detection. LIGENTEC is planning to address this in the future with the inclusion of active elements. A second demand is for modulation using low power and compact footprint devices. The combination of speed, power, size and phase shift losses (including insertion) is a challenge that LIGENTEC addresses.

## B. LioniX International TriPleX platform

Since 2001, LioniX International commercially offers the SiN-based platform called TriPleX. The main characteristics of the platform are the ultra-low loss, broad wavelength range of operation (400 nm - 2350 nm) and the possibility to adapt the mode properties on the chip. The TriPleX waveguide platform is based on LPCVD processes and comes in several cross sectional types, optimized for specific applications [61]–[63].

The cross sections use one (single stripe) or multiple layers of LPCVD  $\mathrm{Si}_3\mathrm{N}_4$  to create waveguides with different properties. The single stripe cross section finds general application in fiber-mode matching at the edges of the chip, or in ultralow loss waveguides. The Symmetric-, Asymmetric Double stripe (SDS, ADS) as well as the box-shape cross sections have a moderate high index contrast allowing bend radii down to a few 10s of  $\mu\mathrm{m}$ . The SDS and ADS are optimized for one polarization, whereas the box-shape is optimized for both polarization states. Finally, the buried TriPleX structure allows

for thick waveguide layers and is used when high confinement is needed, for example in non-linear applications [61]. A key capability of the TriPleX technology is the tapering process to convert between different cross sections. For example, to taper from the ADS, allowing tight bends on chip, to the single stripe that is optimized for fiber coupling. LioniX offers the TriPleX waveguides on 100, 150 and 200 mm wafers, depending on the quantity needed. The ADS structure has a typical propagation loss of 0.1 dB/cm for  $\lambda$  =1550nm. For the single stripe record low losses of 0.1 dB/m have been demonstrated. [63].

The TriPleX waveguide platform is offered via dedicated runs as well as via open-access MPWs and can be accessed directly or via several brokers (i-e, JePPIX and PIX4life [64]). The platform is part of the vertically integrated offer of LioniX for product development as well as production runs, where design, manufacturing and assembly are integrated. Also, the MPW offering has a strong focus on assembly, for example by the characterization package that allows for easy assembly of a chip manufactured in an MPW.

The work-horse cross section at this moment (ADS) has a typical propagation loss of  $\sim\!\!0.1$  dB/cm. On-chip, the bend radius is as small as 25  $\mu \rm m$ , capable for micro-ring resonators. Fiber-to chip coupling sections are optimized to have  $<\!0.5$  dB per facet in-coupling loss. Along with design rules, templates to optimize packaging and standard building blocks such as directional couplers, y-splitters and thermo-optic phase elements, the MPW also offers a tunable laser module (tunable over 40 nm,  $>\!\!1$  mW output power) as a PDK building block whereby the user receives an assembled module including the InP integration.

TriPleX is used in a broad range of applications ranging from life science, tele- and datacom, quantum technology, to food and health [61]. A good demonstrator of the capabilities is the *integrated Optical Beam Forming Network* (iOBFN), shown in Fig. 8, for *Microwave Photonic* (MWP) systems [62]. This iOBFN is fully RF-in RF-out due to the hybrid assembly of lasers, photo-diodes and modulators. The tunable phase elements for the long delays are made in the TriPleX technology. The low-loss silicon-nitride waveguides combined with the InP sections are enabling this application.

For the MPW, a full PDK is available on the Synopsys Software and well as VPI Photonics platform. It contains the validated building blocks and design templates and rules for assembly of the chip. When one of the TriPleX technologies are used and not offered via MPW, an internal PDK library is used to support the customers in a first time right design.

The TriPleX waveguide technology is a mature siliconnitride platform that is serving several industrial customers. The platform is continuously improved, both by adding new basic building blocks (like AWG, or MMI) as well as by technology improvements. The most recent is the development of a new actuator principal, based on the stress-optic effect using piezo material (PZT) that has been introduced to dedicated runs. It is expected to be offered through MPW mode as well. The main advantage of PZT actuator is the large reduction in power consumption of the actuators from tens of mW down to several  $\mu$ W per actuator.

The TriPleX waveguide platform, especially combined with

Fig. 8. Commercial example of TriPleX waveguide technology: Integrated Optical Beam Forming network showing hybrid integration of TriPleX and InP elements into an MWP module for satellite communications.

hybrid integration of InP active elements is set to address many upcoming applications. The main challenge is the scaling of the assembly of photonic modules. The market will keep pushing the technology for lower losses, lower power and lower assembly costs. Novel markets, especially in the visible domain, require a different approach (market not used to working with chips), as well as improved assembly techniques as the shorter wavelength range requires an increased fabrication accuracy. The vertically integrated offer containing the TriPleX platform addresses these upcoming demands.

#### C. imec's BioPIX PECVD SiN platform

imec started in 2012 with the development of a SiN photonic platform named BioPIX. A PECVD SiN material with low losses in the visible and near-infrared range of the electromagnetic spectrum has been developed. Its low autofluorescent properties and the prospect of an ultra-high waveguide density by leveraging small mode sizes and very tight bending radii make this platform ideally suited for bio-applications, e.g. biosensing and DNA sequencing [65], [66]. In addition, the low-temperature deposition method (PECVD) used, makes this platform fully compatible with the BEOL of CMOS circuits. The latter enables monolithic integration of photonic circuits directly on top of CMOS wafers containing e.g., CMOS imagers or electronic circuits enabling more innovative life science applications, e.g., on-chip spectrometers [67], [68].

The BioPIX platform has further matured during the PIX4life project, which is a European funded pilot initiative for SiN photonics together with the accompanying supply chain focusing on visible light applications for life sciences. There are two flavors of the BioPIX platform, which are readily available: i.e., the BioPIX300 and BioPIX150. BioPIX300 is targeting wavelengths above 650 nm with a SiN core thickness of 300 nm whereas the BioPIX150 is meant for wavelengths between 450 nm to 700 nm with a SiN core thickness of 150 nm, all fabricated on 200 mm wafers. The current status of the technology is estimated to match a TRL

Fig. 9. The BioPIX platform gives the opportunity for components such as (a) spiral waveguides and (b) ring resonators to interface with biological samples through the use of the open-clad module, while also providing high performance standard components such as (c) compact Mach-Zehnder Inteferometers and (d) grating couplers for vertical interfacing, down to 388 nm wavelength on the BioPIX150 platform.

of 7. Figure. 9 gives an overview of a selection of components of the BioPIX PDK.

imec offers the BioPIX platform through dedicated wafer runs under bilateral agreements. Also, the BioPIX platform is accessible since 2018 through the PIX4life pilot line by means of MPW runs. The MPW service is offered at subsidized cost to external industrial and academic users aiming to launch new products in the life science area. The announcements of these runs and all necessary information for the customers can be found on the PIX4life website [64], [69].

PIX4life has enabled a portfolio of building blocks which is validated and available for the users in the respective PDK libraries of the platform. For example, various building blocks for shallow and deep etched waveguide layer have been fabricated and thoroughly tested. For each run, *Process Control Monitoring* (PCM) structures were implemented and measured using an automated wafer scale probe station. Building blocks are, but not limited to, rib and strip waveguides, grating couplers [70], evanescent couplers, splitters, MMIs, AWGs and ring resonators. Moreover, the imec BioPIX platforms offer a module where the top oxide cladding is removed selective to the SiN waveguides, in order to expose the bare SiN core material.

Further to those standard passive building blocks, thermooptic modulators, top metallization and edge coupling modules are currently under development. All the information regarding the basic building blocks performance, design, layer nomenclature, stack description with process variations are available within the PDK. The PDK of the BioPIX platform is part of the photonic design software packages offered by Luceda Photonics and Synopsys. A technology handbook including layer and stack descriptions and basic performance values of the process control monitoring structures is provided to the designers as well, especially for those who do not work with the above mentioned software packages.

To demonstrate the success of the technology, two demonstrators have been fabricated based on the BioPIX300 platform technology within the context of PIX4life. The first demonstrator is the on-chip *Optical Coherence Tomography* (OCT) imaging system for ophthalmology applications. This demonstrator is designed and developed by the industrial partners of PIX4life consortium and is intended for their future

OCT-products. New process modules such as thermo-optic modulators and edge couplers are incorporated in the circuitry of the OCT chip. The second demonstrator developed by the PIX4life consortium is a multi-degree of freedom or multi-DoF sensor for liquid or gas sensing applications. One of the target applications for this demonstrator is sweat analysis. This sensor is predominantly employing the clad opening module of the BioPIX technology.

To realize a prototype, PIX4life focuses on light integration options and general packaging solutions. More importantly, recently PIX4life intensified its collaboration with the PIXAPP pilot line for assembly and packaging (www.pixapp.eu). The aim is to integrate the necessary metallization steps and alignment structures on the BioPIX platform in order to allow smooth and easy packaging of the PICs within the PIXAPP pilot line.

In addition to packaging challenges, a challenge that is not tackled within the PIX4life pilot line, is the surface activation or pre-treatment for life science applications. For example, biosensing applications require an anti-fouling or bio-specific chemistry. These specific surface conditions should not alter during packaging, assembly or storage. However, the current photonic assembly and fabrication houses are not equipped for this. Furthermore, in the longer term, especially for the life science industry, it will be necessary to integrate photonic chips not only with electronics but also with microfluidics. The challenge will be the integration and assembly of all these components on a small footprint in a cost-effective way.

# D. AMO's Silicon Nitride Photonic Platform: Full Custom Pilot Line Services

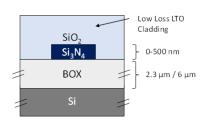

Recently, AMO has established a rapid prototyping SiN platform offering passive devices and actives, which are based on thermo-optic effect. Photonic devices in this platform are fabricated via projection lithography (i-line stepper) on 150 mm wafer equipment. The ultra-low loss platform uses Si handle wafers with 6  $\mu$ m thermal oxide and a top layer of LPCVD SiN (see Fig. 10). On top of the waveguide layer, a specially developed low-loss cladding is applied. Low-loss switches can be built by adding heaters to the design.

Key building blocks of the SiN platform are waveguides for 1550 nm and 800 nm as well as grating couplers for these wavelengths. Waveguide losses at 1550 nm are  $\sim 0.1$  dB/cm (cladding dependent). Directional couplers enable the precise functionality of Mach Zehnder interferometers for switches. The thickness of the waveguide layer can be customized from  $\sim 50$  to 500 nm. TRL 6-7 is reached within this platform. AMO provides direct access to its SiN platform and provides support in design and process flow to the end-users.

The SiN platform has been used to demonstrate *Synthetic Aperture Radar* (SAR) applications [71], plasmonic sensors [72] and integrated perovskite lasers [73], [74]. Variable optical attenuators, using graphene as active material, demonstrate the platform functionality at 855 nm [71]. Recently, true-time delay control of an optical beamforming network has been realized based on this platform [71]. This can be used for array antenna systems for SAR applications. Long waveguide

## Passive Si<sub>3</sub>N<sub>4</sub>

# Thermo-optics with Si<sub>3</sub>N<sub>4</sub> Electrodes Thermal Isolation Groove H1 SiO<sub>2</sub> Si<sub>3</sub>N<sub>4</sub> BOX

Fig. 10. AMO's Full Custom Rapid Prototyping Platform for silicon nitride photonics: left: Passive devices with customized Si3N4 waveguide dimensions. Right: Thermo-optical devices can be built either with metal heaters on top of the low-loss cladding (H1) or next to the waveguide (H2). Thermal isolation grooves improve the power budget for the heaters.

lengths of up to meter-scale can be utilized, which open the field of routing applications for efficient switches. With the help of plasmonic materials, highly integrated sensors with high-sensitivity were built [72]. Moreover, the first integrated perovskite lasers have been realized on top of AMO's SiN waveguides. The low-loss platform also enables integrated quantum photonic components.

AMO is investigating efficient fiber to chip coupling techniques as the availability of broadband and low-loss I/O is key to widen the range of applications. Further developments for AMO's SiN platform target the availability of active devices by integration of novel materials onto the platform.

#### E. IMB-CNM SiN Platform

The IMB-CNM is a moderate confinement SiN photonics integration platform aiming at covering a wavelength range from 400-3700 nm for photonic integrated applications such as biophotonics, tele/datacom and sensing (TRL $\geq$ 7) [76]. The photonic platform runs in the Integrated Micro- and Nanotechnology clean room hosted by the IMB-CNM (CSIC) parallel to a standard CMOS line. The infrastructure has 1500 m<sup>2</sup>, with Class 100 (ISO5) and Class 1000 (ISO6) areas.

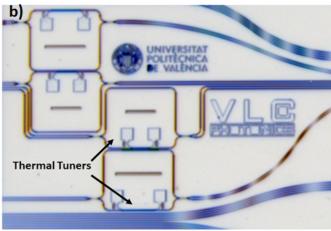

SiN waveguide structures are defined with CMOS compatible fabrication equipment. The process makes use of 100 mm (4 inch) Si wafers. The guiding cross sections for NIR wavelengths (C-Band) comprise three geometries: rib 150/300 height, ridge and mini-ridge having 300 and 150 nm thick Si<sub>3</sub>N<sub>4</sub> core layer, respectively. Figure 11 (a) shows an example of basic building blocks used. For the visible wavelength range, a rib cross section with a small rib height were used as basic waveguide structure. For both technologies, process technical features include thermo-optic tuners (Cr/Au) for optical modulation and selective area trenching for development of evanescent sensors. Figure 11 (b) shows a thermo-optic tuner developed within the platform. For the visible range, the waveguide basic structure comprises a 2.0  $\mu$ m thick BOX grown on a silicon substrate by thermal oxidation. On top of the BOX layer, a SiN layer deposited via by LPCVD, with a thickness of 150 nm, forms the propagation core. To work under single mode and enhance the confinement a rib waveguide is used. The technology includes the sensing well

definition level for direct interaction with the media in order to do the measurements.

The IMB-CNM SiN platform offers open-access in MPW mode and provides design support for design submissions. IMB-CNM is accessible directly or through VLC-Photonics. Two standard die sizes are available: M  $(5.0 \times 5.0 \text{ mm})$  and L  $(10.0 \times 5.0 \text{ mm})$ . At least 20 copies of each die are delivered to the users to be used as proof of concept for research or industrial prototypes.

The technology provides low-loss shallow waveguides with 0.3 dB/cm, deep waveguides for sharp bending with  $<50~\mu m$  radius,  $1\times2$  and  $2\times2$  MMI couplers with arbitrary splitting rations, tunable Mach-Zehnder and Sagnac interferometers Arrayed Waveguide Gratings with custom channel count and wavelength spacing/FSR, Echelles Gratings, ring resonators with Q-factors up to 1 Million, etc [77].

A key demonstration of IMB-CNM platform is the implementation of a field-programmable photonic arrays in a SiN chip [78]. The demonstrator employed an MPW run in the CNM platform to make a low-loss physical implementation of their novel concept. The circuit comprises multiple tunable Mach-Zehnder Interferometers arranged in a hexagonal mesh that will allow implementing multiple optical functionalities by exploiting the reconfiguration capabilities of the circuit by thermal tuners.

A PDK is available for the Synopsys Software platform, containing all the technology related information automatized for the design, simulation and layout of the user components, and the guidelines to submit contributions to the platform.

New process modules are under development to enable expansion of the platform from visible to mid-infrared wavelengths, increasing the functionality of the photonic integrated circuit to cover the biosensing and molecular spectroscopy applications. The modules are based in the experience gained by fabricating interferometric biosensors [79] and PICs for nanoscopy purposes working in the visible range [80].

There is on-ongoing research to design and demonstrate SiN membrane waveguide technology for broadband operation ( $\lambda$  range 0.4-6.7  $\mu$ m).

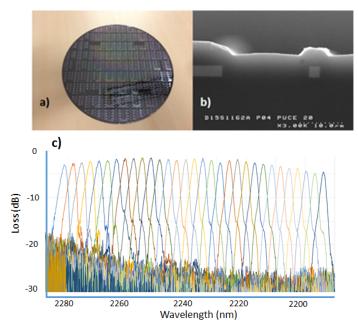

#### IV. LONG WAVELENGTH SILICON PHOTONICS PLATFORMS

In 2006, Soref proposed to expand the Si photonics technology to the long-wave infrared region, advocating that the cointegration of group IV photonics with appropriately designed III-V heterostructures, could be effectively translated to the Mid-IR wavelength band [3-12  $\mu$ m] to obtain fully integrated optical devices [81], [82]. The applications addressed by these technologies include free-space data communication, optical countermeasures, IR imaging of biological tissues, spectroscopy and many others. However, the most mature field of use is the detection of traces of chemicals in gaseous, liquid or solid phases. Due to its high absorption, silicon oxide is not allowed in this wavelength band. CEA-LETI has developed a technology platform for PIC fabrication based on SiGe materials on 200 mm Si wafers. For applications in the 3-8  $\mu$ m range, the waveguides are composed of a SiGe40% core surrounded by Si cladding. In the 8-12  $\mu$ m range, the

Fig. 11. (a) Arrayed waveguide grating, and (b) thermal tuners as an example of available components in the IMB-CNM platform.

waveguides are composed of a pure epitaxial Ge surrounded by SiGe cladding [83]. The TRL is around 5 to 6. VTT has also demonstrated low-loss (0.1-0.5 dB/cm) operation in both 4 and 11  $\mu$ m thick SOI waveguides at 3.4  $\mu$ m wavelength. Absorption in silicon oxide has been avoided by using an air cladding (see Fig. 12).

The technologies are accessible through the European MIR-PHAB pilot line via the website http://www.mirphab.eu/ and the broker CMP. It is an open access service with a focus on industrial users. Dedicated runs of a limited number of wafers are used for specific prototyping. Based on a design rule manual for each technology, the design can be optimized for each application.

For gas sensing applications with a need for combining different sources, many AWGs with a high number of inputs have been designed and produced. As an example, we report here results @  $4.5~\mu m$  with SiGe/Si technology. Basic passive devices (lines, bends, and splitters with Multi-Mode Interferometers) were first characterized in order to verify the quality of fabrication. The waveguide loss was measured by cut-back method using spirals waveguides [84] and is  $\sim 0.3~\text{dB/cm}$ . The Arrayed Wave Guide AWG is designed with 17 outputs and 35 input waveguides. The AWG exhibited a low-loss normalized

Fig. 12. Illustration of a Thick-SOI waveguide for mid-infrared sensing applications.

Fig. 13. (a) 200 mm SiGe/Si wafer for mid-IR PICs. (b) Cross section of the fabricated waveguides. (c) Transmission response of 31 channels of the AWG operating at mid-IR wavelengths.

transmission (-1.6 dB insertion loss) with a crosstalk below -12 dB (see Fig. 13). The maximum shift from channel spacing measured for the AWG central output was  $\Delta\sigma_{input22}=0.13$  cm<sup>-1</sup>, which is a 4 % variation from the designed 2.94 cm<sup>-1</sup> channel spacing.

Under the MIRPHAB and REDFINCH EU projects, these technologies are in permanent evolution in order to address many other application fields. Especially the introduction of other materials could give more versatility. For example, supercontinuum in the MIR could have an interest in spectrometers.

# V. EVOLUTION OF THE EUROPEAN SILICON PHOTONICS ECOSYSTEM

Silicon photonics draws its value proposition from the ability to demonstrate cheap and compact photonic *System on a Chip* (SoC). A mature technology platform with high TRL is one element to demonstrate high-density photonic

SoC using silicon photonics. Equally important are Electronic-Photonic Design Automation (EPDA) tools for the design of photonic SoCs, and advanced packaging and assembly tools/techniques to test them. In the last few years, the European silicon photonics ecosystem has consolidated to offer a complete supply chain to transform a design idea into a functional integrated photonic system. On the design side, the interoperability between physical level simulation tools, circuit level simulation tools, system-level simulation/emulation environments and electronic design tools has increased. Similarly, for the packaging and assembly aspects, a broad range of solutions have emerged. This includes techniques for fiber to chip coupling or PIC to PIC coupling, DC/RF electrical interfacing with PICs, assembly of electrical ICs and photonic ICs, handling of thermal and mechanical issues for packaging, and standardised test protocols. The above-mentioned packaging and assembly solutions for small volumes are provided by the PIXAPP packaging pilot lines. The pilot lines also provide scale-up routes towards larger volume silicon PIC packaging and assembly [6], [86].

#### VI. SUMMARY

Open-access of silicon photonics is of vital importance to enable the uptake of this technology by industry. The silicon photonics open-access model emulates the proven methodology used by electronics. In Europe, various types of open-access silicon photonics technologies are offered to address the needs of different market sectors. The maturity of the European open-access platforms enables routes for scalable volume manufacturing of PICs.

## APPENDIX

The TRL of open-access silicon photonics platforms discussed in this paper are defined by using the below defined criteria. The definitions of these TRLs are determined by translating the TRL definitions outlined by the European Commission [85].

- TRL 1, 2 and 3: not applicable

- TRL 4: PIC process flow successfully developed and demonstrated in a laboratory environment, typically with research-oriented tools

- TRL 5: PIC process flow successfully developed in an environment with manufacturing-grade tools or waferlevel prototyping tools

- TRL 6: PIC process flow successfully and reproducibly demonstrated (with a yield acceptable for prototyping) in an environment with manufacturing-grade tools or wafer-level prototyping tools

- TRL 7: Prototyping (including MPW-based prototyping or dedicated full-wafer prototyping) of market-relevant products by means of a PIC process flow that has been successfully and reproducibly demonstrated (with a yield acceptable for at least prototyping) in an environment capable of manufacturing or wafer-level prototyping

- TRL 8: PIC process flow qualified with respect to manufacturing requirements (yield, turn-around-time, quality assurance) in an environment capable of manufacturing

• TRL 9: PIC process flow used for competitive manufacturing at least at low and/or high-volume level

Hereby the following definitions are used for various openaccess modalities:

- MPW-based prototyping: up to 100 chips per order.

- *Prototyping:* typically one to a few wafers per order.

- Low-volume manufacturing: up to 50 wafers per order.

- Medium-volume manufacturing: up to 500 wafers per order.

- High-volume manufacturing: beyond 500 wafers per order.

#### REFERENCES

- M. Salib et al., Silicon Photonics, Intel Technology Journal, Vol. 8, Issue 2, p143-160, May 2004.

- [2] B. Jalali and S. Fathpour, Silicon Photonics, Journal of Lightwave Technology, vol. 24, no. 12, pp. 4600-4615, Dec. 2006.

- [3] W. Bogaerts et al., Nanophotonic waveguides in silicon-on-insulator fabricated with CMOS technology, Journal of Lightwave Technology, vol. 23, no. 1, pp. 401-412, Jan. 2005.

- [4] S. K. Selvaraja et al., Highly uniform and low-loss passive silicon photonics devices using a 300 mm CMOS platform, Proc. Opt. Fiber Commun. Conf. Exhib., San Francisco, CA, 2014, pp. 13. doi: 10.1364/OFC.2014.Th2A.33.

- [5] T. Mogami et al., High-performance silicon photonics process platform for low-power photonic integrated circuits, 2016 IEEE Silicon Nanoelectronics Workshop (SNW), Honolulu, HI, 2016, pp. 216-217.

- [6] A. Rahim et al., Open-Access Silicon Photonics: Current Status and Emerging Initiatives, in Proceedings of the IEEE, vol. 106, no. 12, pp. 2313-2330, Dec. 2018.

- [7] P. Dumon, Towards Fabless Silicon Photonics, Frontiers in Optics 2008/Laser Science XXIV/Plasmonics and Metamaterials/Optical Fabrication and Testing, OSA Technical Digest (CD) (Optical Society of America, 2008), paper FMG1.

- [8] P. Dumon and A. Khanna, Foundry technology and services for Si photonics, 2013 Conference on Lasers and Electro-Optics Pacific Rim (CLEOPR), Kyoto, 2013, pp. 1-2.

- [9] M. Hochberg and T. Baehr-Jones, Towards fabless silicon photonics, Nature Photonics volume 4, pages 492494 (2010).

- [10] P. Absil et al., Reliable 50Gb/s Silicon Photonics Platform for Next-Generation Data Center Optical Interconnects, 63<sup>rd</sup> International Electronic Device Meeting, San Francisco, CA, 2017.

- [11] B. Szelag et al., Multiple wavelength silicon photonic 200 mm R+D platform for 25Gb/s and above applications, Proceedings Volume 9891, Silicon Photonics and Photonic Integrated Circuits V; 98911C (2016); doi: 10.1117/12.2228744, Event: SPIE Photonics Europe, 2016, Brussels, Belgium

- [12] D. Knoll et al., BiCMOS silicon photonics platform for fabrication of high-bandwidth electronic-photonic integrated circuits, 2016 IEEE 16th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Austin, TX, 2016, pp. 46-49.

- [13] E. Timurdogan et al., AIM Process Design Kit (AIMPDKv2.0): Silicon Photonics Passive and Active Component Libraries on a 300mm Wafer, Optical Fiber Communication Conference, OSA Technical Digest (online) (Optical Society of America, 2018), paper M3F.1.

- [14] T. Aalto et al., 3 Micron Silicon Photonics, OFC 2018, San Francisco, CA, 2018, pp. 1-3.

- [15] T. Horikawa et al., A 300-mm Silicon Photonics Platform for Large-Scale Device Integration, IEEE Journal of Selected Topics in Quantum Electronics, vol. 24, no. 4, pp. 1-15, July-Aug. 2018, Art no. 8200415.

- [16] T. Liow et al., Silicon Modulators and Germanium Photodetectors on SOI: Monolithic Integration, Compatibility, and Performance Optimization, IEEE Journal of Selected Topics in Quantum Electronics, vol. 16, no. 1, pp. 307-315, Jan.-feb. 2010.

- [17] X. Chen et al., The emergence of silicon photonics as a flexible technology platform, Proceedings of the IEEE, 2018 (invited).

- [18] M. Hochberg et al., Silicon Photonics: The Next Fabless Semiconductor Industry, in IEEE Solid-State Circuits Magazine, vol. 5, no. 1, pp. 48-58, winter 2013.

- [19] A. E. Lim et al., Review of Silicon Photonics Foundry Efforts, IEEE Journal of Selected Topics in Quantum Electronics, vol. 20, no. 4, pp. 405-416, July-Aug. 2014, Art no. 8300112.

- [20] Andy Eu-Jin Lim et al., Path to Silicon Photonics Commercialization: The Foundry Model Discussion, Silicon Photonics III Systems and Applications Editors: Pavesi, Lorenzo, Lockwood, David J (Eds.), 2016.

- [21] P. De Dobbelaere et al. Advanced silicon photonics technology platform leveraging a semiconductor supply chain, 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2017, pp. 34.1.1-34.1.4.

- [22] G. Q. Lo et al., The foundry model for silicon photonics-technology, challenges, and opportunities, 2012 Conference on Lasers and Electro-Optics (CLEO), San Jose, CA, 2012, pp. 1-3.

- [23] A. Jovic et al., A MEMS Actuator System for an Integrated 3-D Optical Coherent Tomography Scanner, Journal of Microelectromechanical Systems, vol. 27, no. 2, pp. 259-268, April 2018.

- [24] Y. Li et al., Six-beam homodyne laser Doppler vibrometry based on silicon photonics, Opt. Express 26, 3638-3645 (2018).

- [25] C. V. Poulton et al., Coherent solid-state LIDAR with silicon photonic optical phased arrays, Opt. Lett. 42, 4091-4094 (2017).

- [26] A. N. Tait et al., Neuromorphic photonic networks using silicon photonic weight banks, Scientific Reportsvolume 7, Article number: 7430 (2017).

- [27] M. Lukosevicius et al., Reservoir Computing Approaches to Recurrent Neural Network Training, Computer Science Review, vol. 3, no. 3, pp. 127, 2009.

- [28] C.-S. Poon et al., Neuromorphic silicon neurons and large-scale neural networks: challenges and opportunities. Front. Neurosci. 5, 108 (2011).

- [29] N. C. Harris et al., Programmable Nanophotonics for Quantum Simulation and Machine Learning, Advanced Photonics 2017 (IPR, NOMA, Sensors, Networks, SPPCom, PS), OSA Technical Digest (online) (Optical Society of America, 2017), paper ITu3A.3.

- [30] Y. Shen et al., *Deep learning with coherent nanophotonic circuits*, Nature Photonics volume 11, pages 441446 (2017).

- [31] A. Peruzz et al., Quantum Walks of Correlated Photons, Science, 17 Sep 2010: Vol. 329, Issue 5998, pp. 1500-1503.

- [32] S. Paesani et al., Experimental quantum hamiltonian learning using a silicon photonic chip and a nitrogen-vacancy electron spin in diamond, 2017 Conference on Lasers and Electro-Optics Europe & European Quantum Electronics Conference (CLEO/Europe-EQEC), Munich, 2017, pp. 1-1.

- [33] M. Pantouvaki et al., 50Gb/s Silicon Photonics Platform for Short-Reach Optical Interconnects, in Optical Fiber Communication Conference, OSA Technical Digest (online) (Optical Society of America, 2016), paper Th4H.4.

- [34] P. Absil et al., Reliable 50Gb/s Silicon Photonics Platform for Next-Generation Data Center Optical Interconnects, 63<sup>rd</sup> International Electronic Device Meeting, San Francisco, CA, 2017.

- [35] P. De Heyn et al., *Ultra-Dense 16×56Gb/s NRZ GeSi EAM-PD Arrays Coupled to Multicore Fiber for Short-Reach 896Gb/s Optical Links*, in Optical Fiber Communication Conference, OSA Technical Digest (online) (Optical Society of America, 2017), paper Th1B.7.

- [36] J. Zhang et al., Transfer-printing-based integration of a III-V-on-silicon distributed feedback laser, Opt. Express 26, 8821-8830 (2018).

- [37] Dan-Xia Xu et al., Silicon Photonic Integration Platform Have We Found the Sweet Spot?, IEEE Journal of Selected Topics in Quantum Electronics, vol. 20, no. 4, 2014.

- [38] B. Szelag et al., Optimization of 64Gbps O-band thin-rib PN junction Mach-Zehnder Modulator fabricated on a 200mm silicon photonics platform, SSDM 2018.

- [39] L. Virot et al., Integrated waveguide PIN photodiodes exploiting lateral Si/Ge/Si heterojunction, Optics Express 25 (16), 19487-19496.

- [40] Q. Wilmart et al., Si-SiN photonic platform for CWDM applications, IEEE GFP 2018.

- [41] G. Winzer et al., Monolithic photonic-electronic QPSK receiver for 28Gbaud, 2015 Optical Fiber Communications Conference and Exhibition (OFC), Los Angeles, CA, 2015, pp. 1-3.

- [42] S. Lischke et al., Performance improvement of a monolithically integrated C-Band receiver enabled by an advanced photonic BiCMOS process, 2017 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), Miami, FL, 2017, pp. 50-53.

- [43] G. R. Mehrpoor et al., 64-GBd DP-Bipolar-8ASK Transmission over 120 km SSMF Employing a Monolithically Integrated Driver and MZM in 0.25-\(\mu\)m SiGe BiCMOS Technology, accepted for presentation at OFC 2019

- [44] T. Aalto et al., Low-loss converters between optical silicon waveguides of different sizes and types, IEEE Photonics Technol. Lett. 18, 709711 (2006).

- [45] M. Cherchi et al., Dramatic size reduction of waveguide bends on a micron-scale silicon photonic platform, Optics Express, 21, 17814-17823 (2013).

- [46] K. Vysrokinos et al., DPSK-Demodulation based on Ultra-Compact micron-scale SOI platform, Proceedings of the Optical Fiber Communication Conference (OFC, 22 - 26 March 2015, Los Angeles, US), paper W2A.14, OSA, 2015.

- [47] D. Jalas et al., Faraday rotation in silicon waveguides in 14th Int. Conf. Group IV Photonics (IEEE, Berlin, Germany, 2017), pp. 141142.

- [48] M. Pagani et al., Low-error and broadband microwave frequency measurement in a silicon chip, Optica, vol. 2, issue 8, pp. 751-756, 2015.

- [49] H. Fueser et al., 56 Gb/s WDM transmitter module based on silicon microrings using comb lasers, in CLEO: QELS-Fundamental Science, 2015, p. JTh2A-66., 2015.

- [50] D. Schall et al., Graphene photodetectors with a bandwidth 76 GHz fabricated in a 6" wafer process line, Journal of Physics D: Applied Physics 50.12 (2017): 124004.

- [51] D. Schall et al., Infrared transparent graphene heater for silicon photonic integrated circuits, Opt. Express, vol. 24, no. 8, p. 7871, 2016.

- [52] N. Iliadis et al., 16 × 1 Packaged MUX/DEMUX for Flexible-Grid Optical Networks, J. Light. Technol., vol. 35, no. 14, pp. 30503059, 2017.

- [53] A. L. Giesecke et al., Ultra-efficient Interleaved Depletion Modulators by Using Advanced Fabrication Technology, ECOC 2016; pp. 10671069, 2016.