# Worcester Polytechnic Institute Digital WPI

Doctoral Dissertations (All Dissertations, All Years)

**Electronic Theses and Dissertations**

2019-07-30

# A Highly Digital VCO-Based ADC With Lookup-Table-Based Background Calibration

Sulin Li

Follow this and additional works at: https://digitalcommons.wpi.edu/etd-dissertations

#### **Repository Citation**

Li, S. (2019). A Highly Digital VCO-Based ADC With Lookup-Table-Based Background Calibration. Retrieved from https://digitalcommons.wpi.edu/etd-dissertations/556

This dissertation is brought to you for free and open access by Digital WPI. It has been accepted for inclusion in Doctoral Dissertations (All Dissertations, All Years) by an authorized administrator of Digital WPI. For more information, please contact wpi-etd@wpi.edu.

# A Highly Digital VCO-Based ADC With Lookup-Table-Based Background Calibration

by

Sulin Li

A Dissertation

Submitted to the Faculty

of the

#### WORCESTER POLYTECHNIC INSTITUTE

In partial fulfillment of the requirements for the

Degree of Doctor of Philosophy

in

Electrical and Computer Engineering

by

July 30th 2019

APPROVED:

Dr. John A. McNeill, Dean of Engineering, Ph.D. Advisor

Dr. Michael C. Coln, Fellow, Analog Devices, Inc.

Dr. Ulkuhan Guler, Assistant Professor of Electrical and Computer Engineering

#### Abstract

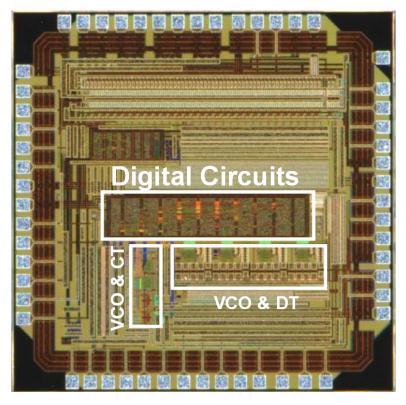

CMOS technology scaling has enabled dramatic improvement for digital circuits both in terms of digital speed and power efficiency. However, most traditional analog-to-digital converter (ADC) architectures are challenged by ever-decreasing supply voltage. The improvement in time resolution enabled by increased digital speeds drives design towards time-domain architectures such as voltage-controlledoscillator (VCO) based ADCs. The main challenge in VCO-based ADC design is mitigating the nonlinearity of VCO voltage-to-frequency (v-to-f) characteristics. Achieving signal-to-noise ratio (SNR) performance better than 40dB requires some form of calibration, which can be realized by analog or digital techniques, or some combination. This dissertation proposes a highly digital, reconfigurable VCO-based ADC with lookup-table (LUT) based background calibration based on "split ADC" architecture [1–3]. Each of the two split channels, ADC "A" and "B", contains two VCOs in a differential configuration. This helps alleviate even-order distortions as well as increase the input dynamic range. A digital controller on chip can reconfigure the ADCs' sampling rates and resolutions to adapt to the various application scenarios. Different types of input signals can be used to train the ADCs LUT parameters through the simple, anti-aliasing continuous-time input to achieve target resolution. The chip is fabricated in a 180 nm CMOS process, and the active area of analog and digital circuits is 0.09 and 0.16  $mm^2$ , respectively. Power consumption of the core ADC function is 25 mW. Measured results for this prototype design with 12-b resolution show ENOB improves from uncorrected 5-b to 11.5-b with calibration time within 200 ms (780K conversions at 5 MSps sample rate).

#### Acknowledgements

First of all, I would like to express my deepest gratitude to my Ph.D. advisor, Professor John McNeill. It has been a great experience for me to work with him at Worcester Polytechnic Institute (WPI) for the past four years. His vision and understanding of integrated circuit (IC) design has significantly influenced me during my Ph.D. life. I really learned a lot from him, not only about circuits, but also the mentality to be a good engineer. His patience, support and guidance in my research work and life, have helped me to become a strong independent researcher. I sincerely thank him for giving me the opportunity to work on this VCO-based ADCs. Without him, this dissertation would not have been possible.

I would also like to thank Dr. Michael Coln at Analog Devices. He is always very kind and patient and I really appreciated his advice on my research. I highly value his guidance to me when I had my internship with him. He opened a door for me in the world of complex ADC system design. Many of my ideas came from discussions with him.

I also want to thank Professor Ulkuhan Guler for her help, support, and guidance. I learned a lot when I was a teaching assistant of her advanced analog IC design class.

Many thanks to Long Pham for his help when I started this project. Many thanks to Jianping Gong for his advice and help in layout. I would also like to thank Ian Costanzo and Devdip Sen for their help and advice in PCB design. Thanks for William Appleyard for his help in soldering. I also want to thank Bob Brown and Edward Burnham for their assistant in Cadence maintenance. I also want to give special thanks to Ian Costanzo for his help and suggestions in grammar, syntax and style of my dissertation.

I am thankful for my friends Junqing Qiao and Yuteng Zhou for their help in

digital circuit design and chip test debugging. I really appreciate them for their encouragement which gave me a lot of power during my Ph.D. journey.

Last but not the least, I would like to thank my family, my wife Han, and my parents for their love, support, and encouragement.

# Contents

| 1              | Intr | oducti | ion                                                           | 2  |  |  |  |

|----------------|------|--------|---------------------------------------------------------------|----|--|--|--|

|                | 1.1  | Motiva | ation                                                         | 2  |  |  |  |

|                | 1.2  | Goals  |                                                               | 3  |  |  |  |

|                | 1.3  | Contri | ibution Overview                                              | 4  |  |  |  |

|                | 1.4  | Organ  | ization                                                       | 5  |  |  |  |

| 2              | Bac  | kgroui | $\mathbf{ad}$                                                 | 6  |  |  |  |

|                | 2.1  | ADC    | Characterization                                              | 6  |  |  |  |

| 2.2 ADC Errors |      |        |                                                               |    |  |  |  |

|                |      | 2.2.1  | Quantization Error                                            | 8  |  |  |  |

|                |      | 2.2.2  | Gain and Offset Error                                         | 10 |  |  |  |

|                |      | 2.2.3  | Differential Nonlinearity (DNL) & Integral Nonlinearity (INL) | 11 |  |  |  |

|                | 2.3  | VCO-   | Based ADC                                                     | 13 |  |  |  |

|                |      | 2.3.1  | VCO-Based ADCs Properties                                     | 15 |  |  |  |

|                |      | 2.3.2  | Other Works of VCO-Based ADCs                                 | 17 |  |  |  |

|                |      | 2.3.3  | Operating Principle of VCO-Based ADC                          | 19 |  |  |  |

|                |      | 2.3.4  | VCO-Based ADCs Nonideality                                    | 22 |  |  |  |

|                |      | 2.3.5  | Fundamental Limits on VCO-Based ADCs                          | 23 |  |  |  |

|                | 2.4  | Nonlin | nearity Mitigation Techniques                                 | 28 |  |  |  |

|   | 2.5 | Split ADC Concept                                   | 30 |

|---|-----|-----------------------------------------------------|----|

| 3 | Ana | alog Front-End Design                               | 32 |

|   | 3.1 | System Architecture of the proposed VCO-Based ADC   | 32 |

|   | 3.2 | VCO Choice for VCO-Based ADC                        | 35 |

|   |     | 3.2.1 LC Oscillator                                 | 35 |

|   |     | 3.2.2 Ring Oscillator                               | 36 |

|   | 3.3 | Phase Measurement Circuit                           | 47 |

|   |     | 3.3.1 Digital Up Counter                            | 48 |

|   |     | 3.3.2 Phase Sampler & Decoder                       | 51 |

|   |     | 3.3.3 Output Buffer                                 | 53 |

|   | 3.4 | Input Ports                                         | 54 |

|   |     | 3.4.1 Discrete-Time Input                           | 54 |

|   |     | 3.4.2 Continuous-Time Input                         | 56 |

|   | 3.5 | System Architecture of Analog Front-End             | 57 |

| 4 | Dig | ital Background Calibration                         | 61 |

|   | 4.1 | Clock Signal Generator                              | 61 |

|   | 4.2 | Lookup-Table-Based Correction                       | 64 |

|   | 4.3 | Digital Background Calibration Flow                 | 67 |

|   |     | 4.3.1 Error Estimation                              | 71 |

|   |     | 4.3.2 Least Mean Square Loop for Iterative Solution | 75 |

|   |     | 4.3.3 "Stitching" Estimation and LUT Adjustment     | 77 |

|   |     | 4.3.4 LUT Adjustment                                | 79 |

|   |     | 4.3.5 Offset Consideration                          | 80 |

|   |     | 4.3.6 Background Calibration Flow                   | 81 |

| 5            | Chi | p Mea               | surement and Results Analysis                            | 83  |  |  |

|--------------|-----|---------------------|----------------------------------------------------------|-----|--|--|

|              | 5.1 | rement Setup        | 83                                                       |     |  |  |

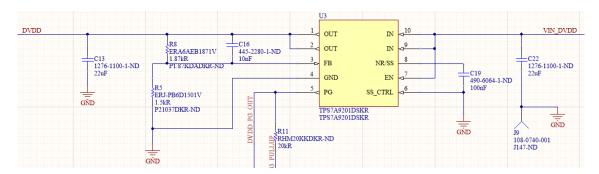

|              |     | 5.1.1               | Chip Introduction                                        | 85  |  |  |

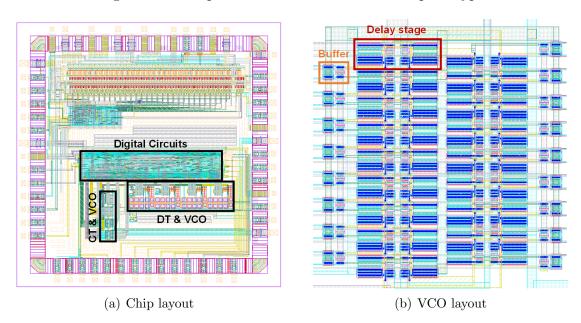

|              |     | 5.1.2               | Test PCB Design                                          | 87  |  |  |

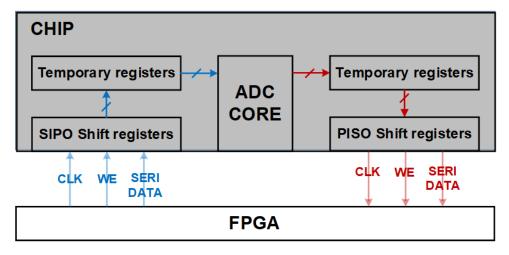

|              |     | 5.1.3               | FPGA Board DE2-115 Implementation                        | 89  |  |  |

|              | 5.2 | Measu               | rement Results                                           | 91  |  |  |

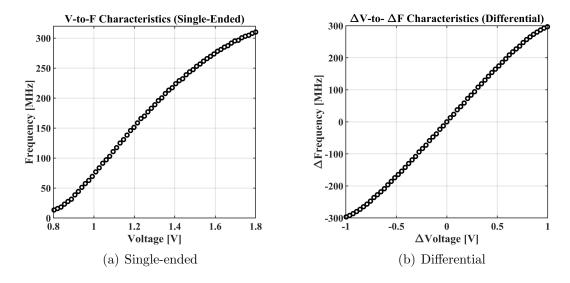

|              |     | 5.2.1               | VCO Measurement                                          | 91  |  |  |

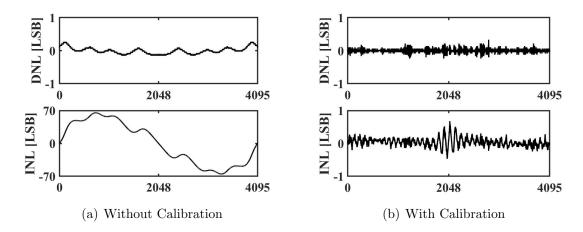

|              |     | 5.2.2               | A 12-bit Resolution ADC Analysis                         | 91  |  |  |

|              |     | 5.2.3               | Analysis of the Proposed VCO-Based ADC at Different CMOS |     |  |  |

|              |     |                     | Process Nodes                                            | 98  |  |  |

| 6            | Con | clusio              | ns                                                       | 102 |  |  |

|              | 6.1 | Future              | e Work                                                   | 103 |  |  |

| $\mathbf{A}$ | MA  | $\mathbf{TLAB}$     | Code                                                     | 105 |  |  |

|              | A.1 | LUT-E               | Based Calibration Algorithm                              | 105 |  |  |

|              | A.2 | DNL 8               | k INL Test                                               | 109 |  |  |

|              | A.3 | LUT (               | Correction                                               | 109 |  |  |

| В            | Ver | ilog Co             | ode :                                                    | 111 |  |  |

|              | B.1 | B.1 Clock Generator |                                                          |     |  |  |

|              | B.2 | Phase               | Measurement Circuits                                     | 115 |  |  |

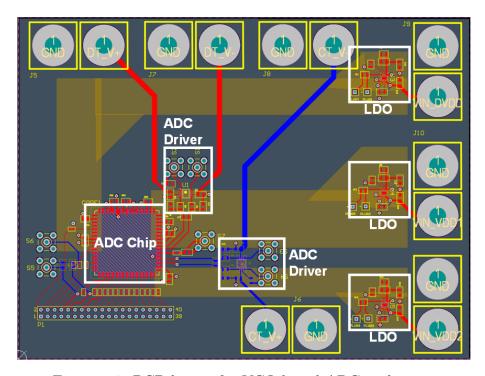

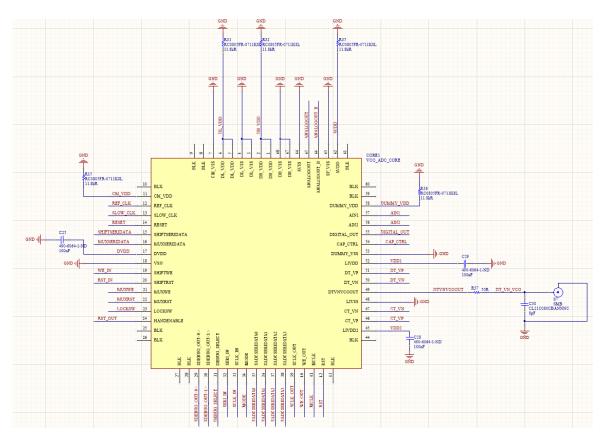

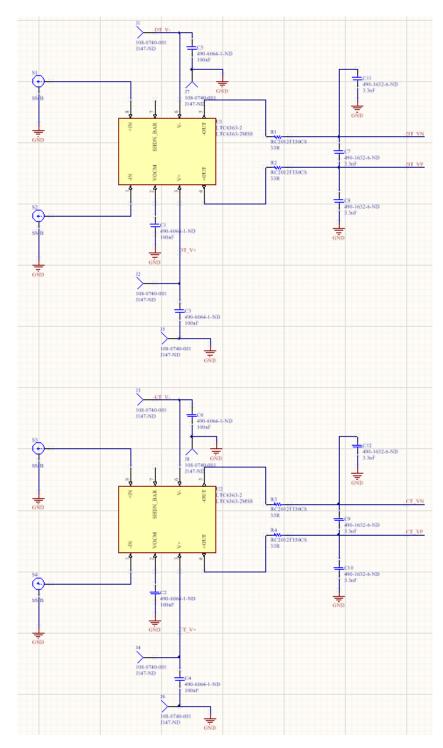

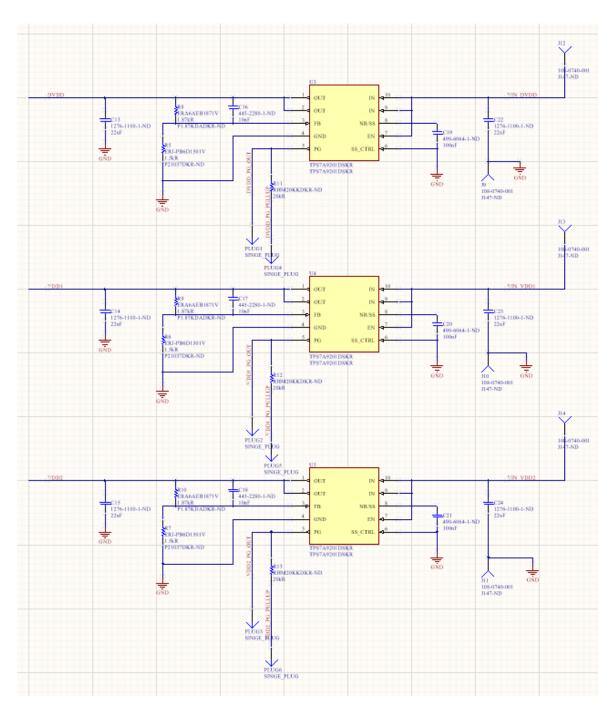

| $\mathbf{C}$ | PCI | B Sche              | matics                                                   | 134 |  |  |

# List of Figures

| 2.1  | ADC overview                                                                                               | 6  |

|------|------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Quantization error                                                                                         | 8  |

| 2.3  | Gain error                                                                                                 | 10 |

| 2.4  | Offset error                                                                                               | 11 |

| 2.5  | DNL                                                                                                        | 12 |

| 2.6  | $\operatorname{INL} \ \ldots \ldots$ | 12 |

| 2.7  | Walden FOM vs. Speed [4]                                                                                   | 14 |

| 2.8  | Equivalent systems (a) a generic VCO-based $\Delta\Sigma$ modulator, (b) the                               |    |

|      | cascade of a continuous-time low-pass filter, sampler, quantizer, and                                      |    |

|      | digital differentiator [5]                                                                                 | 16 |

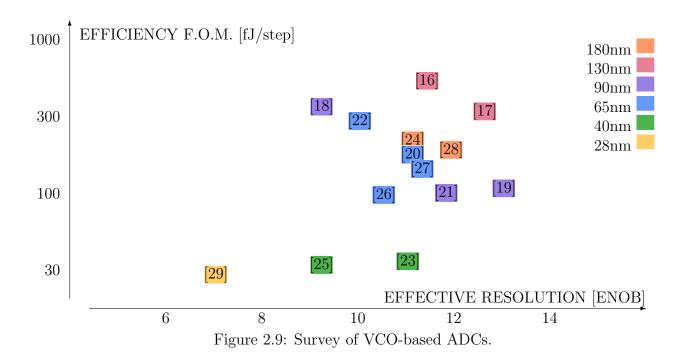

| 2.9  | Survey of VCO-based ADCs                                                                                   | 19 |

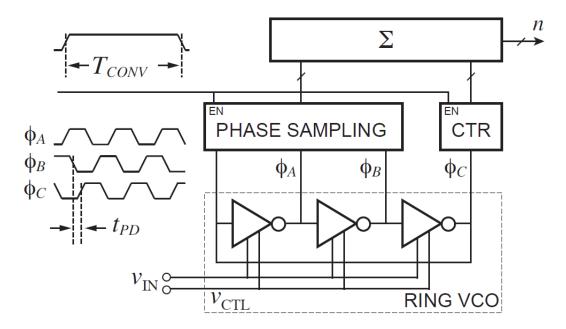

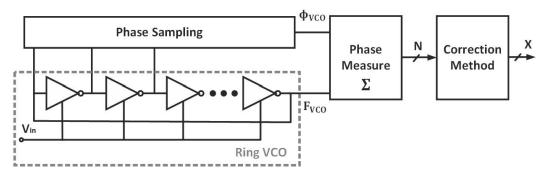

| 2.10 | Simplified VCO-based ADC structure                                                                         | 20 |

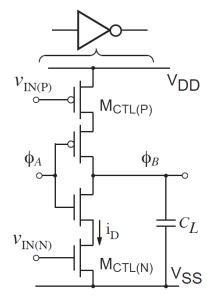

| 2.11 | Delay stage of VCO-based ADC                                                                               | 20 |

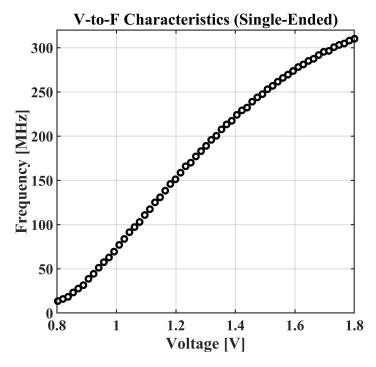

| 2.12 | V-to-f characteristics of 17-stage single-ended VCO in 180nm CMOS $$                                       | 22 |

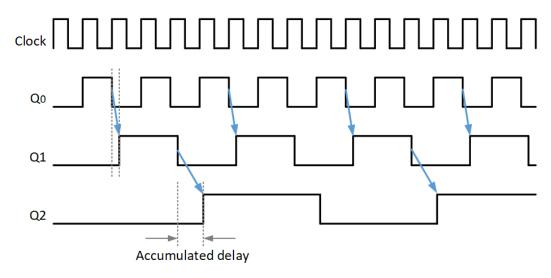

| 2.13 | Jitter accumulation in ring oscillaor                                                                      | 26 |

| 2.14 | Organization of architecture choices for VCO-based ADC                                                     | 28 |

| 2.15 | Split ADC architecture                                                                                     | 30 |

| 3.1  | System Architecture of the VCO-based ADC                                                                   | 34 |

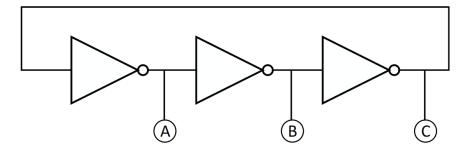

| 3.2  | 3-stage single-ended ring oscillator                                                                       | 37 |

| 3.3  | Delay stage of 3-stage single-ended ring oscillator               | 37 |

|------|-------------------------------------------------------------------|----|

| 3.4  | Waveform of 3-stage single-ended ring oscillator                  | 38 |

| 3.5  | Feedback system                                                   | 40 |

| 3.6  | Waveform of 3-stage and 9-stage single-ended ring osc             | 43 |

| 3.7  | Delay stage of current starved VCO                                | 44 |

| 3.8  | Pseudo differential ring VCO                                      | 46 |

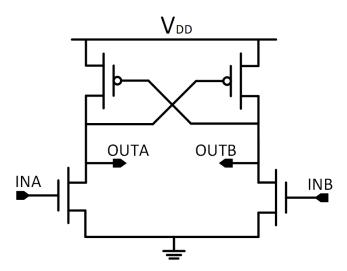

| 3.9  | Delay stage of pseudo differential ring VCO                       | 46 |

| 3.10 | Simplified VCO-based ADC structure                                | 47 |

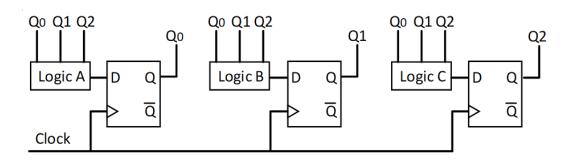

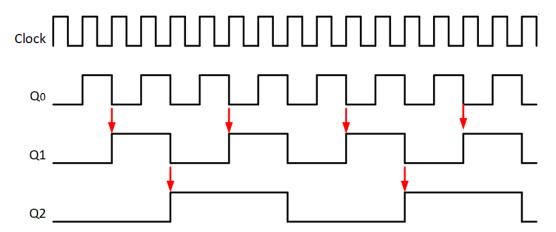

| 3.11 | Synchronous 3 bit counter using D Flip Flops                      | 49 |

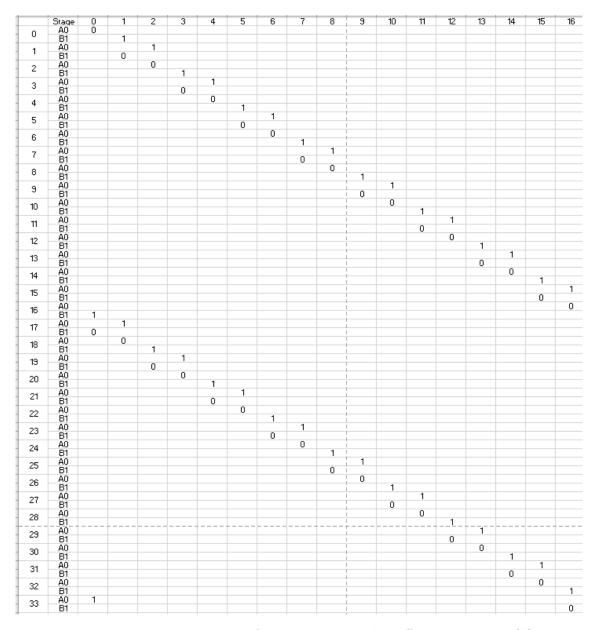

| 3.12 | Waveform of synchronous 3 bit counter                             | 49 |

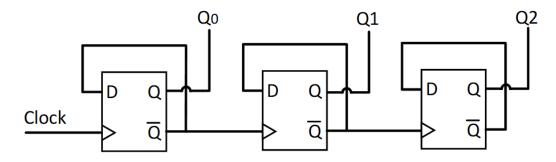

| 3.13 | Asynchronous 3 bit counter using D Flip Flops                     | 50 |

| 3.14 | Waveform of asynchronous 3 bit counter                            | 50 |

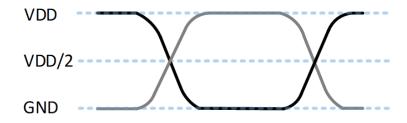

| 3.15 | Ideal pseudo differential swing                                   | 51 |

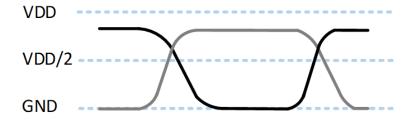

| 3.16 | Practical pseudo differential swing                               | 51 |

| 3.17 | Output buffer of pseudo differential ring VCO                     | 53 |

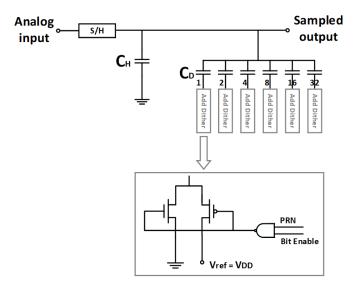

| 3.18 | Sample & Hold with dither implementation                          | 54 |

| 3.19 | CT input with dither implementation                               | 56 |

| 3.20 | System architecture of analog front end                           | 58 |

| 3.21 | Uniform quantization of 5-stage pseudo differential ring VCO      | 59 |

| 3.22 | Phase decoder for 17-stage pseudo differential ring VCO           | 60 |

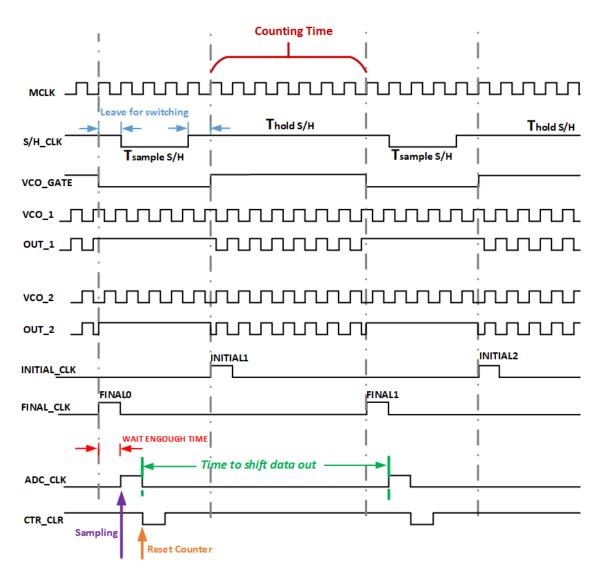

| 4.1  | Timing diagram of the ADC system                                  | 63 |

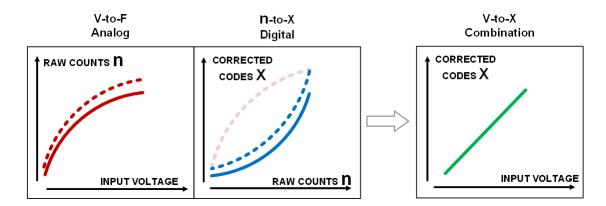

| 4.2  | Transfer functions of nonlinear VCO-based ADC with LUT correction | 64 |

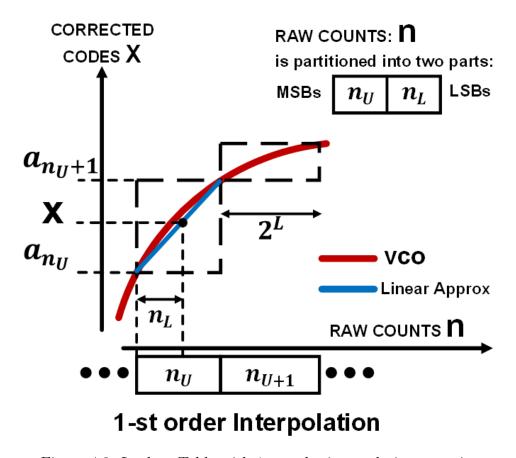

| 4.3  | Lookup Table with 1-st order interpolation corretion              | 65 |

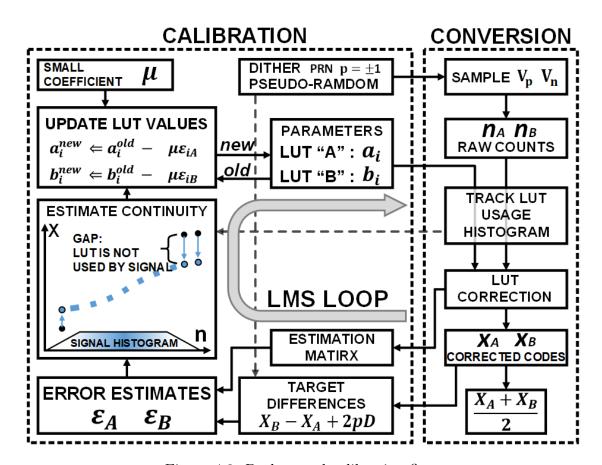

| 4.4  | Dithered "Split ADC" system block diagram [6]                     | 68 |

| 4.5  | Split ADC calibration with dither                                 | 70 |

| 4.6  | "Stitching" estimation for signal continuity in one ensemble      | 78 |

| 4.7  | Lookup-table adjustment                                                  |

|------|--------------------------------------------------------------------------|

| 4.8  | Background calibration flow                                              |

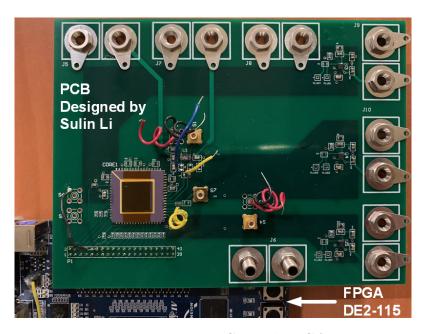

| 5.1  | Test PCB and FPGA                                                        |

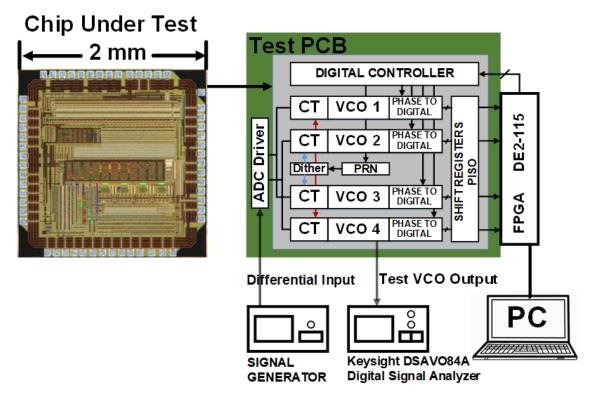

| 5.2  | Block diagram of measurement setup                                       |

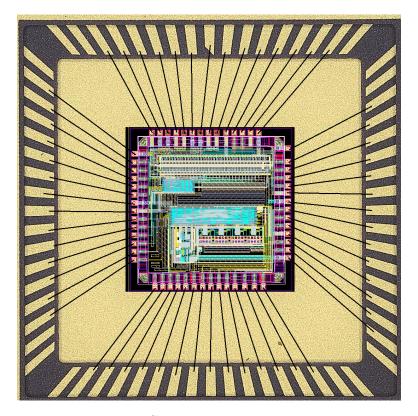

| 5.3  | Chip connection with package                                             |

| 5.4  | Die photo of the VCO-based ADC prototype                                 |

| 5.5  | Layouts                                                                  |

| 5.6  | PCB layout for VCO-based ADC evaluation                                  |

| 5.7  | Schematic of LDO                                                         |

| 5.8  | Schematic of ADC driver                                                  |

| 5.9  | Block diagram of the chip and FPGA connection 90                         |

| 5.10 | Waveform of VCO at $V_{in} = 1.8V$ (Maximum)                             |

| 5.11 | V-to-f characteristics                                                   |

| 5.12 | DNL & INL                                                                |

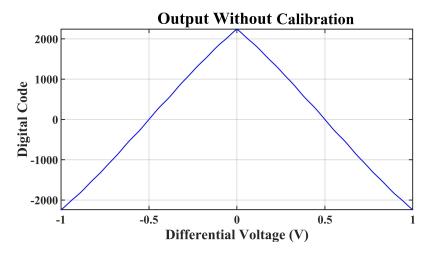

| 5.13 | Output (Without calibration) of triangle input                           |

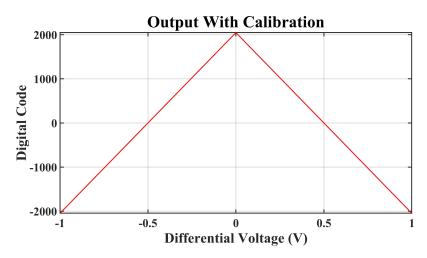

| 5.14 | Output (With calibration) of triangle input                              |

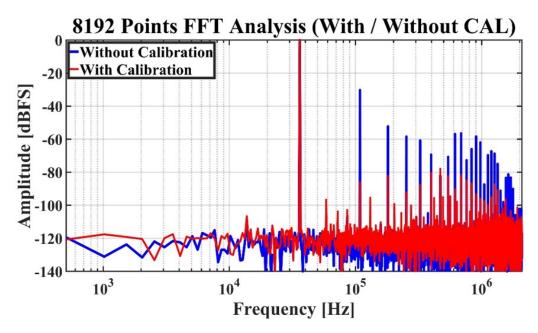

| 5.15 | 8192 Points FFT analysis                                                 |

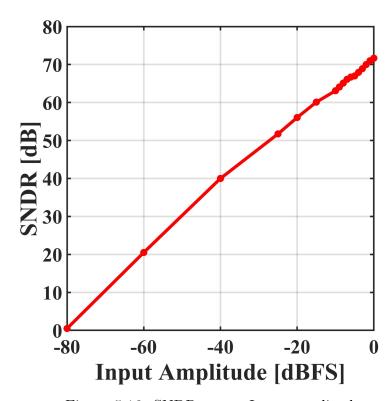

| 5.16 | SNDR versus Input amplitude                                              |

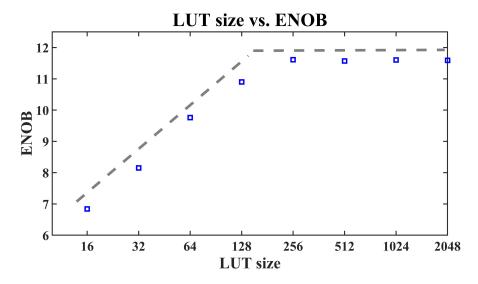

| 5.17 | LUT size versus ENOB                                                     |

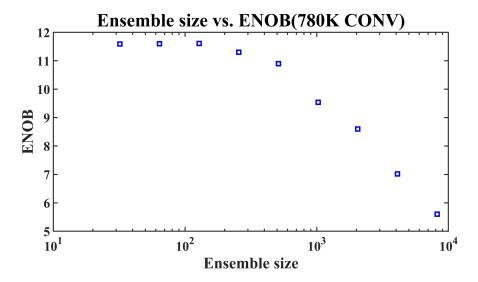

| 5.18 | Ensemble size versus ENOB (Other parameters are fixed) 97                |

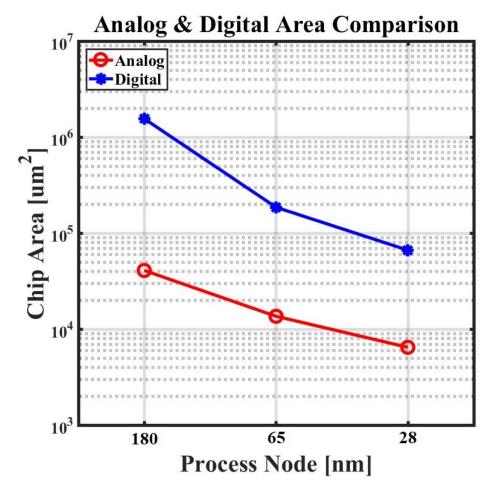

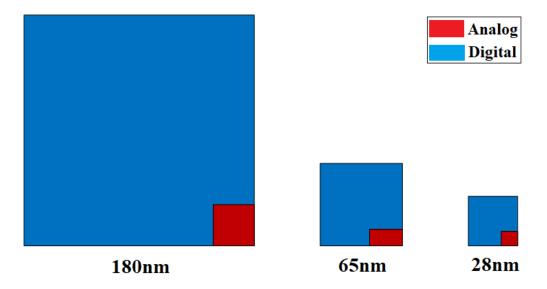

| 5.19 | Analog and digital area comparison in different CMOS process nodes 99    |

| 5.20 | Percentage of analog and digital area in different CMOS process nodes100 |

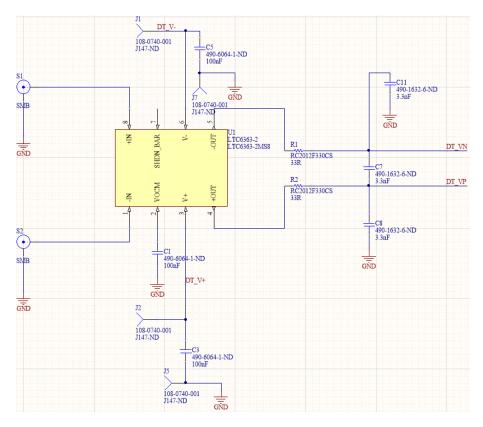

| C.1  | Test circuits around the chip                                            |

| C.2  | ADC drivers                                                              |

| C.3  | LDOs                                                                     |

# List of Tables

| 2.1 | Summary of other works of VCO-based ADCs | 18  |

|-----|------------------------------------------|-----|

| 5.1 | Analysis of Chip Area Comparison         | 98  |

| 6.1 | PARAMETER / RESULTS SUMMARY              | 102 |

# Chapter 1

# Introduction

## 1.1 Motivation

Analog-to-digital converter (ADC) is one of the popular and recurring themes in integrated circuits (ICs) these years. Different kinds of ADCs are used in various scenarios, building a bridge between analog world and digital processing. With the rapid development of microelectronic systems and scaling of CMOS technology [7–9], ultra-low-power ADCs are becoming one of the hottest topics in IC design. They are needed in many analog mixed-signal applications such as implanted biomedical devices, wireless communication, low power sensors, and even high speed wirelines, that demand high power efficiency.

Scaling of CMOS to nanometer dimensions has enabled large improvement in digital power efficiency, with lower power supply voltage and decreased power consumption for logic functions. However, most traditionally prevalent ADC architectures are not well suited to the lower voltage environment. Moreover, another advantage that come with the nanometer CMOS is its dramatically increased speed, which drives the traditional analog design to highly digital assisted mixed-signal system

design.

Thus, it will be a meaningful and valuable work to develop a novel ADC that takes advantage of nanometer CMOS technology. The large improvement in time resolution enabled by increased digital speeds drives the design towards time-domain architectures. Voltage-controlled-oscillator (VCO) based ADCs are one of the most favored ADC architecture nowadays. In contrast to classical ADCs, VCO-based ADC, which is a kind of time-based converter, transfers the continuous analog signal to time-doman signals by taking the advantage of the increased digital speed in nanometer CMOS.

A main obstacle in the VCO-based technique is linearizing the VCO voltage-to-frequency (v-to-f) characteristic. Achieving SNR performance better than 40dB requires some form of calibration, which can be realized by analog or digital techniques, or some combination. A further challenge is implementing calibration without degrading energy efficiency performance.

## 1.2 Goals

The goal of this Ph.D. work is to develop a highly digital VCO-based ADC with LUT based background calibration. Based on the calibratable "split ADC" architecture [1–3], a differential analog circuit configuration with real-time digital calibration system to linearize the VCO's v-to-f characteristics is proposed. The main challenge to design a good VCO-based ADC is to deal with the nonlinearity of VCO v-to-f characteristics. As described in Chapter 2, most other VCO-based ADC works usually use balanced analog and digital circuitry combination (e.g.,  $\Delta\Sigma$  loop, replica VCO, etc.) to achieve a good SNR. However, this work chooses a special method, using only simple analog circuitry with highly digital assisted calibration system

to alleviate the VCO's v-to-f nonlinearity. This dissertation not only introduce the background calibration algorithm but also provides the design flow of highly digital self-calibrating VCO-based ADCs. Because of the fast scaling of CMOS technology, the highly digital VCO-based ADC must be one of best ADCs in the future.

## 1.3 Contribution Overview

To summarize the contribution of the Ph.D. work, this section gives the overview of the related contribution in detail with corresponding publications.

In paper [10], the fundamental limits on energy efficiency performance of VCO-based ADCs are introduced, which include the limits from quantization and jitter. Analysis of a simplified model of the VCO-based ADC approach shows that there is an opportunity for order-of-magnitude improvement in efficiency F.O.M., with a quantization limit floor due to process energy per gate transition. Limitation due to oscillator jitter is expected to be appreciable only for ADC resolutions of order 12-13 bits, depending on process. Simulation results for a reconfigurable VCO-based ADC show conformance with theoretical predictions.

In paper [11], the specific circuit level design of the proposed highly digital VCO-based ADC is completed in 65 nm CMOS process. The proposed ADC is constructed according to split ADC calibratable architecture, and its novel and straightforward design by combining differential arrangement of VCOs and digital calibration engine provide another applicable option for VCO-based ADC creation. The variations of the VCOs v-to-f characteristics are analyzed through Monte Carlo simulation. The detailed calibration algorithm implementation in the digital circuit is also introduced. Simulation results in a 65 nm CMOS process show the propsed VCO-based ADC targeting 13-b resolution can achieve 12.5-b ENOB.

In paper [12], the related digital calibration system is developed and implemented for a delay lock loop (DLL) in 28 nm CMOS process. The two-step coarse and fine digital control circuit is used to mitigate the effects of jitter accumulation iteratively. The simulation results show the proposed DLL output can achieve  $\leq 0.1$ psrms jitter clock. The DLL can operate with input clock frequency from 2GHz to 10GHz, enabling interleaved ADC sampling with a low-jitter sample clock over a 20GHz to 100GHz frequency range.

# 1.4 Organization

This dissertation is organized as follows: Chapter 2 starts with the background of ADC characteristics and ADC nonideal behaviors. Then, the VCO-based ADC is investigated including its advantages and disadvantages. After that, the general "split ADC" concept is introduced briefly. Chapter 3 demonstrates a system architecture of the VCO-based ADC, providing a whole picture of the design. Then, the analog front-end of the proposed work is illustrated block by block. It consists of VCO choice, phase measurement circuits and input ports design implementation. Chapter 4 shows the background calibration and correction technique in detail, as well as introduces the design techniques when implementing the algorithm into real circuits. Chapter 5 introduces the measurement setup including test board design and test plan. Then, the measurement results are demonstrated in detail with quantitative analysis. Finally, Chapter 6 summarizes the research work presented and provides possible paths for future investigation in VCO-based ADC area.

# Chapter 2

# Background

## 2.1 ADC Characterization

Analog-to-digital converter (ADC) translates continuous-time signals into digital numbers to represent their discrete amplitude. This section introduces fundamental knowledge of the ADC as well as basic ideals of how an ADC works.

An ADC performs the conversion by sampling the real world analog signal periodically. The number of conversions that the ADC needs to convert analog input

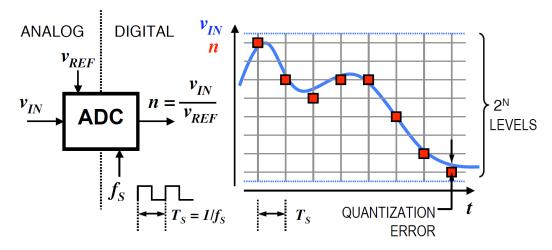

Figure 2.1: ADC overview

to a digital code within a specific time is called the sampling rate,  $f_s$ . For example, a 1kS/sec ADC collects one thousand samples in a second of time. As we can see in Figure 2.1, the blue line represents the analog input signal, and the red rectangular points represent the periodically sampled signal data. The time  $T_s$  between two adjacent data points is the conversion time. The sample rate is inversely proportional to conversion time,  $f_s = 1/T_s$ .

The resolution of an ADC is the number of output levels of quantizing an analog signal and it is given in powers of 2 as the output of a ADC comes in binary format. An N-bit ADC represents the analog input using  $2^N$  quantization levels. Right part of Figure 2.1 shows that the input signal range is divided equally into  $2^N$  levels. An ADC needs a reference voltage to digitize the analog signal and divides the reference voltage into small quantization levels. The smallest quantization level that ADC can resolve called the least significant bit (LSB) and it is defined as [13],

$$LSB = \frac{V_{FSR}}{2^N},\tag{2.1}$$

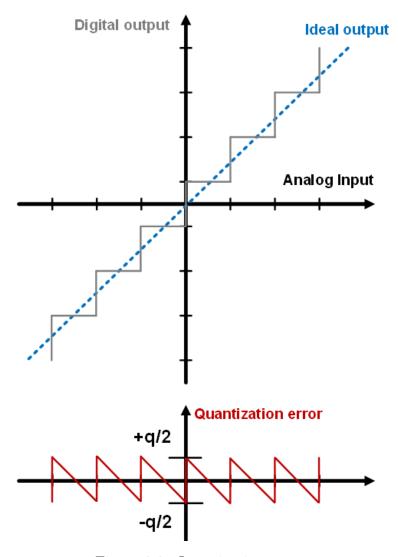

where  $V_{FSR}$  is full scale range (FSR) of input voltage. An ideal ADC transfer function is illustrated in the above plot in Figure 2.2. The Y-axis represents the ADC digital output and X-axis is the analog input. The quantized value of the analog input is represented by the diagonal staircase. The distance between two successive transition points is defined as 1 LSB.

## 2.2 ADC Errors

The source of ADC errors which affect the accuracy of ADC when it is transferring analog signals to the digital domain, can be described by quantization error, gain error, offset error and nonlinearity error including differential nonlinearity (DNL)

and integral nonlinearity (INL) [13,14]. They all can be expressed in least significant bit (LSB) units or sometimes as a percentage of the full scale range.

Figure 2.2: Quantization error

## 2.2.1 Quantization Error

In an ideal ADC system, when the analog input is quantized to a limited resolution of digital codes, error can appear between the analog input and the digital output. For example, a change in the input signal is smaller than the size of the ADC's LSB, that change can not be detected by the converter and then quantization error occurs.

Figure 2.2 illustrates the quantization error of an ideal ADC. In this example, the quantization level space is assumed as q. The sawtooth as error signal e(t) is the difference between the analog input signal and the quantized digital output signal. The maximum error an ideal ADC makes during the conversion is one half of LSB.

When we treat the quantization error e as having equal probability of lying anywhere in the range  $\pm q/2$ , its mean square value is given by,

$$e_{rms}^2 = \frac{1}{q} \int_{-q/2}^{q/2} e(t)^2 dq = \frac{q^2}{12}.$$

(2.2)

For a N-bit ADC, the full scale analog input sinewave  $V_{FS}$  can be expressed as,

$$V_{FS} = q \cdot 2^{N-1} \dot{s}in(2\pi ft). \tag{2.3}$$

Thus, the signal-to-noise ratio (SNR) for an ideal N-bit ADC is,

$$SNR = 20log \frac{V_{FS,rms}}{e_{rms}} = 6.02N + 1.76dB.$$

(2.4)

It is important to know that in equation (2.2), the RMS quantization error is estimated over the full Nyquist bandwidth, DC to  $f_s/2$ , where  $f_s$  is the sampling frequency. If the signal of interest has a smaller bandwidth (BW) or any noise shaping method is used to filter out the noise components, then a correction factor (called process gain) needs to be added to RMS quantization error equation. Therefore this correction factor results in increased SNR and we have,

$$SNR = 6.02N + 1.76 + 10log(\frac{f_s}{2 \times BW}). \tag{2.5}$$

where BW is the bandwidth of interest [13]. The equation (2.5) looks reasonable, because if sampling rate is larger than twice of input signal bandwidth, more unrelated quantization errors are accumulated in equation (2.4). Then a compensation term is added in equation (2.5).

#### 2.2.2 Gain and Offset Error

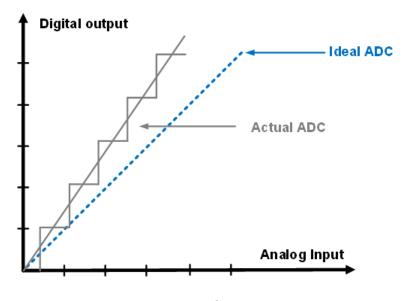

The gain error shown in Figure 2.3 is defined as the difference between the nominal and actual gain points on the transfer function after the offset error has been corrected to zero. For an ADC, the gain point is the midstep value when the digital output is full scale. The error represents a difference in the slope of the actual and ideal transfer functions and as such corresponds to the same percentage error in each step.

Figure 2.3: Gain error

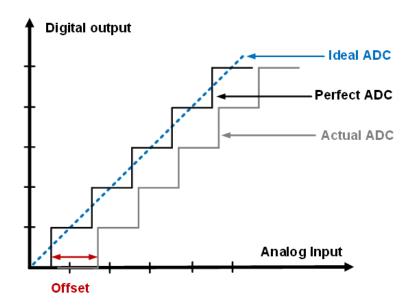

The offset error as shown in Figure 2.4 is defined as the difference between the nominal and actual offset points. In an ADC, the offset point is the midstep value when the digital output is zero. This error affects all codes by the same amount and

can usually be compensated for by a trimming process [14].

Figure 2.4: Offset error

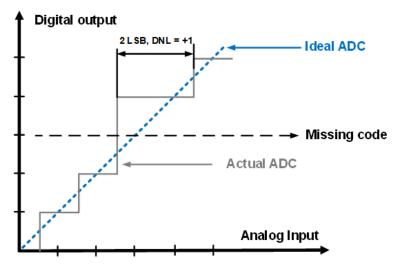

# 2.2.3 Differential Nonlinearity (DNL) & Integral Nonlinearity (INL)

The differential nonlinearity error (DNL) shown in Figure 2.5 is the difference between an actual step width and the ideal value of 1 LSB [13]. Therefore if the step width is exactly 1 LSB, then the differential nonlinearity error is zero. If the DNL exceeds 1 LSB, there is a possibility that the converter can become nonmonotonic. This means that the magnitude of the output gets smaller for an increase in the magnitude of the input. In an ADC there is also a possibility that there can be missing codes, for example, one or more of the possible  $2^N$  binary codes are never output.

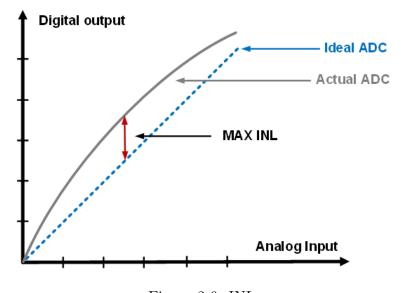

The integral nonlinearity error (INL) shown in Figure 2.6 is the deviation of the values on the actual transfer function from a straight line [13]. This straight line can be either a best fit straight line which is drawn so as to minimize these deviations or

Figure 2.5: DNL

it can be a line drawn between the end points of the transfer function once the gain and offset errors have been nullified. The name integral nonlinearity derives from the fact that the summation of the differential nonlinearities from the bottom up to a particular step, determines the value of the integral nonlinearity at that step.

Figure 2.6: INL

## 2.3 VCO-Based ADC

Many parameters characterize ADC design and performance, ADCs can be broadly described by:

**Resolution** Number of bits N in the ADC digital output, resolving the input into  $2^N$  quantization levels,

**Speed** Rate  $f_S$  at which ADC samples its analog input and updates digital output, **Power Dissipation** Power  $P_{DISS}$  consumed by the ADC from supply and any necessary voltage reference,

**Architecture** The organization of the internal ADC functional blocks.

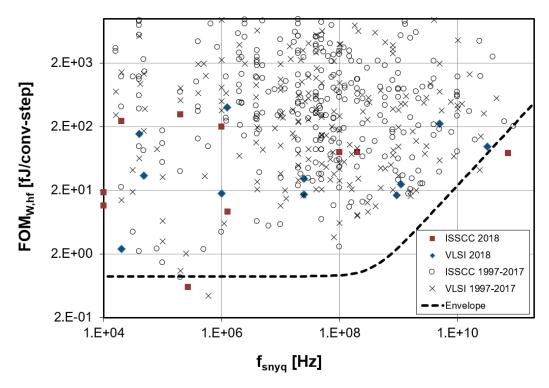

Design of ADCs is subject to challenging tradeoffs among resolution, speed, power consumption, and complexity. As a result several different ADC architectures have evolved, each suited to a different range of performance. The Walden figure-of-merit (F.O.M.) is commonly used to compare different ADCs, both within and across architectures, and it is defined by

$$FOM = \frac{P_{DISS}}{f_S \cdot 2^{ENOB}} \left[ \frac{J}{step} \right]. \tag{2.6}$$

In equation (2.6), resolution is expressed as effective number of bits (ENOB) defined by

$$ENOB = \frac{SNDR - 1.76dB}{6.02dB}. (2.7)$$

in which SNDR is the signal-to-(noise+distortion) ratio and is derived from equation (2.4) .

With the rapid development of ADCs, there are already large variety of different ADC architectures available for different requirements and applications. For example, flash ADCs are usually used in high-speed, low resolution scenarios, while  $\Delta\Sigma$  ADCs are the main choice for high-resolution, low-speed applications. As for the

theme of this dissertation, power efficiency is the most critical parameter that is being considered.

Figure 2.7: Walden FOM vs. Speed [4]

As we can see in the Figure 2.7, the Walden FOM vs. Speed of ADC survey from [4], due to the scaling of CMOS to nanometer dimensions, performance of ADCs are approaching to the lower value of Walden FOM. This is because the nanometer CMOS has enabled dramatic improvement in digital power efficiency, with lower supply voltage and decreased power consumption for logic functions. Thus, a novel ADC architecture called VCO-based ADC is proposed, which can take advantage of the high speed performance and low power consumption of nanometer CMOS technology.

This section consists of following materials: (1) simplified VCO-based ADC structure and its operating principle, (2) properties of VCO-based ADCs, (3) previous works of VCO-based ADCs, (4) fundamental limits of VCO-based ADCs, (5)

nonlinearity of VCO-based ADCs, (6) nonlinearity mitigation techniques.

## 2.3.1 VCO-Based ADCs Properties

The VCO-based ADC has several important properties making it as a popular candidate among other ADCs, especially in current nanometer CMOS technology. A detailed analysis of VCO-based ADCs' properties was published in paper [5,15].

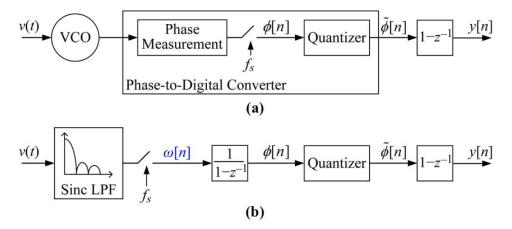

One property of VCO-based ADC is that the continuous time input behaves as a low-pass filter, which could be considered as an anti-aliasing filter [5]. Compared with traditional ADCs with discrete time input (sample and hold), it largely improves the ADC's performance. Ideally, the instantaneous frequency of the VCO can be expressed as,

$$f_{VCO}(t) = \frac{K_{VCO}}{2\pi} \cdot v(t), \tag{2.8}$$

where  $K_{VCO}$  is the VCO gain in radians per second per volt. The phase-to-digital converter quantizes the VCO phase (i.e., the time integral of the instantaneous frequency) and generates output samples of the result at times  $nT_s$  for n = 0, 1, 2,..., where  $T_s$  is the counting period.

As we can see in equation (2.9), the nth output sample of the phase to digital converter in radian is a quantized version of

$$\phi[n] = \int_0^{nT_s} K_{VCO} \cdot v(\tau) d\tau. \tag{2.9}$$

Equivalently, equation (2.9) can be written as

$$\phi[n] = \sum_{k=1}^{n} \omega[k] \tag{2.10}$$

where  $\omega$  can be expressed as (by integrating input signal in a constant period of time)

$$\omega[n] = \int_{(n-1)T_s}^{nT_s} K_{VCO} \cdot v(\tau) d\tau. \tag{2.11}$$

If the input signal is a sinusoidal function  $cos(2\pi ft)$ , where f is the input frequency.  $K_{VCO}$  is constant in the input signal range. If we consider a simple example when the phase is integrated from 0 to  $T_s$ ,

$$\omega[1] = K_{VCO} \cdot \int_0^{T_s} \cos(2\pi f \tau) d\tau = K_{VCO} \cdot \frac{\sin(2\pi f T_s)}{2\pi f}.$$

(2.12)

Thus,  $\omega[n]$  can be considered by passing through a low-pass filter as shown in equation (2.12). The system of Figure 2.8(b) is, therefore, equivalent to that of Figure 2.8(a). It obtains by sampling a filtered version of the input signal as described above and implements (2.10) as a discrete time integrator [5].

Another property that makes ring VCO-based ADC superior to other architectures is that the output of a ring VCO is digital in nature. The clock signal toggles

Figure 2.8: Equivalent systems (a) a generic VCO-based  $\Delta\Sigma$  modulator, (b) the cascade of a continuous-time low-pass filter, sampler, quantizer, and digital differentiator [5].

between two discrete levels, either VDD or GND. This property makes the VCO a great converter building block which takes advantage of the high performance nanometer CMOS technology without worrying about the decreasing power supply. In addition, since the amplitude of the VCO output does not play an essential role in the quantization process, the architecture greatly reduces the need of additional analog circuitry such as buffers and amplifiers, reducing chip area and power consumption.

What's more, the ring VCO-based ADC can be more reconfigurable than other structures. From equation (2.13) we see that resolution can be increased simply by allowing more time  $T_{CONV}$  for the conversion process. As long as the analog circuitry (e.g. Sample & Hold circuit, signal chain bandwidth) are compatible with desired sample and hold time, no reconfiguration of analog circuitry is required. To realize performance commensurate with the increased resolution, the digital back end must be designed with the capability for the maximum resolution required, but pushing the complexity of this trade-off into the digital domain is preferred in nanometer scaled CMOS.

In the end, the VCO-based ADC is inherently monotonic, and exhibits good DNL performance since it does not rely on any matching considerations to maintain local linearity of the ADC transfer characteristic. But INL performance does depend on the linearity of the VCO V-to-f characteristic, and will require some kind of correction.

#### 2.3.2 Other Works of VCO-Based ADCs

There are many different architectures of VCO-based ADC. The main focus of those works is trying to improve VCO-based ADC linearity.

Table 2.1 summarizes the reported performance for previously and recently pub-

lished work [16–29]. One technique is to employ the VCO as an integrator in a  $\Delta\Sigma$  modulator [17, 19, 20, 22, 24, 25, 27, 30–33]. Since the VCO is inside a feedback loop, the effects of VCO nonlinearity are reduced. However the technique requires a digital-to-analog converter (DAC) in the  $\Delta\Sigma$  feedback path and/or additional analog amplifiers; these go against the design philosophy of avoiding analog complexity in nanometer scaled CMOS. Another technique to improve linearity is to reduce input signal amplitude to avoid nonlinear portions of the transfer characteristic [34, 35], which imposes an SNDR penalty by reducing input signal range. Similarly, circuit techniques such as degeneration to linearize the voltage-to-current characteristic in a current-starved VCO [36] rely on open-loop analog behavior which is not well controlled in nanometer scaled CMOS.

Calibration can also be performed, but techniques reported to date use offline calibration [5, 15, 33, 37, 38] which requires additional precise circuitry and/or the ADC to be removed from the signal path, or use blind calibration techniques [31] which place restrictions on the content of the ADC input signal.

Table 2.1: Summary of other works of VCO-based ADCs

| Ref. | Year | Tech | $f_S$ | Bandwidth | SNDR | Power | Wal F.O.M | Area     |

|------|------|------|-------|-----------|------|-------|-----------|----------|

|      |      | [nm] | [MHz] | [MHz]     | [dB] | [mW]  | [fJ/step] | $[mm^2]$ |

| [16] | 2008 | 130  | 950   | 10        | 72   | 40    | 614       | 0.42     |

| [17] | 2009 | 130  | 900   | 20        | 78.1 | 87    | 330       | 0.45     |

| [18] | 2011 | 90   | 640   | 8         | 59.1 | 4.3   | 366       | 0.1      |

| [19] | 2012 | 90   | 600   | 10        | 78   | 16    | 120       | 0.41     |

| [20] | 2013 | 65   | 2400  | 37.5      | 70   | 39    | 196       | 0.08     |

| [21] | 2014 | 90   | 640   | 5         | 73.9 | 4.1   | 101       | 0.16     |

| [22] | 2014 | 65   | 1280  | 50        | 64   | 38    | 294       | 0.49     |

| [23] | 2014 | 40   | 1600  | 40        | 66.8 | 4.98  | 35        | 0.16     |

| [24] | 2014 | 180  | 35    | 3.5       | 70   | 5     | 272       | 0.4      |

| [25] | 2015 | 40   | 1600  | 40        | 59.5 | 2.57  | 42        | 0.017    |

| [26] | 2015 | 65   | 1000  | 30        | 65   | 8.2   | 94        | 0.62     |

| [27] | 2015 | 65   | 1200  | 50        | 71.5 | 54    | 176       | 0.5      |

| [28] | 2017 | 180  | 51.2  | 2.5       | 73.4 | 4.8   | 244       | 0.22     |

| [29] | 2019 | 28   | 5000  | 1780      | 45.2 | 22.7  | 30.5      | 0.023    |

## 2.3.3 Operating Principle of VCO-Based ADC

A VCO-based ADC is a time-based architecture which uses a VCO as an integrator converting continuous analog input to VCO phases which are then quantized by digital measurement circuitry [15].

Figure 2.10 shows a basic and simple VCO-based ADC. A ring VCO is usually used as the integrator to accumulate the phases since it is monotonic and has much lower power consumption comparing with other VCO structures like LC oscillator. The number stages of the VCO is considered according to specific conditions. For example, for single-ended ring VCO, there should be an odd number of stages. If a differential ring VCO is used, we can choose even number. A large number of ring VCO stages could reduce VCO frequency to the following counters, which could reduce some of the design difficulties such as static timing analysis. However, a

large number of ring VCO stages will cost more chip area and it might also induce overtone problems. The detailed discussion will be covered in Chapter 3.

The input  $v_{IN}$  of ADC is actually the controlling signal  $v_{CTL}$  to the VCO. When the input analog signal changes its value, it will consequently influence the frequency

Figure 2.10: Simplified VCO-based ADC structure

Figure 2.11: Delay stage of VCO-based ADC

of VCO. In other words, the control voltage changes the gate propagation delay  $t_{PD}$  or transition speed of phases in the VCO. The frequency-to-digital converter is essentially a phase measurement circuit: The ring phases  $\phi_A$ ,  $\phi_B$ ,  $\phi_C$  are sampled and the number of oscillator cycles is counted. The result at the end of the conversion time is the ADC output n, the total number of phase transitions observed in the time  $T_{CONV}$ . From the timing diagram in Figure 2.10, the output n is given by

$$n = \frac{T_{CONV}}{t_{PD}}. (2.13)$$

in which  $t_{PD}$  is the ring oscillator gate delay time.

To develop an expression involving  $v_{IN}$ , we need the v-to- $t_{PD}$  characteristic of the delay stage, which depends on the particular circuit architecture being used. Figure 2.11 shows a current-starved gate architecture, which we will use in this example. We can approximate the MOSFET drain current  $i_D$  during the gate delay time  $t_{PD}$  as

$$i_D = G_m \cdot v_{IN}, \tag{2.14}$$

where  $G_m$  is the slope of the  $V_{GS}$  to  $I_D$  relationship or transconductance for the  $M_{CTL}$  MOSFETs.

To develop the simplified operating principle of the VCO-based ADC, we temporarily make the assumption that this relationship is linear. Techniques for mitigating the effects of nonlinearity will be described in the following chapters. For a conservative approximation of the gate propagation delay, we apply charge conservation as the gate output drives the total load capacitance  $C_L$  over a peak-to-peak voltage swing of  $V_{DD}$  in time  $t_{PD}$  with drain current  $i_D$  as

$$i_D = \frac{C_L \cdot V_{DD}}{t_{PD}} \tag{2.15}$$

Combining equations (2.13), (2.14) and (2.15) gives for the output n,

$$n = \frac{T_{CONV}}{C_L/G_m} \cdot \frac{v_{IN}}{V_{DD}}.$$

(2.16)

From (2.16), it indicates that the output n is proportional to the input  $v_{IN}$ , which is the desired relationship for an ADC, building a bridge from continuous analog input to discrete digital codes.

## 2.3.4 VCO-Based ADCs Nonideality

Although VCO-based ADCs have attractive advantages and properties, there still exist a critical challenge to be solved before it can be used as a good ADC. Ideally, to build a workable ADC, we need to have a linear relation between analog input and digital output. In VCO-based ADC, the bridge from analog to digital is between

Figure 2.12: V-to-f characteristics of 17-stage single-ended VCO in 180nm CMOS

VCO controlling input and VCO ouput phases, which is called voltage-to-frequency characteristics. However, the v-to-f relationship is not linear as we expected.

Figure 2.12 shows the voltage-to-frequency characteristic of a 17-stage single-ended VCO, the structure of this VCO is demonstrated in section 3.2.2. When VCO input voltage is tuning from 0.8 to 1.8 V, the VCO's output frequency is increasing in a nonlinear form. This phenomenon can also be expressed in a mathematical way, the VCO gain  $K_{VCO}$  is no longer a constant, and it should be considered as value which will change according to the tuning region,

$$K_{VCO}(f) = \frac{\partial f_{VCO}}{\partial V_{in}}. (2.17)$$

This directly induces the nonlinearity into the ADC system, which highly degrades both static and AC performance of VCO-based ADC. Thus, mitigating the nonlinearity of v-to-f characteristics becomes the most important and challenging work in designing a good VCO-based ADC. In the later chapters, detailed design consideration of how to solve this problem will be demonstrated including both analog and digital techniques.

#### 2.3.5 Fundamental Limits on VCO-Based ADCs

This section investigates the fundamental limit achievable for efficiency of the VCO-based approach [10]. In the following subsections, the quantitative analysis of the VCO-based ADC will be demonstrated.

#### Quantization Limited

Before we start to analyze the VCO-based approach, we adopt the following assumptions: (1) VCO jitter is negligible over conversion time  $T_{CONV}$ . (2) Linearity

has been corrected such that ENOB is limited by unshaped quantization noise. (3) Power consumption is dominated by VCO. (4) Time resolution is limited by the gate delay  $t_{PD}$  (no phase interpolation used)

An advantage of analyzing the simplified VCO-based ADC of Figure 2.10 with these assumptions is that we can develop a simple expression for the fundamental limit on the efficiency figure-of-merit, defined as

$$FOM = \frac{Power}{f_s \cdot 2^{ENOB}}. (2.18)$$

To find this limit we need the power dissipation, sampling frequency, and effective resolution.

The worst-case maximum power dissipation will occur for the maximum current  $i_D$ , which from (2.15) will occur for the minimum gate delay  $t_{PD(MIN)}$ :

$$i_{D(MAX)} = \frac{C_L \cdot V_{DD}}{t_{PD(MIN)}} \tag{2.19}$$

which gives for *Power*,

$$Power = i_{D(MAX)} \cdot V_{DD} = \frac{C_L \cdot V_{DD}^2}{t_{PD(MIN)}}.$$

(2.20)

To find the limit of best achievable performance for the effective-number-of-bits expression  $2^{ENOB}$ , we will use the ADC resolution  $n_{MAX}$ , the maximum number of counts n. Using  $t_{PD(MIN)}$  in equation (2.13) we have,

$$n_{MAX} = \frac{T_{CONV}}{t_{PD(MIN)}}. (2.21)$$

Combining equation (2.18), (2.20), (2.21),

$$\frac{C_L \cdot V_{DD}^2}{t_{PD(MIN)}} \cdot T_{CONV} \cdot \frac{t_{PD(MIN)}}{T_{CONV}} \Rightarrow FOM = C_L \cdot V_{DD}^2$$

(2.22)

The result in equation (2.22) also indicates benefits of the VCO-based ADC approach:

- (1) Scaling friendly: the ADC efficiency F.O.M. from (2.22) is the same as the energy per gate transition figure of merit, the reduction of which is the goal of digital scaling. Also, from equation (2.21), we see that achievable resolution in a given conversion time  $T_{CONV}$  will improve as  $t_{PD(MIN)}$  decreases at smaller geometry nodes.

- (2) Reconfigurable resolution: equation (2.21) we see that resolution can be increased simply by allowing more time  $T_{CONV}$  for the conversion process. No reconfiguration of analog circuitry is required.

- (3) Efficiency F.O.M. is independent of resolution: from (2.22) we see that the efficiency figure-of-merit depends only on the supply voltage  $V_{DD}$  and the gate load capacitance  $C_L$ . So if the ADC is reconfigured for a different point in the speed-resolution trade-off space, the efficiency F.O.M. should be unchanged.

#### VCO Jitter Limited

In general, the quantization noise portion of SNDR can be improved by increasing ADC resolution. The ability to trade an increase in conversion time for improved resolution without reconfiguring hardware is an advantage of this technique. As resolution increases, however, at some point noise performance will be limited by some fundamental aspect of the analog to digital conversion process. In this case, since we have moved A/D conversion into the time domain, a possible limit on ADC noise performance is oscillator jitter. Jitter-limits the ability of the VCO to measure time accurately. In this section we drop the assumption of negligible VCO jitter;

this can be considered a time domain approach complementary to the frequency domain approach of [15].

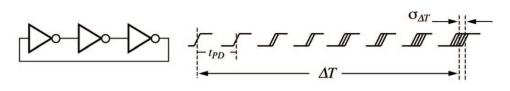

Figure 2.13: Jitter accumulation in ring oscillaor

Figure 2.13 shows how jitter accumulates over a time interval  $\Delta T$ . For a VCO-based ADC, the time delay  $\Delta T$  in equation (2.23) is the conversion time  $T_{CONV}$ . Since the jitter in separate delay stages is caused by noise in different MOS devices, we can assume the added noise in each stage to be independent, so the RMS jitter increases proportional to the square root of delay [39, 40] and can be characterized by a figure of merit  $\kappa$ ,

$$\sigma_{\Delta T} = \kappa \sqrt{\Delta T}.\tag{2.23}$$

The difficulty with noise occurs as we attempt to increase resolution  $n_{MAX}$  by lengthening  $T_{CONV}$  as indicated in equation (2.21). From equation (2.21) and Figure 2.13 we can see that the rms jitter of the VCO will also keep increasing. To find the contribution of jitter to ADC noise as  $T_{CONV}$  increases, we express the time error of in ADC counts n by dividing by the gate delay  $t_{PD}$ ,

$$\sigma_n = \frac{\sigma_{\Delta T}}{t_{PD}} = \frac{\kappa \sqrt{T_{CONV}}}{t_{PD}}.$$

(2.24)

For a worst-case analysis, the maximum noise occurs with the minimum  $t_{PD}$  in (2.24); using equation (2.21) gives,

$$\sigma_n = \frac{\kappa \sqrt{T_{CONV}}}{\sqrt{t_{PD}}} \cdot \sqrt{n_{MAX}}.$$

(2.25)

In reference [40],  $\kappa$  for a full swing CMOS delay is approximated as,

$$\kappa = 2\sqrt{\frac{kT}{i_D V_{DD}}} \tag{2.26}$$

in which k is Boltzmanns constant and T is absolute temperature. Combining equations (2.26), (2.25), (2.15),

$$\sigma_n = 2\sqrt{\frac{kT}{C_L V_{DD}^2}} \sqrt{n_{MAX}},\tag{2.27}$$

showing that the noise contribution due to jitter will increase as the square root of the target resolution  $n_{MAX}$ .

To find the resolution at which the noise effect of jitter becomes appreciable, define  $n_{MAX}^*$  as the resolution for which the rms noise due to jitter is just equal to the ADC quantization noise of  $1/\sqrt{12}$  LSB,

$$1/\sqrt{12} = 2\sqrt{\frac{kT}{C_L V_{DD}^2}} \sqrt{n_{MAX}^*} \Rightarrow n_{MAX}^* \approx \frac{C_L V_{DD}^2}{48kT}$$

(2.28)

Evaluating (2.28) with  $C_L$  and  $V_{DD}$  suggesting that that jitter will limit noise performance for resolution above  $\log 2$  (6590) = 12.7 bits.

Further interpreting the result in (2.28) shows:

- (1) The dimensionless quantity  $n_{MAX}^*$  in (2.28) is the result of a ratio of two energies: the energy of the switching event  $C_L V_{DD}^2$  relative to the random thermal energy kT. This makes intuitive sense since the noise effect of jitter will be of less concern as the random thermal energy is a small fraction of the switching energy which determines the time domain behavior of the delay stage.

- (2) As switching energy per transition decreases with scaling, we expect the resolution  $n_{MAX}^*$  to decrease, meaning that jitter will affect performance at lower ENOB.

The limit in equation (2.28) was developed assuming a thermal noise jitter model. For channel lengths less than 100nm, it is likely that 1/f effects [41] and/or excess noise [42, 43] will contribute additional noise beyond the prediction of equation (2.28).

# 2.4 Nonlinearity Mitigation Techniques

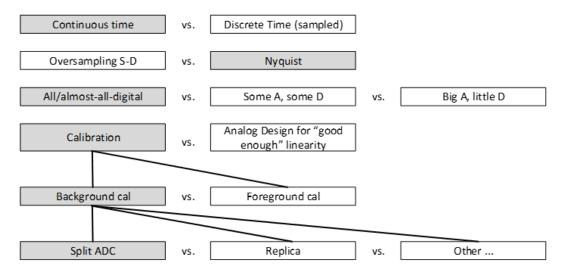

To design a good VCO-based ADC, the major work is to solve the nonlinearity of v-to-f characteristics of VCO. As shown in Figure 2.14, we can see the organization of architecture choices for VCO-based ADC.

Figure 2.14: Organization of architecture choices for VCO-based ADC

Firstly, there are two choices for input ports: continuous or discrete time input. For the continuous time input, the average value of signal during every conversion time is used as the input voltage to ADC. While for the discrete time input, a fixed value of signal at every conversion time is sampled as the input voltage.

According to the sample rate of the ADC, the ADC architecture can be divided into oversampling ADC or Nyquist ADC. Then, the detailed structure of VCO-based

ADC can be further decided. In the third row of Figure 2.14, "All/almost-all-digital" block represents that the VCO-based ADC has only very simple analog circuitry, such as single-ended ring VCO, and the most other parts are digital circuits. "Some A, some D" and "Big A, little D" blocks represent the ADC structure has some complex analog circuits, while digital circuits are simplified. For example, the most popular VCO-based ADC architecture nowadays is the oversampling ADC by using a  $\Sigma\Delta$  loop to mitigate the nonlinearity of VCO v-to-f characteristics, which locates in the "Some A, some D" or "Big A, little D" section.

Furthermore, to deal with the VCO v-to-f nonlinearity, designing a "good enough" linear analog circuit might not be a smart and visionary option in the future subnanometer CMOS era. Calibration methods including background or foreground calibration are a relatively hot topic. Although the foreground cal is much easier, it does not provide real-time adaption to the temperature changing or other unpredictable process influence. Therefore, the background calibration technique is more attractive.

Under the background calibration category, there are also various kinds of calibration algorithms. For example, the "split ADC" based calibratable system which is used in this work is one of the most achievable and efficient algorithms [1]. Additionally, the algorithm using replica VCOs published in [5] is another very interesting and excellent work.

In this work, in order to hit the highly digital, low power consumption target, the following architecture is investigated: continuous time input, Nyquist sampling, almost all digital background calibration assistant system based on "split ADC" structure.

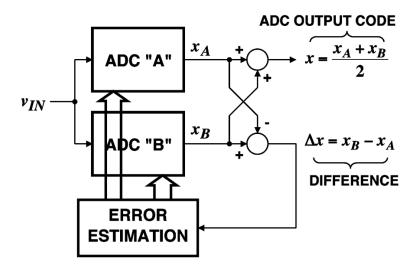

## 2.5 Split ADC Concept

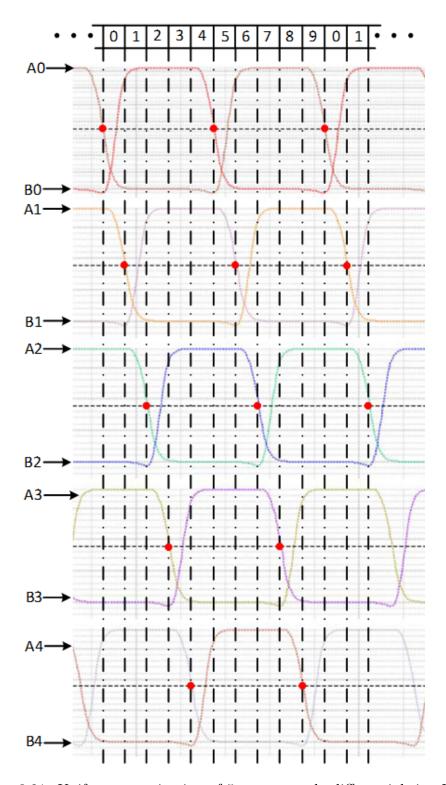

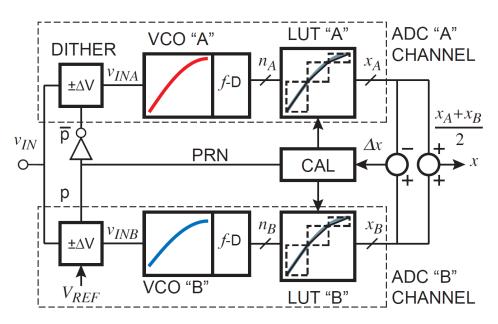

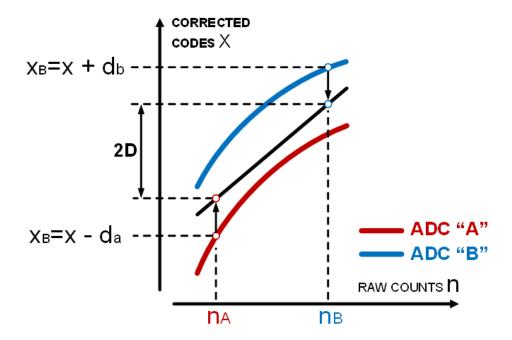

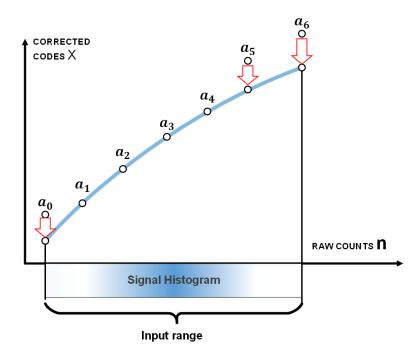

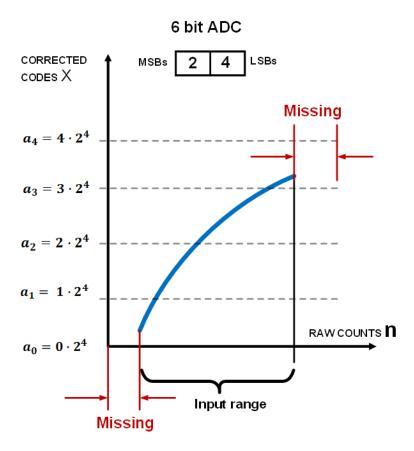

In this section, the general idea of how "split ADC" based calibratable system is discussed. Figure 2.15 shows the concept of the general "split ADC architecture [1–3]: the ADC is split into two channels, each converting the same input  $v_{IN}$  and producing individual output codes  $x_A$  and  $x_B$ . The average of the two outputs is the ADC output code x. The background calibration signal is developed from the difference  $\Delta x$  between codes  $x_A$  and  $x_B$  and is completely transparent to converter operation in the output code signal path.

Figure 2.15: Split ADC architecture

If both ADCs are correctly calibrated, the two outputs will agree and the difference  $\Delta x$  will be zero. In the presence of nonzero differences, the pattern of disagreements in  $\Delta x$  can be examined in an error estimation process to adjust calibration parameters in each ADC, driving the difference and the ADC errors to zero. In the split ADC approach calibration and correction are performed entirely in the digital domain, without interrupting normal ADC operation.

The "split ADC" was originally developed by professor John McNeill and his

collaborators Michael Coln and Brian Larrivee from Analog Devices [1–3]; a similar technique was developed independently by Moon and Li at Oregon State [44]. An indication of quality and impact of this technique is the broad range of published work using the "split ADC" approach developed by other investigators.

While the original work [1–3] was for an algorithmic (cyclic) ADC architecture, work has also been published applying the "split ADC" concept to architectures such as pipeline [44–64], oversampling [65–69], flash [70], folding [71], interleaved [72,73] and SAR [74–77] ADCs. Over a broad range of the speed-resolution-architecture ADC trade-off space, there are examples in the literature in which the "split ADC" approach enables fast digital background self-calibration. The proposed work would be the first to extend the advantages of the "split ADC" approach to VCO-based ADCs. As will be shown later, this will enable drastically improved power efficiency by moving all calibration and correction into the digital domain, allowing VCO-based ADCs to fully realize the promise of nanometer scaled CMOS while avoiding the performance trade-offs and disadvantages of the calibration techniques.

# Chapter 3

# Analog Front-End Design

This chapter describes the analog front-end design of the proposed VCO-based ADC. Firstly, the system architecture of the proposed VCO-based ADC is introduced. Secondly, the analysis and choice of the VCO architecture is discussed. After that, the customized phase measurement circuits including ripple counters, uniform phase detector and phase decoder are demonstrated in detail for this specific VCO-based ADC application. The differential output buffers which are used to improve the driving ability of VCO outputs are also shown. In the end, the overall architecture of the whole analog front end will be demonstrated

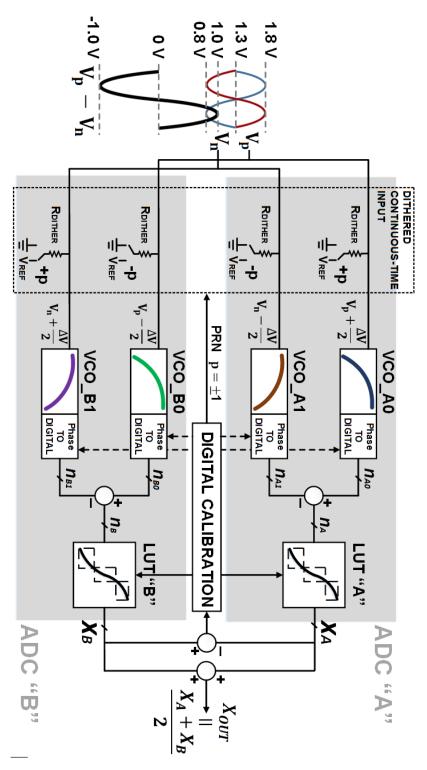

# 3.1 System Architecture of the proposed VCO-Based ADC

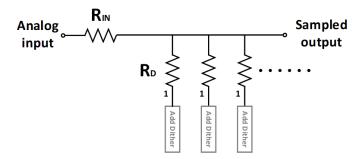

First of all, this section gives a whole picture of the overall VCO-based ADC system architecture of the proposed VCO-based ADC. The system block diagram is shown in Figure 3.1. For the calibratable "split ADC" architecture [1–3], there are two identical ADC channels in the systems, called ADC "A" and ADC "B". They are

absolutely the same. In the each ADC "A" or ADC "B", there are two identical VCOs in a differential configuration. This structure is chosen because the differential signal path can suppress even order harmonics (as shown in Figure 5.11). In other words, it can improve the linearity of v-to-f characteristics and reduces the workload for the digital calibration system.

Under the single-ended condition, the analog input range is from 0.8 to 1.8V and the corresponding VCO frequency is roughly from 10 to 310 MHz (To have a large input signal swing, the maximum input is equal to the supply voltage. The minimum input is the one that can just make the ring start to oscillate). Thus, for the differential configuration, the differential input is from -1 to +1 V, and the differential VCO frequency is from -300 to +300 MHz. The input dynamic range increases as well as the v-to-f linearity. However, the power consumption is doubled. In fact, there is a trade-off between power and ENOB. This depends on the specific application, but in general, to make Walden F.O.M remain the same or smaller, the ENOB should increase at least 1 bit if the power is doubled. Thus, the question is if the differential configuration for v-to-f linearity improvement could bring another 1 bit ENOB, or if it can improve calibration speed, chip area and other system performance.

In fact, one of the important reasons to choose the differential configuration in this work, is to improve the input signal bandwidth. As discussed in the last chapter, it will be faster for calibration to reach convergence if the input signal is slow, as it means the LUT can built in a more continuous way without skipping lots of LUT locations. Thus, if the differential signal path enables a relatively linear relationship between voltage and VCO output frequency, under the same calibration time requirement as a single-ended system, the input signal bandwidth can be larger.

Figure 3.1: System Architecture of the VCO-based ADC

## 3.2 VCO Choice for VCO-Based ADC

This subsection mainly discusses the choice of VCO architecture for the usage in VCO-based ADC. It will start from introduction of different types of VCOs with analysis of their advantages and disadvantages. Then, according to this proposed VCO-based ADC work's requirement and application scenarios, the main reason of choosing a ring VCO will be given. In the end, the implementation of the VCO on chip will be shown in detail.

#### 3.2.1 LC Oscillator

LC oscillator is a well-known VCO topology that is famous for its performance in phase noise [78]. The oscillation frequency is determined primarily by its resonant LC tank. And the LC oscillator could be tuned by varing an element value, such as a voltage controlled capacitance like varactor. However, in this work, the LC oscillator is not chosen for the following reasons,

- (1) This VCO-based ADC work is focusing on the low power consumption target. Though the LC oscillator could provide very good jitter performance, it is not suitable for this application condition because the large bias current required by LC oscillator (which cost lots of power) goes against the original goal of this project. The ring oscillator's moderate jitter performance is good enough for this VCO-based ADC design requirement.

- (2) LC oscillator requires much larger chip area than a ring oscillator because of its resonant LC tank. In this highly digital system, the die area is supposed as small as possible and the large integrated inductors are to be avoided.

- (3) The tuning in LC oscillator by varying capacitance of varactors is not as straightforward as in ring VCO, which need only control its input gate voltage.

The indirect tuning method of the LC oscilator will induce some unexpected design issues. For example, due to this work's calibration algorithm requirement, small dithers need to be added at the input ports, which can be a big problem if using an LC VCO.

(4) Another advantage of this novel highly digital VCO-based ADC is its scalling friendly merit. As CMOS technology is moving to nanometer very fast from 65nm to 28nm or even 7nm these days, simple analog circuitry with digital systems supporting will be the main trend. It is a big requirement that the design could be re-usable in different CMOS technologies, however, LC oscillator due to its resonance reason, it usually needs to be re-designed when moving to new technology.

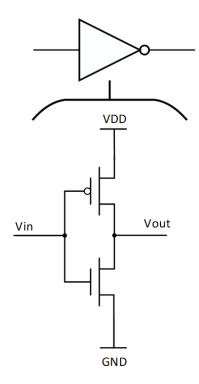

## 3.2.2 Ring Oscillator

Another common type of oscillator is the ring oscillator. Figure 3.2 shows the simplest 3-stage, single-ended ring oscillator. The delay stage is usually created by a CMOS inverter as shown in Figure 3.3. Its oscillation frequency is determined by the propagation delay  $t_{PD}$  of each delay stage. Thus ring VCO output frequency can be expressed as,

$$f_{vco} = \frac{1}{2 \cdot N \cdot t_{PD}} \tag{3.1}$$

where N is the number of ring VCO stages.

However, due to different characteristics of NMOS and PMOS (for example, difference of carrier mobility of electron and holes, mismatches in two transistors) in the inverter as shown in Figure 3.3, the gate delay actually could be separated into two different delays,  $t_{rise}$  and  $t_{fall}$ . The paths through PMOS and NMOS are not ideally the same, therefore, the equivalent path resistance of PMOS and NMOS will

Figure 3.2: 3-stage single-ended ring oscillator

be slightly different.  $t_{rise}$  represents the delay time when the inverter transitions from a low voltage level to a high voltage level.  $t_{fall}$  represents the delay time when the inverter transitions from a high voltage level to a low voltage level. Though it seems not a big problem as seen in the VCO's output frequency, it is a critical challenge if the VCO-based ADC requires a high resolution. The specific design of uniform phase sampling will be explained in the later sections.

Figure 3.3: Delay stage of 3-stage single-ended ring oscillator

Now, if we differentiate gate delay  $t_{PD}$  by using  $t_{rise}$  and  $t_{fall}$ , the output fre-

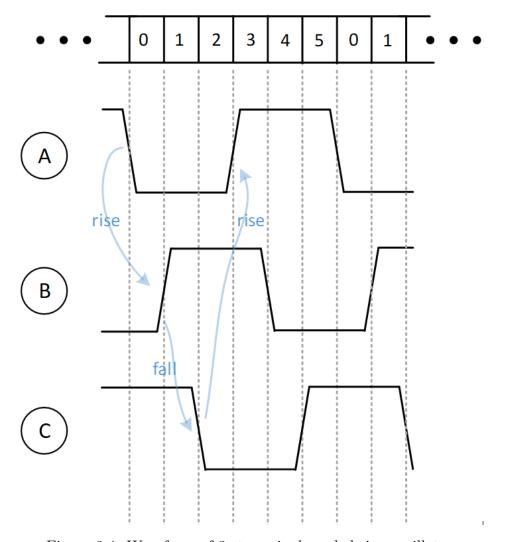

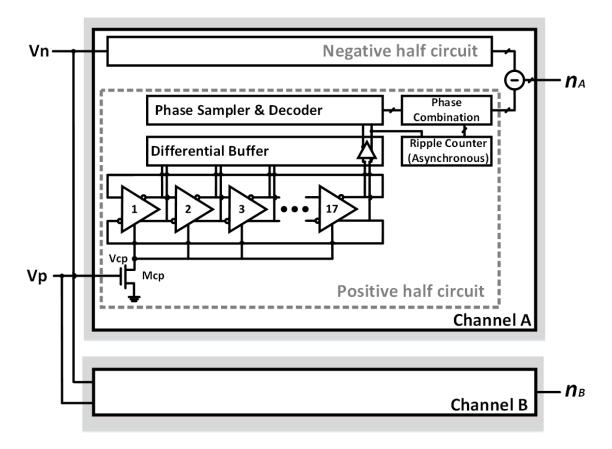

Figure 3.4: Waveform of 3-stage single-ended ring oscillator

quency of ring VCO can be expressed as,

$$f_{vco} = \frac{1}{N \cdot (t_{rise} + t_{fall})}. (3.2)$$

To explain the transition condition more carefully, an example of a 3-stage, single-ended ring VCO output waveform is displayed in Figure 3.4. The A, B, C nodes represent a short period of the output waveform of the 3-stage, single-ended ring VCO output as shown in Figure 3.2. The numbers 0, 1, 2, 3, 4, 5 represent

the total transition phase conditions in one clock period. As we can see in Figure 3.4, when the clock waveform transfers from a low voltage level in node A to a high voltage level in node B, there is a rising time delay between node A and node B, thus a phase condition 0 is created. Similarly, when the clock waveform transfers from a high voltage level in node B to a low voltage level in node C, there is a falling time delay between node B and node C, thus, a phase condition 1 is created. Thes rising and falling time gate delays will appear alternatively and finally create a full clock period.

In this specific 3-stage ring oscillator case, a full clock period  $T_{clock}$  can be expressed as,

$$T_{clock} = t_{rise} + t_{fall} + t_{rise} + t_{fall} + t_{rise} + t_{fall}$$

$$(3.3)$$

and it could be summarized as,

$$T_{clock} = 3 \cdot t_{rise} + 3 \cdot t_{fall} = n \cdot (t_{rise} + t_{fall}) \tag{3.4}$$

where N = 3, and  $T_{clock} = 1 / f_{VCO}$

There may provoke a question: why a full clock is built by  $2 \cdot N$  gate delays? The most straightforward answer is the clock period represents a pattern. However, this is actually related to an interesting overtone issue which will be discussed in the next subsection about how to choose number of stages in ring oscillator.

Compared with the LC oscillator, ring oscillator may not have better jitter performance [40], however, the advantages of ring oscillator are matching the proposed VCO-based ADC design:

(1) Low power: because ring oscillator only consumes power when a transition happens, there are no other passive components or large static currents burning power.

- (2) Small area: ring oscillator is consist of only simple inverters which are built by PMOS and NMOS, no large integrated inductors or capacitors are needed. This significantly reduces die area requirements.

- (3) Easy Tuning: there are quite a lot of ways to tune the frequency of a ring oscillator. For example, by controlling the transition current or supply voltage, which are both direct and simple.

- (4) Scaling friendly: ring oscillators are much simpler to be re-designed than LC oscillators when moving from one CMOS technology to another. It typically involves changing the ratio of widths and lengths in PMOS and NMOS to make them stay balanced. What's more, for the case in the ultra small nanometer CMOS technology, ring oscillator is also very easy to implement by creating a positive closed loop of inverters without consideration of other complex questions in LC oscillator.

Thus, according to the requirements of VCO-based ADC design, a ring voltage controlled oscillator is chosen over an LC oscillator. In the following subsection, design considerations and real chip implementation is explained.

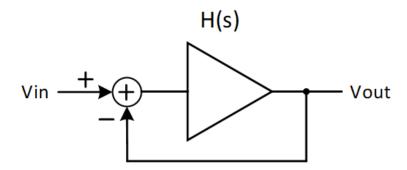

#### Number of Stages in a Ring VCO

Figure 3.5: Feedback system

An oscillator is actually a unity gain negative feedback system, as displayed in Figure 3.5. The relation of output and input can be given as,

$$\frac{V_{out}}{V_{in}}(s) = \frac{H(s)}{1 + H(s)}. (3.5)$$

However, the difference between an oscillator and a normal negative feedback system is that its loop gain satisfies two conditions,

$$|H(s)| \ge 1 \tag{3.6a}$$

$$\angle H(s) = 180^{\circ} \tag{3.6b}$$

It can be explained that oscillators could start to oscillate when the forward gain is large enough and the total phase shift is actually 360°. Thus, the first thing for considering to design a simple ring oscillator is the number of stages, which directly decides the gain and phase shift in oscillator.

For single-ended ring VCOs, the number of delay stages should be odd numbers like 3, 5, 7, 9, 11, etc. An even number of delay stages could make a single-ended VCO output locked, which means at every output of the ring VCO, the voltage level is stable. On the other hand, for differential ring VCOs, even and odd number of delay stages could both be used because the differential output of two VCOs can be swapped to avoid locking problem.

There are some other practical considerations beyond theoretical reasons. For example, the ring VCO will usually be followed by a digital counter to collect the number of clock periods. However, a small number of delay stages will make the VCO output frequency very large, as defined in equation (3.2): when N is small,  $f_{VCO}$  will be a large value. It could cause a very big problem since the digital circuits may not pass static timing analysis (STA). A very high output frequency may unecessarily increase the difficulties in the following digital circuit design.

However, to design a good high speed and high resolution VCO-based ADC, counting the number of clock period is not enough; all of the phase transitions should be collected. This will be a challenge; the standard cell of D flip flops may not meet the requirement, and customized fast flip flops are needed to handle tiny setup and hold time window. One important point to remember is, if we are counting transition numbers in a constant time at one same output node of a ring oscillator, result is constant,

$$n = \frac{T_{CONV}}{t_{PD}} \tag{3.7}$$

where  $T_{CONV}$  is the constant counting time (or, the conversion time), and  $t_{PD}$  is the gate delay.

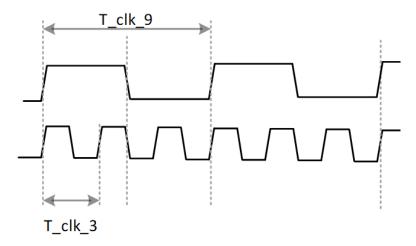

Another significant and interesting design issues related to number of delay stages in ring VCO is called "overtone". For the single-ended ring oscillator case, the issue usually happens for an odd, composite number of delay stages. Recall the formula which be used to calculate VCO output frequency in (3.2), when the VCO architecture and CMOS technology are the same (gate delay of VCO is the same), then, if a 3-stage ring VCO's clock period is  $T_{clk}$ 3, another 9-stage ring VCO's clock period should be  $T_{clk}$ 9 =  $3 \cdot T_{clk}$ 3. In Figure 3.6, the waveforms of 9-stage and 3-stage ring oscillator are shown, the period of 9-stage ring oscillator is 3 times of that in 3-stage.

According to this special case analysis, the general case could be derived. Assuming there is a odd composite number  $k = p \cdot q$ , then the output clock period of two ring oscillators (everything is the same but number of ring stages), with k stages and p stages, will have the relationship as follows,

Figure 3.6: Waveform of 3-stage and 9-stage single-ended ring osc

$$T_{-}clk_{-}k = \frac{k}{p} \cdot T_{-}clk_{-}p = q \cdot T_{-}clk_{-}p.$$

$$(3.8)$$

According to the work in [79] and the above analysis, a ring oscillator with composite number of delay stages may have higher harmonic components besides its own fundamental frequency. These unexpected harmonics will introduce noise into the whole ADC system. Therefore prime numbers of delay stages are preferred. Thus, in this chip implementation, the number of delay stages in ring oscillator is 17. Because 17 is a relatively large stage number which do not require very high speed counter to collect the output transitions and it is also a prime number to avoid overtone issues.

#### Tuning Method in Ring VCO

To use a ring oscillator in VCO-based ADC, we need to add some tuning techniques to change the simple oscillator to a voltage controlled oscillator, whose gate delay transition time could be tuned with an input signal. As shown in equation (3.2), for a constant conversion period, to change the digital output counts n the only choice

in ring oscillator is to change the gate delay,  $t_{PD}$ .

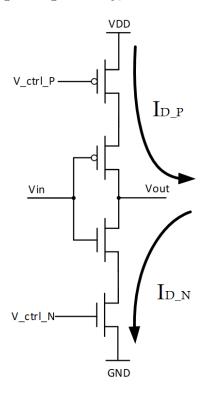

Figure 3.7: Delay stage of current starved VCO

There are several ways to control the gate delay of a ring oscillator. The first one is to control the current strength which charges and discharges the load of each inverter. This topology is referred as the current-starved VCO. Figure 3.7 shows a simplified view of a delay stage of a current-starved VCO. The two additional MOS-FETs work as current sinks and sources, and are controlled by the input voltage. Thus, the transient drain current when the transition happens could be limited. In other words, the inverter is starved for current as it could not get enough current from supply voltage. The total sum of the output capacitor of the first stage and the input capacitor of the second stage can be modeled as a load capacitor  $C_L$ . The time it takes to charge and discharge  $C_L$  depends on the drain current  $I_{D_P}$  and  $I_{D_N}$ , respectively. These time delays are actually the same as  $t_{rise}$  and  $t_{fall}$ .

Another similar option is to change the gate delay by controlling the supply

voltage. The supply voltage not only influences the charging drain current but also the output swing of the oscillator. However, these kinds of two combination tuning will introduce nonlinearity into the ADC system and is not usually used.

Instead of changing the charging and discharging current strength, the time delay is also dependent on the load capacitance. Thus, another method is to vary the propagation delay by changing the output capacitive load  $C_L$ . This variation in load capacitance can be realized by one or more voltage dependent capacitors called a varactor. A reverse-bias PN junction can serve as a varactor which has capacitance [80],

$$C_{var} = \frac{C_0}{(1 - V/\Phi_B)^m} \tag{3.9}$$

where  $C_0$  is a zero bias capacitance, V is the applied voltage,  $\Phi_B$  is the built in voltage of the junction, and m is a value typically between 0.3 and 0.5 [80]. Adding a varactor diode increases the load capacitance, directly affecting the tuning range of the VCO. Additionally, the nonlinear relationship between controlled voltage and the varactor diode capacitance translates into the nonlinearity of the VCO.

#### Ring VCO Architecture

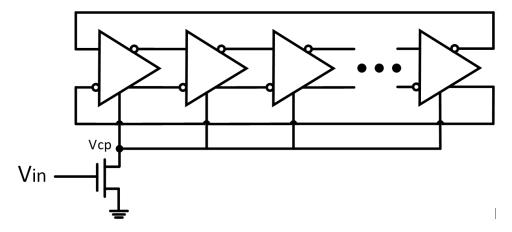

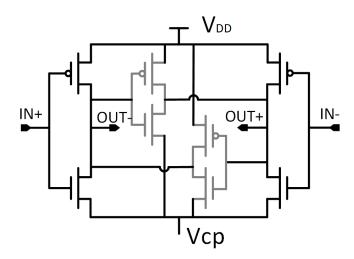

Until now, the details design of VCO's gate delay, tuning method are discussed. The next step is to analyze the applied ring VCO architecture while considering the benefit of the whole ADC system performance. There are many ways to implement a ring VCO such as single-ended, true differential, source-coupled and other architecture. By upholding the design target of low-power, small area and scaling friendly, the pseudo differential ring VCO architecture is used on chip as we can see in Figure 3.8.

In Figure 3.9, the delay stage of is displayed in detail. The two middle gray

Figure 3.8: Pseudo differential ring VCO

Figure 3.9: Delay stage of pseudo differential ring VCO

inverters are used to lock the pseudo differential ring oscillator in a 180° phase difference, and the size of these two inverters should be the small. Because if their size is comparable with the two outside large inverters, they will influence the VCO's output frequency. Actually, the middle two inverters are usually designed in the smallest size and the main inverters for the ring oscillation are in a proper larger size. Thus, the total power consumption of the pseudo differential ring VCO will be small. A large tail transistor is used to limit the current of the whole oscillator. It could improve the noise performance of the ring oscillator by blocking it from

supply noises.

The most important reason to use the pseudo differential ring VCO is the need to have uniform phase quantization by checking only rising edge or only falling edge of the VCO transition. Recall the equation that represents the VCO's frequency in (3.2), because of the different characteristics of NMOS and PMOS, and the other mismatches in the charging and discharging paths, the rising delay time  $t_{rise}$  and the falling delay time  $t_{fall}$  are different. If we use single-ended ring VCO, we need to check the rising and falling time alternatively, which can induce large noises because of non-uniformed phase quantization. However, since the two output signals of the pseudo differential VCO are 180° out of phase, we can check only the falling time or only the rising time by sampling the two ring oscillator outputs alternatively. This method will be explained more carefully in section 3.3.2.

## 3.3 Phase Measurement Circuit

To build a VCO-based ADC, besides the design of VCO as an integrator, a phase measurement circuit is also required to transfer the VCO frequency or phase into discrete digital codes. In this section, the detailed design of the phase measurement circuit is described. The phase measurement circuit is consist of digital counter,

Figure 3.10: Simplified VCO-based ADC structure

phase detector, phase decoder and output buffer.