# **Automatically Parallelizing Embedded Legacy Software** on Soft-Core SoCs

Automatische Parallelisierung bestehender eingebetteter Software mit Soft-Core SoCs

Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing.) genehmigte Dissertation von Kris Heid aus Groß-Umstadt Tag der Einreichung: 24.06.2019, Tag der Prüfung: 20.08.2019 Darmstadt — D 17

1. Gutachten: Prof. Dr.-Ing. Christian Hochberger 2. Gutachten: Prof. Dr.-Ing. Jeronimo Castrillon

Fachgebiet Rechnersysteme Fachbereich Elektrotechnik und Informationstechnik

Automatically Parallelizing Embedded Legacy Software on Soft-Core SoCs Automatische Parallelisierung bestehender eingebetteter Software mit Soft-Core SoCs

Genehmigte Dissertation von Kris Heid aus Groß-Umstadt

Gutachten: Prof. Dr.-Ing. Christian Hochberger

Gutachten: Prof. Dr.-Ing. Jeronimo Castrillon

Tag der Einreichung: 24.06.2019 Tag der Prüfung: 20.08.2019

Darmstadt — D 17

URN: urn:nbn:de:tuda-tuprints-90205

URL: http://tuprints.ulb.tu-darmstadt.de/id/eprint/9020

Dieses Dokument wird bereitgestellt von tuprints, E-Publishing-Service der TU Darmstadt http://tuprints.ulb.tu-darmstadt.de tuprints@ulb.tu-darmstadt.de

Die Veröffentlichung steht unter folgender Creative Commons Lizenz: Namensnennung – Keine kommerzielle Nutzung – Keine Bearbeitung 4.0 International https://creativecommons.org/licenses/by/4.0/deed.de

| Erklärungen laut Promotionsordnung                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                             |

| § 8 Abs. 1 lit. c PromO                                                                                                                                                                                                     |

| Ich versichere hiermit, dass die elektronische Version meiner Dissertation mit der schriftlichen Version übereinstimmt.                                                                                                     |

| § 8 Abs. 1 lit. d PromO                                                                                                                                                                                                     |

| Ich versichere hiermit, dass zu einem vorherigen Zeitpunkt noch keine Promotion versucht wurde. In diesem Fall sind nähere Angaben über Zeitpunkt, Hochschule, Dissertationsthema und Ergebnis dieses Versuchs mitzuteilen. |

| § 9 Abs. 1 PromO                                                                                                                                                                                                            |

| Ich versichere hiermit, dass die vorliegende Dissertation selbstständig und nur unter Verwendung der<br>angegebenen Quellen verfasst wurde.                                                                                 |

| § 9 Abs. 2 PromO                                                                                                                                                                                                            |

| Die Arbeit hat bisher noch nicht zu Prüfungszwecken gedient.                                                                                                                                                                |

|                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                             |

| Ort, Datum und Unterschrift                                                                                                                                                                                                 |

|                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                             |

#### **Abstract**

Nowadays, embedded systems are utilized in many areas and become omnipresent, making people's lives more comfortable. Embedded systems have to handle more and more functionality in many products. To maintain the often required low energy consumption, multi-core systems provide high performance at moderate energy consumption. The development started with dual-core processors and has today reached many-core designs with dozens and hundreds of processor cores. However, existing applications can barely leverage the potential of that many cores.

Legacy applications are usually written sequentially and thus typically use only one processor core. Thus, these applications do not benefit from the advantages provided by modern many-core systems. Rewriting those applications to use multiple cores requires new skills from developers and it is also time-consuming and highly error prone. Dozens of languages, APIs and compilers have already been presented in the past decades to aid the user with parallelizing applications. Fully automatic parallelizing compilers are seen as the holy grail, since the user effort is kept minimal. However, automatic parallelizers often cannot extract parallelism as good as user aided approaches. Most of these parallelization tools are designed for desktop and high-performance systems and are thus not tuned or applicable for low performance embedded systems. To improve this situation, this work presents an automatic parallelizer for embedded systems, which is able to mostly deliver better quality than user aided approaches and if not allows easy manual fine-tuning.

Parallelization tools extract concurrently executable tasks from an application. These tasks can then be executed on different processor cores. Parallelization tools and automatic parallelizers in particular often struggle to efficiently map the extracted parallelism to an existing multi-core processor. This work uses soft-core processors on Field Programmable Gate Arrays (FPGAs), which makes it possible to realize custom multi-core designs in hardware, within a few minutes. This allows to adapt the multi-core processor to the characteristics of the extracted parallelism. Especially, core-interconnects for communication can be optimized to fit the communication pattern of the parallel application.

Embedded applications are often structured as follows: receive input data, (multiple) data processing steps, data output. The multiple processing steps are often realized as consecutive loosely coupled transformations. These steps naturally already model the structure of a processing pipeline. It is the goal of this work to extract this kind of pipeline-parallelism from an application and map it to multiple cores to increase the overall throughput of the system. Multiple cores forming a chain with direct communication channels ideally fit this pattern. The previously described, so called pipeline-parallelism is a barely addressed concept in most parallelization tools. Also, current multi-core designs often do not support the hardware flexibility provided by soft-cores, targeted in this approach.

The main contribution of this work is an automatic parallelizer which is able to map different processing steps from the source-code of a sequential application to different cores in a multi-core pipeline. Users only specify the required processing speed after parallelization. The developed tool tries to extract a matching parallelized software design along with a custom multi-core design out of sequential embedded legacy applications. The automatically created multi-core system already contains used peripherals extracted from the source-code and is ready to be used. The presented parallelizer implements multi-objective optimization to generate a minimal hardware design, just fulfilling the user defined requirement. To the best of my knowledge, the possibility to generate such a multi-core pipeline defined by the demands of the parallelized software has never been presented before.

The approach is implemented for two soft-core processors and evaluation shows for both targets high speedups of 12x and higher at a reasonable hardware overhead. Compared to other automatic parallelizers, which mainly focus on speedups through latency reduction, significantly higher speedups can be achieved depending on the given application structure.

#### Zusammenfassung

Eingebettete Systeme werden heutzutage in vielen Bereich eingesetzt, um unseren Alltag zu erleichtern. Hierbei übernehmen diese immer mehr Aufgaben. Um die wachsende Anzahl an Aufgaben erledigen zu können werden Mehrkernprozessoren benötigt, welche eine hohe Leistungsfähigkeit bei gleichzeitig moderatem Energiebedarf bieten. Waren die ersten Mehrkernprozessoren noch mit zwei Rechenkernen ausgestattet, so existieren heute bereits Prozessoren mit dutzenden und hunderten Rechenkernen. Viele bestehende Anwendungen können jedoch ohne Anpassungen kaum von dieser hohen Anzahl an Rechenkernen profitieren.

Existierende Anwendungen haben meist einen sequenziellen Programmablauf und nutzen daher per se nur einen einzigen Rechenkern. Somit können sie nicht von den Vorteilen und der Rechenleistung moderner Prozessoren profitieren. Die Anwendungen müssten umgeschrieben werden, um das volle Potenzial von Mehrkernprozessoren zu nutzen, was jedoch neue Fertigkeiten und Denkmuster von Entwicklern fordert und zudem sehr mühsam und fehleranfällig ist. In den letzten Jahren wurden bereits eine Reihe an Programmiersprachen, Programmierschnittstellen und Compilern entwickelt, um Entwickler bei der Parallelisierung zu unterstützen. Dabei sind vollständig automatische Parallelisierer der heilige Gral der Parallelisierung, da sie dem Nutzer den Großteil der Arbeit abnehmen. Automatische Parallelisierer können jedoch teilweise nicht die Qualität der einer manuellen Parallelisierung von erfahrenen Entwicklern erreichen. Die Meisten der entwickelten Parallelisierungswerkzeuge sind außerdem für Desktop- oder Hochleistungsrechner entworfen worden und sind daher kaum an die Bedürfnisse eingebetteter Systeme angepasst. Daher wird in dieser Arbeit ein automatischer Parallelisierer für eingebettete Systeme vorgestellt, welcher oftmals die Qualität manueller Parallelisierungen übertrifft und auf Wunsch manuelle Anpassungen erlaubt.

Parallelisierungswerkzeuge sind in der Lage parallel ausführbare Aufgaben aus einer Anwendung zu extrahieren und diese dann auf verschiedenen Prozessorkernen auszuführen. Vor allem automatische Parallelisierer haben jedoch oft Probleme den gefundenen Parallelismus effizient auf die verfügbare beschränkte Anzahl an Kernen abzubilden. Daher werden in dieser Arbeit Soft-Core Prozessoren auf FPGAs verwendet, welche es ermöglichen ein angepasstes Mehrkernsystem innerhalb weniger Minuten zu realisieren. Hierdurch kann das System auf die Charakteristiken des extrahierten Parallelismus angepasst werden. Besonders die Kommunikationsinfrastruktur kann speziell auf das Kommunikationsmuster der parallelisierten Anwendung angepasst werden.

Anwendungen eingebetteter Systeme haben oftmals die folgende Struktur: Eingangsdaten empfangen, Verarbeitung der Daten (in mehreren Schritten), Ausgabe der Daten. Die verschiedenen Verarbeitungsschritte sind hierbei meist nur locker gekoppelte aufeinanderfolgende Transformationen der Daten. Die beschriebenen Schritte weisen somit die Struktur eine Verarbeitungs-Pipeline auf. Daher ist das Ziel dieser Arbeit diesen sogenannten Pipeline-Parallelismus aus der Anwendung zu extrahieren. Die einzelnen Verarbeitungsschritte werden dann zur Erhöhung des Datendurchsatzes auf verschiedene Kerne abgebildet. Hierbei passt eine Kette von Prozessorkernen mit direkter Kommunikation zwischen den Nachbarn ideal zur Charakteristik des extrahierten Pipeline-Parallelismus. Das Konzept des Pipeline-Parallelismus ist in heutigen Parallelisierungswerkzeugen eher selten vorzufinden, was auch daran liegt, dass aktuelle Mehrkernsysteme nicht die benötigte Struktur bzw. Flexibilität von Soft-Cores bieten, um die Pipeline-Muster ideal abzubilden.

Der Beitrag dieser Arbeit ist ein automatischer Parallelisierer, welcher in der Lage ist aus einer sequentiellen Anwendung Pipeline-Parallelismus zu extrahieren und diesen auf eine zuvor beschriebene Kette von Prozessorkernen abzubilden. Der Nutzer muss lediglich eine Verarbeitungsgeschwindigkeit vorgeben, welche die parallelisierte Anwendung erreichen soll. Der Parallelisierer extrahiert anschließend den nötigen Parallelismus aus der Anwendung und erstellt automatisch ein individuell angepasstes Mehrkernsystem. In diesem System sind neben der Kommunikationsinfrastruktur auch bereits alle genutzten

Peripherien enthalten, sodass es direkt einsatzbereit ist. Der Parallelisierer optimiert das System in verschiedenen Aspekten, um möglichst minimale Hardware zu generieren, die dennoch den Nutzervorgaben entspricht. Die Generierung einer Mehrkern-Pipeline, die individuell auf die parallelisierte Anwendung angepasst ist, wurde nach meinem besten Wissen noch nicht veröffentlicht.

Das Konzept wurde für zwei Soft-Core Prozessoren implementiert und die Evaluation weist einen hohen möglichen Geschwindigkeitszuwachs des Faktors 12 und mehr, bei moderat erhöhtem Hardwarebedarf auf. Im Vergleich zu anderen automatischen Parallelisierern, die sich lediglich auf eine Erhöhung des Durchsatzes durch Verringerung der Latenz fokussieren, kann ein weitaus höherer Geschwindigkeitszuwachs erreicht werden, falls die Anwendung die nötigen Charakteristiken aufweist.

## Contents

| Αk  | brev    | viations       | 5                                                   | 10       |

|-----|---------|----------------|-----------------------------------------------------|----------|

| Lis | st of I | Figures        | ;<br>;                                              | 12       |

| Lis | st of T | Γables         |                                                     | 14       |

| Lis | st of ( | Code Li        | istings                                             | 15       |

| 1   |         | oductio        |                                                     | 17       |

|     | 1.1     | Motiva         | ***************************************             | 17       |

|     | 1.2     |                | ems & Goals                                         | 18       |

|     | 1.3     | Work           | plan                                                | 19       |

| 2   |         | e-of-th        |                                                     | 21       |

|     | 2.1     |                | /Many-Core SoC Platforms                            | 21       |

|     |         | 2.1.1          | Embedded Multi-Core Architectures                   | 21       |

|     |         | 2.1.2          | Embedded Many-Core Architectures                    | 22       |

|     |         | 2.1.3          | Soft-core multi-/many-cores                         | 24       |

|     | 0.0     | 2.1.4          | Conclusion                                          | 25       |

|     | 2.2     |                | eting Parallelism from Applications: Design Choices | 26       |

|     |         | 2.2.1          | Programming Paradigms                               | 26       |

|     |         | 2.2.2<br>2.2.3 | Types of Parallelism                                | 27<br>27 |

|     |         | 2.2.3          | Partitioning Level                                  | 28       |

|     |         |                | Memory Architecture                                 | 28<br>28 |

|     |         | 2.2.5<br>2.2.6 | Task Scheduling                                     | 28<br>28 |

|     | 2.3     |                | elization Tools                                     | 20<br>29 |

|     | ۷.5     | 2.3.1          | Tools out of Scope                                  | 29       |

|     |         | 2.3.1          | DSLs/Language Extensions                            | 31       |

|     |         | 2.3.2          | APIs/Libraries                                      | 32       |

|     |         | 2.3.4          | Annotations                                         | 33       |

|     |         | 2.3.5          | Automatic                                           | 36       |

|     |         | 2.3.6          |                                                     | 38       |

|     |         | 2.0.0          | Sammary                                             | 00       |

| 3   |         | get Plat       |                                                     | 40       |

|     | 3.1     | -              | anMC                                                | 40       |

|     |         | 3.1.1          | Inter-Core Communication                            | 40       |

|     | 2.2     | 3.1.2          | Performance-Counter                                 | 45<br>46 |

|     | 3.2     |                |                                                     | 46<br>46 |

|     |         | 3.2.1          | Inter-Core Communication                            | 46<br>47 |

|     | 2.2     | 3.2.2          |                                                     |          |

|     | 3.3     | 3.3.1          | Core Communication performance evaluation           | 48<br>48 |

|     |         | 0.0.1          |                                                     | 48<br>48 |

|     | 21      | 3.3.2          | 1-to-N and N-to-1 Communication                     | 48<br>49 |

|     | 3.4     | Giona          | t Memory                                            | 49       |

| 4   |         |                | i-Core Architectures and Execution Concepts         | 51       |

|     | 4.1     | Requi          | red Application Structure                           | 51       |

|   | 4.2 | Pipeline S                                     | 51 |

|---|-----|------------------------------------------------|----|

|   |     | 4.2.1 Pipeline Hardware Limitations            | 52 |

|   | 4.3 | Pipeline with Replication                      | 53 |

|   |     | 4.3.1 Replicated Pipeline Hardware Limitations | 54 |

|   | 4.4 | Shared Global Memory                           | 54 |

|   | 4.5 | Communication Overhead                         | 54 |

|   | 4.6 | Latency                                        | 55 |

|   |     |                                                |    |

| 5 |     |                                                | 57 |

|   | 5.1 |                                                | 57 |

|   |     |                                                | 57 |

|   |     |                                                | 57 |

|   |     | •                                              | 59 |

|   |     |                                                | 59 |

|   | 5.2 |                                                | 60 |

|   |     |                                                | 60 |

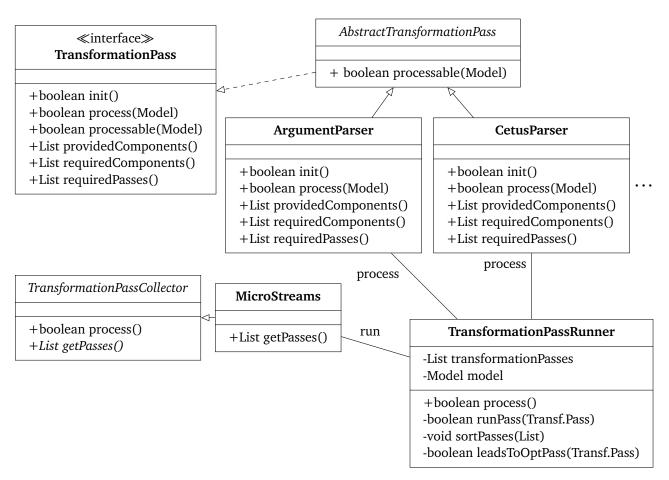

|   |     | 5.2.2 Common Transformation Infrastructure     | 62 |

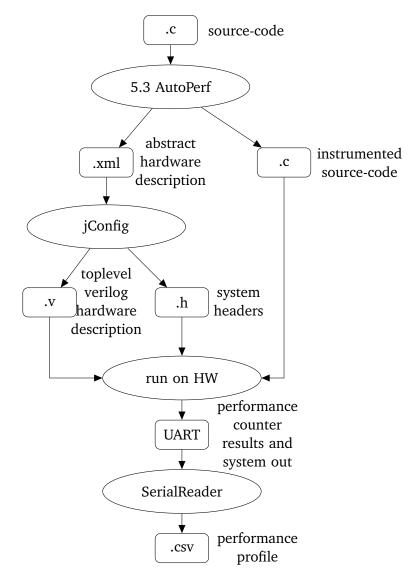

|   | 5.3 | AutoPerf                                       | 64 |

|   |     | 5.3.1 Traditional Approaches                   | 64 |

|   |     | 5.3.2 Implementation                           | 66 |

|   |     | 5.3.3 Credibility of Measured Results          | 67 |

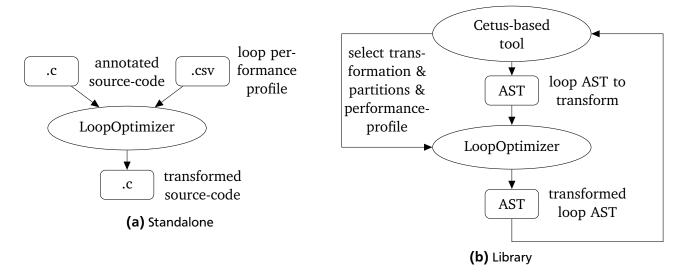

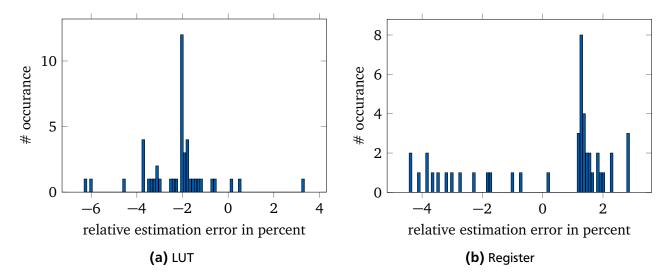

|   | 5.4 | LoopOptimizer                                  | 69 |

|   |     | 5.4.1 Loop Parallelization Techniques          | 70 |

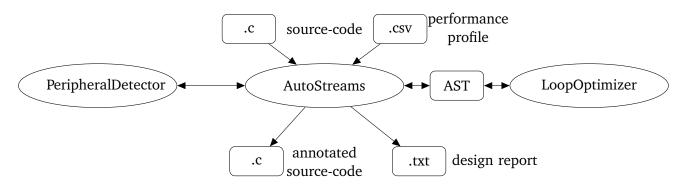

|   | 5.5 | AutoStreams                                    | 73 |

|   |     |                                                | 73 |

|   |     | •                                              | 74 |

|   | 5.6 | •                                              | 78 |

|   |     | •                                              | 79 |

|   |     | · ·                                            | 80 |

|   |     | **                                             | 81 |

|   | 5.7 | PeripheralDetector                             |    |

|   |     | •                                              | 89 |

|   |     |                                                | 91 |

|   |     | •                                              | 92 |

|   |     |                                                | 93 |

|   |     |                                                |    |

| 6 | Eva | uation                                         | 94 |

|   | 6.1 | Test Applications                              | 94 |

|   |     | 6.1.1 ADPCM                                    | 95 |

|   |     | 6.1.2 MJPEG2000                                | 95 |

|   |     | 6.1.3 IIR Butterworth Filter                   | 96 |

|   |     | 6.1.4 Firewall                                 | 96 |

|   | 6.2 |                                                | 97 |

|   |     |                                                | 98 |

|   | 6.3 |                                                | 00 |

|   |     |                                                | 00 |

|   |     |                                                | 04 |

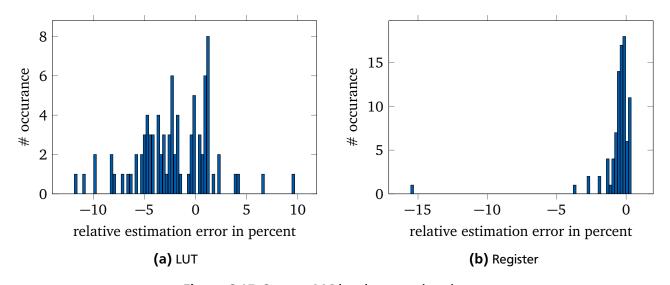

|   |     | 6.3.3 Parallelization with DMA Interconnects   |    |

|   |     | 6.3.4 Parallelization with LoopOptimizer       |    |

|   |     | 1 - f                                          |    |

|    | 6.4                                                                                                                                                                                                                                                                                                                       | AutoStreams Estimation Accuracy    | 115 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----|

|    | 0.1                                                                                                                                                                                                                                                                                                                       | •                                  |     |

|    |                                                                                                                                                                                                                                                                                                                           |                                    |     |

|    | 6.5                                                                                                                                                                                                                                                                                                                       | <del></del>                        |     |

|    |                                                                                                                                                                                                                                                                                                                           |                                    |     |

|    |                                                                                                                                                                                                                                                                                                                           |                                    |     |

|    | 6.6                                                                                                                                                                                                                                                                                                                       |                                    |     |

|    | 6.7                                                                                                                                                                                                                                                                                                                       |                                    |     |

|    |                                                                                                                                                                                                                                                                                                                           |                                    |     |

|    | 6.8                                                                                                                                                                                                                                                                                                                       | Latency in the Generated Pipelines | 131 |

|    | 6.9                                                                                                                                                                                                                                                                                                                       | Dynamic Verification: System Tests | 133 |

|    | 6.10                                                                                                                                                                                                                                                                                                                      | Comparison with Related Work       | 133 |

|    | 6.11                                                                                                                                                                                                                                                                                                                      | Best Practice Proposals            | 134 |

| 7  | Con                                                                                                                                                                                                                                                                                                                       | clusion & Future Work              | 135 |

| Re | 6.7.1 Speedup vs. Performance Loss through Lower Frequency 6.8 Latency in the Generated Pipelines 6.9 Dynamic Verification: System Tests 6.10 Comparison with Related Work 6.11 Best Practice Proposals 7 Conclusion & Future Work 8 Eferences 13 14 15 16 17 18 18 18 19 19 19 19 10 10 10 11 11 11 11 11 11 11 11 11 11 | 139                                |     |

| Su | perv                                                                                                                                                                                                                                                                                                                      | ised Students' Theses              | 146 |

| Οι | vn P                                                                                                                                                                                                                                                                                                                      | ublications                        | 147 |

#### **Abbreviations**

AHB Advanced High-performance Bus

AI artificial intelligence

APD Activity and Pattern Diagram

API application programming interface

ASIC application-specific integrated circuit

AST Abstract Syntax Tree

BRAM Block RAM

CDFG control data flow graph

Cell B.E. Cell Broadband Engine

CFG control-flow graph

CGRA coarse-grain reconfigurable architecture

CPN C for Process Networks

DAG directed acyclic task graph DMA direct memory access

DMCG Directive-Based MPI Code Generator

DSE design-space exploration

DSL domain specific language

DSP digital signal processing block

EMB<sup>2</sup> Embedded Multicore Building Blocks

FMC FPGA Mezzanine Card

FPGA Field Programmable Gate Array

FSL fast simplex link

GCC GNU Compiler Collection

GPIO general purpose input/output

GPU graphics processing unit

GUI Graphical User Interface

HDL hardware desciption language

HLS high-level synthesis

HPC high performance computing

ICC Intel C/C++ Compiler

IDE integrated development environment

ILP instruction level parallelism

IoT Internet of Things

ISA instruction set architecture ISR interrupt service routine JTAG Joint Test Action Group IEEE 1149.1

KPN Kahn Process Network

LUT look up table

MCAPI Multicore Communications API

MDM MicroBlaze Debug Module

MIMD multiple instruction multiple data

MP-SoC multi-processor system-on-chip

MPI message passing interface

MRAPI Multicore Resource Management API MTAPI Multicore Task Management API

NoC Network-on-Chip

NUMA nonuniform memory access

OpenHMPP Open Hybrid Multicore Parallel Programming

OS operating system

PPE PowerPC processor element

RISC reduced instruction set architecture

SANLP static affine nested loop program

SIMD single instruction multiple data

SMP symetric multi processor

SoC System-On-Chip

SPARC Scalable Processor ARChitecture SPE synergetic processing element

SUIF Stanford University Intermediate Format

TBB Intel Threading Building Blocks

TLP thread-level parallelism TPL task parallel library

UART Universal Asynchronous Receiver Transmitter

VLIW very long instruction word

WCET worst-case execution time

## **List of Figures**

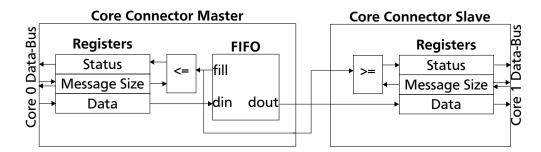

| 3.1  | Core-Connector simplified schematic hardware design                                   | 41  |

|------|---------------------------------------------------------------------------------------|-----|

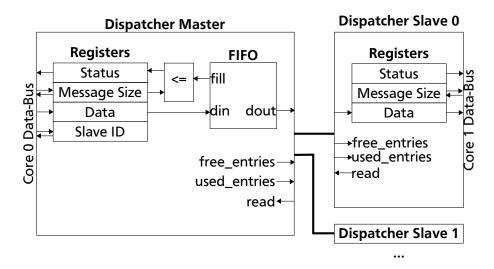

| 3.2  | Dispatcher simplified schematic hardware design                                       | 42  |

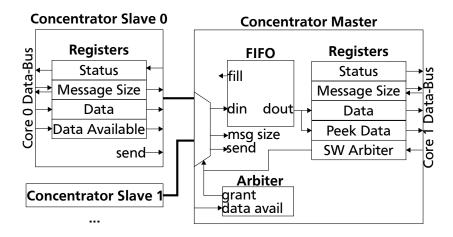

| 3.3  | Concentrator simplified schematic hardware design                                     | 43  |

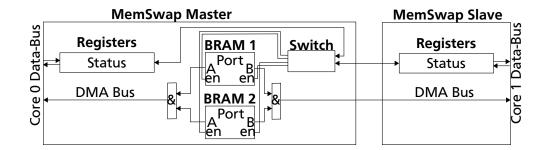

| 3.4  | MemSwap Dual simplified schematic hardware design                                     | 44  |

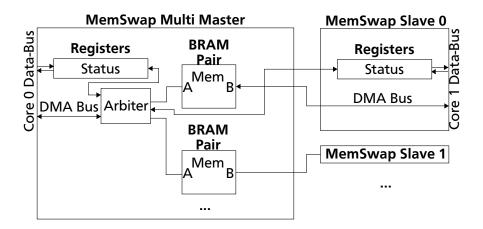

| 3.5  | MemSwap Multi simplified schematic hardware design                                    | 44  |

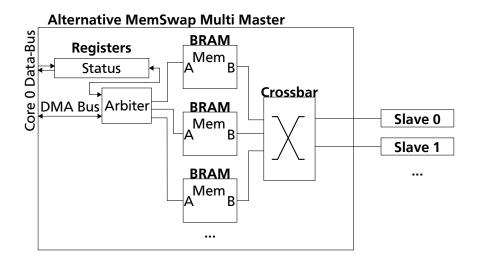

| 3.6  | Alternative approach for MemSwap Multi with fewer BRAMs                               | 45  |

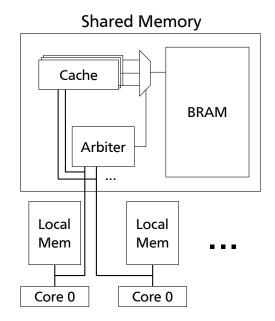

| 3.7  | Shared Memory simplified schematic hardware design                                    | 45  |

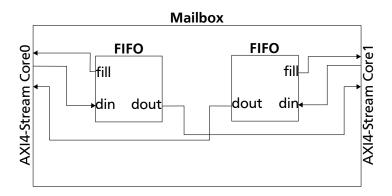

| 3.8  | MicroBlaze Mailbox AXI-Stream simplified schematic hardware design                    | 47  |

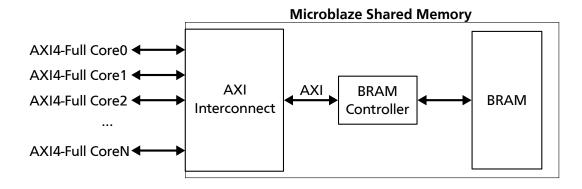

| 3.9  | MicroBlaze shared memory simplified schematic hardware design                         | 47  |

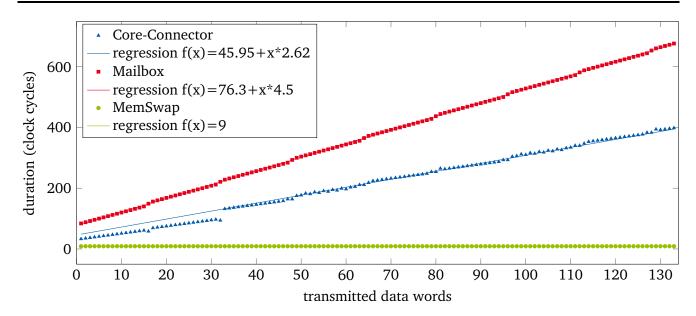

|      | Transmission duration vs. data size for different 1-to-1 core-interconnects           | 49  |

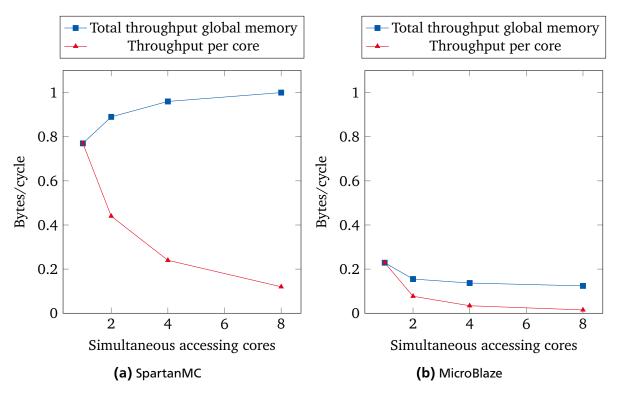

|      | Global memory throughput                                                              | 50  |

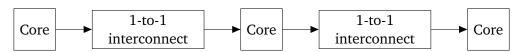

| 4.1  | Pure pipeline, hardware configuration                                                 | 52  |

| 4.2  | Replicated pipeline, hardware configuration                                           | 53  |

| 4.3  | Pipeline with global memory, hardware configuration                                   | 54  |

|      |                                                                                       |     |

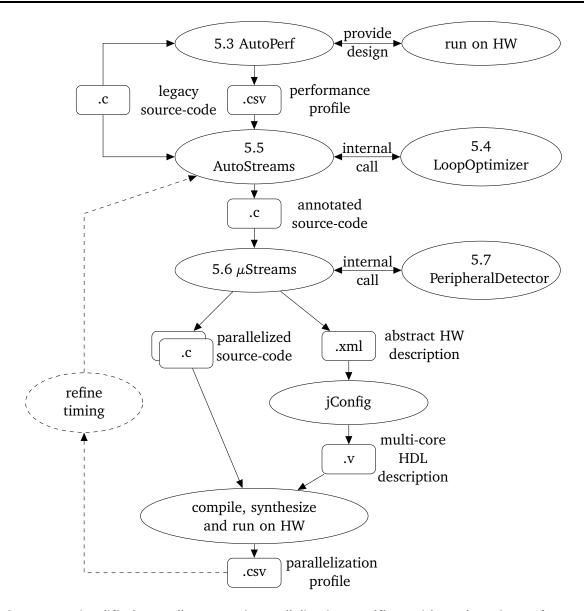

| 5.1  | Simplified Overall Automatic Parallelization Toolflow with Tool Section Reference     | 58  |

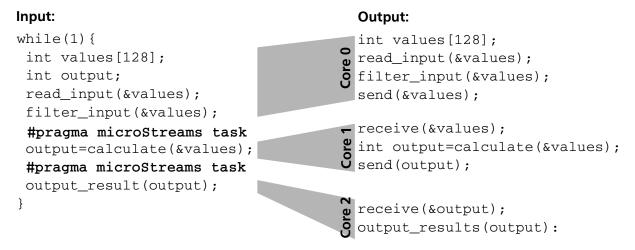

| 5.2  | μStreams concept: SW transformation                                                   | 59  |

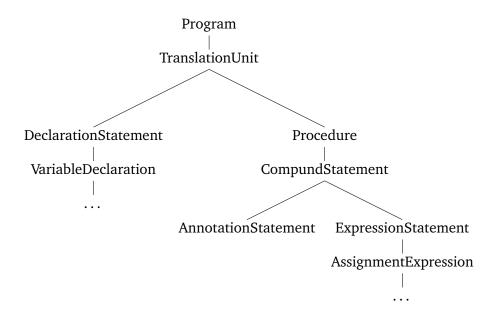

| 5.3  | Simplified Cetus Abstract Syntax Tree (AST) generated from Listing 5.1                | 61  |

| 5.4  | Simplified $\mu$ Streams transformation pass runner class diagram                     | 63  |

| 5.5  | Detailed AutoPerf toolflow                                                            | 65  |

| 5.6  | Detailed LoopOptimizer toolflow for different operation modes                         | 69  |

| 5.7  | Detailed AutoStreams toolflow                                                         | 73  |

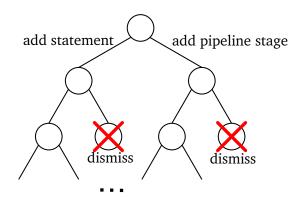

| 5.8  | Search tree for design space exploration                                              | 76  |

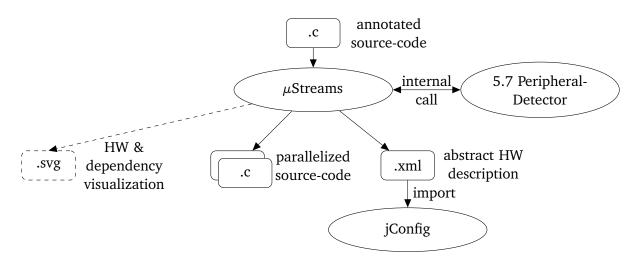

| 5.9  | Detailed $\mu$ Streams toolflow (dashed=optional)                                     | 78  |

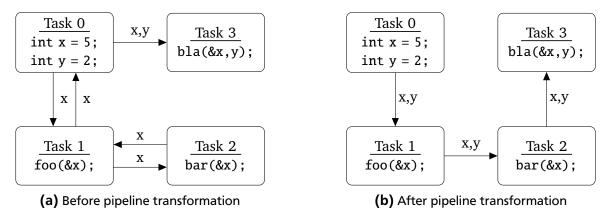

|      | Task dependency created from Listing 5.10                                             | 84  |

|      | Generated pipeline structure and communication                                        | 88  |

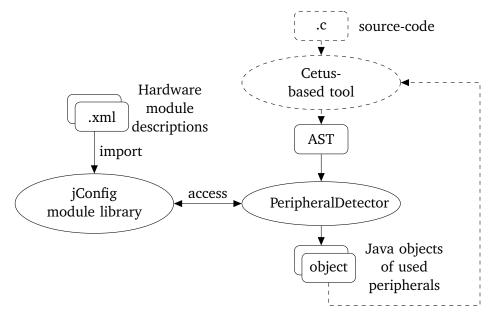

| 5.12 | Detailed Peripheral-Detector toolflow (dashed=optional)                               | 90  |

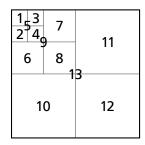

| 6.1  | Image tiles as processed by the JPEG 2000 encoder                                     | 96  |

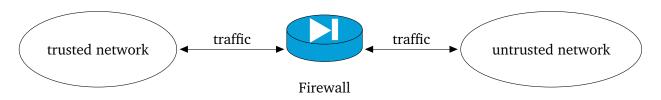

| 6.2  | Firewall zones                                                                        | 97  |

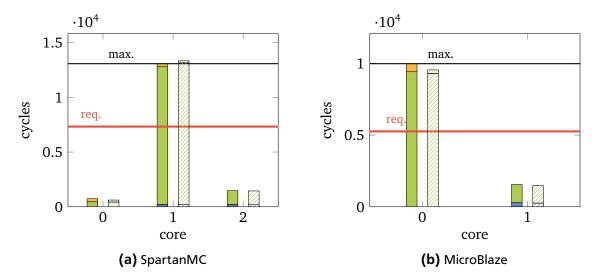

| 6.3  | ADPCM 2x speedup requirement, no optimizations                                        | 101 |

| 6.4  | MJPEG 2x & 4x speedup requirement, no optimizations                                   | 102 |

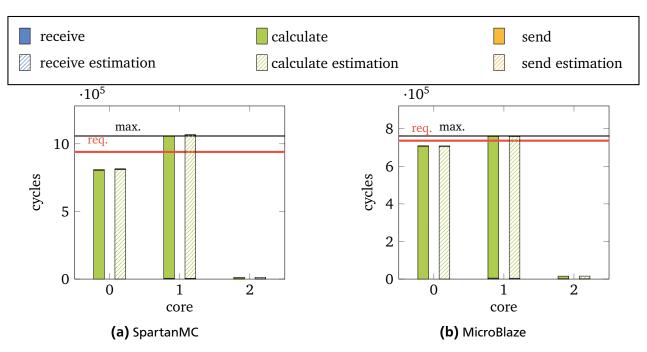

| 6.5  | IIR 2x speedup requirement, no optimizations                                          | 103 |

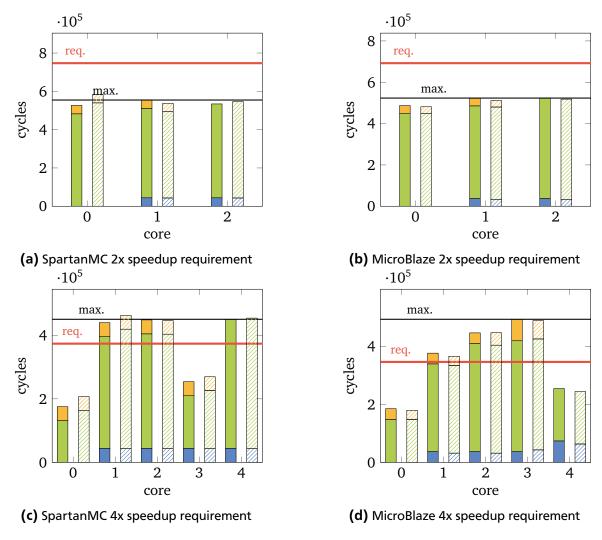

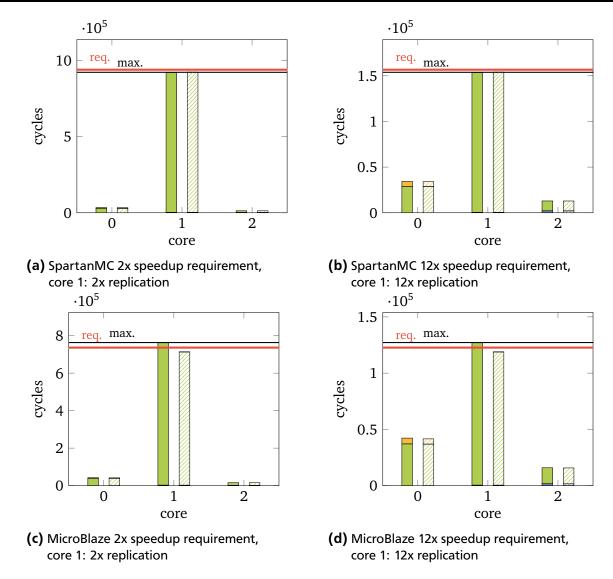

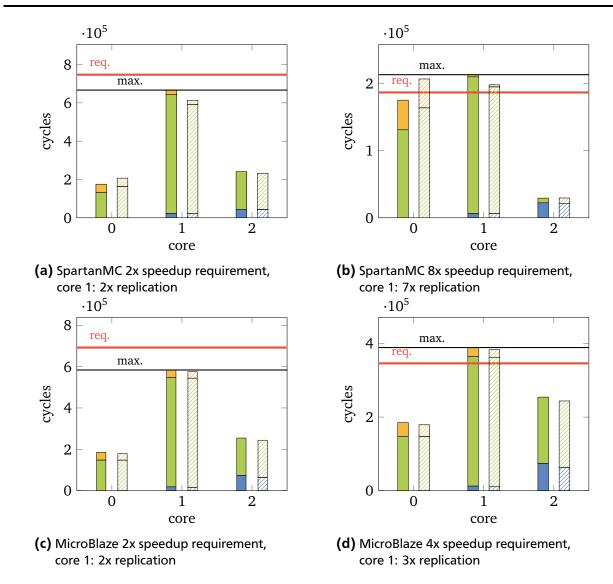

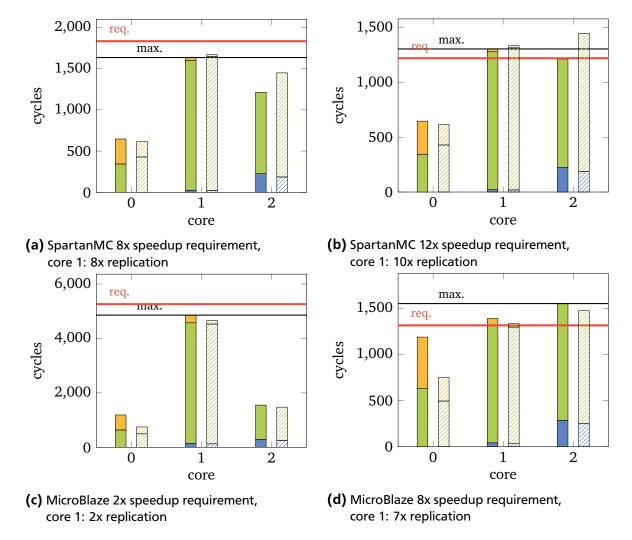

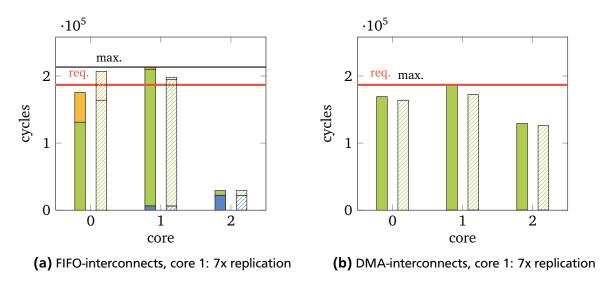

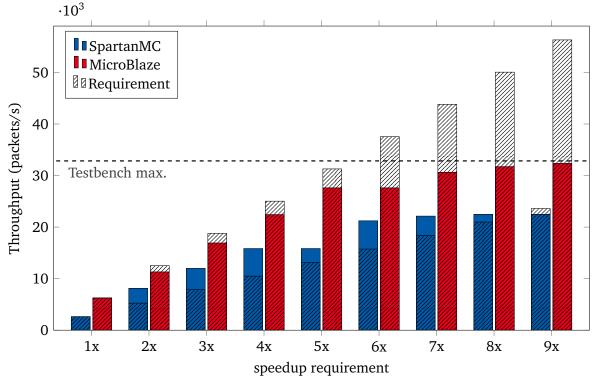

| 6.6  | ADPCM with replication                                                                | 105 |

|      | MJPEG with replication                                                                |     |

| 6.8  | IIR with replication                                                                  | 107 |

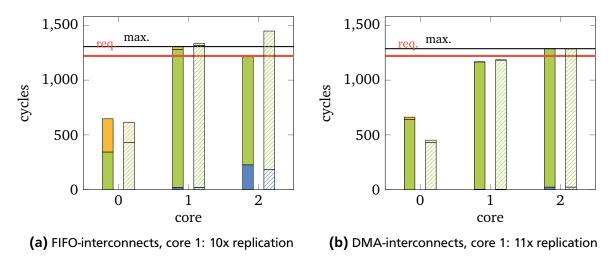

| 6.9  | SpartanMC MJPEG replication with and without DMA-interconnects, 8x speedup require-   |     |

|      | ment                                                                                  | 109 |

| 6.10 | SpartanMC IIR replication with and without DMA-interconnects, 12x speedup requirement | 110 |

| 6.11 | ADPCM with loop optimization                                                          | 111 |

|      | MJPEG with loop optimization                                                          |     |

|      | IIR with loop optimization                                                            |     |

|      | IIR 2x speedup requirement, loop splitting VS loop fission                            |     |

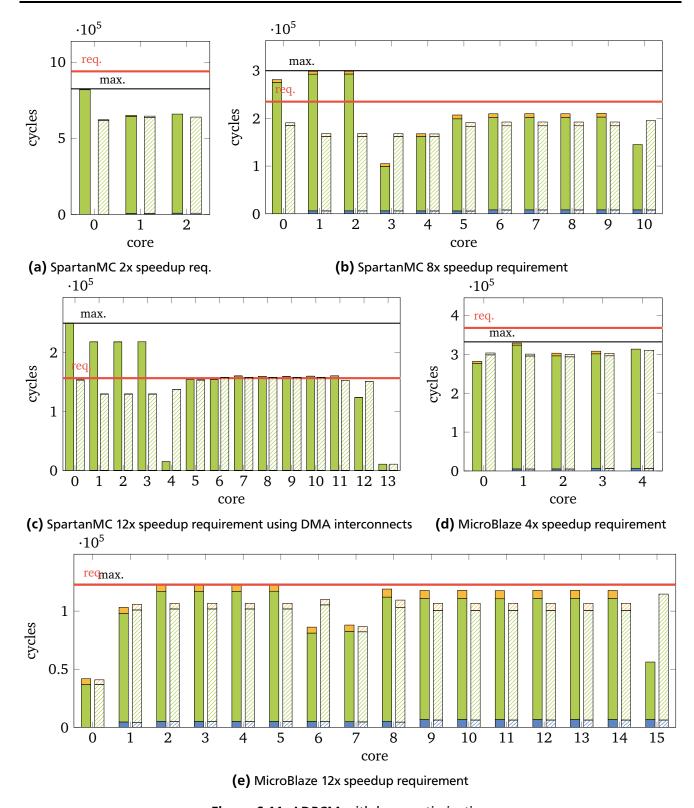

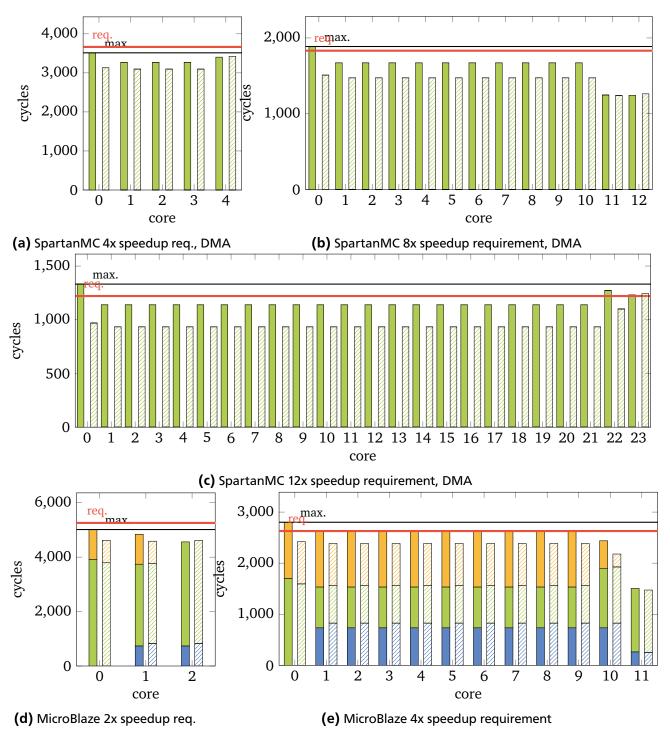

|      | SpartanMC hardware estimation error                                                   |     |

|      | MicroBlaze hardware estimation error                                                  |     |

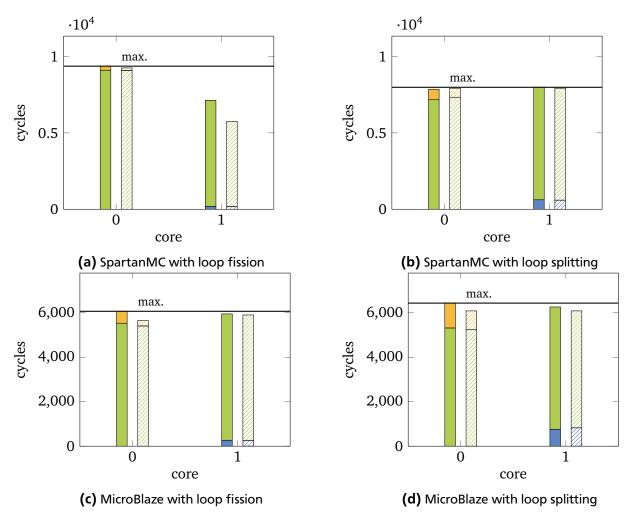

|      | SpartanMC cycles estimation error of different parallelized software parts            |     |

|      | MicroBlaze cycles estimation error of different parallelized software parts           |     |

|      | Firewall hardware design                                                              |     |

|      | Network throughput in Mbit/s for different system configurations                      |     |

|      | Network packet throughput for different system configurations                         |     |

| J 1  | L L                                                                                   |     |

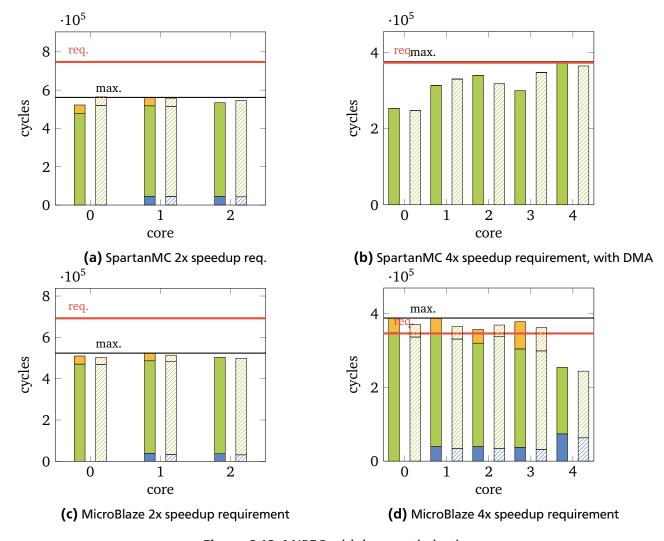

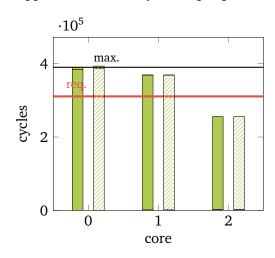

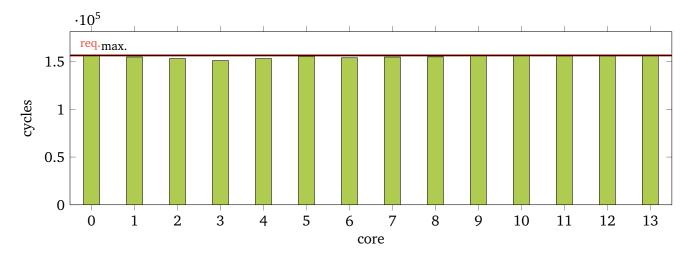

| 6.22 | Duration per SpartanMC core with ADPCM 8x speedup requirement, core 1: 5x replication | 125 |

|------|---------------------------------------------------------------------------------------|-----|

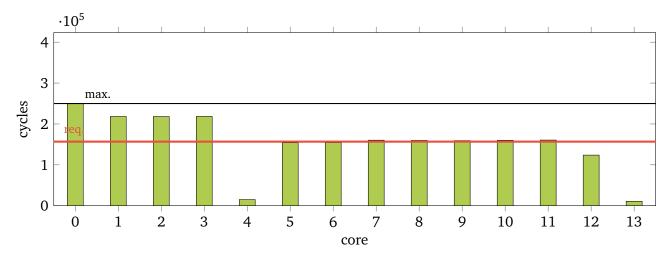

| 6.23 | ADPCM 12x speedup requirement with DMA and loop optimizations, manually paral-        |     |

|      | lelized, first try                                                                    | 126 |

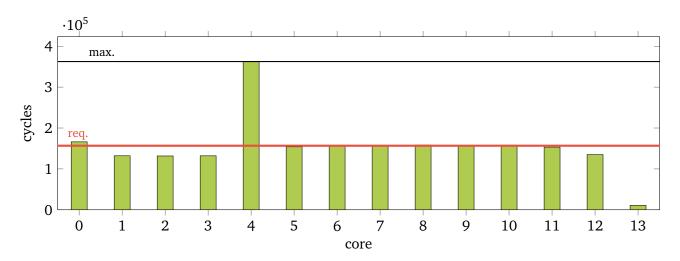

| 6.24 | ADPCM 12x speedup requirement with DMA and loop optimizations, manually paral-        |     |

|      | lelized, second try                                                                   | 127 |

| 6.25 | ADPCM 12x speedup requirement with DMA and loop optimizations, manually paral-        |     |

|      | lelized after 16 tries                                                                | 128 |

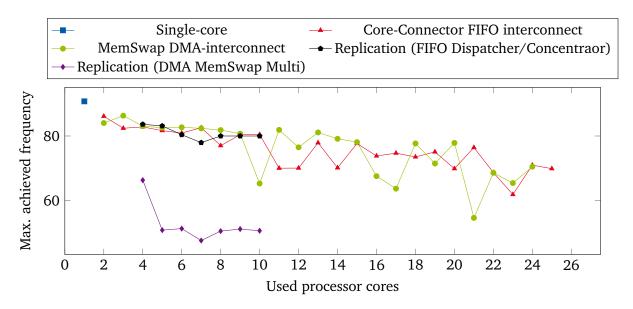

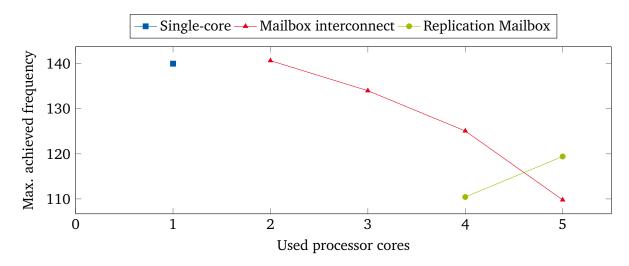

| 6.26 | ADPCM and IIR maximum achievable frequency evaluation over multiple connected Spar-   |     |

|      | tanMC cores and interconnect types                                                    | 129 |

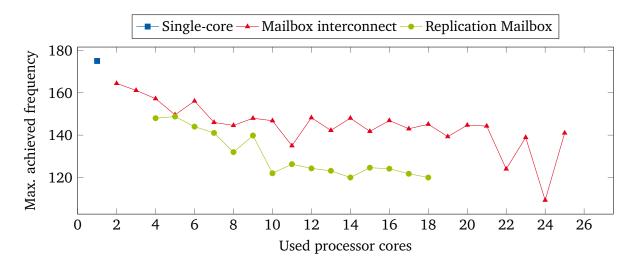

| 6.27 | ADPCM and IIR maximum achievable frequency evaluation over multiple connected Mi-     |     |

|      | croBlaze cores and interconnect types                                                 | 129 |

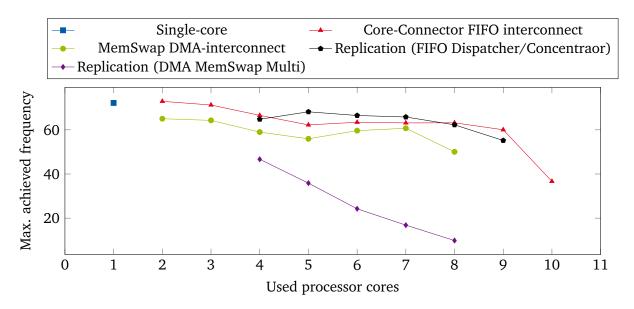

| 6.28 | MJPEG2000 maximum achievable frequency evaluation over multiple connected Spar-       |     |

|      | tanMC cores and interconnect types                                                    | 130 |

| 6.29 | MJPEG2000 maximum achievable frequency evaluation over multiple connected MicroB-     |     |

|      | laze cores and interconnect types                                                     |     |

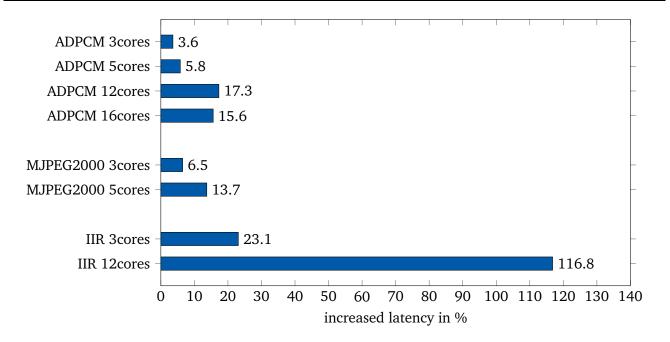

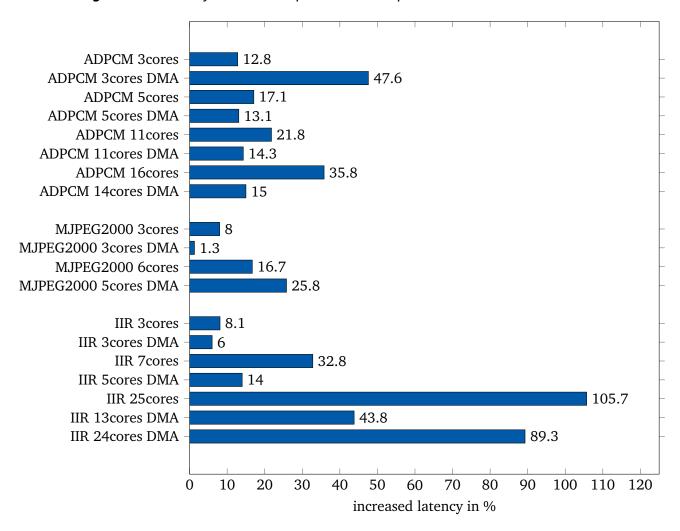

|      | Latency increase compared to the sequential variant with MicroBlaze                   |     |

| 6.31 | Latency increase compared to the sequential variant with SpartanMC                    | 132 |

|      |                                                                                       |     |

### **List of Tables**

| 2.1 | Reviewed parallelization tools                                                        | 30  |

|-----|---------------------------------------------------------------------------------------|-----|

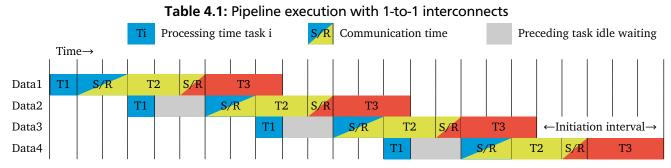

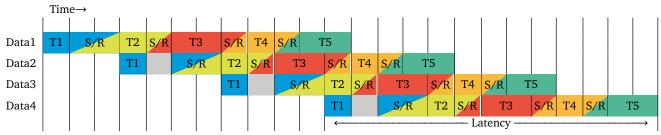

| 4.1 | Pipeline execution with 1-to-1 interconnects                                          | 52  |

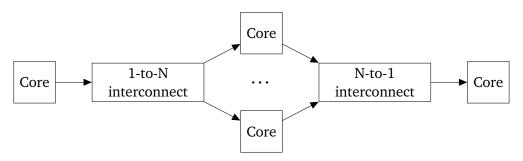

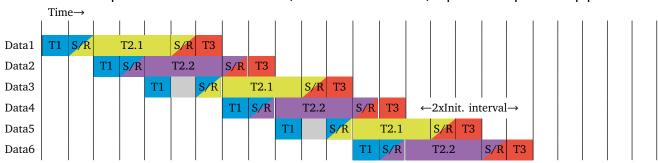

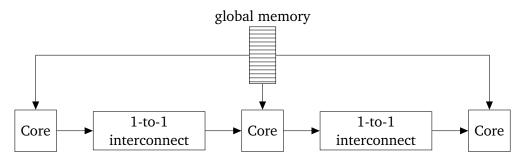

| 4.2 | Pipeline execution with 1-to-N, N-to-1 interconnects, replicated superscalar pipeline | 53  |

| 4.3 | Latency for pipeline execution                                                        | 56  |

| 5.1 | Produced performance-profile example                                                  | 64  |

| 5.2 | Detection accuracy with different applications                                        | 93  |

| 6.1 | Benchmark processing step runtimes in cycles for SpartanMC and MicroBlaze             | 99  |

| 6.3 | SpartanMC core and interconnect hardware cost on Artix-7 XC7A200T FPGA                | 108 |

| 6.4 | Achieved speedups and AutoStreams DMA design choice                                   | 109 |

| 6.5 | Achieved speedups and AutoStreams DMA design choice for previous replicated designs . | 109 |

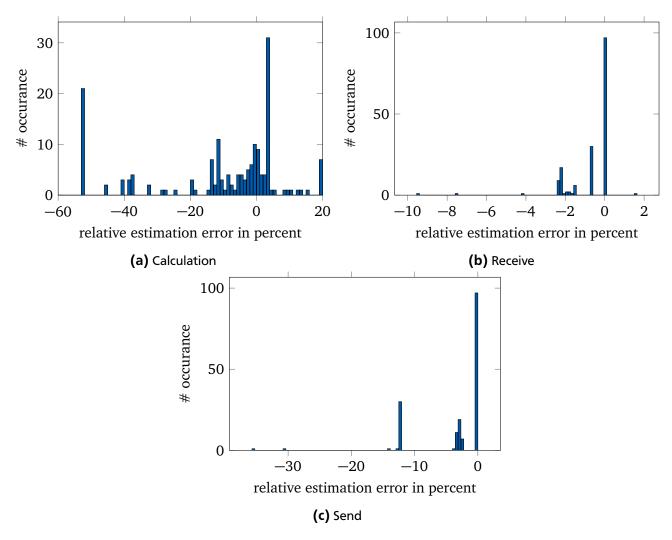

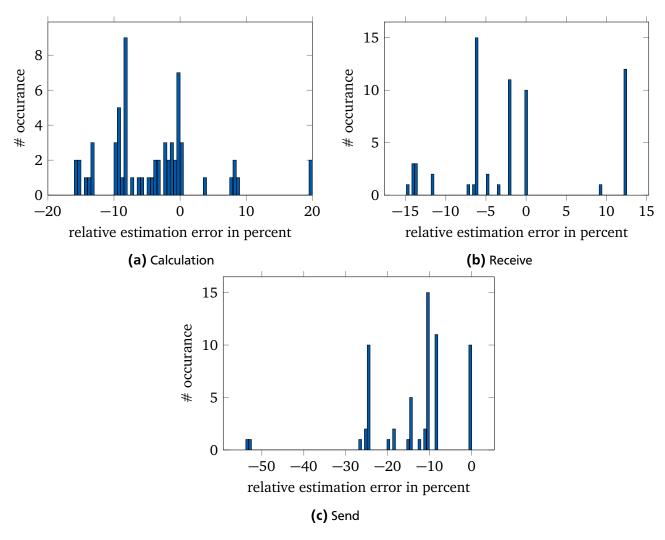

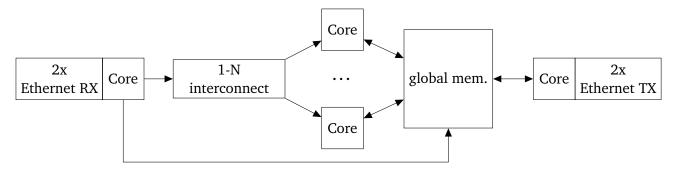

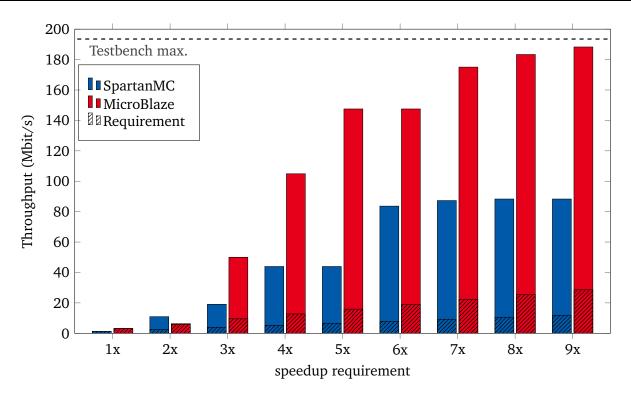

| 6.6 | Estimation accuracy as relative estimation error in percent                           | 123 |

| 6.7 | SpartanMC ADPCM performance-profile with peripheral IO                                | 125 |

## **List of Code Listings**

| 5.1  | Example Cetus Input Program                                                      | 61  |

|------|----------------------------------------------------------------------------------|-----|

| 5.2  | Input source-code for profiling                                                  | 64  |

| 5.3  | Instrumented source-code (diff-style highlighting: green lines with + are added) | 67  |

| 5.4  | Original loop                                                                    | 70  |

| 5.5  | Fissioned loop                                                                   | 70  |

| 5.6  | Split loop                                                                       | 70  |

| 5.7  | Break loop                                                                       | 72  |

| 5.8  | Break loop transformed                                                           | 72  |

| 5.9  | Usable $\mu$ Streams pragmas                                                     | 79  |

| 5.10 | Example code to visualize task pipeline creation                                 | 83  |

| 5.11 | Simplified abstract XML hardware description                                     | 86  |

| 5.12 | Simplified main.c Freemarker task template                                       | 87  |

| 5.13 | Usage of differnt Peripherals in a SpartanMC C-application                       | 89  |

| 6.1  | Generated assembler code, IIR benchmark processing step 0, parallelized variant  | 104 |

| 6.2  | Generated assembler code, IIR benchmark processing step 0, single-core variant   | 104 |

#### 1 Introduction

Computers have become a major part of our everyday live. Even though they are not always directly visible or identifiable as a computer. They are embedded into many products that we daily use. Today, way more so-called embedded computers or embedded systems exist than traditional desktop computers. Embedded systems are used in many areas, such as car industry, avionics, manufacturing industry, multimedia entertainment systems, health care and household items. With the Internet of Things (IoT) boom in the last years, almost everything contains embedded systems and is connected. We live in a world where coffee makers and dish washers can be controlled over the internet and cleaning robots tidy up your home while you are at work. These embedded systems take over more and more jobs and also the complexity which these systems handle increases. With more complex jobs, also the demanded processing power increases. For example, a cleaning robot continuously scans the room with a 360 degree distance measurement, generates a map of the room and calculates an ideal cleaning route covering all areas. New obstacles may appear on the route and new rooms could become visible, requiring an adaptation of the map and the route. At the same time the robot has to interact with a smartphone to display the status and receive commands. These tasks require high processing power from a battery driven device.

Traditionally, the processing power of a processor increases with a higher working frequency e.g. clock frequency, besides other methods found in the past decades of research in this field. However, a higher clock frequency and thereby increased operation voltage result in disproportionately high power consumption [1]. Performance scaling with frequency has also physically reached its limits with today's chip manufacturing techniques. At the same time, embedded devices are often battery powered and demand high processing power at an extremely low energy consumption.

These combined demands are fulfilled through multi-core processors nowadays. Multiple processors are combined on one chip and process workloads together. Multi-core processors theoretically increase processing power with each additional core, while the operation frequency and thereby the power consumption can be kept low. Thus, a multi-core system can maintain the same processing power of a single-core system at lower power consumption [2].

Writing software to use multiple concurrent processors is not that easy. Firstly, many existing algorithms in software are not written to process data concurrently and not all algorithms hold such concurrency. Secondly, software developers must learn new techniques to write new concurrent applications or adapt existing applications.

#### 1.1 Motivation

A lot of legacy applications already exist for embedded systems which could benefit from multi-core devices. Especially legacy software that grew over the time requires adaptation since the additional tasks cannot be fulfilled anymore with a single-core processor. Parallelism must be extracted from the application. This parallelism is represented by different tasks that are mapped to different processor cores. Several possibilities to detect and leverage parallelism already exist. The challenge is to find enough parallelism and to map it efficiently to the multi-core platform [3]. Since multi-core platforms have unique characteristics, like for example communication cost, several objectives have to be optimized to successfully parallelize software. If for example an extracted parallel task is very small, it might take more time to tell another processor to start this task and collect the results than to execute it together with the original task on one processor. To aid the programmer in this process, already plenty of programming languages and language constructs exist. These techniques require manual effort from a developer. Alternatively, some automatic parallelization tools exist to relive the developer. Such tools imply low effort for the developer but sometimes hand tuned parallelizations from skilled programmers result in a better performance. Language constructs for parallelization often exhibit great parallelization

possibilities. This gives a developer a great choice for possible parallelization, but also great chances for inexperienced developers to generate bad parallelizations.

Thus, automatic parallelization is desirable if it works well. And it works better when narrowed down to specific use cases. Development for parallelization tools has mainly been driven by the high performance computing (HPC) community, without focus on embedded systems. By targeting embedded systems for parallelization, restrictions as well as new opportunities for automatic parallelization tools apply in this narrowed field. In the domain of HPC, the maximum amount of parallelism is often desired. The higher the parallelization is, the faster the application runs, the better the solution is considered. Maximum parallelization is not necessarily optimal for an embedded system. Embedded systems often have a minimum required processing speed. As long as this speed can be achieved by parallelization, everything is fine. Higher parallelization is not required and might even lead to less energy efficiency.

With regard to hardware efficiency and task mapping to processors, another aspect can come into play for embedded systems: FPGAs. FPGAs are special circuits to realize almost arbitrary other digital systems. FPGA development has advanced so far that it becomes possible to even realize multiple embedded processors (called soft-cores) on one FPGA. The flexibility and reprogrammability of FPGAs make it possible to use arbitrary custom multi-core designs. It is thinkable to generate hardware to better fit the needs and structure of the parallelized application. One could even adapt the multi-core system with changing application requirements.

#### 1.2 Problems & Goals

Different kinds of parallelism exist within applications that are coarse-grained enough to justify offloading to a different processor: Task-level, data-level and pipeline parallelism. The first two are widely researched and applied in parallelization tools. Pipeline parallelism is addressed by fewer tools, because it is not as widely applicable and has restrictions regarding application structure. Nevertheless, it is shown that parallelization for these applications on desktop computers[4, 5] gives promising results. Cordes et al.[6] showed the applicability of this concept for a simulated embedded system. Besides benchmark applications which mostly cover only one data transformation algorithm, embedded systems might execute multiple such transformations and also have to handle data in and output (not covered by Cordes et al.). Thus, the execution order is often: receive input data from peripherals, run (multiple) data transformation steps, send output data to peripherals. Such an application structure already exhibits different pipeline steps, which could very well be extracted and transformed into a processing pipeline to increase the throughput of the application.

An automatic parallelization tool with the following characteristics would be well suitable for embedded systems:

- Extract only necessary parallelism and not as much as possible. This would not result in the fastest system, but a sufficiently fast system with a small hardware footprint.

- Consider full system parallelization and not only concentrate on parallelizing loops.

- Consider the influence of peripheral interaction during parallelization, even though embedded systems always have peripheral interaction.

- Target low-performance embedded systems running bare-metal, incapable of running an operatingsystem.

- Adapt a configurable hardware system such as soft-cores on FPGAs to the extracted parallelism characteristics.

Currently there is no automatic parallelizing compiler for embedded systems covering the described aspects.

There are several open questions which arise from the set objectives:

- How good are current soft-core communication interconnects and how big is the communication overhead in contrast to computation complexity. Can interconnects be improved to better support the pipeline concept?

- How much parallelism is extractable from this concept? Previous approaches were only using processors with up to four cores.

- Can parallelization be done with distributed or shared-distributed memory systems to overcome the bottleneck of a global common memory?

- Can automatic parallelization keep up with hand parallelized variants from experienced developers?

- Can multi-core soft-core designs be automatically created and tuned to the application characteristics to not bother software developers with hardware design?

- What is the impact on the latency of a pipeline parallel design, since an upper bound for latency is important in some embedded systems?

- Do multi-core designs have a negative impact on the maximum achievable frequency in contrast to single-core designs, when realized on an FPGA?

#### 1.3 Work plan

A work plan is elaborated to design an automatic parallelization tool, covering the aforementioned aspects. The work plan also incorporates the described uncertainties and open questions to verify the applicability of an automatic parallelization tool in this environment.

The following work packages are stated:

- 1. Find applications for low-performance embedded systems that benefit from the aspired pipeline concept.

- 2. Analyze current multi-core capabilities of soft-cores and the performance of supported interconnects. If necessary or possible, the multi-core capabilities and interconnect performance should be improved to support pipeline parallelism.

- 3. Investigate the pipeline concept with low-performance embedded systems through a manual annotation based parallelization tool at first. With an annotation-based parallelization, different applications can be parallelized and the resulting performance can be measured. The parallelization tool should work on the granularity of functions or multiple statements to deliver coarse-grained enough tasks to justify offloading to a different processor core. Also, functions imply a clear, easily analyzable interface for input and output data. This first step should reveal, if this concept is applicable and where possible improvements can be made.

- 4. The tools should be implemented as source-to-source tools. This makes the tools more independent of the target architecture and the compiler implementation. Additionally, this gives the user the freedom to easily analyze and manipulate the generated design without touching the implementation.

- 5. Design a profiler to give the user an idea of which parts to parallelize. Otherwise, the user would need to guess and parallelize with trial and error.

- 6. Investigate concepts to also parallelize loops, which are often steps consuming much processing time.

- 7. Develop concepts to detect used peripherals from the source-code. On the one hand, this allows the parallelizer to adapt to peripheral interaction. On the other hand, the necessary hardware infrastructure in terms of cores, interconnects and peripherals per core can be inferred.

- 8. In the last step, an automatic parallelization tool can be designed, using the previously developed tools. The different intermediate tools allow an easy exchangeability to adapt for new target platforms. An application performance profile should be automatically analyzed and annotations can automatically be set for the previously developed parallelization tool. The automatic parallelization tool should extract only as much parallelism as necessary to fulfill user defined requirements. The user must specify a minimum input processing rate as often demanded by embedded systems. Besides the parallelized software, a multi-core hardware design should be provided by the parallelization tool. Different interconnects should be evaluated to get the necessary performance with resource efficient interconnect. The tool should be able to obey restricted hardware bounds since differently sized FPGAs exist or other digital systems are also desired on the same FPGA.

The following pages describe the state of the art, related work and the shortcomings of existing tools in more detail. Afterwards, the chosen target architectures are analyzed, the tool's implementation details are highlighted and design choices are described according to the work plan. The quality of the implemented automatic parallelization tool is evaluated with respect to different implemented optimizations to increase extractable parallelism. A conclusion is given at the end and suggestions for future work are made.

#### 2 State-of-the-Art

In this section, firstly multi- and many-core architectures are reviewed in Section 2.1, with a specific focus on low-performance embedded domain. Afterwards, Section 2.2 discusses different possible design choices for extracting parallelism out of sequentially written applications. Last but not least, in Section 2.3 different parallelization tools are reviewed, categorized by their programming paradigm.

#### 2.1 Multi-/Many-Core SoC Platforms

For many years the performance of processors was mainly increased through higher frequencies. When high-end processors surpassed the 4 GHz domain around year 2000, power consumption and wire delays became the dominant problems, limiting further scaling by frequency [1]. Researchers became aware of this dead-end by the 80s and had already researched multi- and many-core architectures. In 2001 the first dual-core processor (IBM POWER4) for personal computers was released. With the first multi-cores, the overall performance of the system was boosted, given that the application is able to leverage multiple cores. Also, multiple cores at lower clock rates achieved lower power consumption at the same level of performance, compared to a higher clocked single-core design [2]. Over the years, the core count of multi-core processors increased continuously from two up to hundreds or thousands of cores, which are then typically referred to as many-core processors.

The term "embedded processor" can be widely stretched to also cover high performance desktop/server processors embedded into a technical device which needs to be controlled or supervised. However, in the context of this work, the focus is on processors with low power consumption, small size at low cost which, implies more or less limited processing power.

In the following, the architectures are separated into multi- and many-core as well as configurable soft-core multi-processor system-on-chips (MP-SoCs), with the latter being able to cover both of the former domains, depending on user configuration.

#### 2.1.1 Embedded Multi-Core Architectures

Today's embedded multi-core processors are widely dominated by ARM. ARM processors are widespread in many electronic systems, such as smartphones, automotive applications, sensors, medical devices or modems and routers. Devices requiring considerable processing power, such as smartphones, nowadays leverage System-On-Chips (SoCs) with multiple ARM high performance Cortex-A<sup>1</sup> series cores. Due to their popularity, there are many vendors producing Cortex-A multi-core SoCs: Freescale iMX<sup>2</sup>, Apple Ax, Samsung Exynos<sup>3</sup>, HiSilicon Kirin<sup>4</sup>, MediaTek MTxxxx and Helio<sup>5</sup>, RockChip RK3xxx<sup>6</sup>, Qualcomm Snapdragon<sup>7</sup>, Nvidia Tegra<sup>8</sup> etc., just to name a few. These SoCs are shared-memory architectures, typically with a bus-based cache coherency protocol and nowadays often contain between four and eight cores. ARM's newest interconnect (CMN-600<sup>9</sup>) is even implemented as a mesh network, allowing for good

Product brief: https://www.arm.com/products/silicon-ip-cpu

Product brief https://www.nxp.com/products/processors-and-microcontrollers/arm-based-processors-and-mcus/i.mx-applications-processors:IMX\_HOME

Product brief: https://www.samsung.com/semiconductor/minisite/exynos/products/mobileprocessor/exynos-9-series-9820/

Product brief: http://www.hisilicon.com/en/Products/ProductList/Kirin

Product brief: https://www.mediatek.com/products/smartphones/helio-x

<sup>6</sup> Product brief: https://www.rockchip.nl/

Product brief: https://www.qualcomm.com/snapdragon

<sup>8</sup> Product brief: https://www.nvidia.de/object/tegra-de.html

Product brief: https://developer.arm.com/products/system-ip/corelink-interconnect/corelink-coherent-mesh-network-family/corelink-cmn-600ae

scalability beyond eight cores. Due to the variety of ARM's Cortex-A cores in terms of power and performance, ARM's big.LITTLE[7] concept is used in many mobile SoCs. High efficiency cores are used during low performance, low power scenarios and less efficient, high performance cores are switched on when required. The kernel scheduler implementation defines whether switching between the performance and efficiency cluster/cores is possible on a per-core basis or only for the whole cluster. Alternatively, heterogeneous task scheduling can be implemented. The performance of Cortex-A series processors is good enough to even run a recent full desktop operating system as shown with the Raspberry Pi project.

Besides the Cortex-A series, ARM also offers the Cortex-R and Cortex-M series targeting real-time and very low power, performance and cost. The multi-core SoCs for these processors are not as widely addressed by the vendors as for the Cortex-A series. NXP Semiconductors has the LPC4300<sup>10</sup> containing one powerful ARM Cortex-M4F and one or two low performance ARM Cortex-M0. The M0 is designed to mainly handle peripheral interaction while the M4 does compute-intensive work. It is a shared-memory 32-bit architecture with interconnect over Advanced High-performance Bus (AHB). Texas Instruments has the OMAP5 series<sup>11</sup> containing two very powerful Cortex-A15 and two Cortex-M4. The M4 can be used for low-power offload and real-time tasks. Even though it has two M4 cores, the chip rather belongs to the high performance embedded domain through the Cortex-A15 cores, with the M4 rather resembling a co-processor. The Espressif ESP32<sup>12</sup> is a Tensilica Xtensa 32-bit LX6 symetric multi processor (SMP) dual-core. The device is able to run FreeRTOS and thus task scheduling becomes possible. Besides interaction between multiple peripherals, the device is even capable of running for example a simple web-server. The Parallax Propeller<sup>13</sup> is a 32-Bit hexa-core with a distributed-shared memory architecture with its own instruction set architecture (ISA). Each core has its own 2KB RAM and a round-robin arbitrated shared 64KB memory partly used as RAM and ROM. Quite uniquely, all cores can have simultaneous read/write access to the same peripheral pins and have to synchronize over mutexes. When it comes to peripherals, many microcontrollers include hardware for SPI or I<sup>2</sup>C, while the Propeller has dedicated cores for protocol handling. However, dedicating peripherals to cores and thus also dedication interrupts, the reaction time to multiple interrupts becomes smaller and also more predictable. Each core delivers 20 MIPS per core and is thus comparable with the Cortex-M0. Parallax later also released the Propeller 2 with up to 16 cores at a slightly higher clock.

#### 2.1.2 Embedded Many-Core Architectures

Many-Core processors offer much processing power due to the high number of cores. Image processing is a application field that can very well make use of many-core architectures. Image processing is also often applied in the domain of embedded computing. Many-core architectures realized as single instruction multiple data (SIMD) processors are often proposed for low-power, high-efficiency. However, those architectures mostly focus on dividing data sets into multiple parts and applying parallel (floating-point) operations only. This approach works well for scenarios having high data parallelism to leverage, but these architectures lack in applicability to general purpose computing without data parallelism. Examples are embedded graphics processing units (GPUs) as found in today's smartphones and also other products like Hiveflex ISP2300[8], ClearSpeed CSX series[9], Intel's Myriad X<sup>14</sup> and Teraflop-s/Polaris[10], Imagine Stream Processor[11] and it's commercialized variant SPI Storm 1. The Imagine Stream Processor is slightly different. Its ability to model processing pipelines through a series of cores is unique. These pipelines are realized over direct local connections instead of using rather limited

Product brief: https://www.nxp.com/products/processors-and-microcontrollers/arm-based-processors-and-mcus/lpc-cortex-m-mcus/lpc4300-cortex-m4-m0:MC\_1403790133078#/

Product brief: http://www.ti.com/pdfs/wtbu/SWCT010.pdf

Datasheet: https://www.espressif.com/sites/default/files/documentation/esp32\_datasheet\_en.pdf

Datasheet: https://www.parallax.com/sites/default/files/downloads/P8X32A-Propeller-Datasheet-v1.4.0\_0.pdf

Product brief: https://www.movidius.com/myriadx

global communication paths. Another area to which these architectures are suited well is the upcoming artificial intelligence (AI) trend, which demands high parallel floating-point performance. Compared to traditional GPUs, many hardware parts can be stripped off to get highly efficient low-power AI coprocessors.

Besides SIMD approaches, multiple instruction multiple data (MIMD) designs exist, being designed as co-processors and some as standalone architectures. In MIMD, each core is able to run its own task on its own data set, independent of other cores. A hybrid SIMD, MIMD approach is the Cell processor[12]. It contains one PowerPC general purpose processor and multiple (usually eight) synergetic processing elements (SPEs) acting as co-processors. These co-processors have dual issue pipelines, one for floating-point and one for non-floating-point operations. Each co-processor is implemented as SIMD processor with multiple execution units, while all SPEs are organized as MIMD processors.

Due to high processing power demands in the high-performance computing domain, many-core architectures are often designed to achieve high processing power through a high number of powerful and feature rich cores. However, with peak performance comes high power consumption, making these processors mostly suitable for servers or high-end PCs. Examples for these processors are AMD's EPYC<sup>15</sup> processors with up to 32 cores or Intel Xeon Platinum 8xxx<sup>16</sup> series with up to 28 cores. AMD uses tightly coupled clusters[13] with up to eight cores. The clusters have direct connections to other clusters, while Intel uses a 2D Mesh to connect all cores. Intel's Xeon Phi started out as co-processors cards and became a standalone architecture with the Knights Landing generation. In contrast to general purpose server processors, their implemented cores have a simpler architecture to allow combinations of up to 72 processor cores. However, with so many cores, inter-core communication and accesses to global memory become a major burden with standard bus protocols. This is demonstrated by Xeon Phi's use of multiple ring buses that were later replaced by a 2D mesh. These architectures are surpassing 100W of power consumption and are out of this works scope, even though they nicely show the newest trends of many-core processors.

The concept of Mesh interconnects or Network-on-Chips (NoCs) in general is also used for lower performance architectures among the embedded domain. A lot of these processors target networking appliances, cloud computing, image and audio processing and many others. Specifically targeting network appliances are for example Cavium Networks' Octeon CN38XX<sup>17</sup> which contain a maximum of 16 MIPS64 cores connected via bus. NXP's T4240<sup>18</sup> contains twelve processing cores communicating through a not further specified point-to-point network called QorIQ. Moving towards chips with hundreds of cores, the interconnect structures mostly implement variants of a 2D mesh. Broadcom's XLP900<sup>19</sup> can be configured with 640 MIPS cores and Kalray's MPPA Manycore<sup>20</sup> contains 1024 very long instruction word (VLIW) cores, both configured as clusters, interconnected by a 2D mesh. Adapteva's Epiphany V[14] also contains 1024 very small reduced instruction set architecture (RISC) cores, interconnected by a 2D mesh. These systems are in general powerful enough to run an operating system, and have even with that many cores a mid range power consumption of 5 to 50 Watt.

Moving further into the low power domain, Toshiba[15] presented a chip with 64 VLIW cores and many special purpose accelerators interconnected through a tree-based NoC. The HyperX hx3100 processor[16] contains 100 processing elements connected through a 2D mesh. Both systems consume

Product brief: https://www.amd.com/de/products/epyc-server

Product brief: https://ark.intel.com/content/www/us/en/ark/products/120496/intel-xeon-platinum-8180-processor-38-5m-cache-2-50-ghz.html

<sup>17</sup> Product brief: https://www.cavium.com/pdfFiles/OcteonCN38XX\_CN36XX\_PB-Jan29-06-web-v1.pdf

Product brief: https://www.nxp.com/docs/en/fact-sheet/T4240T4160FS.pdf

Product brief: https://www.broadcom.com/products/embedded-and-networking-processors/communications/xlp900/

http://www.kalrayinc.com/IMG/pdf/FLYER\_MPPA\_MANYCORE.pdf

around 1W of power, which makes them good representatives for a low-performance and low-power embedded many-core system.

Besides commercial processors and many other 2D-mesh-like architectures with slight variations, there also exist research architectures dealing with aspects and hardware constructs off the beaten track. Apple-CORE[17] uses UTLEON3[18] processor cores bundled in clusters of four cores and clusters are connected through a NoC. The peculiarity of the design lies in the ability of the processors fast hardware-based task switching mechanism to hide communication latencies. It has hardware units to organize software concurrency among the cores instead of leaving it to the operating system (OS). The Ne-XVP[8] architecture also utilizes the strengths of Apple-CORE, such as multi-threaded cores and a hardware task scheduler. The peculiarity here is that the scheduler synchronizes data to cores based on software defined checkpoints elaborated by means of the ACOTES programming model (see Section 2.3.4). Synchronization happens via configurable *cache-to-cache tunnels*. XGRID[19] uses a scalable 2D grid of simple, low performance RISC cores forming a distributed memory system. The interesting part is the interconnect network which is very similar to current FPGA routing resources. The application is transformed into a Kahn Process Network (KPN), which is then mapped to the processors. The interconnects are configured accordingly at compile time.

Another class of processors are coarse-grain reconfigurable architectures (CGRAs)[20] which is an intermediate between fully reconfigurable FPGAs and usual processors. This means that a CGRA has some more complex structures like processing elements whose interconnect network can be dynamically configured through so called contexts, realizing a series of operations on input data. To run an application on such a processor, it is transformed into a control data flow graph (CDFG) which is then translated to multiple contexts mapped to the CGRA. The CGRA needs reconfigured upon every context switch. The similarity of CGRAs with the concepts in this work are the synchronization of processors/processing elements through arrival of data and the adaption of the hardware to the application's data flow. However, the reconfiguration in this work doesn't happen during application runtime and data flow is extracted at a coarser level.

#### 2.1.3 Soft-core multi-/many-cores

Besides all previously shown commercial processors and research projects with configurable processor count and interconnects there also exists the class of soft-core processors. These processors are often described in hardware desciption language (HDL) and they can be synthesized on an FPGAs. Those processors come in handy when off-the-shelf solutions do not provide the needs or the hardware environment is rapidly changing (during development) with different requirements to the processor. There already exists a broad variety of soft-core processors for different instruction sets and bit widths. Some are one-man projects, some are university research projects and others are soft-cores provided by FPGA manufacturers. The man-power behind the projects also usually reflects the eco-system's comprehensiveness such as presence of a debugger, compiler, documentation, system-builder or available peripherals. Since FPGAs have grown considerably, multi- and even many-core systems become realizable. At the moment, most soft-core SoC kits deliver very limited support for multiple cores out-of-the-box.

One of the most popular soft-cores is the MicroBlaze[21] with many ISA compatible clones. To support multi-cores the following components exist: A common global memory, a mutex peripheral and a FIFO based bidirectional inter-core communication peripheral for distributed-memory systems called Mailbox<sup>21</sup>, formerly known as fast simplex link (FSL). The PicoBlaze, MicroBlaze's smaller 8 bit sibling, has no multi-core support provided. Intel (former Altera) has the NiosII, a 32 bit RISC soft-core. The NiosII uses the Qsys interconnect<sup>22</sup>, a dedicated N-to-M master-slave interconnect, for inter-core communica-

Product brief: https://www.xilinx.com/products/intellectual-property/mailbox.html

Datasheet: https://www.intel.co.jp/content/dam/altera-www/global/ja\_JP/pdfs/literature/hb/qts/qsys\_interconnect.pd

tion. Access to slave components, such as peripherals, is shared by all masters and can be exclusively locked using integrated mutexes. Furthermore, communication is possible via a shared memory located in the .data section<sup>23</sup>. Lattice's LatticeMicro32<sup>24</sup> is not advertised to have dedicated multi-core peripherals or mechanisms. The only option are third-party peripherals connected to the integrated Wishbone bus. Cobham Gaisler's (formerly Aeroflex Gaisler) Leon soft-cores can be configured as a multi-processor system<sup>25</sup>. Multiple processors share a common memory and peripheral bus. Inter-core communication thus happens via the common memory.

The SpartanMC SoC kit[22] offers different variants of inter-core communication for it's soft-core. Communication is possible via 1-to-1, 1-to-N and N-to-1 peripherals. Each either as FIFO-based or DMA-like variant. Additionally, shared data and/or program memory is possible.

In conclusion, soft-core vendors mostly deliver quite limited multi-core functionality. However, the user can always use one of the aforementioned cores together with a custom third-party (open-source) interconnect and trust in the interconnects compatibility to future processor releases.

#### 2.1.4 Conclusion

As shown in Section 2.1, many multi-core systems still rely on a common central bus architecture nowadays. With additional cores, these systems are running into the memory wall [3] and thus cannot fully utilize available processing power. This is one reason why many-core designs moved towards 2Dmesh-like core-interconnects, often with distributed memory. This step shows the need for localized communication in combination with lower communication interference compared to classical bus structures. Generic 2D mesh structures may work well for processors that must have the ability to execute arbitrary applications. However, in the embedded domain, a processor might run a specific application for years. Traditionally, this application is written to leverage a target multi-core processor as much as possible. Choosing an off-the-shelf processor might limit future extensibility of the software and potentially require to target the application to a new processor. It would be promising to adapt the processor and the communication infrastructure to the application and not vice versa. FPGAs in combination with soft-core processors provide the freedom to generate an arbitrary number of cores and communication infrastructure ideally suited to the application's communication pattern, emphasizing communication locality. Additionally, FPGAs allow continuous adaption to changing requirements. However, the price to pay for the reconfigurability is, in contrast to an application-specific integrated circuit (ASIC), a lower achievable clock speed, a lower energy efficiency [23] and a higher per unit price.

Since the full reconfigurability provided by FPGAs is not needed, one could settle for a less reconfigurable platform in the future to regain clock frequency and energy efficiency. Thus, it is thinkable to use a platform such as the proposed XGRID[19]. The cores and peripherals are fixed hardware and the interconnect network can form arbitrary point-to-point connections configured at compile time.

The proposed concept of this work could also be applied to hard processors, even though the benefit of hardware adaptability is lost. The software challenge would shift from generating the required hardware, to efficiently mapping the software to a given hardware, which is actively researched in Daedalus[24] for example.

Intel tutorial: https://www.intel.com/content/dam/altera-www/global/en\_US/pdfs/literature/tt/tt\_nios2\_multiprocessor\_tutorial.pdf

Product brief: http://www.latticesemi.com/en/Products/DesignSoftwareAndIP/IntellectualProperty/IPCore/ IPCores02/LatticeMico32.aspx

Vendor design reference: https://www.gaisler.com/doc/antn/GRLIB-AN-0005.pdf

#### 2.2 Extracting Parallelism from Applications: Design Choices

There already exists a huge amount of approaches for parallelizing applications leveraging multi- and many-core systems. The existing solutions differ in the programming paradigm which specifies the instruments that the user has at hand for parallelization as well as the partitioning level indicating the language constructs and task granularity. The tools also differ in the target hardware architecture which allows parallelization only for specific processors or requires a shared and/or distributed memory architecture specifically for inter-core communication.

#### 2.2.1 Programming Paradigms

There are different programming paradigms to extract parallelism from applications. The approaches mainly differ in the effort required to express parallelism and the kinds of parallelism that can be modeled. The existing approaches can be summarized into the following categories and according examples are named in Section 2.3.

Domain specific languages (DSLs): A custom language for expressing parallelism. The language models parallelism implicitly through specific constructs. Some DSLs are very close to commonly known general purpose languages and only modify/add specific aspects and thus are counted as language extensions. A new compiler is always needed to translate the language. The benefit of a DSL is that parallelism can be very well modeled and a high degree of parallelization can often be achieved. However, the user has to learn how to use a new language. It also highly depends on the experience and skill of the developer how successful the parallelization will be. In general, the user effort to rewrite an existing application in a DSL can be relatively high.