© 2019 Enver Candan

#### IMPROVING DATA CENTER POWER DELIVERY EFFICIENCY AND POWER DENSITY WITH DIFFERENTIAL POWER PROCESSING AND MULTILEVEL POWER CONVERTERS

BY

ENVER CANDAN

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2019

Urbana, Illinois

Doctoral Committee:

Associate Professor Robert C. N. Pilawa-Podgurski, Chair Professor Philip T. Krein Professor Alejandro Domínguez-García Assistant Professor Arijit Banerjee Dr. Pradeep S. Shenoy, Texas Instruments

## ABSTRACT

Existing data center power delivery architectures consist of many cascaded power conversion stages. The system-level power delivery efficiency decreases each time the requisite power is processed through the individual stages, and the total power converter footprint increases by each cascaded conversion stage. Innovative approaches are investigated in this dissertation for dc-dc step-down conversion and single-phase ac-dc conversion to improve power delivery efficiency and power density in data centers. This dissertation proposes a series-stacked architecture that provides inherently higher efficiency between a dc bus and dc loads through architectural changes, reporting above 99% power delivery efficiencies. The proposed series-stacked architecture increases power delivery efficiency by connecting the dc loads in series to allow the bulk of the requisite power to be delivered without being processed and by reducing overall power conversion using differential power processing. The series-stacked architecture exhibits voltage regulation and hot-swapping while delivering power to rapidly changing computational loads. This dissertation experimentally demonstrates series-stacked power delivery using real-life computational loads in a custom designed four-server rack. In order to provide a complete grid-to-12 V power delivery for data center applications, this dissertation also proposes a buck-type power factor correction converter that yields high power density between a single-phase grid and the dc bus, achieving 79  $W/in^3$  power density. The proposed buck-type power factor correction converter improves power density by eliminating the high-voltage step-down dc-dc conversion stage, which is typically cascaded to boost-type power factor correction converters in conventional data center power delivery architectures, and by leveraging recent developments in flying capacitor multilevel converters using wide-bandgap transistors. The buck-type flying capacitor multilevel power factor correction converter presents a unique operation condition where the flying capacitor voltages are required to follow the input voltage at 50/60 Hz. This dissertation experimentally explores the applicability of such an operation by using a digitally controlled six-level flying capacitor multilevel converter prototype.

To Miranda, my parents Ali and Mahinur, and my sister Sebnem.

## ACKNOWLEDGMENTS

When I reminisce about my time in Champaign-Urbana, I very much appreciate this little town, which many would sniff at because of its location, for being the place where my path has crossed with those of many amazing people. I am grateful for those who directly or indirectly made my graduate student life remarkable, and will do my best to acknowledge them all here. It is said that the two most important people in a Ph.D. student's life are his/her advisor and spouse. I am so fortunate that I met with both of them at the University of Illinois at Urbana-Champaign.

I must start with thanking Professor Robert C. N. Pilawa-Podgurski, my advisor, for accepting me to his research group at Illinois, because it has been a life-changing opportunity for me. I am grateful for his guidance through my career, for his trust in me during the projects, and for his support in attending many conferences and workshops all around the globe. Owing to the freedom he provided me during my time at Illinois, my graduate school experience exceeded pure research and included organizing conferences and working at several technology companies. His enthusiasm for power electronics teaching and research has always been a source of inspiration for me. I admire the research group culture he created and upheld while guiding more than a dozen graduate students through some of the most challenging projects. I am fortunate to be able to learn from his hands-on experience in power electronics to become a better engineer and researcher.

I would like to thank Professor Philip T. Krein, Professor Arijit Banerjee, Professor Alejandro Domínguez-García, and Dr. Pradeep S. Shenoy for being on my doctoral committee and sharing their valuable time and knowledge. I especially would like to thank Prof. Philip T. Krein for his advice on the ac-dc power conversion portion of this dissertation, and Dr. Pradeep Shenoy for his feedback on the series-stacked power delivery portion of this dissertation, and for his mentorship over the years. I would also like to thank all the professors in the Power and Energy group at Illinois, especially Professor Pete Sauer for holding the Power and Energy Systems group together, his support in organizing the Power and Energy Conference at Illinois, and the amazing speeches he gave during many gatherings. Also, I am thankful to Professor George Gross, as I found out at the beginning of my final exam that he made my admission to Illinois possible by bringing my application to Professor Pilawa-Podgurski's attention.

I am pleased to be a member of the Pilawa-Group at Illinois. I learned a lot from every experience I had with members of the group, past and present: Yutian Lei, Shibin Qin, Christopher Barth, Andrew Stillwell, Thomas Foulkes, Nathan Pallo, Tomas Modeer, Nathan Brooks, Yizhe Zhang, Zichao Ye, Zitao Liao, Josiah McClurg, Derek Heeger, Maggie Blackwell, Pourva Assem, Derek Chou, Wen-Chuen Joseph Liu, Pei Han Ng, Samantha Coday, Jeff Wheeler, Yujia Zhang, Eric Saathoff, Intae Moon, Adwaita Dani, Benedict Foo, Won Ho Chung, Aaron Ho, Ben Macy, Yuqi Li, Roy Bell, Marcel Shuck, and many more. Thank you all for your sincere friendship in this journey. Nowadays, what one can learn from papers and textbooks is the same anywhere in the world. I believe what made my dissertation and research unique in many ways is working with you, so I thank you all for that. I would like to especially acknowledge Andrew Stillwell for his help on the power factor correction portion of this dissertation; Shibin Qin, Zitao Liao and Nathan Brooks for their help on developing the power factor correction microcontroller code; Nathan Pallo, Thomas Modeer, and Maggie Blackwell for their help in flying capacitor multilevel converter design; Thomas Foulkes and Christopher Barth for their help on frequency response analysis and countless discussions in the lab as we work on our own projects; and Josiah McClurg, Yizhe Zhang, Jeff Wheeler, and Yujia Zhang for their help in development of the series-stacked testbed. Your genuine help reduced the workload on my shoulders during the development of this dissertation. It is much appreciated.

Many incredible people at Illinois have become my friends and made my time in graduate school a very delightful experience: In addition to the members of the Pilawa-Group mentioned above, I thank Shamina Hossain-McKenzie, Giang-Chau Ngo, Mehmet Kurt, Itir Akgun, Onur Gur, Sezer Ozerinc, Bilge Acun, Tutku Buyukdegirmenci, Maryam Kazerooni, Andy Yoon, Cecilia Klauber, Adriano Lima Abrantes, Jason Galtieri, Dipanjan Das, Phuc Thanh Huynh, Siddhartha Nigam, Mariola Ndrio, Soteris Demetriou, Dimitra Apostolopoulou, Kai Van Horn, Stanton Cady, Matt Magill, Stanton Cady, Trevor Hutchins, and many more. Thank you all for your friendship; knowing you all has been a true pleasure. I hope we can keep in touch.

The Electrical and Computer Engineering staff have helped me tremendously during my time at Illinois. I would like to thank Joyce C. Mast and Robin Lynn Smith for administering the Power and Energy Systems group, from filing reimbursements to organizing many social events that I had always looked forward to attending. Thanks to Kevin Colravy for managing the research and teaching labs; Beverly Curtis, Stephanie Schneider, Joshua McNattin, and Clint Harper for handling an enormous amount of purchase orders and shipments that made the experimental work in this dissertation possible; and James Hutchinson for proofreading and editing many of my publications, including this dissertation.

I also would like to thank the Fulbright Commission in Turkey and the Institute of International Education for supporting my master's degree at Illinois. Thanks to them, I was able to make it to the United States and attend my dream with the privilege of being a Fulbright Scholar. I would like to thank the IEEE Power Electronics Society for choosing me as the 2017 recipient of the IEEE Joseph John Suozzi INTELEC Fellowship Award in Power Electronics. I also would like to acknowledge the financial support from Texas Instruments, Google, National Science Foundation under Grant 1509815, and Advanced Research Projects Agency - Energy (ARPA-e), U.S. Department of Energy, under Award Number DE-AR0000906 for funding the work in this dissertation in part.

I must extend special thanks to Miranda, my wife-to-be. She has just accepted my proposal which was long overdue. Although there have been times that we had to live on different continents, she has never left me alone in this journey. Working for a Ph.D. is not easy, but I am sure putting up with its roller-coaster effect on my personal life on a daily basis is not any easier. She deserves a special acknowledgment for that. In addition, I proudly thank her for proofreading many of my writings. Since she accepted my coffee offer in Espresso Royale in Urbana, not only has she been a substantial joy of my life, she has also shown me, by example, how to become a better person. I cannot overstate her love and support, for which I am and will be always grateful.

Last but certainly not least, I would like to thank my parents, Ali and Mahinur, and my sister, Sebnem, for their unconditional love and support. My parents, sister and Miranda have made the biggest sacrifice by giving up their time with me during my graduate school. This dissertation, like my all accomplishments, is thus dedicated to them.

# TABLE OF CONTENTS

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ζ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | i |

| CHAPTER 1       INTRODUCTION       1         1.1       Research contribution       2         1.2       Organization of this dissertation       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2 |

| CHAPTER 2BACKGROUND ON DATA CENTER POWER DELIVERY42.1Common power delivery architectures in data centers42.2Efficiency72.3Reliability102.4Backup power102.5Redundancy102.6Isolation and grounding122.7Protection132.8Renewable and distributed energy sources142.9Cooling152.10Total cost of ownership15                                                                                                                                                                                                                                                                                                          |   |

| CHAPTER 3       SERIES-STACKING AND DIFFERENTIAL POWER PROCESSING         FOR DATA CENTER POWER DELIVERY       17         3.1       Motivation       17         3.2       Background on series stacking and differential power processing       18         3.3       Analysis of the server-to-virtual bus DPP architecture       21         3.3.1       Steady-state operation       21         3.3.2       Hot-swapping operation       25         3.4       Key implementation challenges       30         3.4.1       Communication across voltage domains       31         3.4.3       Hot-swapping       31 |   |

| CHAPTER 4       BIDIRECTIONAL HYSTERESIS CONTROL FOR THE SERVER-TO-         VIRTUAL BUS DPP ARCHITECTURE       32         4.1       System analysis for control discussion       32         4.2       Control objectives       35         4.3       Proposed control       36                                                                                                                                                                                                                                                                                                                                     | 2 |

|         | 4.3.1     | Voltage sampling                                                              | 37        |

|---------|-----------|-------------------------------------------------------------------------------|-----------|

|         | 4.3.2     | Current need                                                                  | 37        |

|         | 4.3.3     | Power flow direction                                                          | 37        |

| 4.4     | $C_s$ and | $C_{VB}$ sizing considerations                                                | 39        |

| 4.5     | Extens    | sion of bidirectional hysteresis control                                      | 11        |

|         | 4.5.1     | Hot-swapping                                                                  | 11        |

|         | 4.5.2     |                                                                               | 42        |

| 4.6     | Simula    | ation Study                                                                   | 14        |

|         |           |                                                                               |           |

| CHAPT   |           | EXPERIMENTAL STUDY OF THE SERVER-TO-VIRTUAL BUS DPP                           | 17        |

|         |           |                                                                               | 17<br>17  |

| 5.1     |           |                                                                               | 47        |

|         | 5.1.1     |                                                                               | 48        |

|         | 5.1.2     |                                                                               | 49<br>- 1 |

| •       | 5.1.3     |                                                                               | 51        |

| 5.2     | -         |                                                                               | 52        |

|         | 5.2.1     |                                                                               | 53        |

|         | 5.2.2     |                                                                               | 54        |

|         | 5.2.3     |                                                                               | 55        |

|         | 5.2.4     |                                                                               | 56        |

| 5.3     |           |                                                                               | 58        |

|         | 5.3.1     |                                                                               | 59        |

|         | 5.3.2     |                                                                               | 60        |

| 5.4     | Result    |                                                                               | 60        |

|         | 5.4.1     | Test I: Initialization and hot-swapping                                       | 60        |

|         | 5.4.2     | Test II: Decaying bus voltage                                                 | 67        |

| CHAPT   | FER 6     | SINGLE-PHASE AC TO DC POWER CONVERSION                                        | 70        |

| 6.1     | Motiva    |                                                                               | 70        |

| 6.2     |           | type power factor correction                                                  |           |

| 6.3     |           | · · ·                                                                         | 78        |

| 0.5     | Flying    |                                                                               | 0         |

| CHAPT   | TER 7     | BUCK PFC CONTROL                                                              | 32        |

| 7.1     | Backg     | round $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 32        |

| 7.2     |           |                                                                               | 33        |

|         | 7.2.1     | * * 0                                                                         | 35        |

|         | 7.2.2     |                                                                               | 35        |

|         | 7.2.3     | *                                                                             | 35        |

|         | 7.2.4     |                                                                               | 37        |

|         | 7.2.5     |                                                                               | 38        |

| arr · - |           |                                                                               |           |

| CHAPT   |           |                                                                               | 91        |

| 8.1     |           |                                                                               | 91        |

| 8.2     | -         | 1                                                                             | 95        |

| 8.3     |           | 1                                                                             | 96        |

| 8.4     |           |                                                                               | 97        |

| 8.5     |           |                                                                               | 99        |

| 8.6     | Flying    | capacitor voltage balancing in ac-dc buck conversion                          | )4        |

| 8.6.1 Time constant of flying capacitor voltage balancing dynamics $\ldots \ldots \ldots 104$                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.6.2 Phase-shift direction $\dots \dots \dots$ |

| 8.6.3 Impact on input and inductor current shaping                                                                                              |

| 8.7 Six-level FCML converter in universal input ac-dc conversion                                                                                |

| CHAPTER 9 CONCLUSION AND FUTURE WORK                                                                                                            |

| 9.1 Conclusion                                                                                                                                  |

| 9.2 Future work                                                                                                                                 |

| 9.2.1 Server-to-virtual bus DPP                                                                                                                 |

| 9.2.2 Buck-type FCML as a PFC converter                                                                                                         |

| APPENDIX A DESIGN FILES OF PROTOTYPE DPP HARDWARE                                                                                               |

| APPENDIX B MICROCONTROLLER CODE USED IN SERVER-TO-VIRTUAL BUS                                                                                   |

| DPP EXPERIMENTAL STUDY                                                                                                                          |

| APPENDIX C FREQUENCY RESPONSE OF A SIX-LEVEL FCML BUCK CONVERTER159                                                                             |

| APPENDIX D DESIGN FILES OF PROTOTYPE FCML BUCK CONVERTER 164                                                                                    |

| APPENDIX E MICROCONTROLLER CODE USED IN FCML BUCK PFC CON-<br>VERTER EXPERIMENTAL STUDY                                                         |

| APPENDIX F       ADDITIONAL EXPERIMENTAL RESULTS WITH SIX-LEVEL BUCK         CONVERTER                                                          |

| REFERENCES                                                                                                                                      |

# LIST OF TABLES

| 2.1 | Tier certificate requirements summary                                                                                                           | 12  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

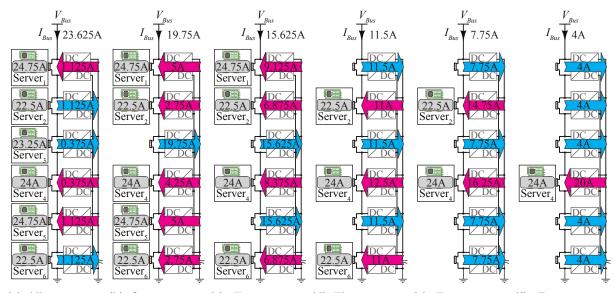

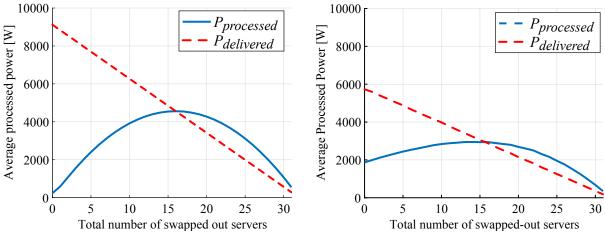

| 3.1 | Processed and delivered power in the example operations of the six-server rack in Figure 3.5, calculated by (3.13) and (3.14)                   | 26  |

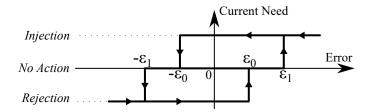

| 4.1 | Decision table for bi-directional hysteresis control                                                                                            | 38  |

| 4.2 | Decision table for extended bidirectional hysteresis control                                                                                    | 42  |

| 5.1 | Key components of the differential converter                                                                                                    | 48  |

| 5.2 | Key components of the stack initialization circuitry                                                                                            | 51  |

| 5.3 | The key components of the hot-swapping circuitry                                                                                                | 52  |

| 5.4 | The key components of the custom design current sense board                                                                                     | 56  |

| 5.5 | Breakdown of average input and output powers, efficiency, and average power                                                                     |     |

| 5.6 | loss during the experiment                                                                                                                      | 64  |

| 0.0 | loss during the experiment                                                                                                                      | 69  |

| 7.1 | Parameters used for multiloop feedback control compensator tuning                                                                               | 90  |

| 8.1 | Key components of the FCML buck-type PFC hardware prototype                                                                                     | 93  |

| 8.2 | Updated components and specifications for the two-level configuration of the hardware prototype                                                 | 98  |

|     |                                                                                                                                                 | 30  |

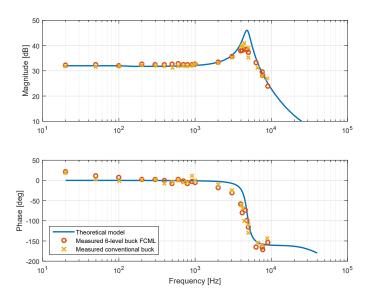

| C.1 | Updated components and specifications for the frequency response comparison of two-level and six-level configurations of the hardware prototype | 160 |

| C.2 | Control-to-output voltage frequency response of the six-level FCML buck converter .                                                             |     |

| C.3 | Control-to-output voltage frequency response of the conventional buck converter                                                                 |     |

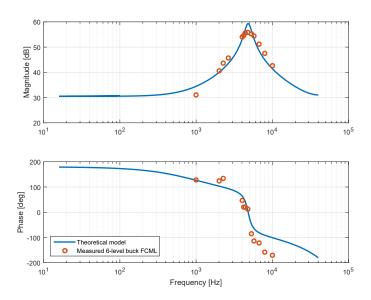

| C.4 | Control-to-output current frequency response of the six-level FCML buck converter .                                                             |     |

| F.1 | Updated components of the FCML buck stage for step-down dc-dc application $\ldots$                                                              | 185 |

# LIST OF FIGURES

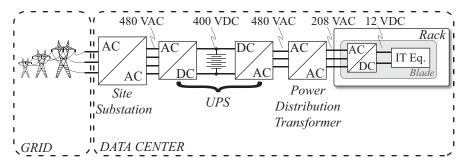

| 2.1        | Simplified drawings of common power delivery architectures in data centers. For prioritizing transition from ac to dc power distribution, protection equipment and cooling devices are not depicted in these figures, but of course exist in practical                                                                                 |          |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2        | designs and may introduce additional power conversion stages                                                                                                                                                                                                                                                                           | 5        |

| 2.3        | conversion in the power delivery architecture                                                                                                                                                                                                                                                                                          | 6<br>11  |

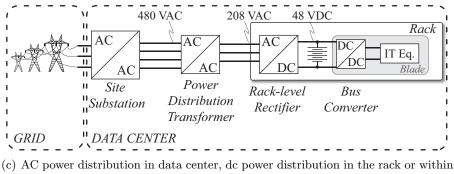

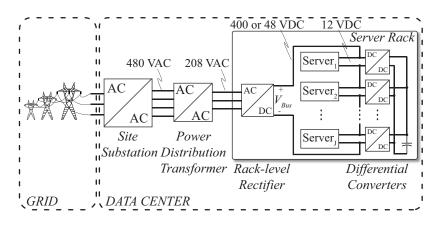

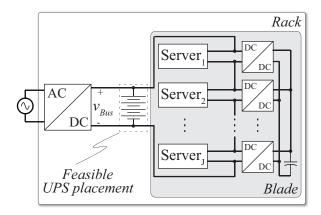

| 3.1        | AC power distribution in data center, dc power distribution in the rack. The ac power is delivered to the racks. Then, a rack-level rectification stage provides an intermediate high dc voltage to the rack. Separate dc-dc converters perform final voltage step-down at the server input.                                           | 17       |

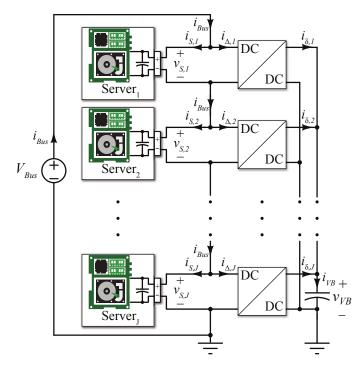

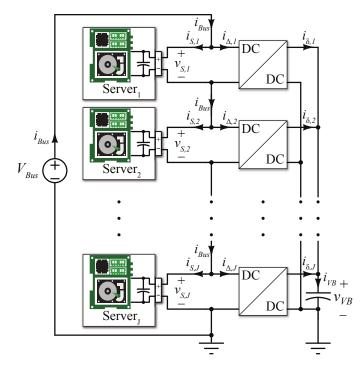

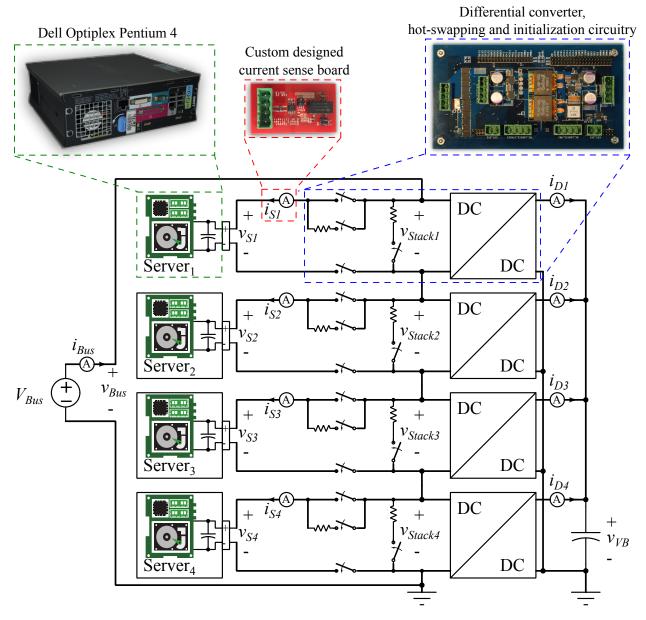

| 3.2        | Proposed server-to-virtual bus DPP power delivery architecture for server racks                                                                                                                                                                                                                                                        | 17<br>19 |

| 3.2<br>3.3 | Server-to-virtual bus DPP architecture schematic used for analysis                                                                                                                                                                                                                                                                     | 19<br>22 |

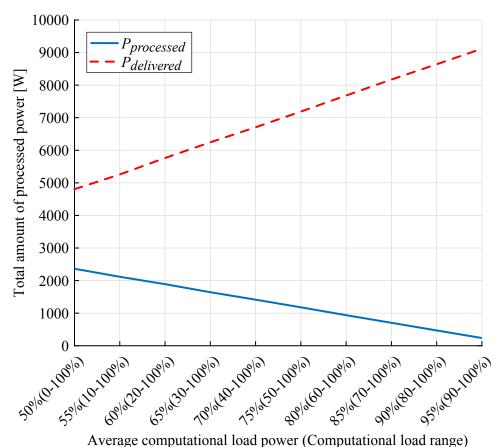

| 3.4        | A statistical comparison between total processed power and delivered power in the server-to-virtual bus DPP architecture, assuming ideal converters and a Gaussian                                                                                                                                                                     | 22       |

|            | distribution of computational load mismatch.                                                                                                                                                                                                                                                                                           | 25       |

| 3.5        | Examples of normal and hot-swapped operations of a six-server rack. Anno-<br>tated server currents correspond to a 95% average computational load with $\pm 5\%$<br>computational load range scenario when all servers are operational. Annotated<br>differential currents show direction and average amount of current flow, assuming | -        |

| 3.6        | ideal converters                                                                                                                                                                                                                                                                                                                       | 27       |

|            | architecture.                                                                                                                                                                                                                                                                                                                          | 30       |

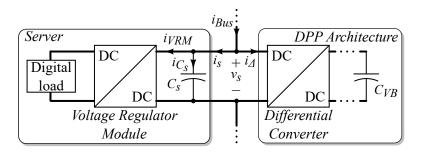

| 4.1        | Server-to-virtual bus DPP architecture schematic used for analysis                                                                                                                                                                                                                                                                     | 33       |

| 4.2        | Server model in the series-stack.                                                                                                                                                                                                                                                                                                      | 34       |

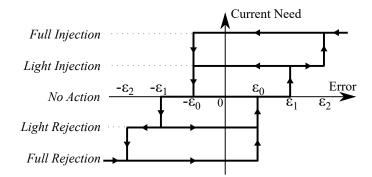

| 4.3        | Proposed bidirectional hysteresis action.                                                                                                                                                                                                                                                                                              | 36       |

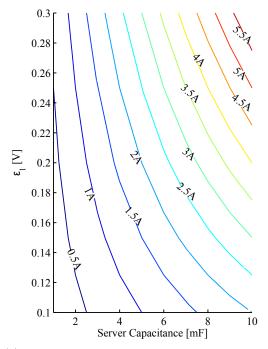

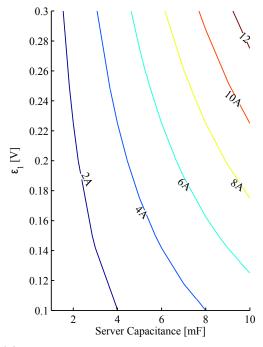

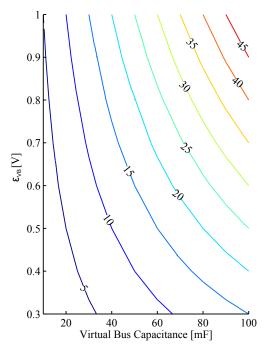

| 4.4        | Charts for $C_s$ , $C_{VB}$ , $\varepsilon_S$ , $\varepsilon_{VB}$ and $i_{\Delta}$ decisions.                                                                                                                                                                                                                                         | 40       |

| 4.5        | Extended bi-directional hysteresis shape. Note that the bidirectional hysteresis shape is generic and independently valid for each series-stacked server and the                                                                                                                                                                       |          |

|            | virtual bus.                                                                                                                                                                                                                                                                                                                           | 41       |

| 4.6        | A circuit diagram depicting feasible UPS placement in the series-stacked architecture.                                                                                                                                                                                                                                                 | 43       |

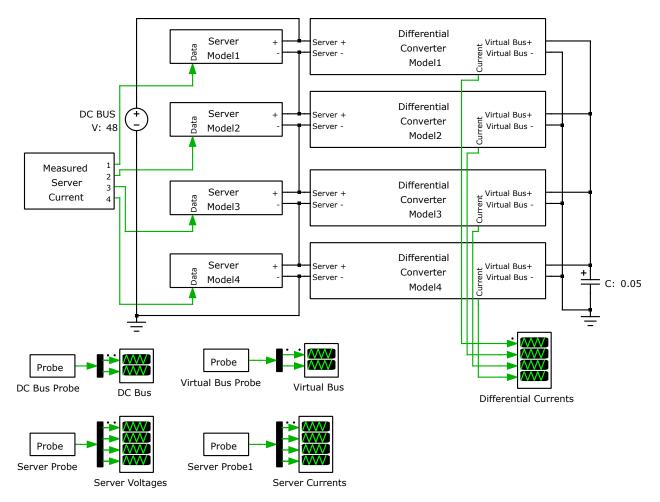

| 4.7        | Simulation schematic model in PLECS.                                                                                                                                                                                                                                                                                                   | 44       |

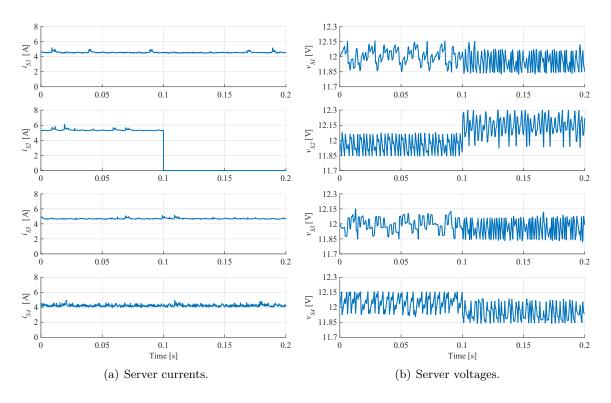

| 4.8        | Simulated server waveforms                                                                                                                                                                                                                                                                                                             | 45       |

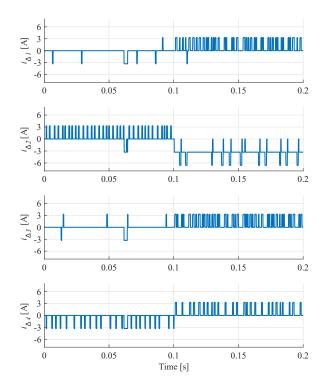

| 4.9        | Simulated differential currents.                                                                                                                                                                                                                                                                                                       | 46       |

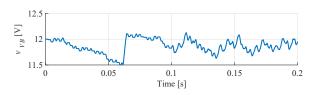

| 4.10       | Simulated virtual bus voltage                                                                | 46  |

|------------|----------------------------------------------------------------------------------------------|-----|

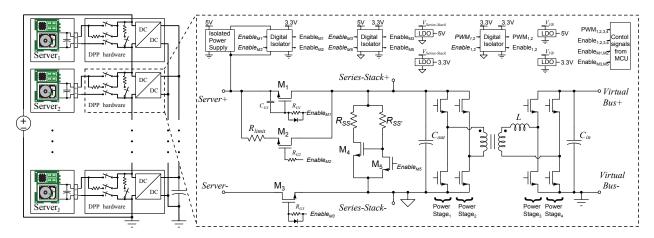

| 5.1        | Schematic of prototype DPP hardware.                                                         | 47  |

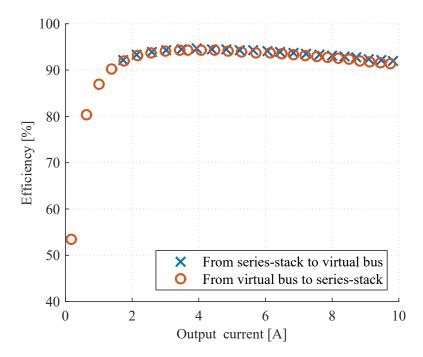

| 5.2        | Efficiency of the power stage in the hardware prototype                                      | 49  |

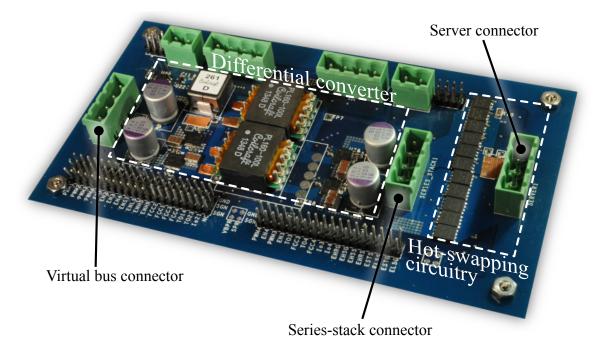

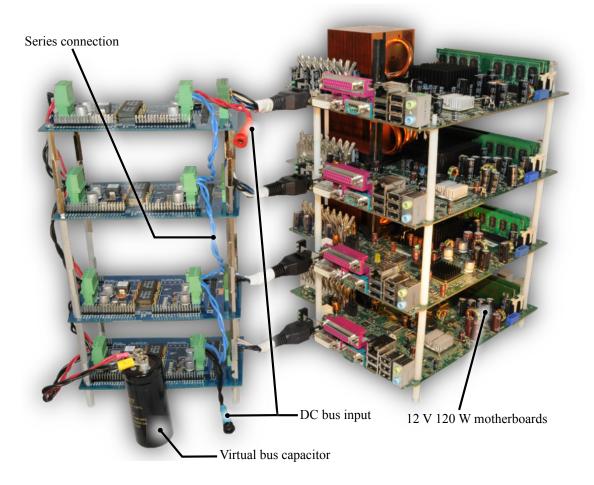

| 5.3        | Annotated photograph of the prototype DPP hardware                                           | 50  |

| 5.4        | Annotated schematic of the experimental setup                                                | 53  |

| 5.5        | Annotated picture of the testbed                                                             | 55  |

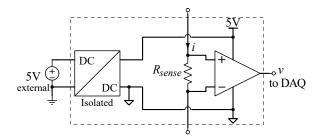

| 5.6        | Schematic of the custom designed current sense board                                         | 56  |

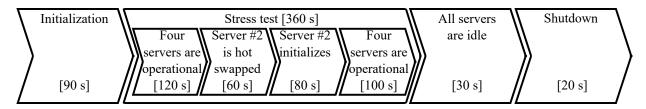

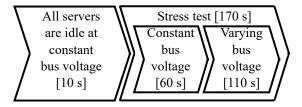

| 5.7        | A timing diagram for initialization and hot-swapping test scenario                           | 59  |

| 5.8        | A timing diagram of decaying bus voltage test scenario.                                      | 59  |

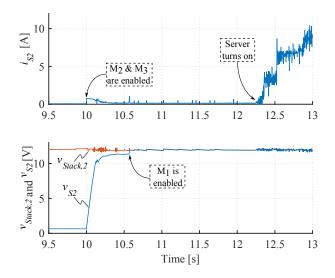

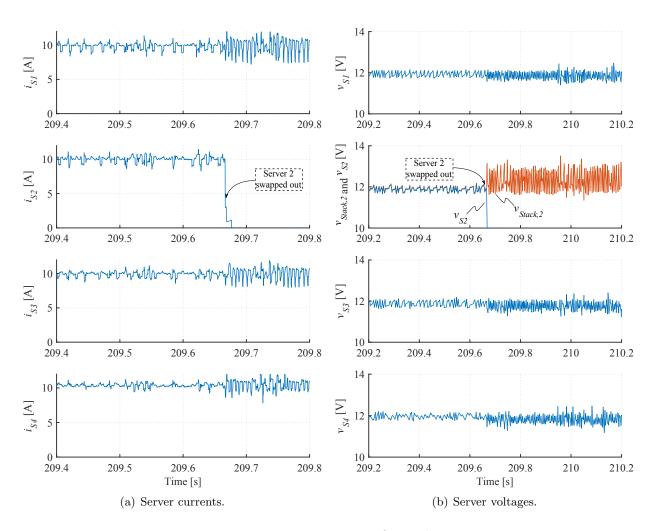

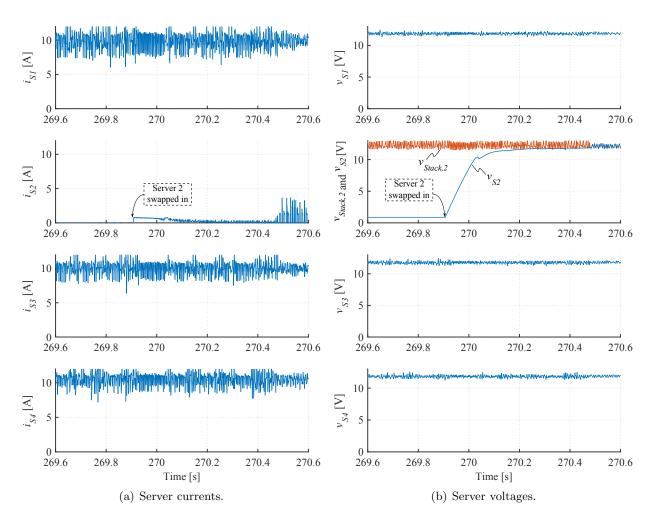

| 5.9        | Measured instantaneous data showing swapin transient of the second server                    | 60  |

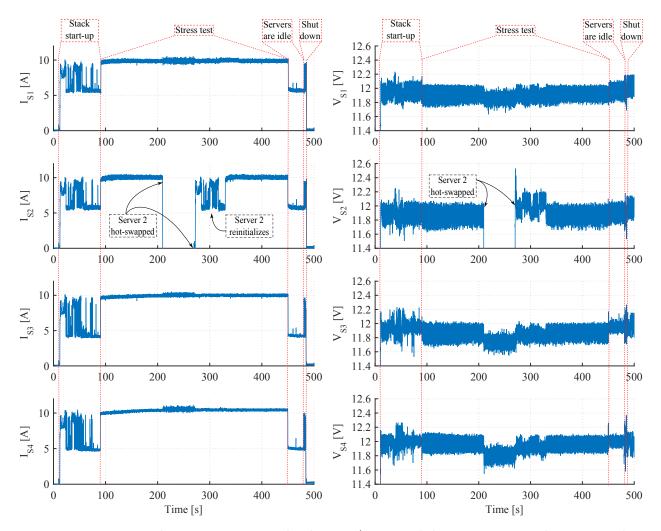

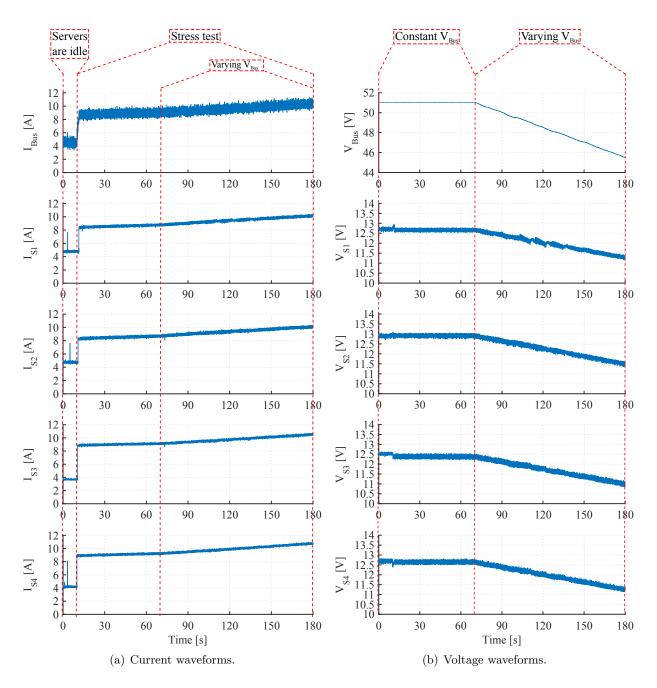

| 5.10       | Measured server currents and voltages. (Measured data is 10 ms window averaged               |     |

|            | for better illustration of the entire test on a single plot.) Major events during            |     |

|            | the experiment are annotated on the plot. Note the absence of the second server              |     |

|            | current and voltage when it is hot-swapped out of the stack                                  | 61  |

| 5.11       | Measured virtual bus voltage that shows its successful regulation. (Measured                 |     |

|            | data is 10 ms window averaged for better illustration of the entire test on a                |     |

|            | single plot.)                                                                                | 62  |

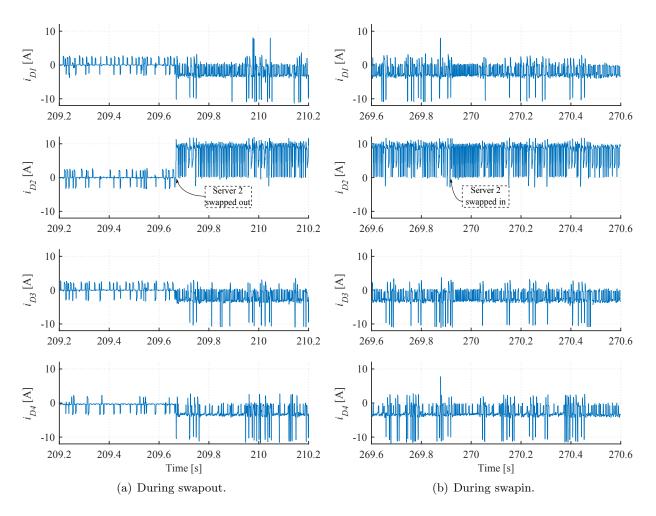

| 5.12       | Instantaneous server waveforms during swapout.                                               | 63  |

| 5.13       | Instantaneous differential currents into the virtual bus node                                | 65  |

| 5.14       | Instantaneous server waveforms during swapout.                                               | 66  |

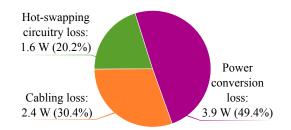

| 5.15       | A pie chart of $P_{loss,sys}$ distribution during the stress test 90 s $< t < 210$ s. During |     |

|            | this time interval, an average of 472.8 W was delivered to the servers.                      | 67  |

| 5.16       | Measured server and bus waveforms during the experiment. Measured data is 10                 |     |

|            | ms window averaged for better illustration of the entire test on a single plot               | 68  |

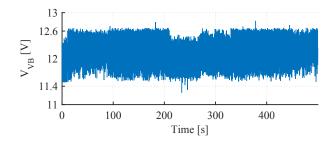

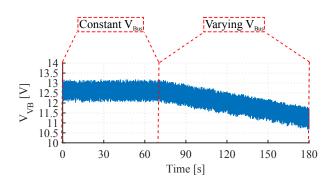

| 5.17       | Measured virtual bus voltage during the experiment. Measured data is 10 ms                   |     |

|            | window averaged for better illustration of the entire test on a single plot                  | 69  |

|            |                                                                                              |     |

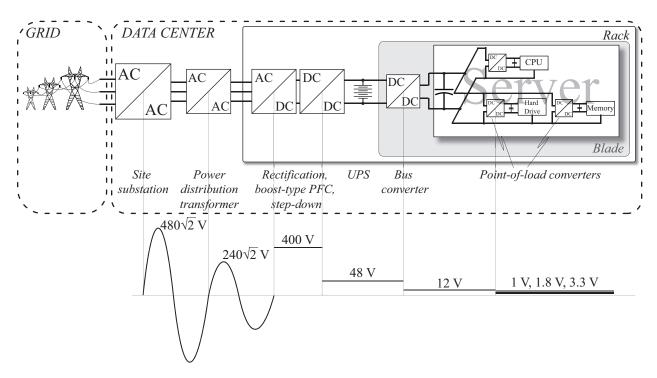

| 6.1        | An example of conventional power delivery in data centers, illustrating major                |     |

|            | power conversion stages with annotated voltage levels at each stage. $\ldots$                | 71  |

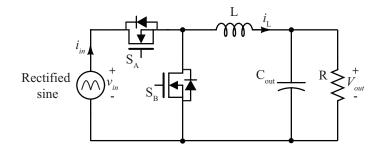

| 6.2        | Buck converter.                                                                              | 73  |

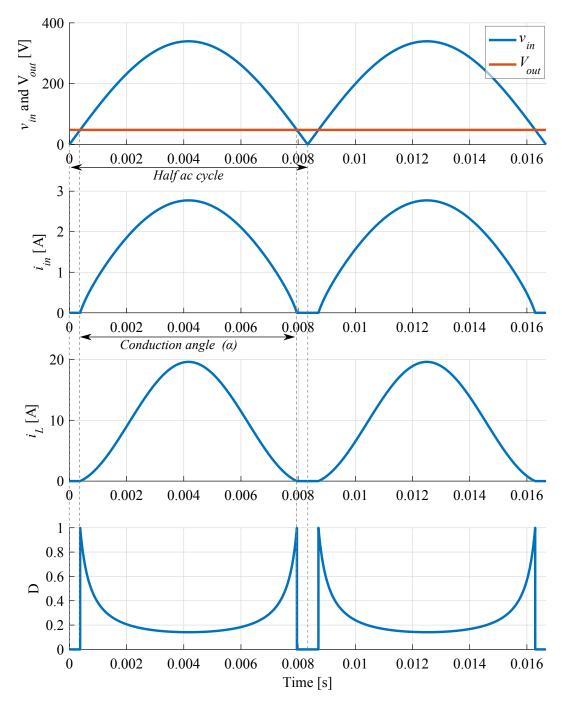

| 6.3        | The input voltage and current, inductor current, and duty cycle in a buck PFC                |     |

|            | converter for a full ac line cycle at 60 Hz, with a 10 A average output current,             |     |

|            | assuming ideal control and filtering.                                                        | 74  |

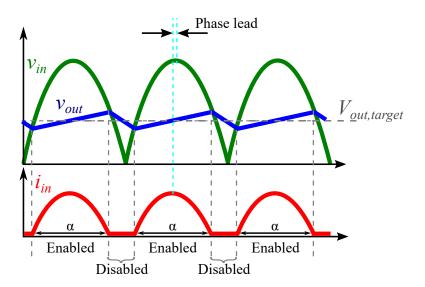

| 6.4        | Phase shift of input current due to output voltage ripple                                    | 75  |

| 6.5        | An ac-dc converter with noninverting buck-boost converter                                    | 77  |

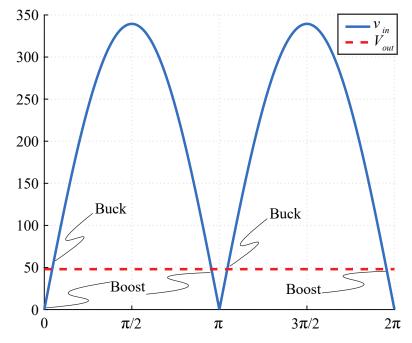

| 6.6        | Operation modes of the noninverting buck-boost converter for ac-dc rectification             | 77  |

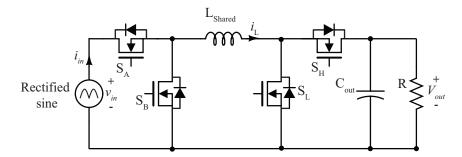

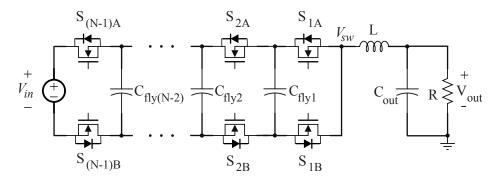

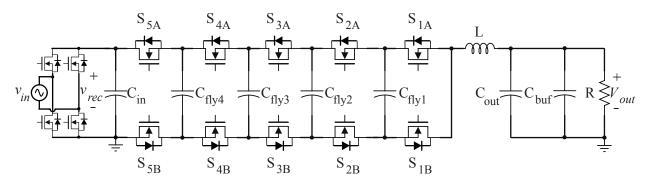

| 6.7        | <i>N</i> -level FCML converter, configured as a buck converter                               | 79  |

| <b>F</b> 1 |                                                                                              | 0.4 |

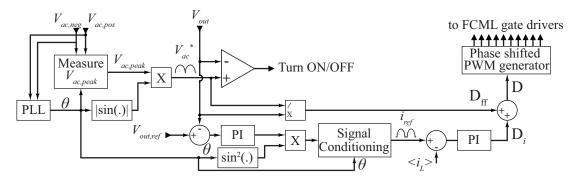

| 7.1        | High-level control diagram.                                                                  | 84  |

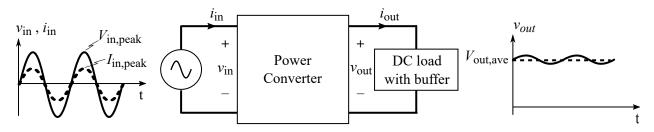

| 7.2        | A generic ac-dc power converter connected between a single-phase ac input source             | 0.0 |

| 7.0        | and a dc load that includes a twice-line frequency energy buffering element. $\dots$         | 86  |

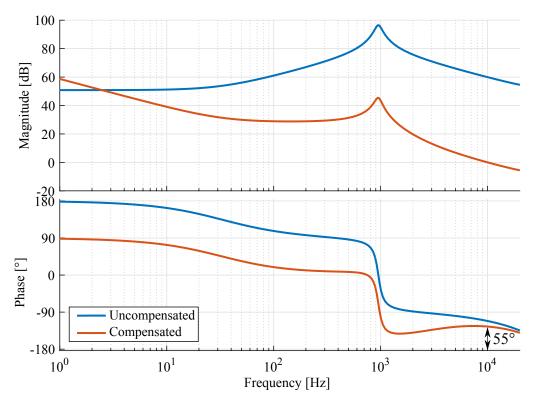

| 7.3        | The uncompensated and PI compensated loop gain of $(G_{id}(z))$                              | 89  |

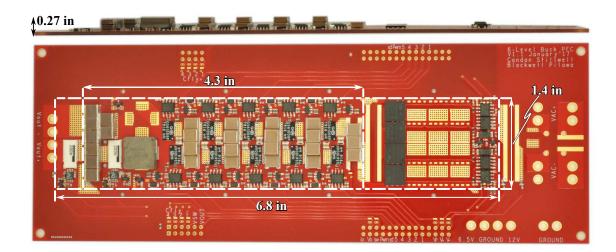

| 8.1        | The six-level FCML buck converter schematic for a single-phase PFC application               | 92  |

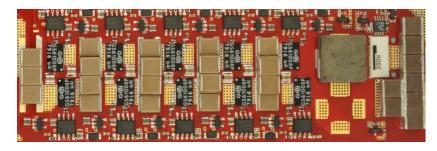

| 8.2        | A close-up photograph of the FCML buck stage of the hardware prototype. (Ac-                 |     |

|            | tual size.)                                                                                  | 92  |

| 8.3        | Top and side views of the hardware prototype.                                                | 94  |

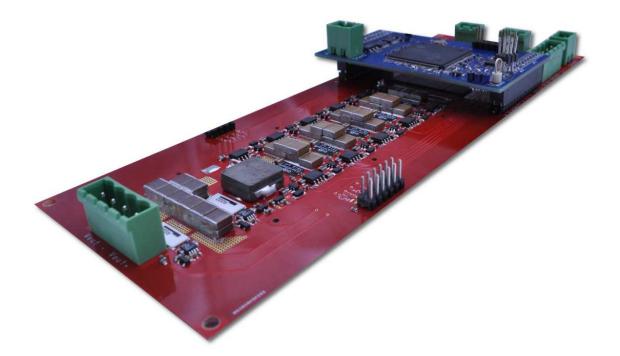

|            | I I I I I I I I I I I I I I I I I I I                                                        |     |

| 8.4         | Side view of the hardware prototype with attached heat sink                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.5         | Hardware prototype with attached microcontroller                                                                                                                                                                                           |

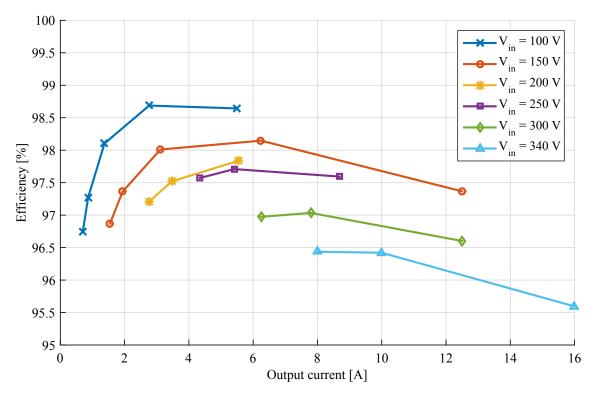

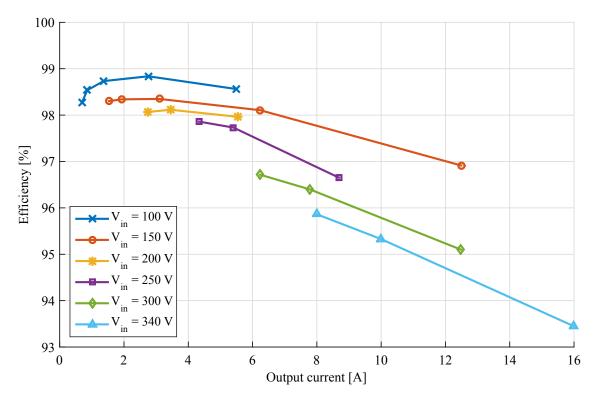

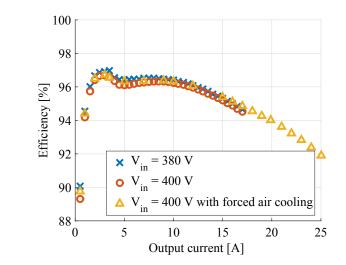

| 8.6         | Efficiency of the FCML buck converter in dc-dc operation                                                                                                                                                                                   |

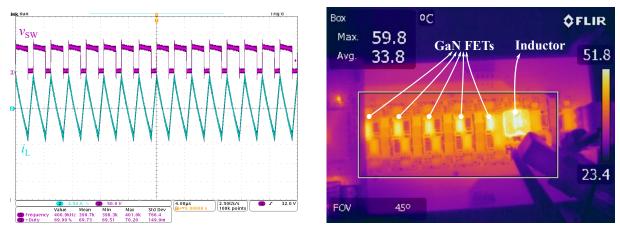

| 8.7         | Six-level FCML buck converter dc-dc operation at $V_{in} = 340$ V, $V_{out} = 48$ V and                                                                                                                                                    |

|             | $I_{out} = 16 \text{ A.} \dots \dots$                                                                                                |

| 8.8         | Input voltage and current, and inductor current, of the conventional (two-level)                                                                                                                                                           |

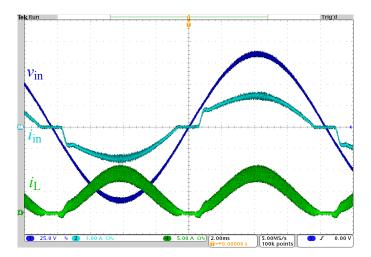

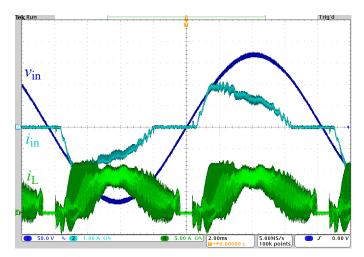

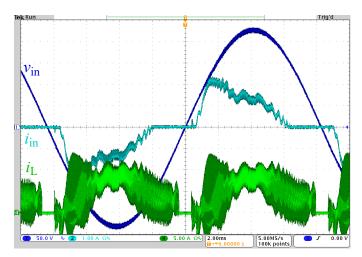

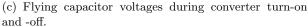

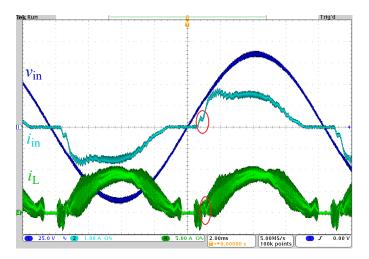

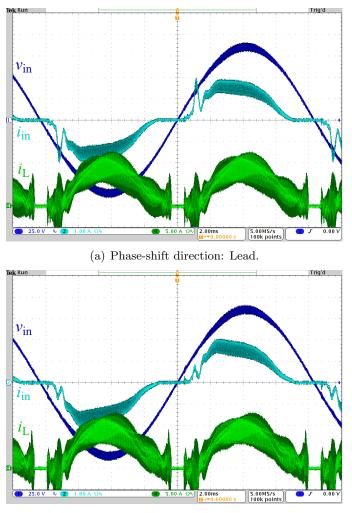

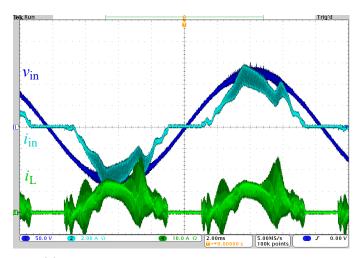

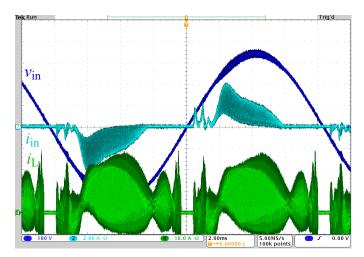

| 0.0         | buck converter for PFC operation. $V_{in} = 60 V_{RMS}$ , $V_{out} = 12 V$ and $I_{out,ave} = 4.5 A$ . 99                                                                                                                                  |

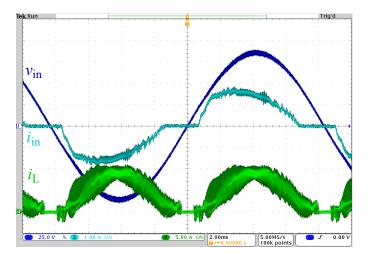

| 8.9         | Input voltage and current, and inductor current, of the six-level buck converter                                                                                                                                                           |

| 0.9         | for PFC operation. $V_{in} = 60 V_{RMS}$ , $V_{out} = 12 V$ and $I_{out,ave} = 4.5 A. \dots 99$                                                                                                                                            |

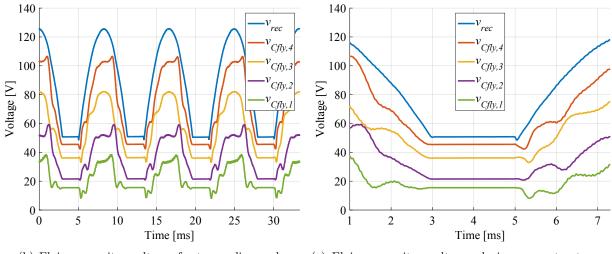

| <b>8</b> 10 |                                                                                                                                                                                                                                            |

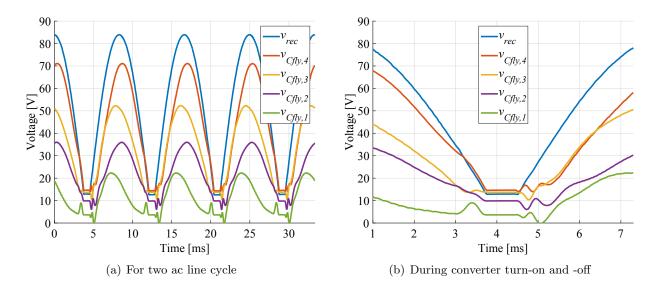

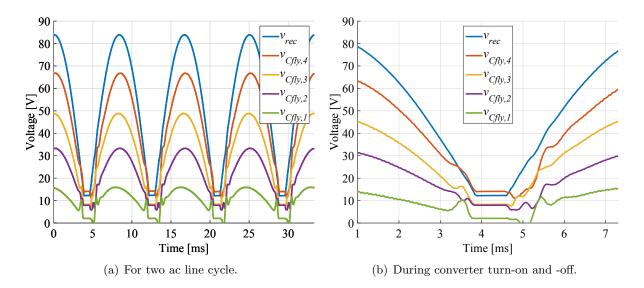

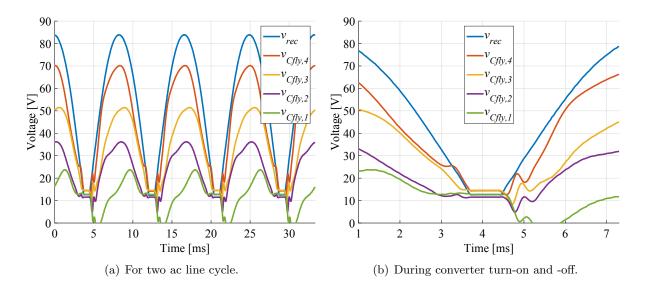

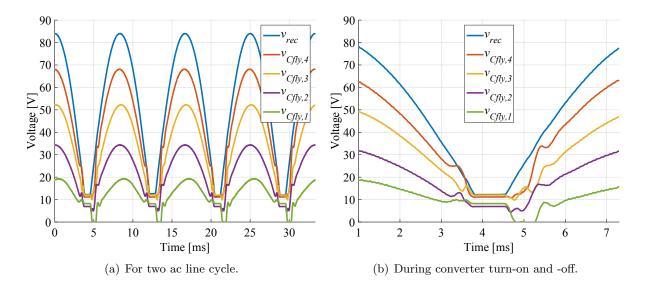

|             | Flying capacitor voltages at $V_{in} = 60$ V <sub>RMS</sub> , $V_{out} = 12$ V and $I_{out,ave} = 4.5$ A 100                                                                                                                               |

| 0.11        | Six-level buck converter for PFC operation at $V_{in} = 120 \text{ V}_{\text{RMS}}, V_{out} = 24 \text{ V}$ and                                                                                                                            |

| 0 10        | $I_{out,ave} = 4.5 \text{ A}. \dots \dots$                                                                                           |

| 8.12        | Six-level buck converter for PFC operation at $V_{in} = 160 \text{ V}_{\text{RMS}}, V_{out} = 32 \text{ V}$ and                                                                                                                            |

| 0.10        | $I_{out,ave} = 4.5 \text{ A.} \dots \dots$                                                                                           |

| 8.13        | Six-level buck converter for PFC operation at $V_{in} = 90 V_{RMS}$ , $V_{out} = 48 V$ and                                                                                                                                                 |

| ~           | $I_{out,ave} = 4.5 \text{ A.} \dots \dots$                                                                                           |

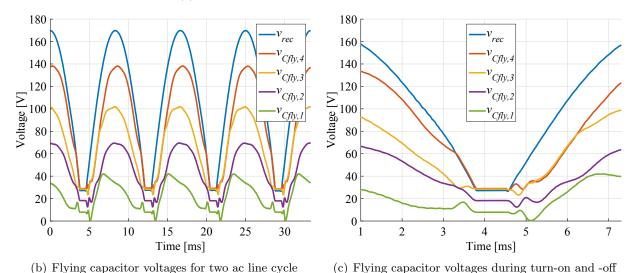

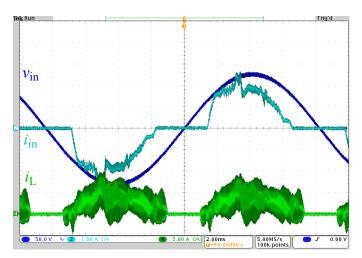

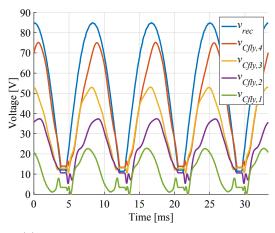

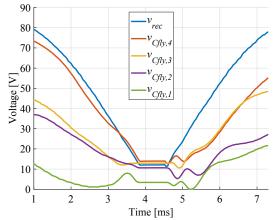

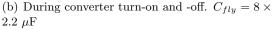

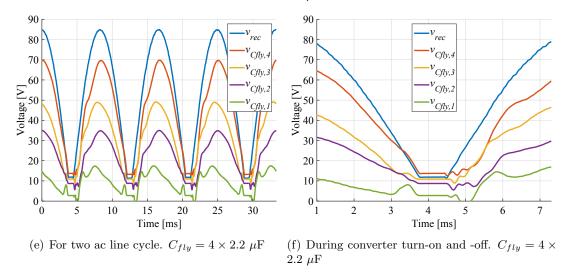

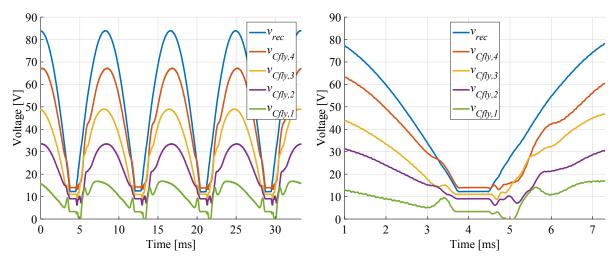

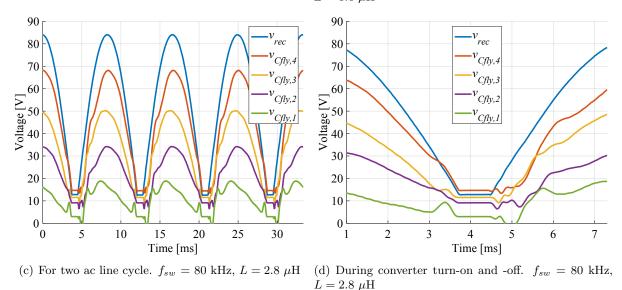

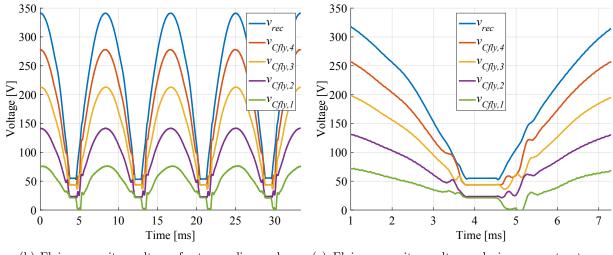

| 8.14        | Flying capacitor voltages of six-level buck converter in PFC operation for different                                                                                                                                                       |

|             | $C_{fly}$ values                                                                                                                                                                                                                           |

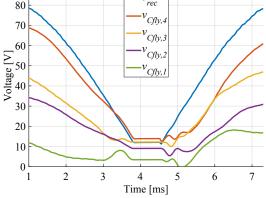

| 8.15        | Flying capacitor voltages of six-level buck converter in PFC operation for different                                                                                                                                                       |

|             | $f_{sw}$ and $L$ values. $C_{fly} = 6 \times 2.2 \ \mu\text{F.} \dots \dots$                                                         |

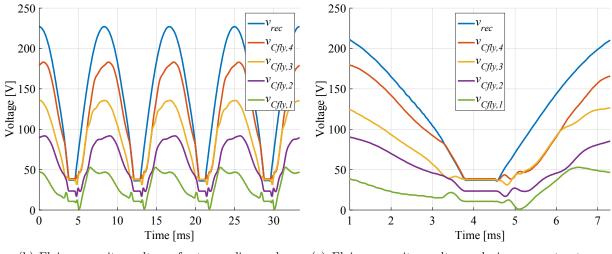

| 8.16        | Flying capacitor voltages of six-level buck converter in PFC operation. $C_{fly} =$                                                                                                                                                        |

|             | $6 \times 2.2 \ \mu\text{F}, L = 2.8 \ \mu\text{H}, f_{sw} = 40 \text{ kHz}.$                                                                                                                                                              |

| 8.17        | Flying capacitor voltages of six-level buck converter in PFC operation. $C_{fly} =$                                                                                                                                                        |

|             | $6 \times 2.2 \ \mu\text{F}, f_{sw} = 80 \text{ kHz}, \text{L} = 5.6 \ \mu\text{H}, \text{ phase-shift direction: Lag.} \dots \dots$ |

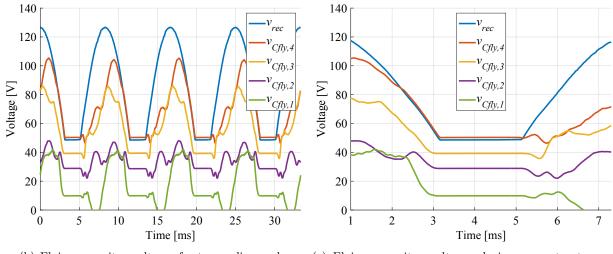

| 8.18        | Flying capacitor voltages of six-level buck converter in PFC operation. $C_{fly} =$                                                                                                                                                        |

|             | $6 \times 2.2 \ \mu\text{F}, f_{sw} = 40 \text{ kHz}, \text{L} = 2.8 \ \mu\text{H}, \text{ phase-shift direction: Lag.} \dots \dots$ |

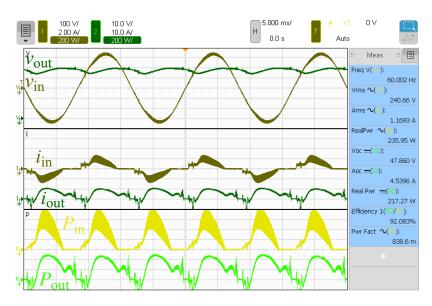

| 8.19        | The input and output voltage, current, and power of the six-level buck converter                                                                                                                                                           |

|             | for PFC operation. $C_{fly} = 6 \times 2.2 \ \mu\text{F}, f_{sw} = 80 \text{ kHz}, L = 5.6 \ \mu\text{H}, \text{ phase-shift}$                                                                                                             |

|             | direction: Lag. $\ldots$                                                                                                                                  |

| 8.20        | The input and output voltage, current, and power of the six-level buck converter                                                                                                                                                           |

|             | for PFC operation. $C_{fly} = 6 \times 2.2 \ \mu\text{F}, f_{sw} = 40 \text{ kHz}, \text{L} = 2.8 \ \mu\text{H}.$                                                                                                                          |

| 8.21        | Efficiency of the updated FCML buck converter in dc-dc operation                                                                                                                                                                           |

|             | Six-level buck converter for PFC operation at $V_{in} = 90 V_{RMS}, V_{out} = 48 V$ and                                                                                                                                                    |

|             | $I_{out,ave} = 4.5 \text{ A}. \dots \dots$                                                                                           |

| 8 23        | Six-level buck converter for PFC operation at $V_{in} = 240 \text{ V}_{\text{RMS}}$ , $V_{out} = 48 \text{ V}$ and                                                                                                                         |

| 0.20        | $I_{out,ave} = 4.5 \text{ A}. \dots \dots$                                                                                           |

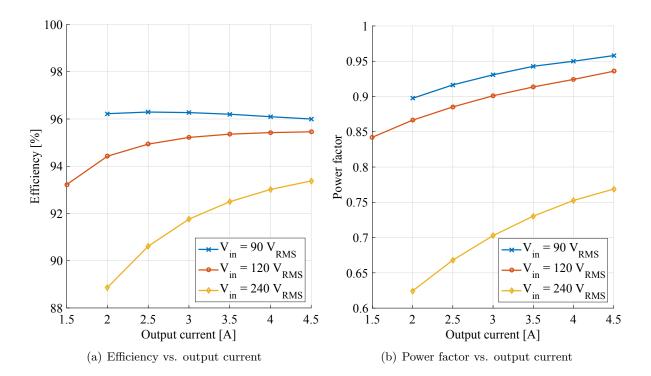

| 8 24        | AC to dc conversion efficiency and power factor at 90, 120 and 240 $V_{RMS}$ input                                                                                                                                                         |

| 0.24        | voltage. $\dots \dots \dots$                                                                                                               |

|             | Voltage                                                                                                                                                                                                                                    |

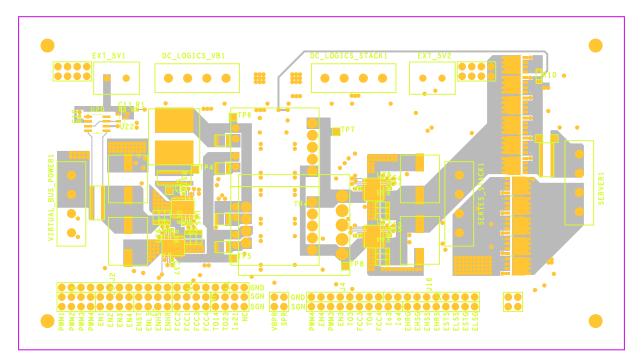

| A.1         | PCB layout of prototype DPP hardware: All layers, silkscreens and solder masks 122                                                                                                                                                         |

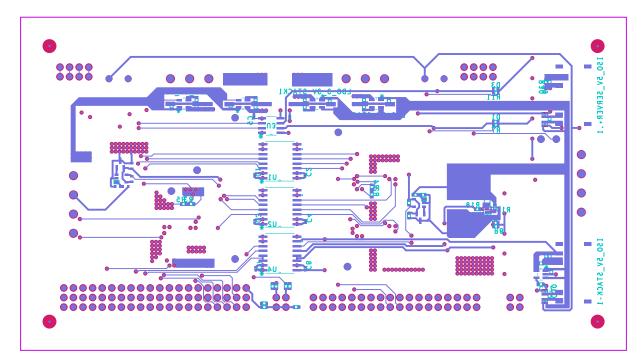

|             | PCB layout of prototype DPP hardware: Top layer, silkscreen and solder mask 123                                                                                                                                                            |

| A.3         | PCB layout of prototype DPP hardware: Bottom layer, silkscreen and solder mask. 123                                                                                                                                                        |

| A.4         | PCB layout of prototype DPP hardware: Ground layer                                                                                                                                                                                         |

| A.5         | PCB layout of prototype DPP hardware: Signal layer                                                                                                                                                                                         |

| 11.0        |                                                                                                                                                                                                                                            |

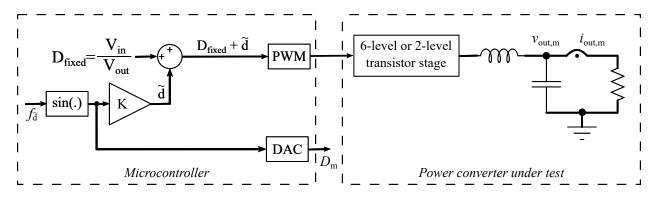

| C.1         | High-level diagram of the frequency response comparison experimental setup 160                                                                                                                                                             |

| C.2         | Control-to-output voltage frequency response of the six-level FCML and conven-                                                                                                                                                             |

|             | tional buck converter                                                                                                                                                                                                                      |

| C.3 | Control-to-output current frequency response of the six-level FCML buck converter. 163       |

|-----|----------------------------------------------------------------------------------------------|

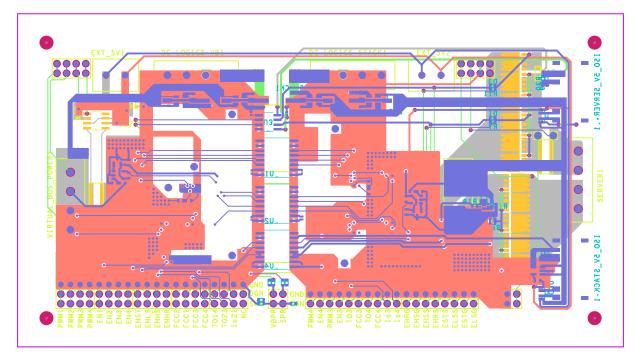

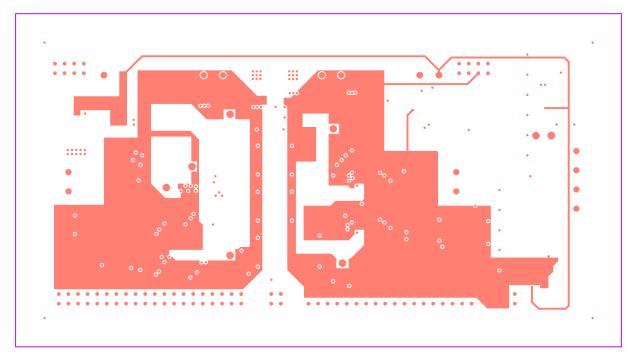

| D.1 | PCB layout of prototype FCML hardware: Top layer, silkscreen and solder mask.                |

|     | Not to scale due to page width                                                               |

| D.2 | PCB layout of prototype FCML hardware: Bottom layer, silkscreen and solder                   |

|     | mask. Not to scale due to page width                                                         |

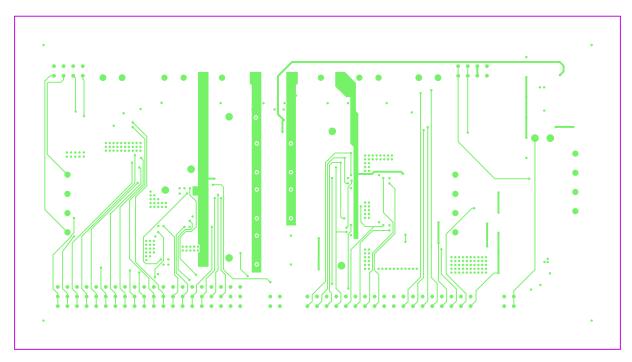

| D.3 | PCB layout of prototype FCML hardware: Second layer. Not to scale due to                     |

|     | page width                                                                                   |

| D.4 | PCB layout of prototype FCML hardware: Third layer. Not to scale due to page                 |

|     | width                                                                                        |

| F.1 | Six-level FCML buck converter dc-dc conversion efficiency at 400 V input voltage 185         |

|     | The input and output voltage, current, and power of the six-level buck converter             |

|     | in PFC operation at 240 $V_{\rm RMS}$ input voltage with 10 $\Omega$ series resistor between |

|     | the ac power supply and the converter                                                        |

|     | the de power suppry and the converter                                                        |

# CHAPTER 1 INTRODUCTION

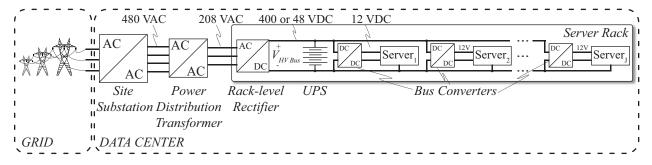

As high performance computing and data storage transition towards becoming Internet-based services, the world has witnessed an ever-increasing demand for both the size and capacity of data centers. The growth of cloud-based services and applications shows no sign of slowing down, with additional custom hardware for machine learning algorithms beginning to be deployed at scale in dedicated data centers. Today's data centers accommodate many pieces of information technology (IT) equipment such as data processing units, data storage units, and communication devices. The technological developments in the early 2000s led to a rapid expansion of data centers. As a result, data center energy consumption has increased greatly, which has been noted in several reports [1,2]. A 2016 report estimated the energy usage of data centers in the United States (US) alone at 70 billion kWh in 2014, corresponding to 1.8% of the total electric energy consumed in the country [3]. A 2018 survey noted that high density IT equipment started to require above 50 kW per rack, mainly driven by artificial intelligence algorithms and high performance computing applications [4]. Power electronics plays a critical role in achieving high power conversion efficiency and high power density in data centers. An in-depth review of power electronics, ranging from utility-scale to chip-level converters in data centers, can be found in [5].

Because IT equipment requires low dc voltage (typically ranging from a few volts to a few dozen volts) to operate, various power converters are needed in data centers to provide low dc voltage from utility and renewable resources. As data processing and cloud services continue to grow, any power conversion loss affects the operational cost of data centers both through the direct cost of electricity and the added cooling requirement. Improved conversion efficiency can be achieved, but this typically results in higher power converter volume, limiting power density in data centers. Alternative architectures that offer high efficiency and small overall volume for data center power delivery must be pursued for sustainable growth of this technology.

#### 1.1 Research contribution

Although a typical data center employs a vast amount of IT equipment, the power delivery architectures for data centers still treat each piece of equipment as a separate load and utilize power delivery methods which were initially intended for single computer applications. This dissertation seeks to demonstrate how architectural changes can increase power delivery efficiency and reduce the requisite converter footprint in data centers. The two crucial power conversion stages, the dc-dc bus converter and the single-phase ac-dc power factor correction converter, are bottlenecks for higher system-level efficiency and power density in data centers. This dissertation focuses on innovative approaches for these power conversion stages.

For the dc-dc bus conversion stage, a series-stacked architecture leveraging an inherently highefficiency power delivery architecture is proposed. In dc systems where multiple similar loads or sources are present, series stacking and differential power processing (DPP) offer improved overall efficiency [6]. The series-stacking and DPP part of this dissertation builds upon a master of science thesis [7], which was the first hardware demonstration of a server-to-virtual bus DPP architecture for 48 V to 12 V voltage conversion. The new work further shows practical implementation challenges such as hot-swapping and varying input voltage. These results are the first hardware demonstration of a series-stacked power delivery architecture where the IT equipment performs real-life data center operations.

For the single-phase ac-dc power factor correction (PFC) stage, a flying capacitor multilevel (FCML) buck converter leveraging an inherently high power density power conversion technique is proposed. The FCML buck converter offers high power density by employing capacitive elements, which inherently have up to 2-3 orders of magnitude higher energy density than inductors, in energy conversion [8]. Despite the notable power density that the FCML converter can offer, its usage in a buck PFC application presents an uncommon operation condition where the flying capacitors must drastically charge and discharge during each ac half-cycle. This dissertation also presents the first experimental study that explores the FCML buck converter in a single-phase ac-dc application.

#### 1.2 Organization of this dissertation

The remainder of this dissertation is organized as follows.

• Chapter 2 provides brief background on data center power delivery architectures and summa-

rizes conventional ac and dc configurations. Key considerations in data center power delivery such as efficiency, reliability, and backup power are explained in this chapter.

- In Chapter 3, background on series-stacked power delivery architectures is provided. The crucial practical considerations in data centers, initialization and hot-swapping of servers, are addressed conceptually using case studies. Mathematical expressions for processed and delivered power in the proposed virtual bus architecture are derived.

- Chapter 4 explains the bidirectional hysteresis control algorithm, which is a key enabler to achieve high efficiency power delivery in the proposed series-stacked power delivery architecture.

- Experimental results that validate the feasibility of the proposed series-stacked power delivery architecture for data center applications are reported in Chapter 5. Also, a prototype DPP hardware design which combines a differential converter and associated hot-swapping and initialization circuits on a single board is explained in this chapter.

- Chapter 6 provides background information on single-phase ac-dc power conversion, specifically focusing on buck-type PFC conversion. The advantages and challenges of the FCML buck converter in PFC operation are presented here.

- The proposed digital PFC control algorithm is explained in Chapter 7.

- In Chapter 8, an experimental study that explores the FCML buck converter in single-phase ac-dc conversion is reported. A thorough investigation of flying capacitor voltage balancing in FCML buck converters for PFC operation is provided here.

- Chapter 9 concludes the dissertation and suggests future research directions.

The material in this dissertation has been published in part in [9–13], and is reused here with permission.

## CHAPTER 2

## BACKGROUND ON DATA CENTER POWER DELIVERY

This chapter addresses major aspects of power delivery architectures in data centers including but not limited to efficiency, power density, reliability, integration with renewable resources, and protection.

#### 2.1 Common power delivery architectures in data centers

In data centers, since the major energy supply is the ac utility and the primary power consumers (i.e., information technology (IT) equipment) require low voltage dc, both ac and dc power infrastructures are concurrent. As power is delivered from the utility to low voltage dc loads, rectification (power conversion from ac to dc form) can be performed at various points, resulting in different power architecture configurations [14].

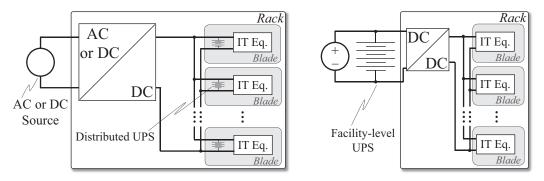

Conventionally, utility power is distributed in ac form inside a data center, and then, rectification and voltage step-down conversion are performed at the load end of the power architecture by a dedicated power supply unit (PSU) for each piece of IT equipment. Conversely, utility power can be rectified at the source end of the power architecture (i.e., data center input), and distributed in high dc voltage form within the data center. Then, a dedicated dc-dc converter per IT device steps down the high dc voltage. Alternatively, ac power can be distributed to racks that host the IT equipment, and rectifiers that are in the same rack (or in another rack that is in close proximity) provide dc power to the IT equipment. Simplified diagrams of these common data center power distribution architectures are depicted in Figure 2.1.

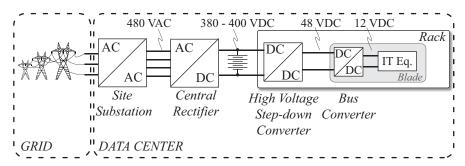

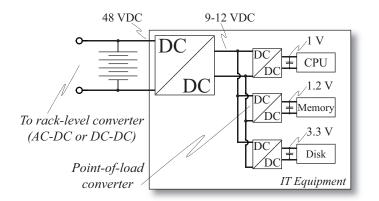

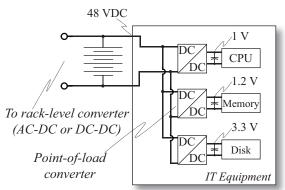

Modern IT equipment employs many dc-dc converters (i.e., point-of-load (POL) converters) in order to step down its input voltage for even lower voltage data processing and storage loads, where the power is eventually needed. For example, Figure 2.2 show key elements of IT equipment that includes a central processing unit (CPU), hard drive, and memory. Since each element requires a different dc voltage, the POL converters step down the IT equipment's input voltage to various

(a) AC power distribution in data centers. A single ac-dc converter provides rectification, voltage step-down and isolation for each piece of IT equipment.

(b) DC power distribution in data center. A central rectifying stage at the data center input provides a high dc voltage which is distributed to the racks. Then, dc-dc converters step down the high dc voltage and provide isolation for each piece of IT equipment.

a few racks. The ac power is delivered to the racks. Then, a rack-level rectification stage provides an intermediate high dc voltage to the rack. Separate dc-dc converters perform final voltage step-down and provide isolation at the IT equipment input.

Figure 2.1: Simplified drawings of common power delivery architectures in data centers. For prioritizing transition from ac to dc power distribution, protection equipment and cooling devices are not depicted in these figures, but of course exist in practical designs and may introduce additional power conversion stages.

lower well-regulated voltage levels. The POL converters may require a lower intermediate bus voltage (9-12 V) as shown in Figure 2.2(a), or they may directly interface the IT equipment input voltage as in Figure 2.2(b). Since the final voltage regulation for the key elements inside the IT equipment is governed by POL converters, conventional power delivery architectures sometimes

(a) 48 V to intermediate bus to POL architecture. A dc-dc converter at the IT equipment input creates an intermediate bus and provides isolation. Then, POL converters step down the intermediate bus voltage to a few volts to provide the ultimate low voltage for the data processing and storage units.

(b) 48 V-to-POL architecture. POL converters step down the IT equipment input voltage directly to a few volts to provide the ultimate low voltage for the data processing and storage units.

Figure 2.2: Simplified drawings of common point-of-load (POL) converter configurations in IT equipment motherboards. POL converters perform the final voltage step-down conversion in the power delivery architecture.

sacrifice precise voltage regulation at the IT equipment input or at the dc bus [15]. This may also enable efficient uninterruptible power supply (UPS) integration in the system, since the voltage typically varies when it is supplied by a UPS, especially during utility-level power loss.

Because of the extensive background, acceptability and well-established standardization of ac distribution in many other applications, a high percentage of existing data centers use variations of the power delivery architectures depicted in Figure 2.1(a) or 2.1(c), which are fundamentally inherited from telecom applications. Recently, dc power delivery architectures, as depicted in Figure 2.1(b), have gained attention, mainly because they involve fewer conversion stages and

could potentially simplify the integration of ancillary distributed energy resources, such as solar PV and fuel cells. A well-cited 2008 report has underlined the benefits of high voltage dc power distribution in data centers [16], although the idea of using a voltage level higher than 48 V for data center power distribution appears in the literature as early as 1999 [17]. Over the years the literature has addressed various high dc voltage levels such as 270 V [17], 300 V [18], 325 V [19], 380 V [20,21], and 400 V [20,22]; however, the consensus for high voltage dc distribution in data centers eventually appears to have become nominal 400 V. The protracted discussion on voltage levels over 15 years, combined with relatively slow development of standards for IT equipment and power distribution such as ETSI EN 300 132-3-1 [23] for 400 V dc bus voltage, ETSI EN 301 605 [24] for grounding, and IEC 61643-21 [25] for protection, arguably have discouraged short-term adoption of dc distribution in data centers.

Following the potential of dc distribution for data centers noted in [16], ac and dc power distribution architectures for data centers have been both quantitatively and qualitatively compared by both academia and industry [26–30]. In addition, [31] has reviewed some highly cited comparison reports and notes that results vary widely and overstate the benefits of dc power architectures. In order to fairly evaluate comparison studies, it should be noted that over the years significant barriers such as lack of standardization, market share, and compatibility with IT equipment have prevented the widespread adoption of high voltage dc in data centers, while already well-established ac distribution architectures have kept developing to meet expectations.

#### 2.2 Efficiency

In recent years, electricity has become the largest operating cost of data centers; thus, maintaining high power conversion efficiency has become critical. As shown in Figure 2.1, regardless of the preferred distribution architecture, utility power must go through several cascaded power conversion stages before it reaches IT equipment. Since power consumed by IT equipment must be processed by each power converter, the overall power infrastructure efficiency is the product of the efficiency of all power converters, and thus mainly limited by the least efficient power converter. Power delivery studies therefore must consider the entire power conversion stage, from high voltage ac input to the building, all the way down to processor and memory voltages, around 1 V.

Recent literature has focused on efficiency improvements of each major power electronics converter type for data center applications. Development and commercial availability of wide band gap devices have been leveraged in converter designs. Consequently, high power density designs have achieved high-90% efficiencies in three phase [32,33] and single-phase rectifiers [34–36], mid-90% efficiencies in 400 V to 12 V [37–39] or to 48 V [40] dc to dc converters, and mid/high-90% efficiencies in both silicon based [41] and GaN based [42–44] 48 V to 12 V bus converters, and 48 V [45–48] or 12 V [49–53] POL converters for data center applications. Since actual power conversion efficiency in a power converter changes depending on the output power, estimating overall power conversion efficiency of cascaded converters between grid and load is not trivial. A survey of prominent peak and full load efficiency values in [32–53] demonstrates a "best-case" combined efficiency between 93% (if the converters ideally operate at their peak efficiency point) and 86% (if the converters operate at full load) from the ac grid to low voltage dc loads.

One key approach to increasing system-level conversion efficiency is to eliminate – to the greatest extent possible – any double conversion, where voltage is stepped up and down or power is converted from ac to dc or dc to ac more times than the absolute minimum. An example of such a double conversion is the back-to-back ac-dc and dc-ac conversion of the centralized UPS approach shown in Figure 2.1(a), which is one reason why it is no longer a preferred approach. Below are some opportunities to reduce the number of power stages.

- A facility-level battery system for power backup in a high voltage dc power distribution architecture as shown in Figure 2.1(b) does not require an inverter stage while providing backup power to both the IT equipment and auxiliary loads such as lighting and cooling. Since electrochemical energy storage is inherently in dc form, a battery bank for a utility outage or failure scenario can be connected to the high voltage dc bus. Of course, additional circuitry may be needed to connect battery banks to the high voltage dc bus for regulatory or other operating reasons; however, such circuitry does not process the requisite power similar to an inverter that outputs a tightly regulated ac waveform and synchronizes with multiple converters across the bus.

- Twice-line frequency energy buffering is a well-known issue in single-phase rectifiers [54]. The recent Google Little Box Challenge [55] has accelerated research efforts in the area of twice-line frequency energy buffering, and as a result extremely high efficiencies for twice-line frequency energy buffering have been reported in the literature [56]. Nevertheless, moving from single-phase rectification at the IT equipment input to centralized three phase rectification at the high voltage dc bus eliminates the need for twice-line frequency energy buffering and the

associated circuitry from the cascaded power chain. Similar benefits can be realized if threephase rectifiers are employed in an ac distribution approach, generally at the rack level (i.e., rack-level three-phase rectifiers).

• Similar to twice-line frequency energy buffering, active power factor correction (PFC) circuitry is an essential requirement in both single and multiphase high power rectifiers. The most common single-phase PFC architecture is the boost-type converter, meaning the output of the PFC circuit is at a higher voltage than its input. Since IT equipment requires low voltage dc, employing PFC closer to the low voltage load requires a back-end, high conversion ratio, voltage step-down converter. Although a centralized three phase rectification does not eliminate PFC circuitry, it can remove a cascaded voltage step up and down conversion at the IT equipment input, which is potentially counterproductive since the load is at low dc voltage. Here, recent developments in step-down (e.g., buck-derived) PFC rectifiers [32, 57] show promise to achieve increased system-level efficiencies.

At a high level, it may appear that simply reducing the number of conversion stages would increase efficiency. However, one must be careful to consider that for a given power converter volume, a high-step-down power converter generally has lower efficiency than a converter with a modest voltage step-down ratio. This is particularly telling in the case of the 48 V to point-of-load concept, where the conventional architecture shown in Figure 2.2(a) involves first 48 V to 9-12 V conversion, followed by (typically several) 9-12 V to point-of-load (e.g., 1-2 V) converters. While it may be tempting to simply eliminate the two-stage conversion and design a single 48 V to 1 V converter as shown in Figure 2.2(b), such a converter is significantly more difficult to design to be highly efficient and power dense [45–48]. For example, consider the reference design of [58], which represents a single-stage buck converter, achieving a peak efficiency of 84%. Other more complex topologies likewise achieve limited performance in both efficiency and power density. In comparison, recent hybrid switched-capacitor power converters have been shown to achieve near 99% efficiency with extraordinarily high power density (106.5 kW/L) for 48 V to 12 V conversion [41], and separate 12 V to 1 V converter can similarly achieve high overall efficiency and power density [49, 51-53]. While there may be other considerations (such as reliability, cost, reduced complexity, etc.) to prefer fewer numbers of stages, the above discussion highlights that increased efficiency is not necessarily an outcome of this approach.

#### 2.3 Reliability

Maintaining high reliability in data centers is crucial because of our society's dependence on uninterrupted IT services. Today, any outage of IT services can have a large impact, both financial and in terms of societal impact. A typical target reliability for a data center is 99.99% uptime (often called "four nines"), which corresponds to 52.5 minutes downtime per year [59]. This requirement, combined with maintaining high efficiency, makes data center power delivery architecture design challenging. Fortunately, similar to improving the power delivery architecture efficiency, reducing the number of cascaded power stages typically reduces the overall risk of system failure and the mean time between failures. Therefore, opportunities to reduce the number of power conversion stages in dc data centers facilitates higher reliability and uptime. Elimination of conversion stages such as power distribution transformers and the inverter at the UPS output in high voltage dc distribution is considered a major advantage for dc data centers [22, 60, 61]. However, the analysis in these past works is qualitative and the details are unclear. A 2010 study quantitatively compared the reliability of ac and dc power distribution for data centers with emphasis on UPS, and concluded that dc distribution would be more reliable than ac distribution without supplementary effects of redundancy [27]. A more recent quantitative reliability analysis for data centers considering UPS, power converter failure mechanisms, and redundancy options is missing in the literature. Nevertheless, reducing the number of conversion stages alone is not sufficient to assure reliable power distribution; backup power and redundancy must be incorporated in data center power architecture design to achieve the desired reliability level.

#### 2.4 Backup power

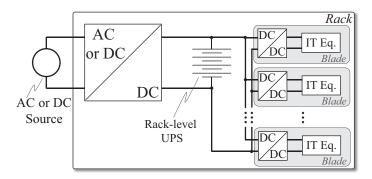

Utility power loss is an expected scenario in data centers instead of a failure. Data centers employ uninterrupted power supplies (UPS), backup generators, and recently fuel-cells at specific points in the power delivery architecture to be able to compensate for both utility loss and power stage failure. Various possible configurations preferred in recently developed data center power delivery architectures are depicted in Figure 2.3.

In case of utility loss, the facility level UPS must be able to provide enough backup power to critical loads until backup generators can initialize and output sufficient energy to the facility. On the other hand, UPS placement close to the load (IT equipment) can compensate for any component

(a) Rack-level UPS. UPS is located inside the racks and provides backup power for multiple pieces of IT equipment.

(b) Distributed UPS. Each piece of IT equipment has a dedicated UPS. This configuration offers uninterruptible power in case of any converter failure.

(c) Facility-level UPS. UPS is located outside of the rack and provides backup power for multiple racks.

Figure 2.3: Various UPS configurations for data centers.

failure between the utility and the IT equipment. Uptime Tier Certification requires data centers to have on-site fuel storage for at least 12 hours of utility loss [62].

Recent data center power delivery designs are moving away from central UPS double-conversion towards rack-level UPS single-conversion in ac distribution architectures (e.g., Figure 2.1(c)). While there are some benefits in terms of maintenance and costs associated with a central UPS system, rack-level UPS can also help mitigate power distribution faults in data centers, as each rack can operate directly from its own UPS.

#### 2.5 Redundancy

Redundancy is typically achieved through the incorporation of additional and separate power conversion stages, UPS, and power distribution paths in data center power infrastructure. Redundant components may be operated at all times (e.g., each running at partial load to increase peak ef-

Table 2.1: Tier certificate requirements summary

|                   | Tier I | Tier II | Tier III              | Tier IV             |

|-------------------|--------|---------|-----------------------|---------------------|

| Redundancy level  | Ν      | N+1     | N+1                   | N After any failure |

| Distribution path | 1      | 1       | 1 active, 1 alternate | 2 active            |

ficiency) but, strictly speaking, are only needed to meet the power demand of the load in case of failures. Typical redundancy levels for data centers are N+1, 2N and 2N+1, where N represents the number of power converters or UPS systems in parallel to meet the load demand. The Uptime Institute defines Tier Classification levels for data centers depending on the redundancy level of the data center [62]. Tier I represents basic data center infrastructure without any redundancy. Tier II certification requires redundant power stages and UPS; however, the power distribution path is not redundant. Tier III certification requires the data center to have both redundant power stages and multiple independent power distribution paths, although only one distribution path is actively used at any time, while the other is for maintenance purposes. Tier IV certification requires redundant power stages and multiple active power distribution paths configured to serve the entire data center under any infrastructure failure. Tier Certificate requirements are summarized in Table 2.1 and details can be found in [62].

#### 2.6 Isolation and grounding