# Design of High-Speed SerDes Transceiver for Chip-to-Chip Communications in CMOS Process

Xuqiang Zheng Supervisor: Professor Shigang Yue

#### School of Computer Science University of Lincoln

A thesis submitted in partial fulfilment of the requirements of the University of Lincoln for the degree of Doctor of Philosophy

#### **Abstract**

With the continuous increase of on-chip computation capacities and exponential growth of data-intensive applications, the high-speed data transmission through serial links has become the backbone for modern communication systems. To satisfy the massive data-exchanging requirement, the data rate of such serial links has been updated from several Gb/s to tens of Gb/s. Currently, the commercial standards such as Ethernet 400GbE, InfiniBand high data rate (HDR), and common electrical interface (CEI)-56G has been developing towards 40+ Gb/s. As the core component within these links, the transceiver chipset plays a fundamental role in balancing the operation speed, power consumption, area occupation, and operation range. Meanwhile, the CMOS process has become the dominant technology in modern transceiver chip fabrications due to its large-scale digital integration capability and aggressive pricing advantage. This research aims to explore advanced techniques that are capable of exploiting the maximum operation speed of the CMOS process, and hence provides potential solutions for 40+ Gb/s CMOS transceiver designs. The major contributions are summarized as follows.

A low jitter ring-oscillator-based injection-locked clock multiplier (RILCM) with a hybrid frequency tracking loop that consists of a traditional phase-locked loop (PLL), a timing-adjusted loop, and a loop selection state-machine is implemented in 65-nm C-MOS process. In the ring voltage-controlled oscillator, a full-swing pseudo-differential delay cell is proposed to lower the device noise to phase noise conversion. To obtain high operation speed and high detection accuracy, a compact timing-adjusted phase detector tightly combined with a well-matched charge pump is designed. Meanwhile, a lock-loss detection and lock recovery is devised to endow the RILCM with a similar lock-acquisition ability as conventional PLL, thus excluding the initial frequency set-

up aid and preventing the potential lock-loss risk. The experimental results show that the figure-of-merit of the designed RILCM reaches -247.3 dB, which is better than previous RILCMs and even comparable to the large-area LC-ILCMs.

The transmitter (TX) and receiver (RX) chips are separately designed and fabricated in 65-nm CMOS process. The transmitter chip employs a quarter-rate multimultiplexer (MUX)-based 4-tap feed-forward equalizer (FFE) to pre-distort the output. To increase the maximum operating speed, a bandwidth-enhanced 4:1 MUX with the capability of eliminating charge-sharing effect is proposed. To produce the quarter-rate parallel data streams with appropriate delays, a compact latch array associated with an interleaved-retiming technique is designed. The receiver chip employs a two-stage continuous-time linear equalizer (CTLE) as the analog front-end and integrates an improved clock data recovery to extract the sampling clocks and retime the incoming data. To automatically balance the jitter tracking and jitter suppression, passive lowpass filters with adaptively-adjusted bandwidth are introduced into the data-sampling path. To optimize the linearity of the phase interpolation, a time-averaging-based compensating phase interpolator is proposed. For equalization, a combined TX-FFE and RX-CTLE is applied to compensate for the channel loss, where a low-cost edge-data correlation-based sign zero-forcing adaptation algorithm is proposed to automatically adjust the TX-FFE's tap weights. Measurement results show that the fabricated transmitter/receiver chipset can deliver 40 Gb/s random data at a bit error rate of  $< 10^{-12}$ over a channel with >16 dB loss at the half-baud frequency, while consuming a total power of 370 mW.

## **Declaration**

I, Xuqiang Zheng, declare that this thesis describes an original study carried out on my own. It has not been previously submitted to any university for the award of any degree. Where I have quoted from the work of others, the source is always given.

## Acknowledgements

First and foremost, I would like to thank my academic advisor, Professor Shigang Yue, for his tolerance and patience in letting me explore my interested fields. He encouraged me to think deeply and creatively. He also taught me how to effectively communicate my research in papers and presentations. I hope through the years I have been able to pick up a little of his ability to find and explain ideas and concepts with such clarity. He will always be a role model to me in my future academic career.

Professor Chun Zhang is my co-advisor, and I am grateful to him for his help and support when I was on secondment to Tsinghua University. I especially value his trust in giving me plenty of tapeout chances, regardless of consequences for him. I have learned a lot from him on how to communicate with people and how to address troublesome issues. I also want to thank my second co-advisor, Dr. Tryphon Lambrou, for his nice advice and kind discussions.

I would like to take this chance to thank my family for their selfless love and constant support. Especially, my parents-in-law who gave me great support on deciding to start my Ph.D. study and provided me generous help during my study. I am grateful to my wife who supported the whole home when I was studying abroad. I also want to say sorry to my son for the absence during my abroad study.

The environment at the University of Lincoln is full of brilliant and enthusiastic colleagues who have provided me valuable help and discussions. I wish to thank the previous and present members in Lincoln Centre for Autonomous Systems (L-CAS) research group who have brought me great convenience in daily life and academic research. In particularly, I want to thank Farshad Arvin, Yi Gao, Junxiong Jia, Feng

Zhao, Tuo Xie, Mingzhu Long, Yan Yan, Guopeng Zhang, Cheng Hu, Qinbing Fu, Jingmin Huang, Biao Zhao, Xuelong Sun, Jiannan Zhao, Huatian Wang, and Tian Liu for their selfless help and creative discussions.

I wish to thank Dr. Fangxu Lv for joint work on parts of the project for always being ready to carry out necessary chip measurements. I also would like to thank Prof. Fule Li for his constructive advice on circuit designs. I thank him most for being patient with me at the very beginning and using his vision to open the door of the integrated circuit design to me.

Finally, I appreciate the financial support from School of Computer Science at University of Lincoln, the EU FP7 projects: EYE2E (269118), LIVCODE (295151), and EU Horizon 2020 project: STEP2DYNA (691154).

#### **List of Main Publications**

- [1] **X. Zheng**, C. Zhang, and F. Lv *et al.*, "A 40-Gb/s quarter-rate SerDes transmitter and receiver chipset in 65-nm cmos," *IEEE J. Solid-State Circuits* (*JSSC*), vol. 52, no. 11, pp. 2963–2978, Nov. 2017.

- [2] **X. Zheng**, Z. Wang, and F. Li *et al.*, "A 14-bit 250 MS/s IF sampling pipelined ADC in 180 nm CMOS process," *IEEE Trans. Circuits Syst. I, Reg. Papers* (*TCAS-I*), vol. 63, no. 9, pp. 1381–1392, Sep. 2016.

- [3] **X. Zheng**, F. Lv, and F. Zhao *et al.*, "A 10 GHz 56 fsrms-integrated-jitter and -247 dB FOM ring-VCO based injection-locked clock multiplier with a continuous frequency-tracking loop in 65 nm CMOS," in *Proc. IEEE Custom Integrated Circuits Conf. (CICC)*, Jul. 2017, pp. 1–4.

- [4] **X. Zheng**, C. Zhang, and S. Yuan *et al.*, "An improved 40 Gb/s CDR with jitter-suppression filters and phase-compensating interpolators," in *Proc. IEEE Asian Solid-State Circuits Conf.* (ASSCC), Nov. 2016, pp. 85–88.

- [5] **X. Zheng**, C. Zhang, and F. Lv *et al.*, "A 5-50 Gb/s quarter rate transmitter with a 4-tap multiple-MUX based FFE in 65 nm CMOS," in *Proc. IEEE European Solid-State Circuits Conf.* (*ESSCIRC*), Sep. 2016, pp. 305–308.

- [6] W. Cao, **X. Zheng**, Z. Wang, and D. Li *et al.*, "A 15Gb/s wireline repeater in 65nm CMOS technology," in *Proc. IEEE International Conference on Electron Devices and Solid-State Circuits* (*EDSSC*), Oct. 2015, pp. 590–593.

## **List of Figures**

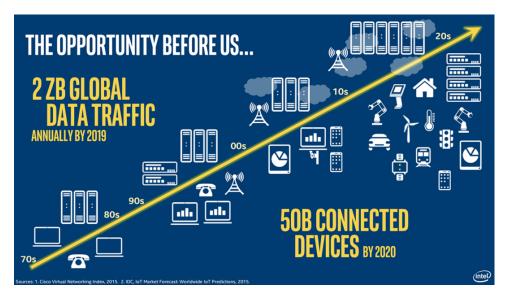

| 1.1  | Diagram of the global data traffic trend [1]. By 2020, 50 billion devices will be connected generating more than two zetta bytes of data traffic |            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | annually.                                                                                                                                        | 2          |

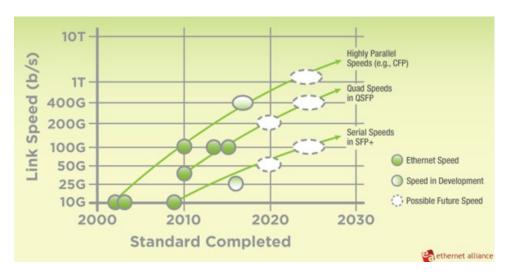

| 1.2  | Wired network roadmap [2]. The data rates in SFP+, QSFP, and CFP are updating towards 100Gb/s, 400Gb/s, and 1Tb/s, respectively.                 | 3          |

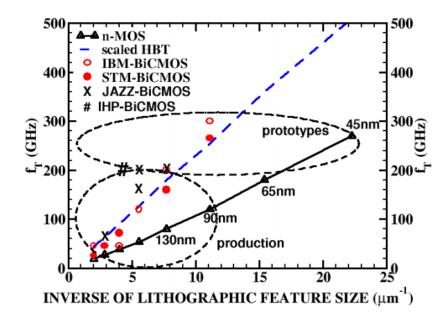

| 2.1  | Cutoff frequency $(f_T)$ scaling comparison among different processes in terms of the inverse of the lithographic feature size [3].              | 11         |

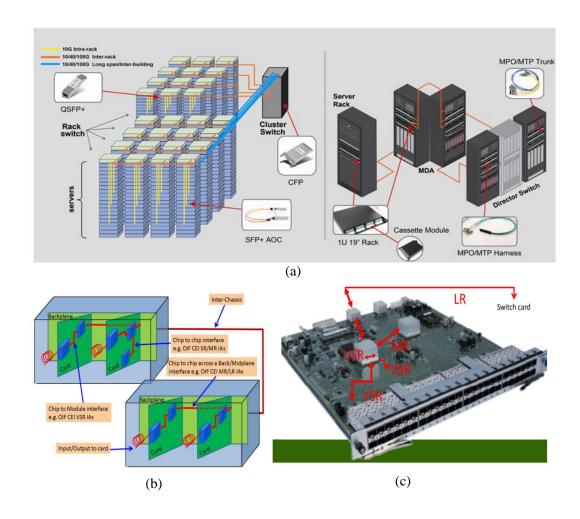

| 2.2  | Typical SerDes application spaces. (a) rack-to-rack link, (b) chassis-                                                                           | 13         |

| 2.3  | to-chassis connection, and (c) intra-chassis interconnect [4].                                                                                   | 13         |

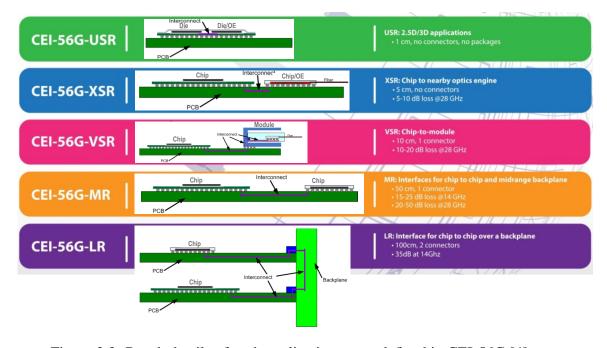

|      | Reach details of each application space defined in CEI-56G [4].                                                                                  | 18         |

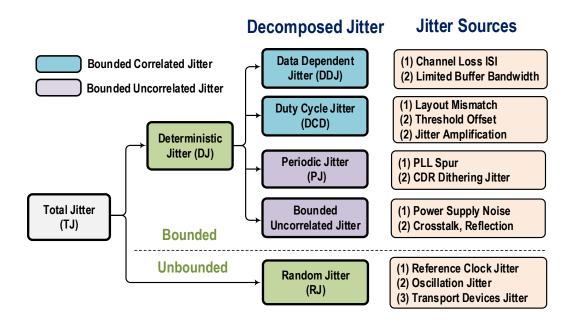

| 2.4  | Jitter decomposition and jitter sources.                                                                                                         | 10         |

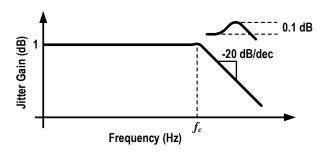

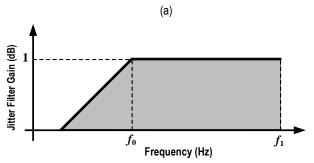

| 2.5  | CDR specifications of (a) JTRAN, (b) JGEN, and (c) JTOL in SONET                                                                                 | 20         |

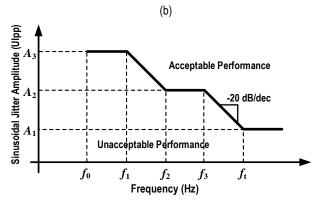

| 2.6  | [5]. Typical serial link for wireline communications.                                                                                            | 22         |

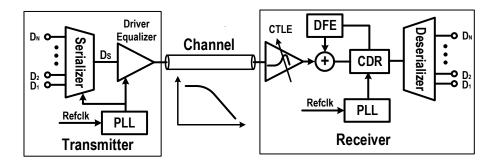

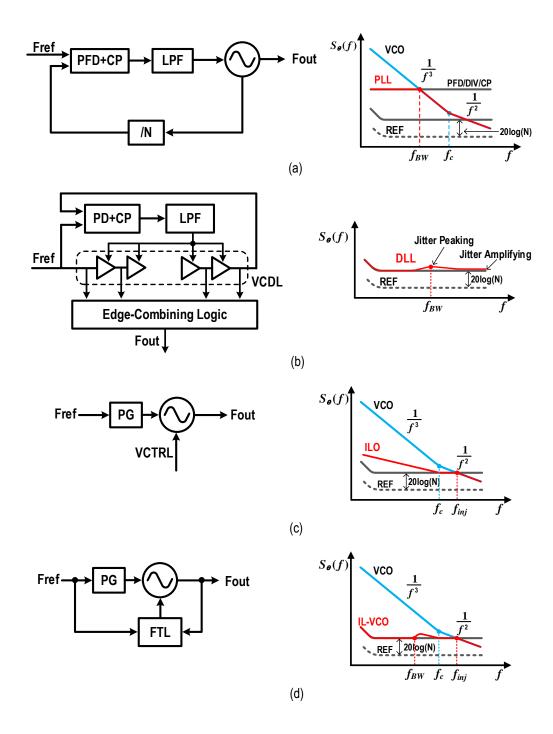

| 2.7  | Clock synthesis implementations and phase noise performances for (a)                                                                             | 44         |

| 2.1  | PLL, (b) DLL, (c) ILO, and (d) IL-VCO. Here, f is the frequency of                                                                               |            |

|      | the noise, $S_{\theta}(f)$ stands for the phase noise spectrum, $f_{BW}$ refers to                                                               |            |

|      | the -3dB bandwidth of the loop, $f_c$ denotes the corner frequency of the                                                                        |            |

|      | VCO, and $f_{inj}$ represents the injection-locking bandwidth of the ILO.                                                                        | 24         |

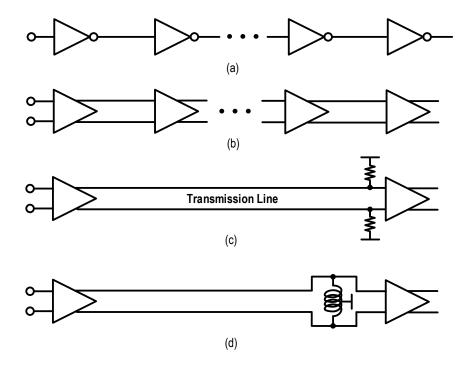

| 2.8  | Clock distribution structures based on (a) inverter chain, (b) CML chain,                                                                        | <b>4</b> - |

| 2.0  | (c) transmission line, and (d) inductive load.                                                                                                   | 28         |

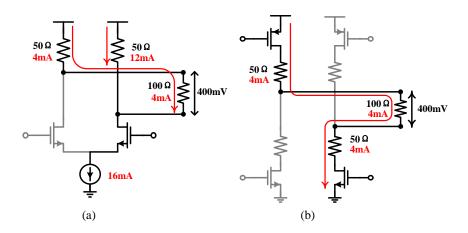

| 2.9  | Typical transmitter driver modes. (a) CML mode and (b) SST mode.                                                                                 | 31         |

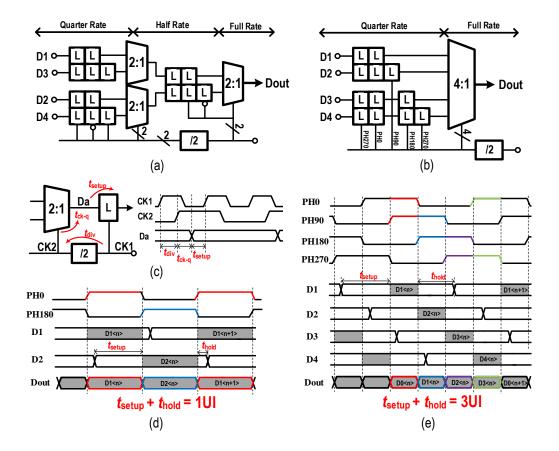

|      | Schemes of the final 4:1 multiplexing. (a) Half-rate topology based                                                                              | <i>J</i> 1 |

|      | on two-stage 2:1 MUXs, (b) quarter-rate structure based on direct 4:1                                                                            |            |

|      | MUX, (c) critical path and timing diagram of the 2:1 MUX, (d) timing                                                                             |            |

|      | margin of the 2:1 MUX, and (e) timing margin of the 4:1 MUX.                                                                                     | 32         |

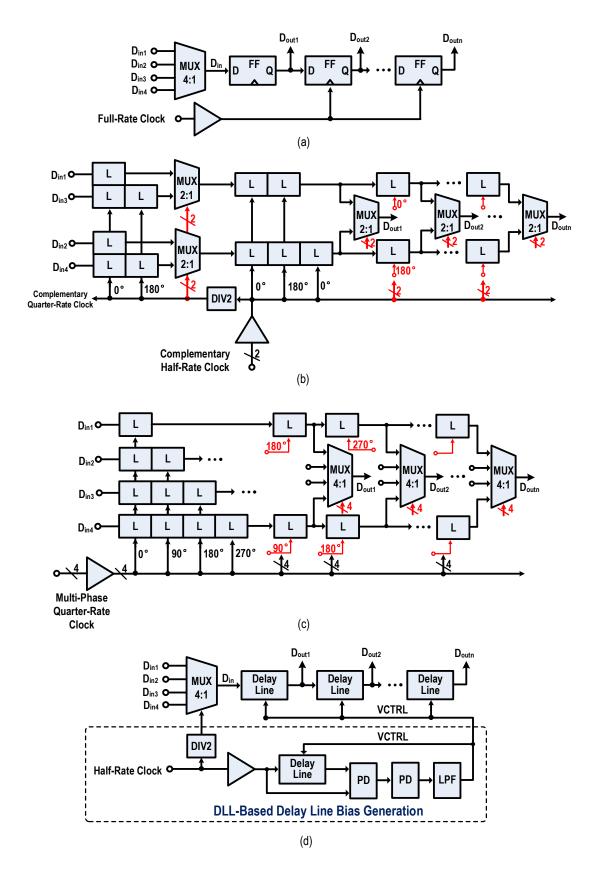

| 2.11 | Techniques of 1-UI delay generation based on (a) full-rate FF, (b) half-                                                                         |            |

|      | rate 2:1 MUX, (c) quarter rate 4:1 MUX, and (d) analog delay line.                                                                               | 34         |

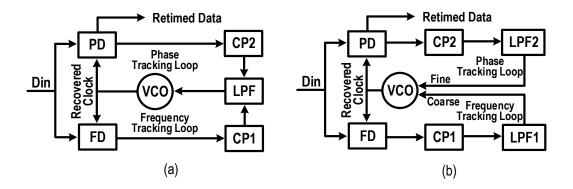

| 2.12 | CDR topologies without a reference. (a) Single control of VCO fre-                                                                               |            |

|      | quency tuning and (b) coarse and fine control of VCO frequency tuning.                                                                           | 36         |

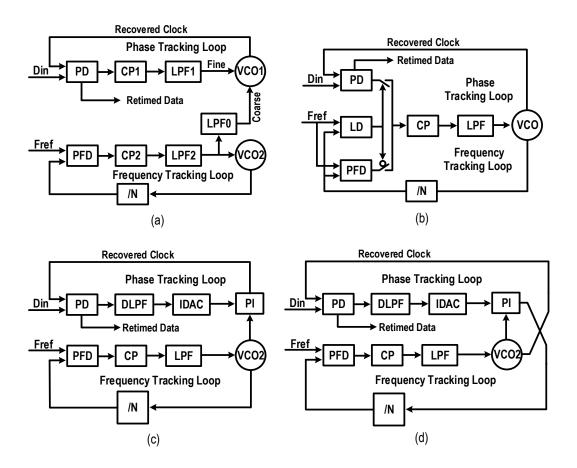

| 2.13 | CDR topologies with a reference. (a) Dual VCO architecture, (b) se-                                                                              |            |

|      | quential locking topology, (c) PI-based structure, and (d) variant of                                                                            |            |

|      | PI-based structure.                                                                                                                              | 38         |

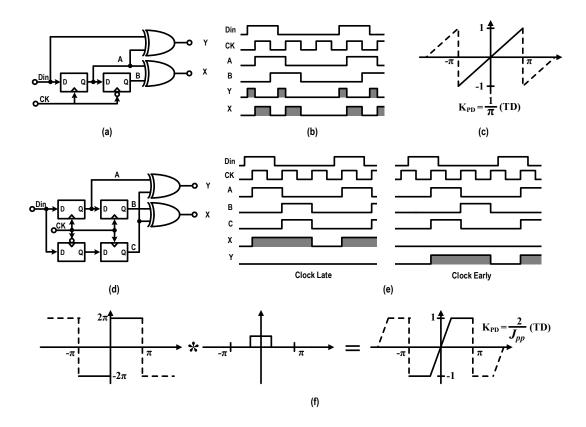

| 2.14 | Two typical CDR PDs. (a) Hogge PD implementation, (b) Hogge PD                                                                                   |            |

|      | detection mechanism, (c) Hogge PD gain, (d) Alexander PD imple-                                                                                  |            |

|      | mentation, (e) Alexander PD detection mechanism, and (e) Alexander                                                                               |            |

|      | PD gain.                                                                                                                                         | 40         |

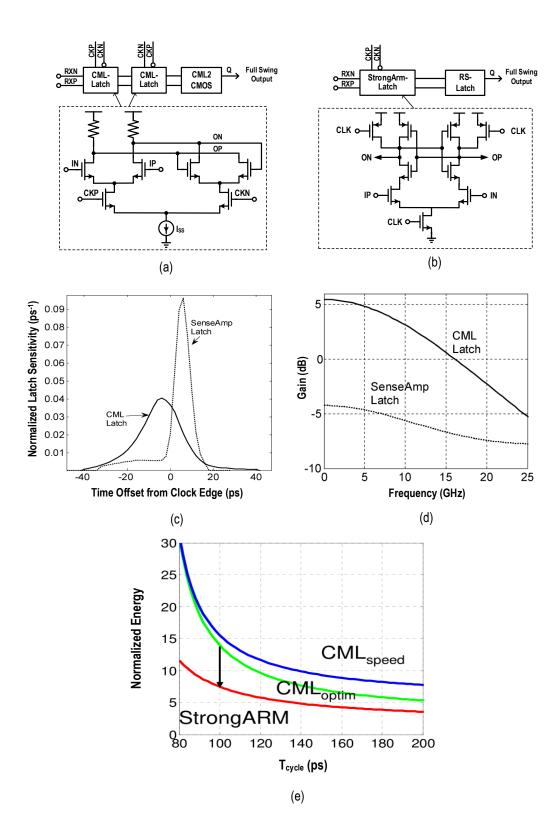

| 2.15 | Arm latch-based compactor, (c) latch sensitivity function comparison                                                                                         |            |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | [6], (d) latch transfer function comparison [6], and (e) energy con-                                                                                         |            |

|      | sumption comparison [7].                                                                                                                                     | 44         |

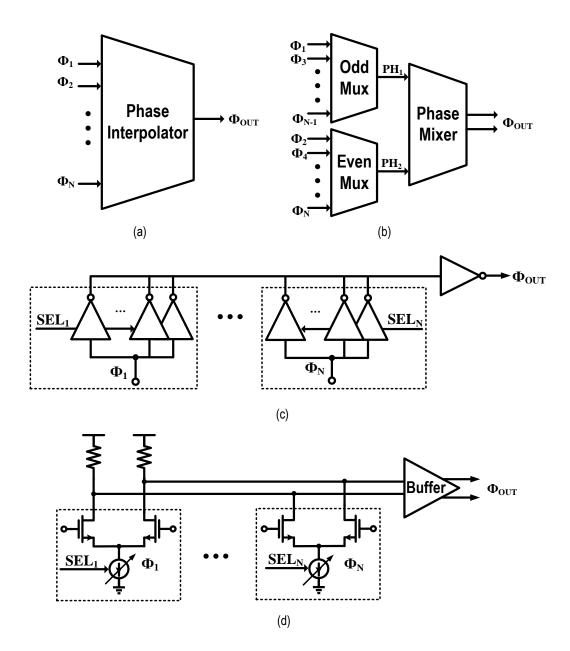

| 2.16 | PI structures and implementations. (a) Structure with direct multiple-                                                                                       |            |

|      | input phases [8, 9], (b) structure with coarse phase selection followed                                                                                      |            |

|      | by a phase mixer [10, 11], (c) inverter-based implementation [12, 13],                                                                                       |            |

|      | and (d) CML-based implementation [14, 15].                                                                                                                   | 46         |

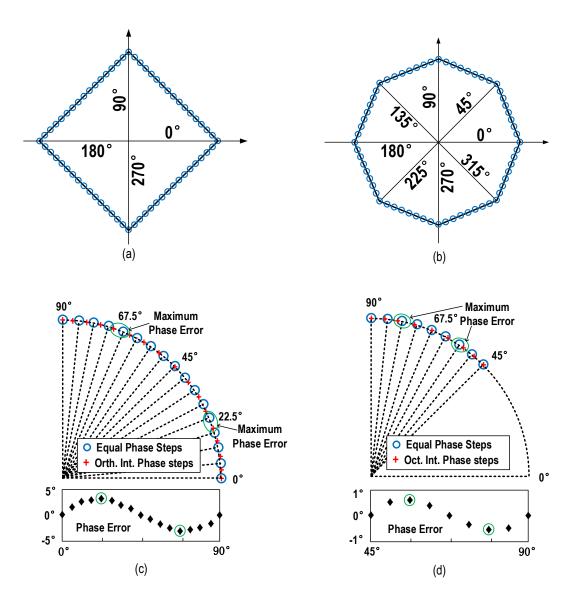

| 2.17 | • • • • • • • • • • • • • • • • • • • •                                                                                                                      |            |

|      | tagonal PI, (c) interpolated phase steps for quadrature PI in one quad-                                                                                      |            |

| 2 10 | rant, and (d) interpolated phase steps for octagonal PI in one octant.                                                                                       | 47         |

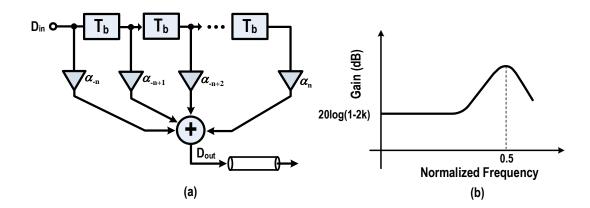

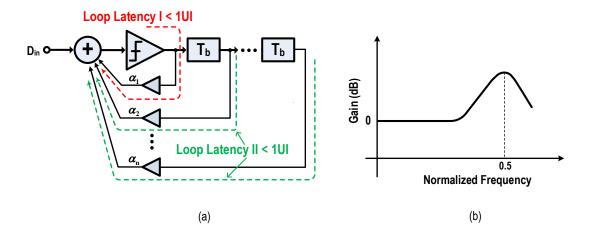

| 2.18 | The FFE. (a) Functional block diagram, where $T_b$ is the bit period and                                                                                     |            |

|      | $\alpha_n$ is the weight of the $n^{th}$ tap. (b) Typical frequency response, where                                                                          | 50         |

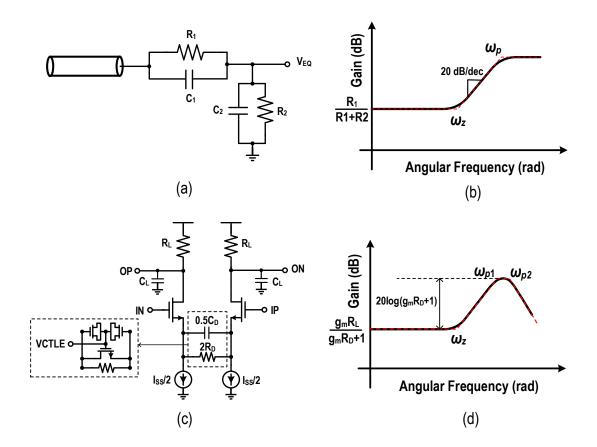

| 2 10 | k is the summation of the absolute tap weights.  The CTLE. (a) Passive implementation, (c) frequency response of the                                         | 30         |

| 2.19 | passive CTLE, (c) active implementation, and (d) frequency response                                                                                          |            |

|      | of the active CTLE. Here, $\omega_z$ is the angular frequency of the zero and                                                                                |            |

|      | $\omega_p$ is the angular frequency of the pole.                                                                                                             | 53         |

| 2.20 | The DFE. (a) Functional diagram, where $T_b$ is the bit period and $\alpha_n$ is                                                                             |            |

|      | the tap weight of the $n^{th}$ tap. (b) Typical frequency response, where                                                                                    |            |

|      | the frequency is normalized to the value of the data rate.                                                                                                   | 56         |

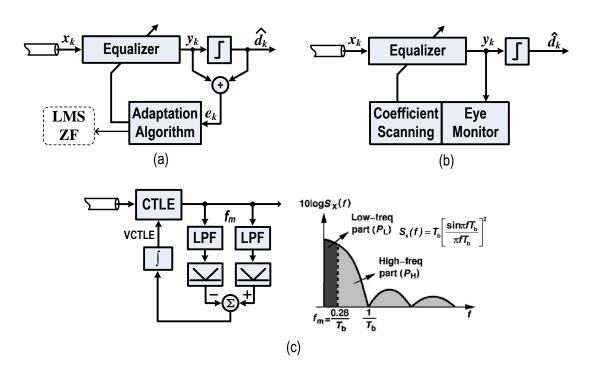

| 2.21 | Equalization adaptations. (a) Algorithm-based adjustment, (b) eye monitor                                                                                    | <b>:</b> - |

|      | based coefficient update, and (c) spectrum matching-based calibration.                                                                                       | 58         |

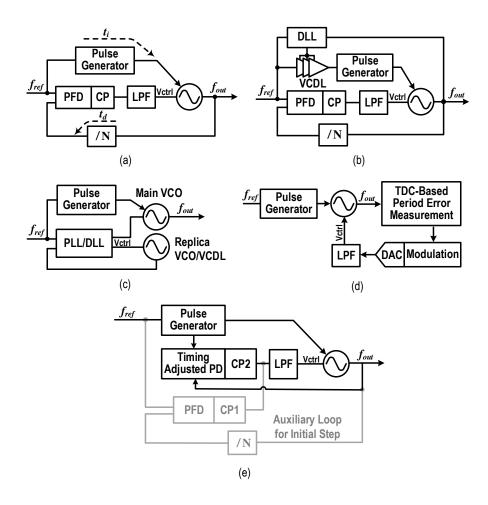

| 3.1  | Previous frequency tracking techniques. (a)Traditional IL-PLL, (b)                                                                                           |            |

| 3.1  | IL-PLL with DLL-based injection position adjustment, (c) dual-loop                                                                                           |            |

|      | architecture with replica-VCO/VCDL, (d) TDC-based FTL, and (e)                                                                                               |            |

|      | TPD-based FTL.                                                                                                                                               | 65         |

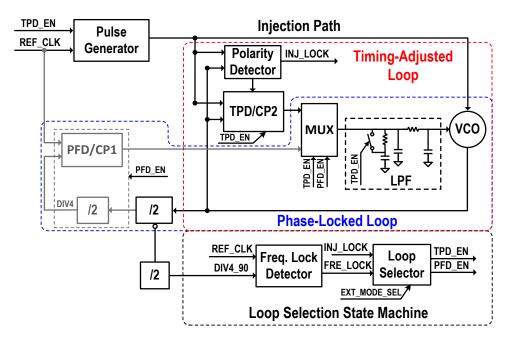

| 3.2  | The architecture of the proposed RILCM.                                                                                                                      | 68         |

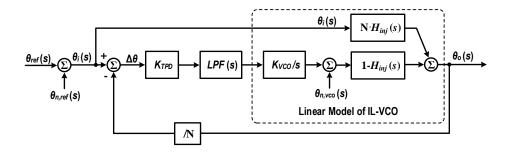

| 3.3  | Linear model of the RILCM in case of the injection-locked condition,                                                                                         |            |

|      | where $\theta_{ref}(s)$ , $\theta_i(s)$ , $\theta_o(s)$ , $\theta_{n,ref}(s)$ , $\theta_{n,vco}(s)$ represent the reference                                  |            |

|      | input phase, total input phase, output phase, reference input noise, and                                                                                     |            |

|      | VCO noise, respectively.                                                                                                                                     | 69         |

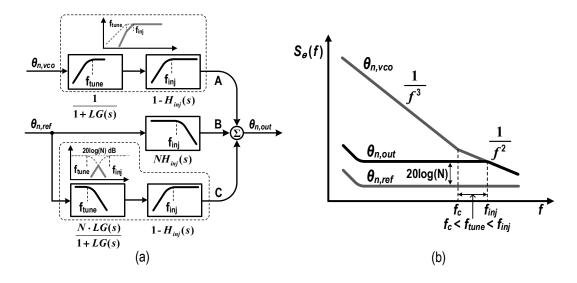

| 3.4  | NTF characteristics of the RILCM. (a) NTF behaviors and (b) simpli-                                                                                          |            |

|      | fied noise shaping characteristics. Here, $f_c$ is the corner frequency of                                                                                   |            |

|      | the oscillator, $f_{inj}$ stands for the bandwidth of the injection locking,                                                                                 |            |

|      | $f_{tune}$ denotes the tunable bandwidth of the TAL, $1/f^2$ represents the white noise of the oscillator, and $1/f^3$ is the flick noise of the oscillator. | 71         |

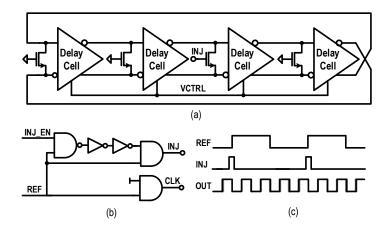

| 3.5  | IL-RVCO. (a) Four-stage RVCO implementation, (b) pulse generator,                                                                                            | / 1        |

| 3.3  | and (c) injection locking behavior.                                                                                                                          | 73         |

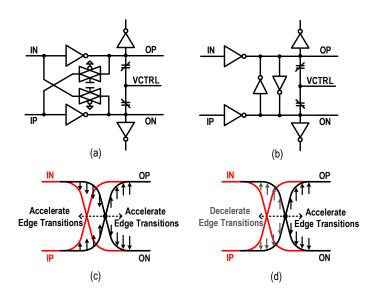

| 3.6  | (a) FTG-based FS-PDDC, (b) CCI-based FS-PDDC, (c) effect of the                                                                                              | , ,        |

|      | FTGs, and (d) effect of the CCIs. Here, the arrows stand for the effort                                                                                      |            |

|      | directions that are offered by the FTGs or CCIs.                                                                                                             | 73         |

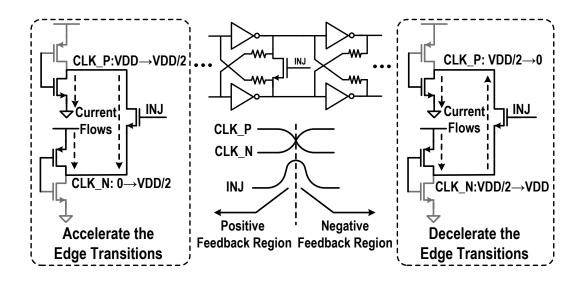

| 3.7  | Effect of the injection pulse on the speed of edge transitions, where the                                                                                    |            |

|      | proceeding portion of the injection pulse contributes positive feedback                                                                                      |            |

|      | while the following portion provides negative feedback.                                                                                                      | 75         |

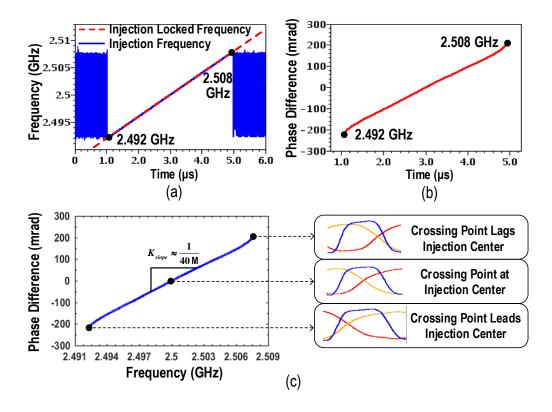

| 3.8  | Transient simulation results of the IL-RVCO. (a) Injection locking range,                                                                                    |            |

|      | (b) the relative phase difference with respect to the transient time, and                                                                                    |            |

| 2.0  | (c) the relative phase difference versus the frequency offset.                                                                                               | 76         |

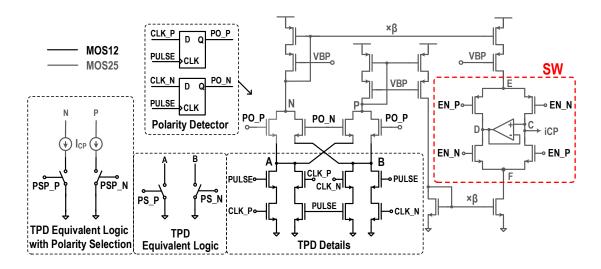

| 3.9  | Circuit implementation of the combined TPD and CP.                                                                                                           | 78         |

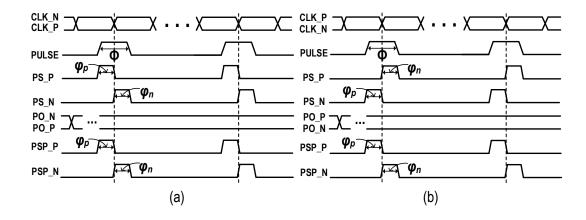

| 3.10 | Locking behaviour of the proposed TPD. (a) Waveforms when injec-                        |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | tion occurs at the falling edge of CLK_P, and (b) waveforms when in-                    |     |

|      | jection occurs at the rising edge of CLK_P.                                             | 79  |

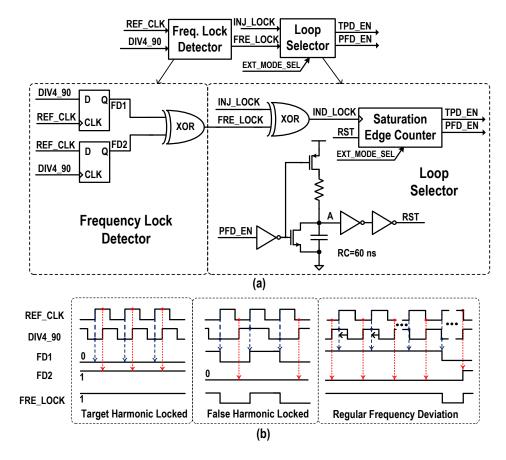

| 3.11 | Implementation of the introduced LSSM. (a) Circuit details and (b) behavior of the FLD. | 81  |

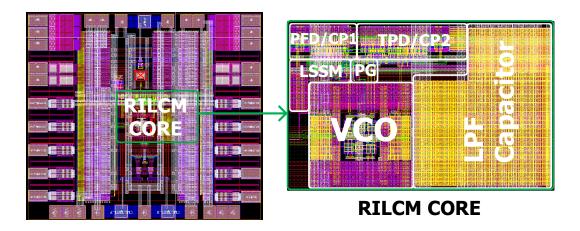

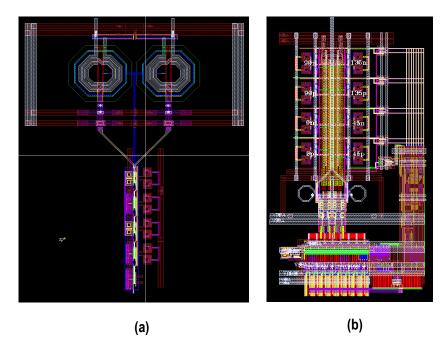

| 3.12 | Layout view of the whole RILCM chip, where the block placement of                       |     |

|      | the core circuits is illustrated in the left view.                                      | 84  |

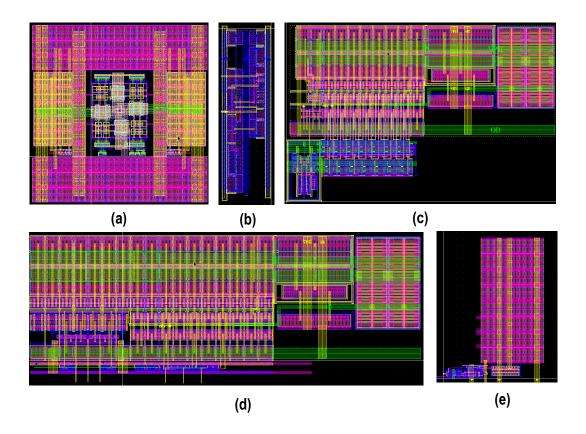

| 3.13 | Layout views of the crucial blocks. (a) VCO, (b) PG, (c) PFD/CP1, (d)                   |     |

|      | TPD/CP2, and (e) LSSM.                                                                  | 84  |

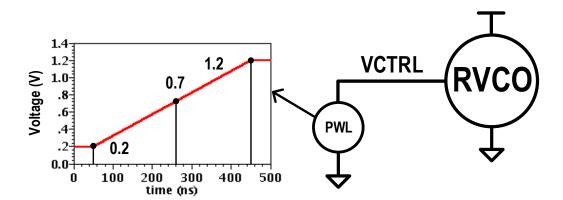

| 3.14 | Simulation setup of the RVCO, where the left curve depicts the VC-TRL of the RVCO.      | 85  |

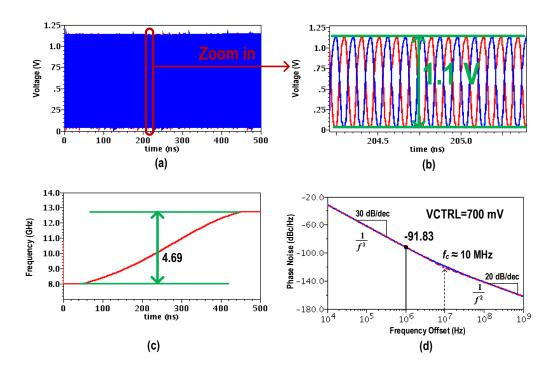

| 3.15 | Simulation results of the RVCO. (a) Differential output clock, (b) swing                |     |

|      | reduction, (c) frequency range, and (d) phase noise.                                    | 86  |

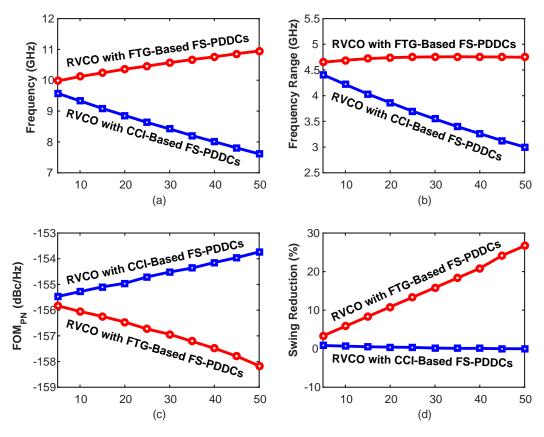

| 3.16 | Simulated performance comparison of the RVCOs with FTG-based                            |     |

|      | and CCI-based FS-PDDCs in terms of (a) operation frequency, (b) fre-                    |     |

|      | quency range, (c) FOM <sub>PN</sub> , and (d) swing reduction. Here, the horizon-       |     |

|      | tal axes denote the percentage of the FTG/CCI to the main inverter in                   |     |

|      | dimension.                                                                              | 86  |

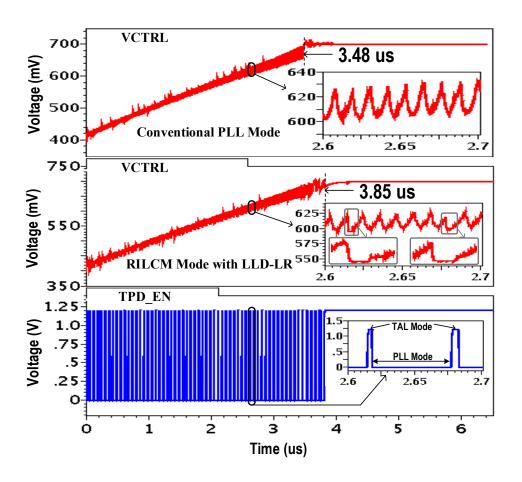

| 3 17 | Comparison of the transient procedure when operating in conventional                    | 00  |

| 3.17 | PLL mode and RILCM mode with LLD-LR.                                                    | 88  |

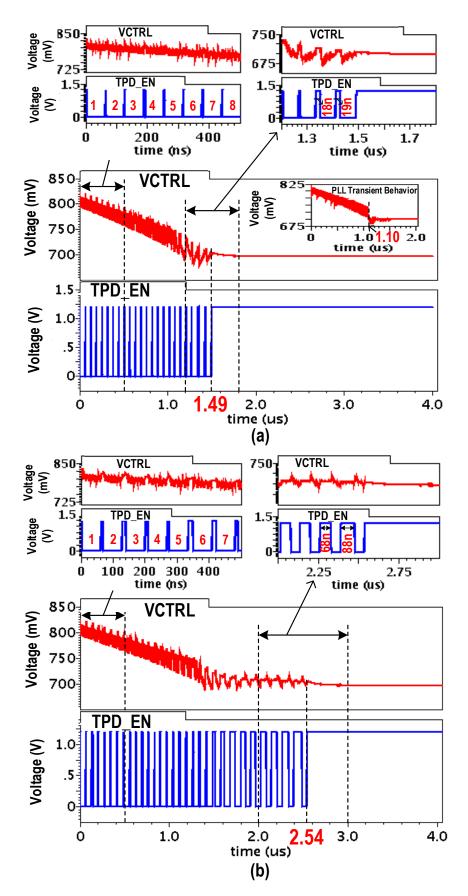

| 3 18 | Transient behavior comparison. (a) With injection-lock indicator IN-                    | 00  |

| 5.10 | JLOCK and (b) without injection lock indicator INJLOCK.                                 | 89  |

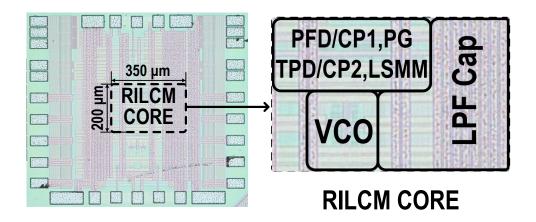

| 3 10 | Die micrograph of the RILCM.                                                            | 91  |

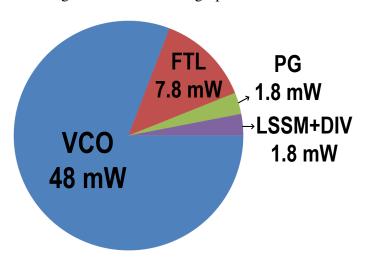

|      | Power breakdown of the RILCM.                                                           | 91  |

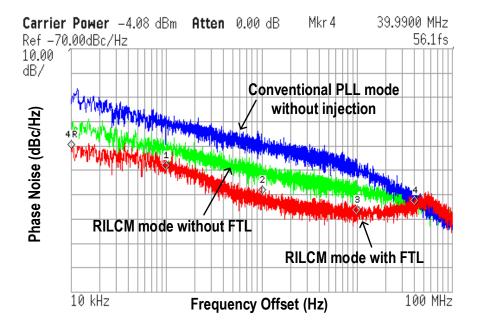

|      | Measured phase noise with half-rate output at 5GHz.                                     | 91  |

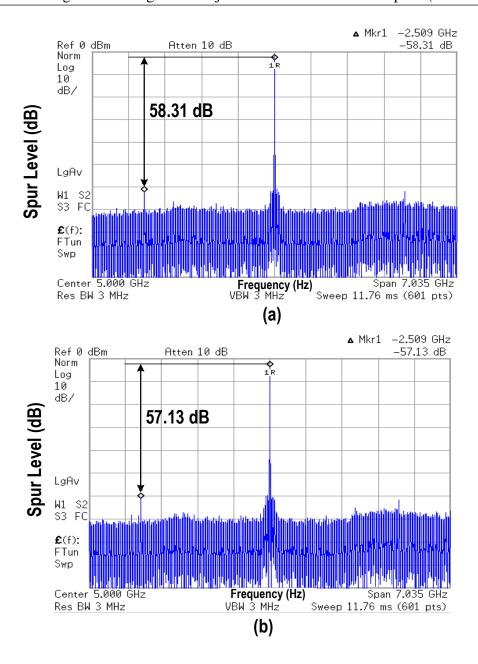

|      | Measured reference spur with half-rate output at 5GHz. (a) RILCM                        | 71  |

| 3.22 | without FTL and (b) RILCM with FTL.                                                     | 92  |

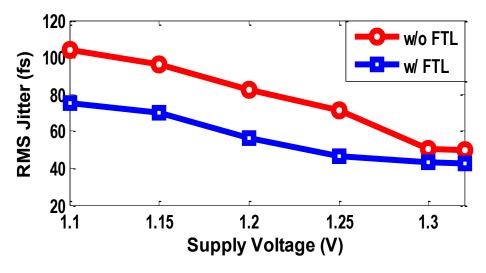

| 3 23 | Integrated rms-jitter versus supply voltage.                                            | 93  |

|      | Integrated rms-jitter versus reference frequency.                                       | 93  |

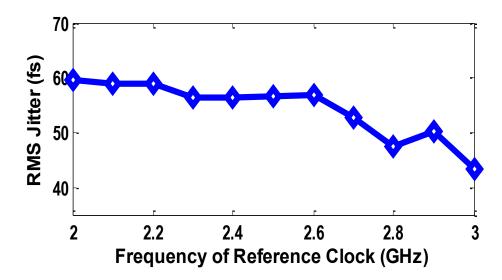

|      | Performance-area-speed graph.                                                           | 96  |

| 3.23 | Terrormance area speed grapm.                                                           | , , |

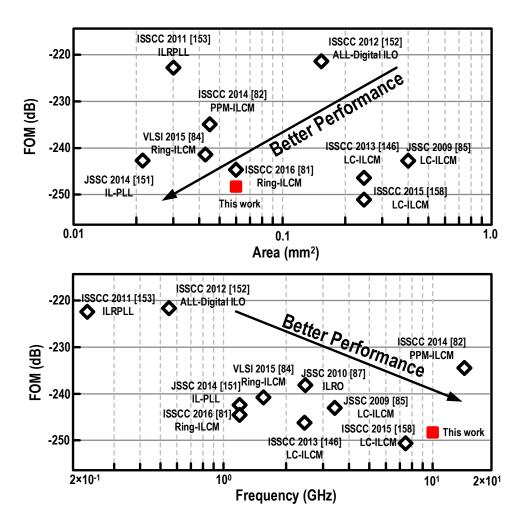

| 4.1  | (a) Critical path and (b) timing diagram for the 2:1 MUX. Here, $t_{div}$ is            |     |

|      | the delay of the divider, $t_{ck-q}$ is the ck-to-q delay of the 2:1 MUX, and           |     |

|      | $t_{setup}$ is the setup time of the sampling latch.                                    | 99  |

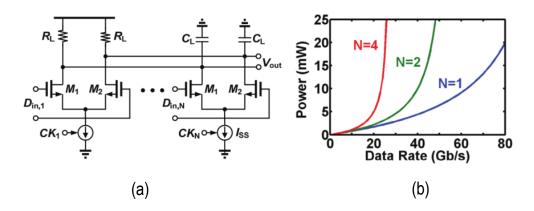

| 4.2  | (a) Traditional CML-based MUX implementation and (b) power con-                         |     |

|      | sumption with different multiplexing ratio [16]. Here, N refers to the                  |     |

|      | the multiplexing branch number.                                                         | 101 |

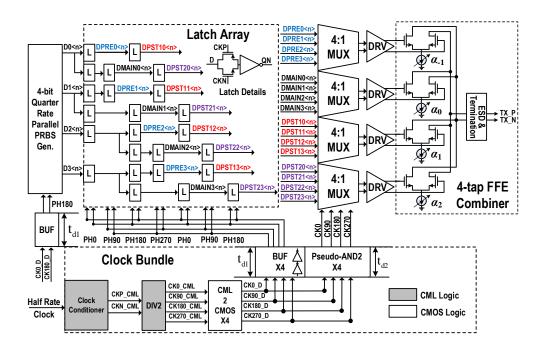

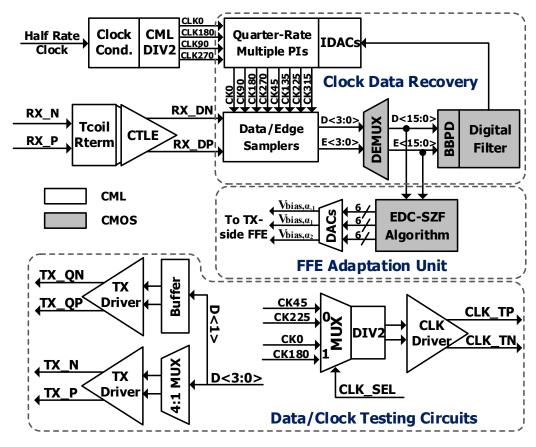

| 4.3  | Block diagram of the transmitter chip.                                                  | 102 |

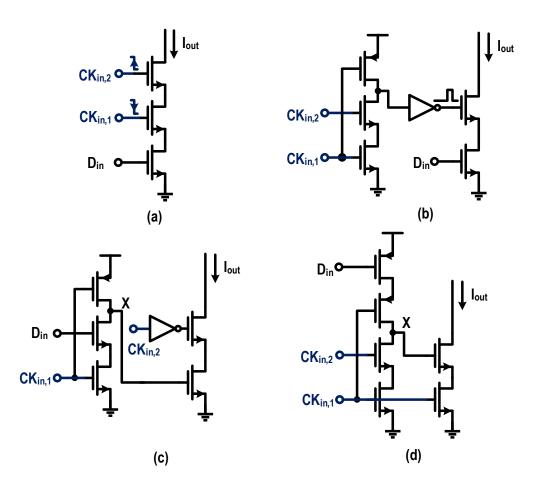

| 4.4  | Conceptional circuit schematic of the traditional 4:1 MUX.                              | 104 |

| 4.5  | Four possible unit cell implementations of the 4:1 MUX.                                 | 104 |

| 4.6  | Topology of the 4:1 MUX. (a) Conceptual schematic and (b) timing                        |     |

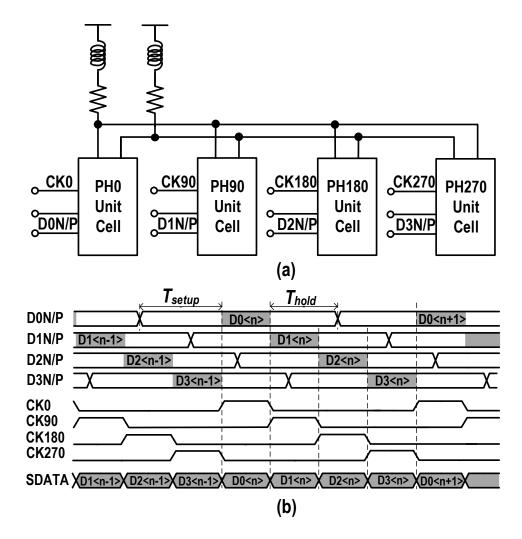

|      | diagram.                                                                                | 107 |

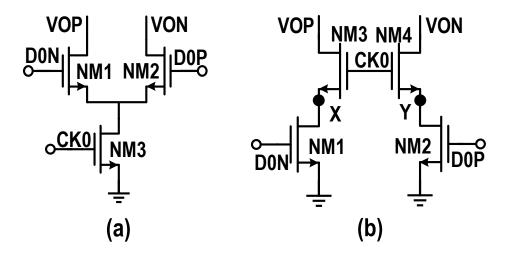

| 4.7  | Traditional unit cell implementations for high-speed 4:1 MUX. (a)                       |     |

|      | Data-up structure and (b) clock-up structure.                                           | 108 |

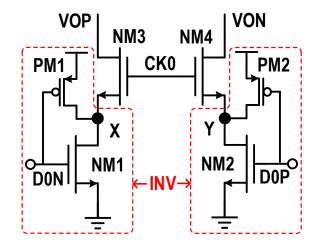

| 4.8  | Improved unit cell implementation.                                                      | 108 |

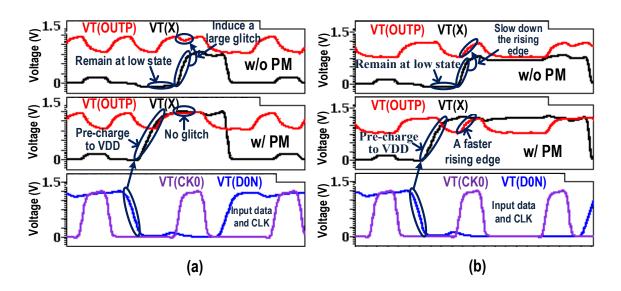

| 4.9  | Effect of the introduced PM on (a) high-level glitches and (b) edge                     |     |

|      | transitions.                                                                            | 109 |

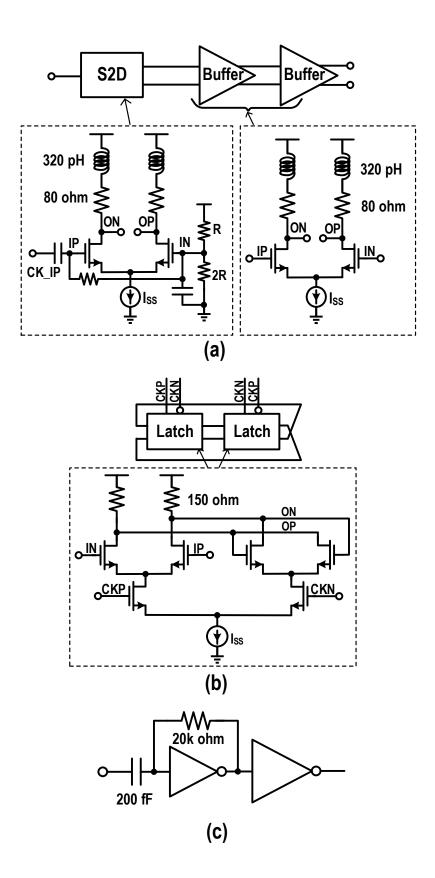

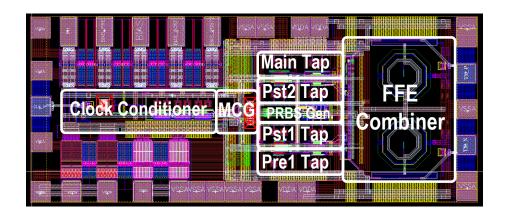

| 4.10 | Circuit details of the clocking blocks. (a) Clock conditioner, (b) DIV2,                |     |

|      | and (c) CML2CMOS.                                                                       | 111 |

| 4.11 | Pesudo-NAND2. (a) Circuit details and (b) operation waveform.                           | 113 |

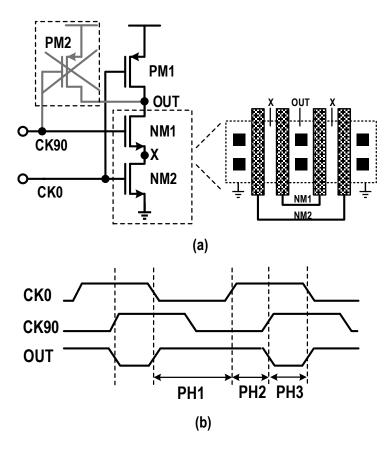

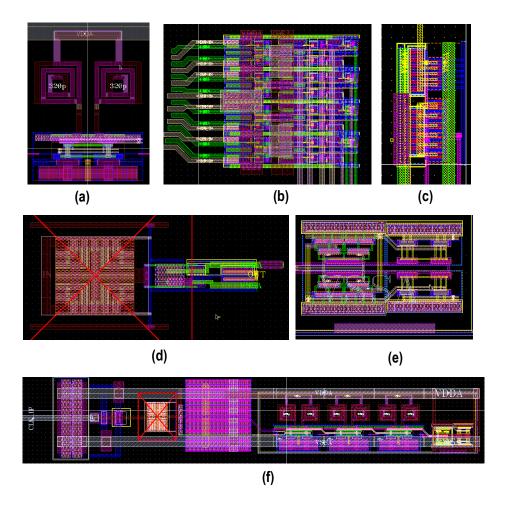

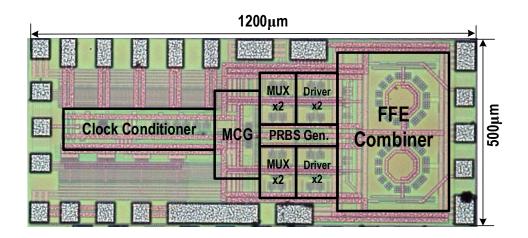

| 4.12 | Layout view of the whole transmitter chip.                                | 114 |

|------|---------------------------------------------------------------------------|-----|

| 4.13 | Layout views of the crucial blocks. (a) 4:1 MUX, (b) interleaved-         |     |

|      | retiming latch array, (c) pesudo-NAND2 with an inverter, (d) CM-          |     |

|      | L2CMOS converter, (e) DIV2, and (f) clock conditioner.                    | 115 |

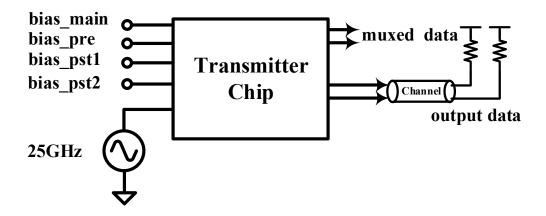

| 4.14 | Simulation setup of the transmitter chip.                                 | 117 |

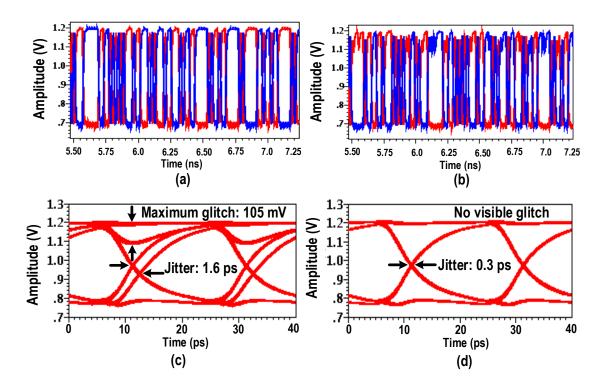

|      | (a) Transient waveform of the traditional unit cell, (b) transient wave-  |     |

| 1.13 | form of the enhanced unit cell, (c) eye-diagram of the traditional        |     |

|      | unit cell, and (d) eye-diagram of the the enhanced unit cell.             | 117 |

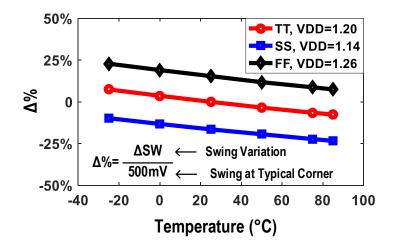

| 116  | , , , ,                                                                   |     |

|      | Swing variations of the improved unit cell under different PVT corners.   | 118 |

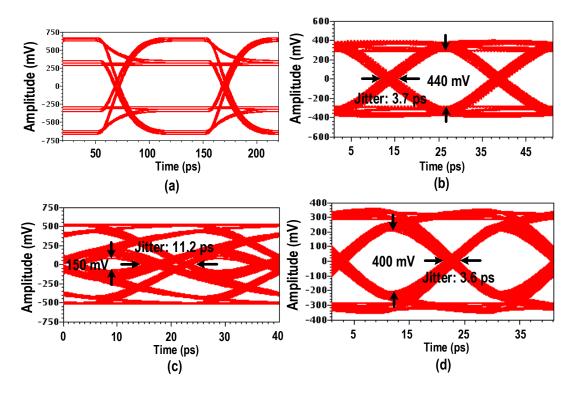

| 4.1/ | Simulation eye-diagrams of the transmitter at (a) 10 Gb/s with over       |     |

|      | equalization, (b) 40 Gb/s with proper equalization, (c) 50 Gb/s without   |     |

|      | equalization, and (d) 50 Gb/s with proper equalization.                   | 118 |

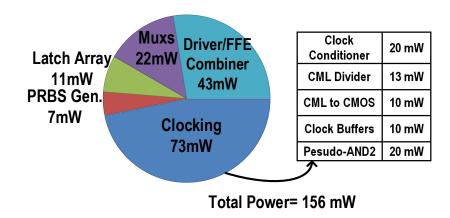

|      | Chip micrograph of the transmitter.                                       | 119 |

|      | Power breakdown of the transmitter when operating at 50 Gb/s.             | 119 |

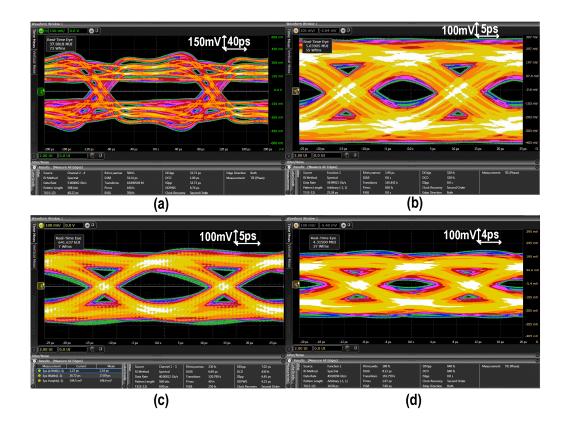

| 4.20 | Measured output eye-diagrams of the transmitter at (a) 5 Gb/s with        |     |

|      | over equalization, (b) 40 Gb/s without equalization, (c) 40 Gb/s with     |     |

|      | proper equalization, and (d) 50 Gb/s with proper equalization.            | 120 |

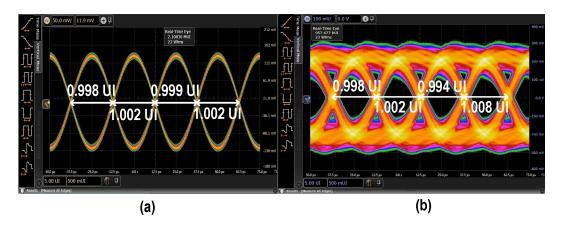

| 4.21 | Measured output eye-diagrams with four separate eyes. (a) Clock pat-      |     |

|      | tern and (b) PRBS pattern.                                                | 121 |

|      | (c) 11225 punorii.                                                        |     |

| 5.1  | Block diagram of the receiver chip.                                       | 126 |

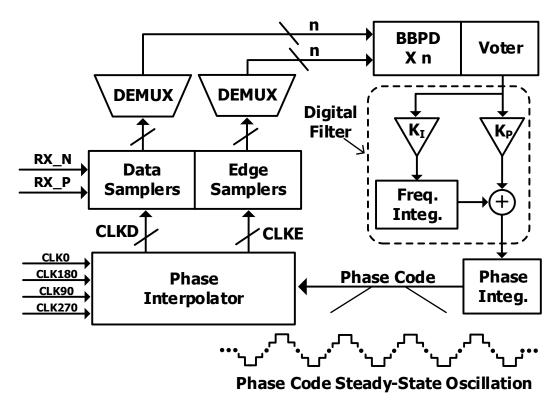

| 5.2  | Conventional BBPD-based CDR.                                              | 127 |

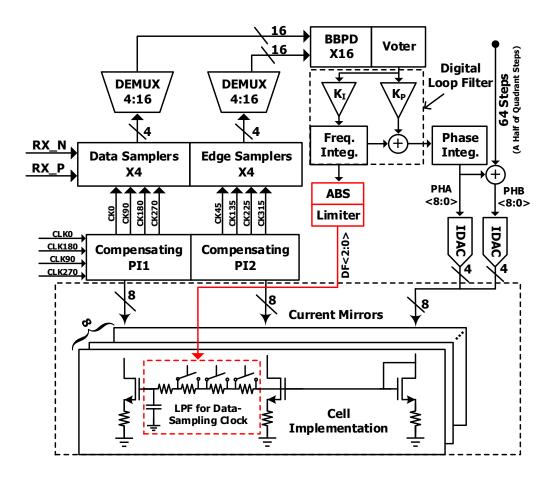

| 5.3  | Block diagram of the modified CDR architecture.                           | 128 |

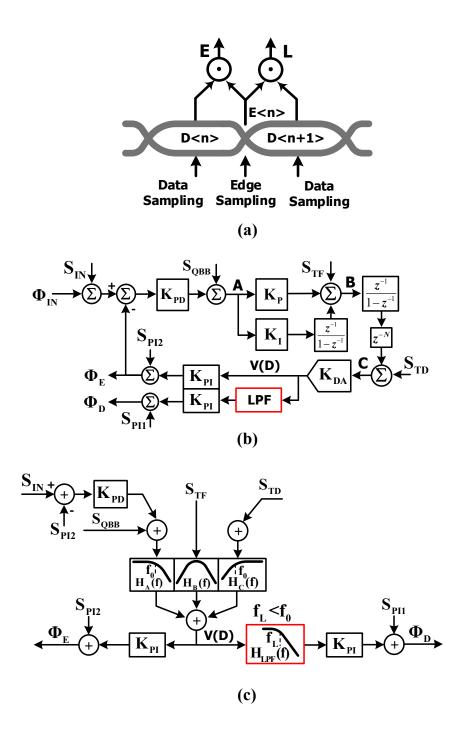

| 5.4  | Functional view of the introduced LPFs. (a) Principle of the BBPD,        |     |

|      | (b) linearized CDR model, and (c) jitter transfer functions.              | 130 |

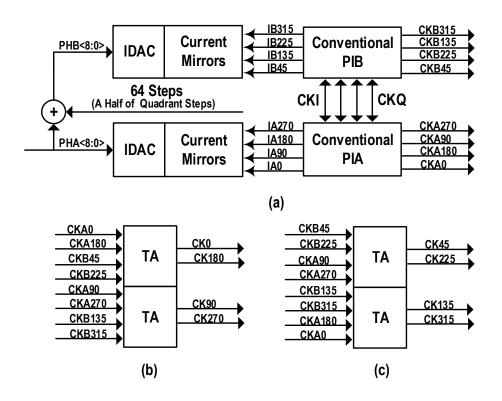

| 5.5  | Proposed compensating PI. (a) Quarter-rate 45°-spaced clock genera-       |     |

|      | tion, (b) in-phase I, Q clock generation for the data sampling, and (c)   |     |

|      | 45° phase-shifted I, Q clock generation for the edge sampling.            | 132 |

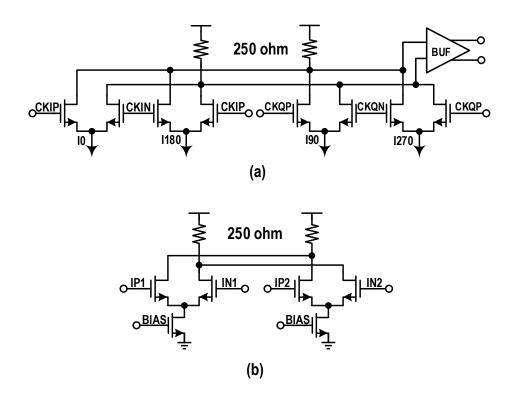

| 5.6  | Details of (a) quadrature PI and (b) TA.                                  | 132 |

| 5.7  | Phase transfer characteristics based on trigonometric-function approx-    | 132 |

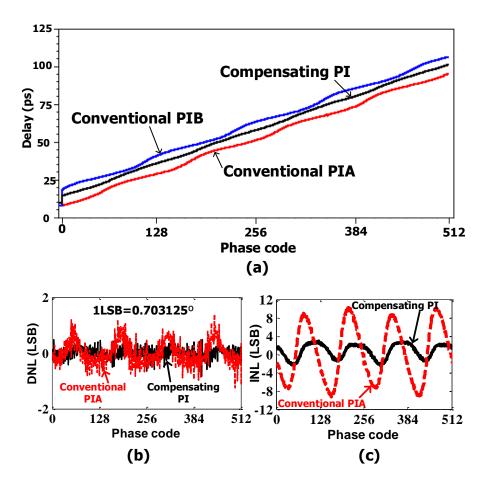

| 3.7  | imation.                                                                  | 134 |

| 5.8  | Simulation results of the phase compensating PI. (a) Simulated phase      | 134 |

| 5.0  | transfer characteristics, (b) DNL performance, and (c) INL perfor-        |     |

|      |                                                                           | 125 |

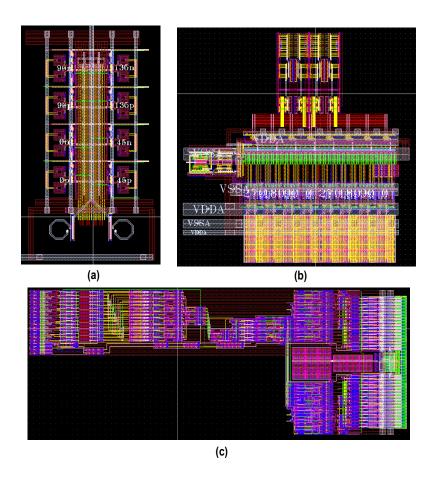

| 5.0  | mance.  Levent view of the whole transmitten chin                         | 135 |

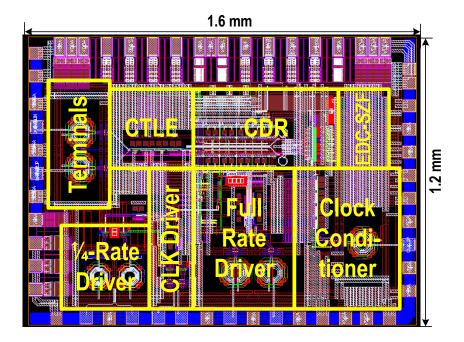

| 5.9  | Layout view of the whole transmitter chip.                                | 137 |

|      | Layout views of the (a) Terminals+CTLE and (b) CDR.                       | 138 |

| 5.11 | Layout views of the crucial blocks within the CDR. (a) Samplers, (b)      | 120 |

|      | compensating PI, and (c) digital loop filter.                             | 138 |

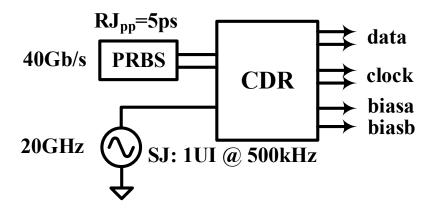

| 5.12 | Simulation setup of the CDR. A PRBS generator is used to produce          |     |

|      | the 40 Gb/s input data with 5 ps peak-to-peak jitter, a clock generator   |     |

|      | is utilized to produce the 20 GHz input clock with a 1 UI amplitude       |     |

|      | sinusoidal jitter at 500 kHz, the output data refers to the input data at |     |

|      | the samplers, the output clock is the recovered data-sampling clock,      |     |

|      | the output biasa represents the current mirror bias for 0°-phase before   |     |

|      | the LFP, and the biasb stands for the current mirror bias for 0°-phase    |     |

|      | after the LFP.                                                            | 139 |

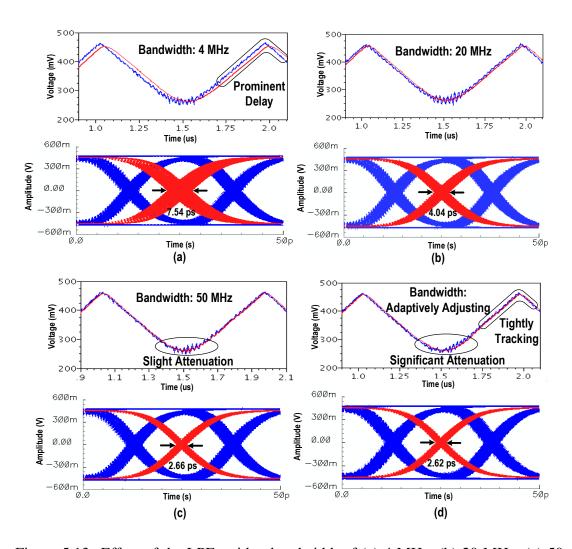

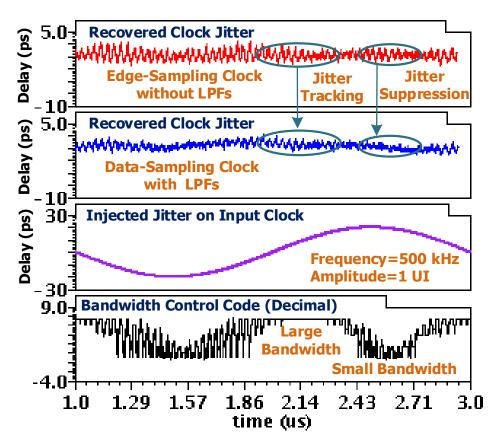

| 5.13 | Effect of the LPFs with a bandwidth of (a) 4 MHz, (b) 20 MHz, (c) 50      |     |

|      | MHz, and (d) adaptively-adjusting.                                        | 140 |

| 5 14 | Properties of the adaptive-handwidth litter suppression                   | 141 |

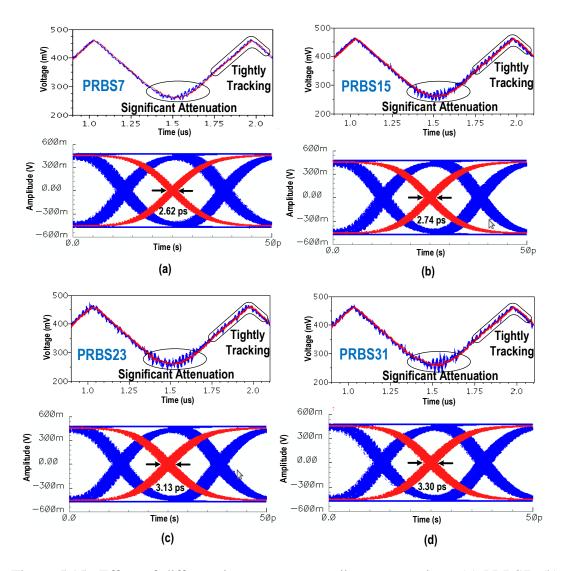

| 5.15        | Effect of different input patterns on jitter attenuation. (a) PRBS7, (b) PRBS15, (c) PRBS23, and (d) PRBS31.                                                                                                                                                                                 | 142        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

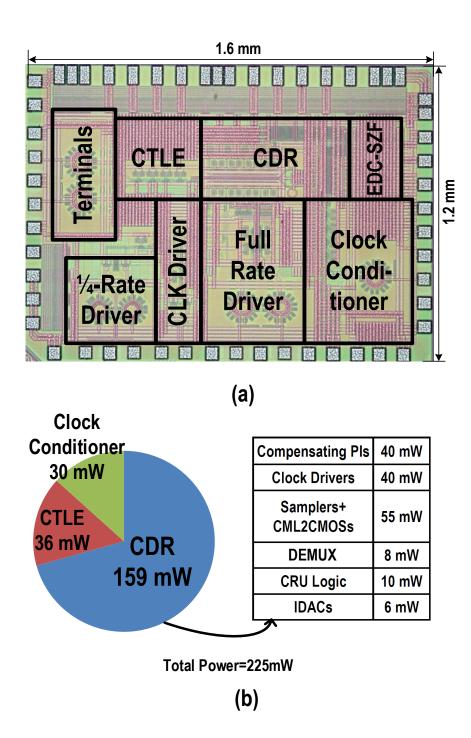

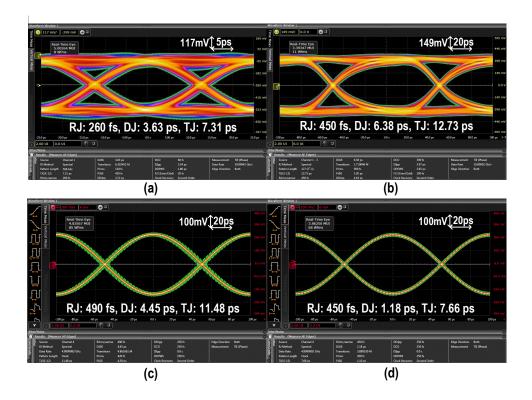

|             | (a) Chip micrograph and (b) power breakdown of the receiver. Measured eye-diagrams for (a) input data at 40 Gb/s, (b) recovered data at 10 Gb/s, (c) recovered edge-sampling clock without LPFs at 5 GHz,                                                                                    | 143        |

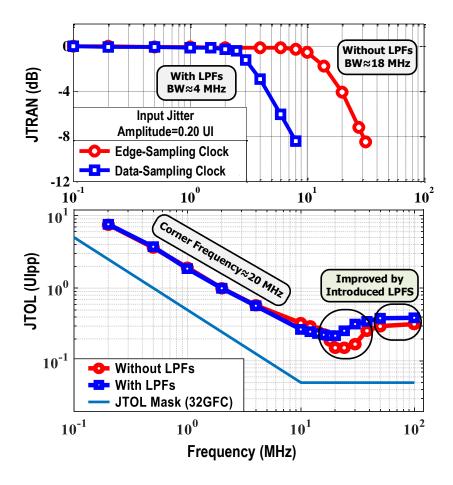

| 5.18        | and (d) recovered data-sampling clock with LPFs at 5 GHz. Measured JTRAN and JTOL with PRBS7 at 28 Gb/s.                                                                                                                                                                                     | 144<br>145 |

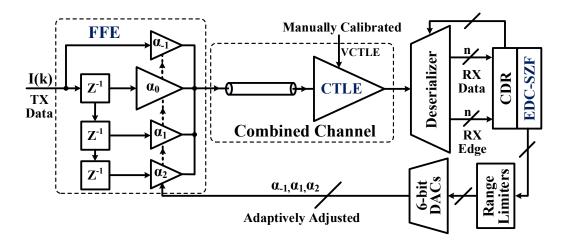

| 6.1         | Implemented equalization scheme with the proposed EDC-SZF algorithm. Here, TX-FFE and RX-CTLE are employed to compensate for the channel loss, the control voltage of the RX-CTLE (VCTLE) is manually calibrated while the tap weights $(\alpha_{-1}, \alpha_1, \alpha_2)$ of the TX-FFE are | 1.10       |

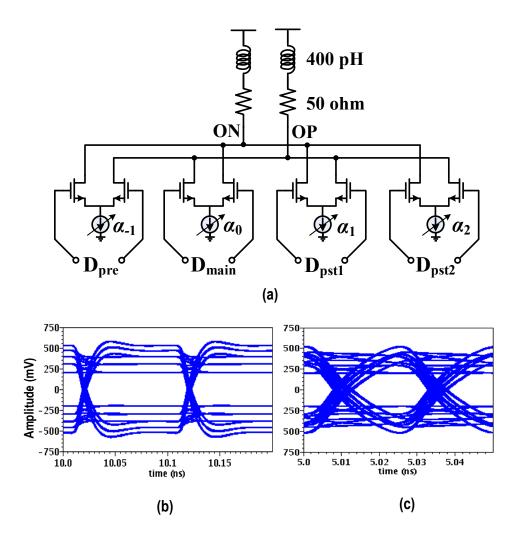

| 6.2         | adaptively adjusted by the proposed EDC-SZF.  TX-FFE. (a) Schematic details, (b) simulated output eye-diagram at 10                                                                                                                                                                          | 149        |

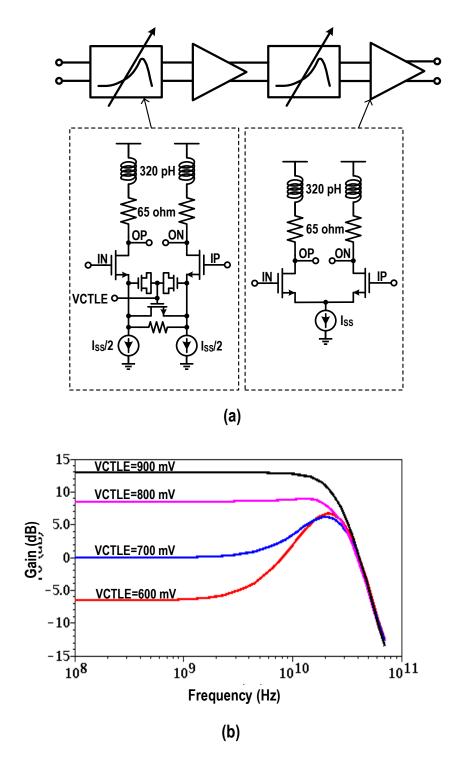

| 6.3         | Gb/s, and (c) simulated output eye-diagram at 40 Gb/s. RX-CTLE. (a) Schematic details and (b) frequency responses for dif-                                                                                                                                                                   | 150        |

|             | ferent control voltages.                                                                                                                                                                                                                                                                     | 151        |

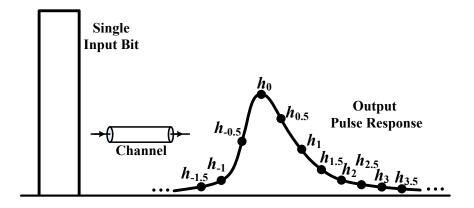

| 6.4         | Pulse response of a typical dispersion channel.                                                                                                                                                                                                                                              | 154        |

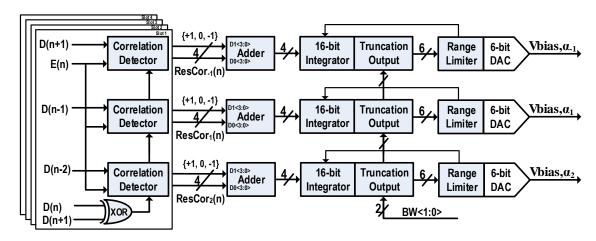

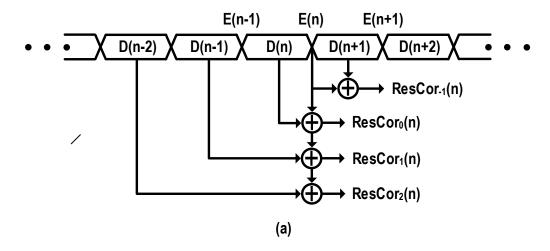

| 6.5         | Block diagram of the EDC-SZF adaptation algorithm.                                                                                                                                                                                                                                           | 158        |

| 6.6         | Correlation detector. (a) Operation principle illustration and (b) function table.                                                                                                                                                                                                           | 158        |

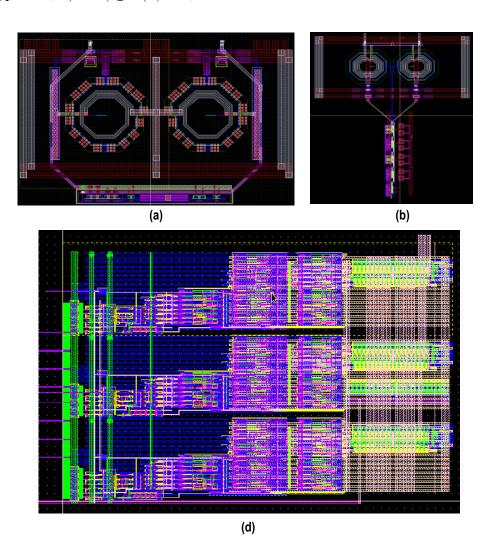

| 6.7         | Layout views of the equalization blocks. (a) TX-FFE, (b) RX-CTLE,                                                                                                                                                                                                                            | 130        |

|             | and (c) EDC-SZF.                                                                                                                                                                                                                                                                             | 159        |

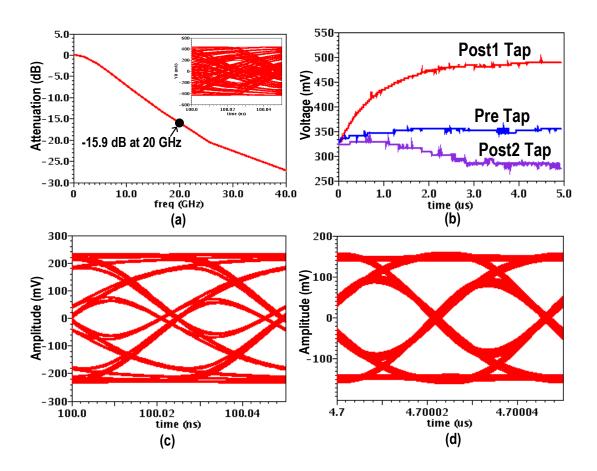

| 6.8         | Transistor-level simulation of the EDC-SZF adaptation. (a) Channel frequency response, (b) convergence process of the TX-FFE tap weights, (c) eye-diagram with zero TX-FFE tap weights, and (d) eye-diagram                                                                                  |            |

|             | with adaptively-adjusted TX-FFE tap weights.                                                                                                                                                                                                                                                 | 160        |

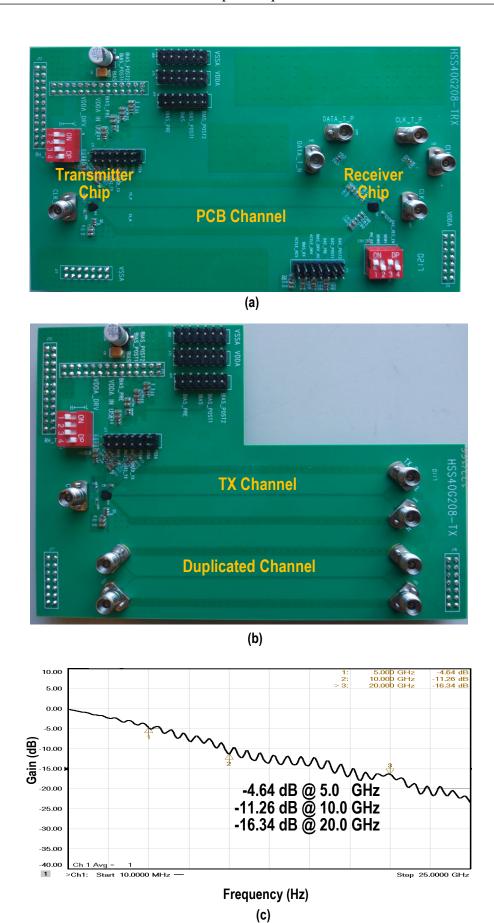

| 6.9         | Constructed chip-to-chip interconnect. (a) Testing PCB, (b) auxiliary PCB, and (c) duplicated channel frequency response.                                                                                                                                                                    | 161        |

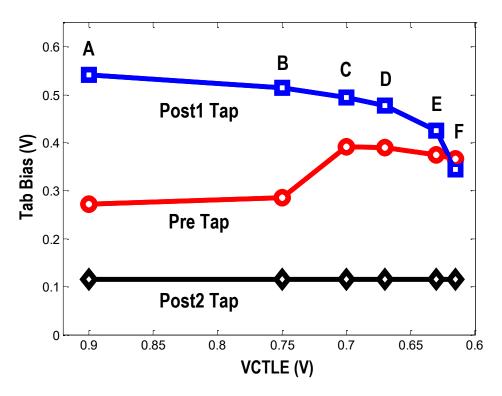

| 6.10        | Adaptively-adjusted bias voltages of the TX-FFE with different RX-                                                                                                                                                                                                                           |            |

| <b>6</b> 11 | CTLE control voltages.                                                                                                                                                                                                                                                                       | 162        |

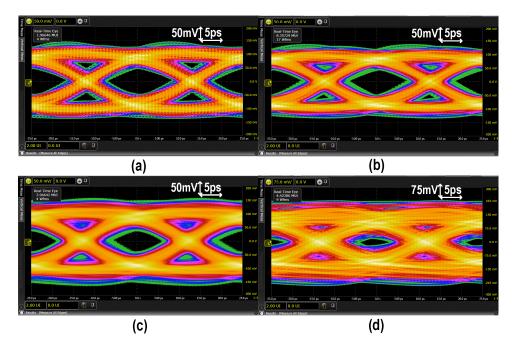

| 0.11        | Measured far-end eye-diagrams for (a) bias condition A, (b) bias condition B, (c) bias condition D, and (d) bias condition F depicted in Fig.                                                                                                                                                |            |

|             | 6.10.                                                                                                                                                                                                                                                                                        | 162        |

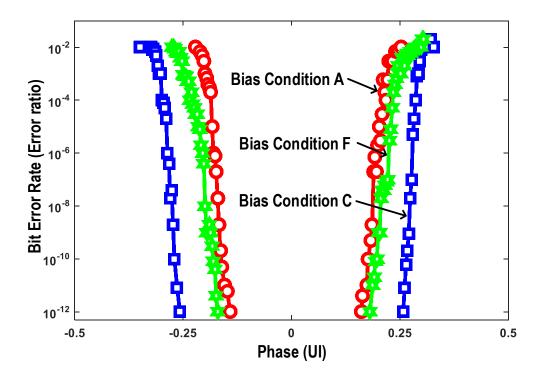

| 6.12        | Measured bathtub curves under different bias conditions depicted in Fig. 6.10.                                                                                                                                                                                                               | 163        |

| A1          | Phase accumulation behavior of the ILO. (a) Output waveform of the ILO in one injection period, (b) flow-chart diagram of the phase accu-                                                                                                                                                    |            |

|             | mulation, and (c) intuitive diagram of the phase accumulation.                                                                                                                                                                                                                               | 179        |

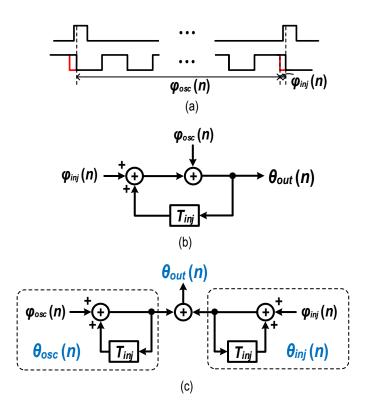

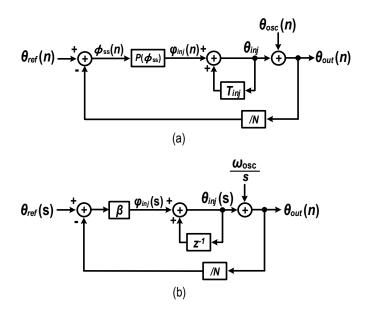

| A 2         | Model of the ILO (a) Signal flow chart and (b) linear model                                                                                                                                                                                                                                  | 180        |

## **List of Tables**

| 3.1 | PERFORMANCE SUMMARY OF THE RILCM       | 94  |

|-----|----------------------------------------|-----|

| 4.1 | PERFORMANCE SUMMARY OF THE TRANSMITTER | 122 |

| 5.1 | PERFORMANCE SUMMARY OF THE RECEIVER    | 146 |

## List of Acronyms and Abbreviations

ADC analog-to-digital converter BBPD bang-bang phase detector

BER bit error rate

CAGR compound annual growth rate

CCI cross-coupled inverter CDR clock data recovery

CEI common electrical interface CFP centum form-factor pluggable

CML current-mode logic

CP charge pump

CPU central processing units

CTLE continuous linear equalizer

DAC digital-to-analog converter

decision feedback equalizer

DIV divider

DJ deterministic jitter

DLL delay-locked loop

DNL differential nonlinearity

DRC Design rule check

DSP digital signal processing

EDC-SZF edge-data correlation based sign zero-forcing

EDR enhanced data rate

ESD electro-static discharge

FEC forward error correction

FFE feed-forward equalizer

FIR finite impulse response

FOM figure-of-merit

FS-PDDC full-swing pseudo-differential delay cell

FTG forward transmission gate FTL frequency tracking loop

GbE gigabit ethernet

GBW gain-bandwidth product

HDR high data rate HPF high-pass filter

IBTA InfiniBand trade association

IEEE institute of electrical and electronics engineers

ILCM injection-locked clock multiplier

ILO injection locked oscillator

IL-RVCO injection-locked ring voltage-controlled oscillator

INL integral nonlinearity

ISI inter-symbol interface

JGEN jitter generation

JTOL jitter tolerance

JTRAN jitter transfer

LD lock detector

LLD-LR lock-loss detection and lock recovery

LMS least mean square

LPF low-pass filter

LR long reach

LSSM loop-selection state machine

LVS layout versus schematics

MAC media access control

MEO maximum eye opening

MR medium reach MUX multiplex

NRZ non-return to zero

NTF noise transfer function

OC optical carrier OSC oscillator

PCB printed circuit board

PD phase detector

PEX parasitic extraction

PFD phase frequency detector

PG pulse generator

PI phase interpolator

PLL phase-locked loop

POD polarity detector

PSD phase shift detection

PTL phase tracking loop

QSFP quad small form-factor pluggable

RILCM ring-oscillator-based injection-locked clock multiplier

RJ random jitter

RVCO ring voltage-controlled oscillator

RX receiver

S/H sample-and-hold SerDes serializer/deserializer

SFP+ small form-factor pluggable plus

SNR signal noise ratio

SONET synchronous optical network SS-LMS sign-sign least mean square SST source-series terminated

SSTPD sub-sampling timing-adjusted phase detector

TAL timing-adjusted loop

TDC time-to-digital converter

TPD timing-adjusted phase detector

TX transmitter

UI unit interval

USR ultra short reach

VCDL voltage-controlled delay line VCO voltage-controlled oscillator

VCTLR control voltage VSR very short reach XSR extra short reach ZF zero-forcing  $f_{BW}$  -3dB bandwidth

$f_T$  cutoff frequency of the transistor  $f_c$  corner frequency of the oscillator

$f_{inj}$  injection-locking bandwidth of the injection-locked oscillator

$1/f^2$  white noise of the oscillator  $1/f^3$  flick noise of the oscillator

$S_{\theta}(f)$  phase noise spectrum of the oscillator

## **Contents**

| ΑJ | ostrac            | Et                                                                 |                                          | 1    |  |  |

|----|-------------------|--------------------------------------------------------------------|------------------------------------------|------|--|--|

| De | eclara            | tion                                                               |                                          | III  |  |  |

| A  | cknov             | vledgen                                                            | nents                                    | IV   |  |  |

| Li | st of ]           | Main P                                                             | ublications                              | VI   |  |  |

| Li | st of ]           | Figures                                                            |                                          | VII  |  |  |

| Li | st of '           | <b>Tables</b>                                                      |                                          | XII  |  |  |

| Li | st of A           | Acrony                                                             | ms and Abbreviations                     | XIII |  |  |

| 1  |                   | oductio                                                            |                                          | 1    |  |  |

|    | 1.1               | Backg                                                              |                                          | 1    |  |  |

|    | 1.2               |                                                                    | enges in Cutting-Edge Transceivers       | 3    |  |  |

|    |                   |                                                                    | rch Objectives                           | 4    |  |  |

|    | 1.4               |                                                                    | rch Contributions                        | 6    |  |  |

|    | 1.5               | Organ                                                              | ization of the Thesis                    | 7    |  |  |

| 2  | Literature Review |                                                                    |                                          | 10   |  |  |

|    | 2.1               | Gener                                                              | al Design Considerations                 | 11   |  |  |

|    |                   | 2.1.1                                                              | Technology Choices                       | 11   |  |  |

|    |                   | 2.1.2                                                              | Spaces of Electrical Links               | 12   |  |  |

|    |                   | 2.1.3                                                              | On-Chip Wire Modeling                    | 15   |  |  |

|    | 2.2               | SerDe                                                              | s Design Metrics                         | 16   |  |  |

|    |                   |                                                                    | Data Rate and Power Efficiency           | 16   |  |  |

|    |                   | 2.2.2                                                              | Bit Error Rate                           | 17   |  |  |

|    |                   |                                                                    | Clock Data Recovery (CDR) Specifications | 19   |  |  |

|    | 2.3               |                                                                    | s of Electrical Serial Links             | 21   |  |  |

|    |                   | 2.3.1                                                              |                                          | 23   |  |  |

|    |                   | 2.3.2                                                              | Transmitter Techniques                   | 30   |  |  |

|    |                   | 2.3.3                                                              | Receiver Techniques                      | 36   |  |  |

|    |                   | 2.3.4                                                              | Channel Equalization                     | 49   |  |  |

| 3  | Desi              | Design of the Ring-Based Injection-Locked Clock Multiplier (RILCM) |                                          |      |  |  |

|    | 3.1               |                                                                    | enges in RILCM and Previous Solutions    | 64   |  |  |

|    |                   | 3.1.1                                                              | Challenges in RILCM                      | 64   |  |  |

|    |                   | 3.1.2                                                              | Prior Arts                               | 66   |  |  |

|    | 3.2               | -                                                                  | sed RILCM Architecture                   | 68   |  |  |

|    |                   | 3.2.1                                                              | Overall Architecture                     | 68   |  |  |

|   |     | 3.2.2   | Architecture Modeling                                       | 69  |

|---|-----|---------|-------------------------------------------------------------|-----|

|   | 3.3 | Injecti | on-Locked Ring Voltage-Controlled Oscillator (IL-RVCO)      | 72  |

|   |     | 3.3.1   | Implementation of the IL-RVCO                               | 73  |

|   |     | 3.3.2   | Relationship Between the Relative Phase Difference and the  |     |

|   |     |         | Frequency Offset                                            | 75  |

|   | 3.4 | The Pa  | roposed Phase Difference Detection                          | 77  |

|   |     | 3.4.1   | Principle of the Proposed Timing-Adjusted Phase Detector    | 79  |

|   |     | 3.4.2   | Polarity Selection                                          | 80  |

|   | 3.5 | Mecha   | anism of the Lock-Loss Detection and Lock Recovery (LLD-LR) | 81  |

|   |     | 3.5.1   | Operation Process of the LLD-LR                             | 81  |

|   |     | 3.5.2   | Principles of the Lock Loss and False Lock Detection        | 82  |

|   | 3.6 | Experi  | imental Results                                             | 83  |

|   |     | 3.6.1   | Tools and Fabrication Process                               | 83  |

|   |     |         | Layout and Simulation Results                               | 85  |

|   |     | 3.6.3   | Chip Micrograph and Measurement results                     | 90  |

|   |     | 3.6.4   | Performance Comparison                                      | 95  |

|   | 3.7 | Chapte  | er Summary                                                  | 96  |

| 4 | The | Transn  | nitter Design                                               | 98  |

|   | 4.1 |         | n Challenges in High-Speed Transmitter                      | 99  |

|   |     | 4.1.1   | Timing Constraints                                          | 99  |

|   |     | 4.1.2   | Bandwidth Limitations                                       | 100 |

|   | 4.2 | Transr  | mitter Architecture                                         | 102 |

|   |     | 4.2.1   | Overall Architecture                                        | 102 |

|   |     | 4.2.2   | Features of the Transmitter                                 | 103 |

|   | 4.3 | Enhan   | ced 4:1 Multiplexer (MUX)                                   | 104 |

|   |     | 4.3.1   | Previous 4:1 MUXs                                           | 104 |

|   |     | 4.3.2   | Topology Consideration                                      | 106 |

|   |     | 4.3.3   | Enhancement on the Unit Cell of the 4:1 MUX                 | 107 |

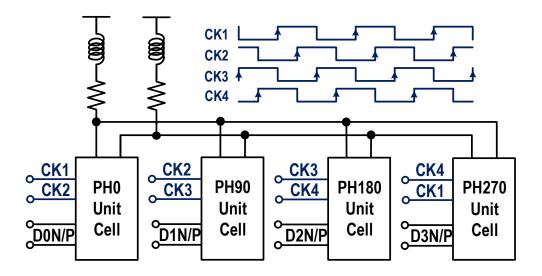

|   | 4.4 | Clocki  | ing for the Transmitter                                     | 112 |

|   |     | 4.4.1   | Topology of the Clock Bundle                                | 112 |

|   |     | 4.4.2   | Clocking Blocks                                             | 112 |

|   | 4.5 | Experi  | imental Results                                             | 114 |

|   |     | 4.5.1   | Tools and Fabrication Process                               | 114 |

|   |     |         | Layout and Simulation Results                               | 116 |

|   |     | 4.5.3   | Chip Fabrication and Measurement Results                    | 120 |

|   |     | 4.5.4   | Performance Comparison                                      | 121 |

|   | 4.6 | Chapte  | er Summary                                                  | 122 |

| 5 | The | Receiv  | er Design                                                   | 123 |

|   | 5.1 |         | n Considerations of the Receiver                            | 124 |

|   |     | 5.1.1   |                                                             | 124 |

|   |     | 5.1.2   | CDR Bandwidth                                               | 124 |

|   |     | 5.1.3   | Challenges within High-Speed CDR                            | 125 |

|   | 5.2 |         | ver Architecture                                            | 126 |

|   |     | 5.2.1   | Overall Architecture                                        | 126 |

|   |     | 5.2.2   | Features of the Receiver                                    | 127 |

|   | 5.3 | Impro   | ved Digital CDR                                             | 127 |

|   |     | 5.3.1   | Dithering Behavior in Digital CDR                           | 127 |

|   |     | 5.3.2   | Architecture Improvement                                    | 128 |

|    |                                                              | 5.3.3    | Behavior of the Improved CDR                            | 129 |  |

|----|--------------------------------------------------------------|----------|---------------------------------------------------------|-----|--|

|    | 5.4                                                          | Comp     | ensating Phase Interpolator                             | 131 |  |

|    |                                                              | 5.4.1    | Implementation Details                                  | 133 |  |

|    |                                                              | 5.4.2    | Linearity Analysis                                      | 133 |  |

|    | 5.5                                                          | Exper    | imental Results                                         | 136 |  |

|    |                                                              | 5.5.1    | Tools and Fabrication Process                           | 136 |  |

|    |                                                              | 5.5.2    | Layout and Simulation Results                           | 137 |  |

|    |                                                              | 5.5.3    | Chip Fabrication and Measurement Results                | 143 |  |

|    |                                                              | 5.5.4    | Performance Comparison                                  | 145 |  |

|    | 5.6                                                          | Chapte   | er Summary                                              | 146 |  |

| 6  | Ove                                                          | rall Ser | rial Link and Adaptive Equalization                     | 148 |  |

|    | 6.1                                                          | Serial   | Link and Channel Equalization                           | 149 |  |

|    |                                                              | 6.1.1    | Link Connection and Equalization Scheme                 | 149 |  |

|    |                                                              | 6.1.2    | Equalizer Implementation Details                        | 150 |  |

|    | 6.2                                                          | Edge-    | Data Correlation-Based Sign Zero-Forcing (EDC-SZF)      | 152 |  |

|    |                                                              | 6.2.1    | Drawbacks of Previous Adaptation Algorithms             | 152 |  |

|    |                                                              | 6.2.2    | Iteration of the EDC-SZF                                | 153 |  |

|    |                                                              | 6.2.3    | Correlation between Edge Information and Recovered Data | 153 |  |

|    |                                                              | 6.2.4    | Derivation of the EDC-SZF                               | 155 |  |

|    |                                                              | 6.2.5    | Implementation of the EDC-SZF                           | 157 |  |

|    | 6.3                                                          | Exper    | imental Results                                         | 160 |  |

|    |                                                              | 6.3.1    | Layout and Simulation Results                           | 160 |  |

|    |                                                              | 6.3.2    | Measurement Results                                     | 163 |  |

|    | 6.4                                                          | Chapte   | er Summary                                              | 164 |  |

| 7  |                                                              |          | s and Future Work                                       | 165 |  |

|    | 7.1                                                          | Concl    | usions                                                  | 165 |  |

|    | 7.2                                                          | Future   | e Work                                                  | 167 |  |

| Bi | bliog                                                        | raphy    |                                                         | 168 |  |

| Aı | pend                                                         | lices    |                                                         | 178 |  |

|    | Appendix A Modeling of the Injection-Locked Oscillator (ILO) |          |                                                         |     |  |

|    |                                                              |          | Behavior Model of the ILO                               | 178 |  |

|    |                                                              | A.2 I    | Linear Model of the ILO                                 | 180 |  |

|    |                                                              |          | Tracking Bandwidth of the ILO                           | 182 |  |

|    | App                                                          | endix B  | Convergence Proof of the Proposed EDC-SZF Iteration     | 184 |  |

## Chapter 1

#### Introduction

#### 1.1 Background

The exponential growth of cloud computing, social networking, and multimedia sharing has led to an explosive bandwidth demand on data communication. Cisco global IP traffic forecast estimates that the global IP traffic will grow at a compound annual growth rate (CAGR) of 22 percent from 2015 to 2020. By 2020, it is expected to see 50 billion connected devices generating more than two Zetta bytes ( $2^{30}$  Tera bytes) of data traffic annually (see Fig. 1.1). Moreover, 64 percent of all the Internet traffic will be delivered globally crossing the content delivery networks [1]. To accommodate this aggregated bandwidth requirement, the study group of Institute of Electrical and Electronics Engineers (IEEE) P802.3bs has approved a 400 Gigabit Ethernet (GbE) standard to quadruple the backbone bandwidth of the existing 100 GbE [17] and the InfiniBand® trade association (IBTA) has announced its 600 Gb/s computer networking communication standard high data rate (HDR) in the roadmap [18]. To support such high-speed data communications, multi-lane high-speed serial links are usually employed to extend the throughput bandwidth. As an example, the next-generation 400 GbE will be most possibly implemented by multiple serial links in forms of 16x25 Gb/s or 8x50 Gb/s, where the latter lane configuration is more in line with the trend because of its low cost, high capability, simplified cabling, high power efficiency, and less coherent optical devices.

Among a variety of components in these high-speed links, the physical Serializ-

Figure 1.1: Diagram of the global data traffic trend [1]. By 2020, 50 billion devices will be connected generating more than two zetta bytes of data traffic annually.

er/Deserializer (SerDes) transceiver plays a critical role in making up the communication connections between the data link layer and the physical medium. Due to the development of the optical communication and post massive data-processing ability, the data-moving capability is mainly limited by the maximum speed of the SerDes transceivers. Over the past few decades, the transceiver data rate has constantly been increased from Mb/s to tens of Gb/s [19]. Fig. 1.2 shows the wired network roadmap since 2000 [2], where the small form-factor pluggable plus (SFP+) line describes the port speeds on servers, the quad small form-factor pluggable (QSFP) curve shows the speeds of switches above the servers, and the centum form-factor pluggable (CFP) line illustrates the data rates of routers. Similar to 10 Gb/s ports on servers that have driven the speed of switches to 40 Gb/s and 100 Gb/s, the development of 25 Gb/s networking has updated 100 Gb/s switching and 400 Gb/s routing. At present, the Ethernet Alliance is evaluating potential standards for 50 Gb/s on the server and 200 Gb/s on the switch. Looking forward to 2025, the data communication speed is tend to be renewed to 100 Gb/s on the server, 400 Gb/s on the switch, and 1 Tb/s on the router. So far, 25-28 Gb/s serial links approved by InfiniBand enhanced data rate (EDR), 32G fibre channel (32GFC), and common electrical interface (CEI)-28G have stepped into the period of industrial deployment [20, 21, 22]. Meanwhile, 38-64 Gb/s transceivers, which will play key roles in the next-generation data rates supported by Ethernet 400 GbE, InfiniBand HDR, and CEI-56G, have attracted increasing research attention in

Figure 1.2: Wired network roadmap [2]. The data rates in SFP+, QSFP, and CFP are updating towards 100Gb/s, 400Gb/s, and 1Tb/s, respectively.

both the industry and academia [17, 18, 23, 24, 25, 26]. This dissertation mainly focuses on the advanced techniques of high-speed SerDes transceivers for chip-to-chip communications operating at 40+ Gb/s in CMOS process.

#### 1.2 Challenges in Cutting-Edge Transceivers

To accommodate the requirement of the continuously increasing data communications, cutting-edge transceivers operating at 38-64 Gb/s have become standard modules within the next-generation connections for data centers and backbone networks [17, 18, 27]. The main challenges in designing such high-speed transceivers originate from the ever decreased UI period [23, 24, 25], which not only poses high bandwidth requests on the blocks located at the critical path, but also makes the link timing budget extremely tight. The CMOS fabrication process, which is preferred due to its large-scale integration and aggressive pricing advantage, has made the designs even more challenging because of its limited cutoff frequency and poor noise performance [7, 28, 29]. Although an advanced process can provide a higher operation speed, it cannot completely solve these problems as the parasitic capacitances/resistances at the high-speed outputs usually do not scale well with the technology because of the bonding and/or electro-static discharge (ESD) protection requirements. Meanwhile, economic feasibility is another factor that must be considered when constructing multilane connections. It usually involves power consumption, area occupation, and heat

dissipation, where small area occupation and low power consumption could improve the port density and lower the requirement of heat dissipation, hence reducing the overall cost [28, 30, 31]. For implementations, the digital media access control (MAC) layer and the analog physical layer (SerDes transceiver) are developing at different stages. Specifically, the 200G MAC (4×50 Gb/s) has been implemented and validated in the industry [31], while the physical layer is still in the period of moving from the lab to the market [17, 18, 23, 24, 25, 26, 27, 32]. This is because the MAC mainly processes the parallel data streams, where the timing requirement can be relaxed by increasing the parallel bit width. In contrast, the SerDes transceiver has to provide accurate timing information, sufficient bandwidth, and appropriate equalization for the full-rate data communication.

#### 1.3 Research Objectives

The next-generation SerDes transceivers that support 38-64 Gb/s have attracted great attentions from both the industry and the academia due to their broad market potential and significant academic value. Although the technical feasibility has been proved by several 40-56 Gbs transceiver designs [33, 34, 35, 36], plenty of research studies are still demanded to further optimize the power consumption, area occupation, and operation robustness, thus paving the path for the upcoming industrial deployment. This thesis mainly focuses on the enhancement techniques to explore the maximum process limit and hence provides potential solutions for the cutting-edge transceiver designs. The major research objectives are summarized as follow.

• Designing a robust ring-oscillator-based injection-locked clock multiplier (RIL-CM) with optimized figure-of-merit. RILCM has been proven to be one of the most promising solutions for high-speed low-jitter clock multiplications since it combines the good properties of small area occupation and low phase noise. However, there still exists two difficulties that hinder its wide spread in product applications. One is the limited accuracy of the frequency offset detection as the accumulated phase error can always be reset by the injection pulse. The other is the fragile robustness due to its limited lock-in range and weak lock-acquisition

ability. This thesis aims to overcome these two difficulties and hence provides a reliable, low-cost clock multiplier for wireline transceivers.

- Designing a wide-range transmitter that explores the maximum process limit. The direct 4:1 MUX multiplexing scheme has provided a promising solution to satisfy the stringent timing requirement at the final serialization stage. Nonetheless, the doubled self-drain capacitance has limited the maximum bandwidth and hence constrains the overall transmission data rate. Another difficulty in the transmitter design is how to generate the UI-spaced serial sequences for the FFE. This thesis targets to optimize the bandwidth of the 4:1 MUX and develop a quarter-rate transmitter with a multi-MUX-based 4-tap FFE.

- Designing a jitter-performance-improved receiver. Quarter-rate PI-based CDR has become the preferred choice for data rates over 20 Gb/s due to its robustness, portability, and compactness. Nevertheless, its jitter performance is limited by the nonlinearity-caused cycle-limited oscillation and the nonlinearity of the phase interpolation. This thesis seeks to improve the CDR architecture to suppress the deterministic jitter caused by the cycle-limited oscillation while maintaining the loop parameter unchanged to satisfy the JTOL specification. Meanwhile, we make an effort to optimize the linearity of the PI.

- Developing a low-cost adaptive equalization algorithm. Adaptive equalization has become a dominant option for data rates over 20 Gb/s. Previous adaptation algorithms such as sign-sign least mean square (SS-LMS), zero-forcing (ZF), and maximum eye opening (MEO) have manifested their validity. However, the auxiliary circuits associated with these methods have degraded their competitiveness in the cutting-edge transceiver design. This thesis aims to develop a low-cost adaptation algorithm that only uses the existing data/edge information to automatically adjust the tap weights of the TX-FFE.

#### 1.4 Research Contributions

This dissertation explores several advanced techniques to make the data rates of the cutting-edge wireline transceivers approach the fundamental technology limit. It addresses some of the architecture-level and circuit-level challenges with appropriate compromises of power consumption, area occupation, performance margin, and operation robustness. The main contributions of this dissertation are summarized in the following.

- A low-jitter ring-oscillator-based injection-locked clock multiplier (RILCM) is designed in 65-nm CMOS process. It employs a hybrid frequency tracking loop that consists of a traditional phase-locked loop (PLL), a timing-adjusted loop, and a loop selection state-machine to automatically adjust the control voltage of the injection-locked voltage-controlled oscillator (VCO). In the ring-VCO, a full-swing pseudo-differential delay cell is proposed to lower the device noise to phase noise conversion. To satisfy the requirements of high operation speed, high detection accuracy, and low output disturbance, a compact timing-adjusted phase detector tightly combined with a well-matched charge pump is designed. Meanwhile, a lock-loss detection and lock recovery is devised to endow the RIL-CM with a similar lock-acquisition ability as conventional PLLs, thus excluding the initial frequency setup aid and preventing the potential lock-loss risk. The measurement results show that the implemented RILCM achieves a good balance among jitter performance, area occupation, operation speed, and power efficiency.

- A 5-50 Gb/s quarter-rate transmitter (TX) with a 4-tap feed-forward equalization (FFE) based on multiple-multiplexer (multi-MUX) is designed in 65-nm CMOS technology. To increase the maximum operating speed, a bandwidth enhanced 4:1 MUX with the capability of eliminating charge-sharing effect is proposed. To produce the quarter-rate parallel data streams with appropriate delays, a compact latch array associated with an interleaved-retiming technique is designed. The measurement results indicate that the fabricated transmitter achieves better jitter

performance and power efficiency, even in comparison to the LC-delay-based FFE, mainly because of the proposed high-speed 4:1 MUX and the compact interleaved-latching scheme.

- A 40 Gb/s receiver (RX) with excellent performance on both jitter suppression and jitter tracking is implemented in 65-nm CMOS process. Passive low-pass filters with adaptively adjusted bandwidth are introduced into the data-sampling path to automatically balance jitter tracking and jitter suppression for data decisions. Additionally, a time-averaging-based compensating phase interpolator is proposed to not only improve the phase-step uniformity but also reduce the phase-spacing drift between edge and data sampling clocks. The measurement results show that the maximum tolerable amplitude of sinusoidal jitter at high frequency outperforms previous receivers, which is mainly because of the introduced LPFs and the developed compensating PI.

- A chip-to-chip connection over a 12-cm printed circuit board (PCB) channel using the designed transmitter and receiver chips is constructed. The channel loss is compensated by a combination of TX-FFE and RX-CTLE. To obtain the optimal equalization coefficients and track the channel-loss variations with respect to operation environment, a low-cost edge-data correlation-based sign zero-forcing (EDC-SZF) adaptation algorithm is proposed to automatically adjust the TX-FFE's tap weights. The measurement results indicate that the equalization scheme of the combination of TX-FFE and RX-CTLE is a good choice for the equalization of the 16-dB loss channel at 40 Gb/s, and the proposed EDC-SZF adaptation can effectively tune the TX-FFE to its optimal tap weights for a given control voltage applied to the RX-CTLE.

#### 1.5 Organization of the Thesis

This thesis is composed of seven chapters. Chapter 1 outlines the research background, objectives, contributions, and organization of the dissertation. Chapter 2 summarizes the mainstream techniques developed on the high-speed serial links. The main

contributions of this thesis are detailed in Chapters 3, 4, 5 and 6, which present the designed clock multiplier, transmitter chip, receiver chip, and chip-to-chip link, respectively. In each of these four chapters, we discuss the design motivation, describe the prototype implementation, and present the experimental results. Finally, Chapter 7 concludes this thesis and outlooks the possible future work. The details in each chapter are summarized as follows.

Chapter 2 reviews the mainstream techniques that have been developed within the wireline transceiver designs. It begins with a brief discussion on the general design considerations when constructing a serial communication link, including technology selection, link space choice, and on-chip wire modeling. Then, we summarize the major metrics that are used to characterize the overall performance of a serial communication link. Following that, the mainstream techniques of the crucial components within a serial link are discussed in detail, including clock multiplier, transmitter, receiver, and equalizers.

Chapter 3 presents the design of the RILCM. It firstly summarizes the challenges in previous RILCM and then describes the proposed RILCM architecture. Following that, we demonstrate the details of the ring-based voltage-controlled oscillator, the phase-shift detection scheme, and the introduced lock-loss detection and lock recovery. Finally, the experimental results are presented and discussed. This chapter is extended based on the publications [3] on page VI.

Chapter 4 presents the designed transmitter chip. It firstly discusses the two main challenges (i.e., timing constrains and bandwidth limitations) in high-speed transmitter designs, and then presents our transmitter architecture. Following that, the enhancement on the 4:1 multiplex and the clocking techniques are separately illustrated. Finally, the experimental results are demonstrated and discussed. This chapter is an enriched version of the contents published in [1] and [5] on page VI.

Chapter 5 presents the implemented receiver chip, which mainly focuses on the improvement on the clock data recovery (CDR) design. It firstly summarizes the design considerations of the receiver, and then displays the receiver architecture. Following that, we separately describe the improved digital CDR and the linearity-optimized

compensating PI. Finally, the experimental results are presented and discussed. This chapter is extended based on the contents published in [1] and [4] on page VI.

Chapter 6 constructs an overall chip-to-chip communication link utilizing the chips designed in Chapters 4 and 5. It firstly describes the link connection and equalization scheme, and then demonstrates the developed low-cost EDC-SZF adaptation algorithm. After that, we present the experimental setup and the measurement results. The condensed contents of this chapter has been published in [1] on page VI.

Chapter 7 summarizes this dissertation in conclusions and discusses the potential optimization work that can be further done in the future.

## Chapter 2

#### **Literature Review**

High-speed serial links are commonly adopted in chip-to-chip communication applications ranging from handheld electronics to supercomputers. Driven by the exponential growth of the computation ability and storage-volume capability, the throughput bandwidths within the connections among memories, graphics, processors, chassis, racks, and routers [37, 38, 39] have been continuously increased. In practical designs, these bandwidth increases are achieved by either raising the number of data lanes or increasing the data rate per lane [40]. As one of the most important component in such links, serial transceiver needs to provide precise timing information, sufficient bandwidth, and appropriate equalization for the data transmission. These requirements have posed significant challenges in the implementation of wireline transceivers and hence made the design of the wireline transceivers a hot research field [41, 42, 36].

This chapter will review the related works for the wireline transceiver designs. It begins by introducing the general design considerations when constructing a serial chip-to-chip connection in Section 2.1. Section 2.2 then presents the crucial metrics that are usually employed to characterize the performance of a serial link. Following that, the pros and cons of the mainstream techniques within a serial link including clocking techniques, transmitter techniques, receiver techniques, and channel equalizers are detailedly discussed in Section 2.3.

Figure 2.1: Cutoff frequency  $(f_T)$  scaling comparison among different processes in terms of the inverse of the lithographic feature size [3].

#### 2.1 General Design Considerations

#### 2.1.1 Technology Choices