# AN INVESTIGATION OF AN ENERGY DIVERTING CONVERTER FOR HVDC APPLICATIONS

# Jose Manuel Maneiro Barral

A thesis submitted in partial fulfilment of the requirement of Staffordshire University for the degree of *Doctor of Philosophy*

March 2019

To Paul, Clara, Marta and Stéphanie. You are the light that brightens my days and keeps me going.

Ama, aita, porque sin vuestro cariño y apoyo nunca habría llegado hasta aquí.

## Declaration

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other University. This dissertation is the result of my own work and includes nothing which is the outcome of work done in collaboration, except where specifically indicated in the text.

> Jose Manuel Maneiro Barral March 2019

## Abstract

Wind power generation in Europe has experienced an unprecedented expansion fuelled by a very favourable regulatory framework promoted to fight climate change. It is currently the second largest power generation source accounting for 17% of the total energy mix and in 2016 it covered an impressive 10.4% of the total energy demand. With faster wind speeds and better availability, offshore wind farm developments have also experienced a surge in recent years. There are 12.7 GW of cumulative installed capacity with the hot spot located in the North Sea.

The grid integration of offshore wind farms has evolved to meet the requirements of recent projects, much larger in power capacity and located farther offshore. High voltage direct current (HVDC) connections using state of the art multilevel voltage source converters are now the industry standard for distant wind farms, with transmission capacities of up to 1 GW. The scale of the projects and frequent grid weakness at the onshore locations challenge transmission system operators which need to ensure the entire grid stability. Grid codes have evolved to regulate such interconnections, with a set of well specified requirements which need to be fulfilled. One such requirement is the fault ride-through capability, which defines the need for the HVDC interconnector to remain connected during onshore grid faults.

A Dynamic Braking System (DBS) is a power electronics device that provides fault ride-through capability to the HVDC interconnector by absorbing the excess energy injected to the link for the duration of the fault. This energy is commonly dissipated in a resistive element. In this way the DC over-voltage is avoided and the operation of the connected wind farms is kept undisturbed. There is a lack of knowledge in the design and implementation of such devices. Therefore four concepts put forward by industry and other researchers are studied in this work. The rating of the different components in each circuit is investigated as the basis for the comparison.

Taking into account the modular structure of AC/DC converters in HVDC stations it makes commercial sense to reuse the same modules as building blocks for the DBS. With modular structures, a good balancing of the total energy stored in the converter and its distribution among the different modules is one of the key elements. Modular DBS circuits can synthesize multilevel voltage waveforms,

allowing for advanced power modulation strategies. Two novel strategies are developed in the thesis and an accurate mathematical modelling is performed to ensure that the energy balance conditions are met for all points of operation. An overall control strategy for each of the four circuits is also developed and presented in the thesis.

A good coordination of the protective actions of the DBS and the main HVDC converters is important to ensure that no negative interactions occur. An operation strategy based on over-voltage thresholds is developed in the thesis. Accurate simulation models of the HVDC link integrating the DBS and controls are also implemented to give the required degree of confidence in the overall system behaviour. These are finally validated by a laboratory scaled-down test platform, where the control actions and the different converters are implemented in real hardware, and the correct coordination of all the elements during a fault event is experimentally tested.

The main drawback of the DBS solution usually highlighted in literature is its cost. The option of adding some extra functionality to better justify the economic investment is explored in this thesis, resulting on a multifunctional circuit named *Energy Diverting Converter (EDC)*. Two proposals including active filtering and HVDC tapping are developed in this thesis, for which two patent applications have been filed.

## Acknowledgements

First and foremost, I would like to express my gratitude to my supervisor, Professor Sarath Tennakoon. This PhD would not have been possible without his guidance, support and help to overcome all the difficulties I found on the way. Secondly, many thanks to Roger Critchley, who guided my first steps in industry as a fantastic manager and ultimately made it possible and encouraged me to undertake this great challenge. My recognition to Carl Barker for the time he dedicated to this work as an industrial advisor and his encouragement to file many patents. This work would not have been possible without the financial support from Alstom and the Engineering and Physical Sciences Research Council (EPSRC).

To the great team in Areva's/Alstom's Research & Technology Centre (ART): Masoud Bazargan and Alan Barlow for having given me the opportunity to join the team in the first place; Will Crookes, excellent engineer who was always there to guide me and teach me; George Russell with his perennial good mood and great lab skills; Amit, Gopal, Guillaume, Tanmay, Jonathan, John and Nathan, for being great friends inside and outside the office; and to the rest of the team which made my whole ART experience an unforgettable one. My gratitude goes equally to all the fantastic people I met in other units with a special thought for Colin Oates, Adrian Lancaster, Bob Whitehouse and Dave Trainer.

The years I spent in Stafford would not have been as enjoyable without all the friends I made along the way: Carlos, Ana, Rita and Luis which for many years were a second family to me. Rui thanks for those coffee breaks, beers and meals, bike rides and hours and hours of discussions. Ketul, my brother from another mother, thanks for having had so much fun together. And to all the rest of the Stafford connection, may the force be with all of you wherever you are. To the other two members of the very select steak night club, Eduardo and Agusti, thanks for the brilliant time we passed during your stay in Stafford and a big thank you to the rest of the people from CITCEA-UPC with whom I had the privilege to discuss, share and exchange during the PhD years and after: Oriol, Monica, Daniel, Adria and many others.

To all the people at SuperGrid Institute who supported (Piotr, Michel) and celebrated with me the final steps of this long journey, many thanks. You are too many to name you one by one! I should not forget to thank all the fantastic admin staff at Staffordshire University, thanks to your help and understanding I have been able to complete this work despite all the personal difficulties.

Finally, to my wife Stéphanie who has suffered more than anybody the sometimes not so easy years but never gave up encouraging me, a big big thank you. Paul, Marta and Clara, our three little stars, you gave me the energy to cross the finish line. And to the rest of the family, thank you all for being there.

# Table of contents

| Τa            | able o             | of cont | ents                                                                | vii |

|---------------|--------------------|---------|---------------------------------------------------------------------|-----|

| $\mathbf{Li}$ | List of figures xi |         |                                                                     |     |

| $\mathbf{Li}$ | st of              | tables  | х                                                                   | vii |

| $\mathbf{Li}$ | st of              | acron   | yms and symbols                                                     | xx  |

| 1             | Intr               | oducti  | on                                                                  | 1   |

|               | 1.1                | Conte   | xt                                                                  | 1   |

|               | 1.2                | Aims a  | and objectives                                                      | 2   |

|               | 1.3                | Organ   | isation of the thesis                                               | 3   |

|               | 1.4                | List of | f publications based on this work                                   | 4   |

|               | 1.5                | Thesis  | contributions                                                       | 5   |

| <b>2</b>      | Rev                | view of | grid integration of offshore wind farms                             | 7   |

|               | 2.1                | Offsho  | re wind generation                                                  | 8   |

|               | 2.2                | Grid i  | ntegration of offshore wind farms                                   | 10  |

|               |                    | 2.2.1   | AC interconnection of offshore wind farms $\ldots \ldots \ldots$    | 10  |

|               |                    | 2.2.2   | DC interconnection of offshore wind farms $\ldots \ldots \ldots$    | 13  |

|               |                    | 2.2.3   | Future developments                                                 | 16  |

|               | 2.3                | Protec  | tion of the HVDC interconnector and the grid code                   | 18  |

|               |                    | 2.3.1   | Behaviour during network faults                                     | 20  |

|               |                    | 2.3.2   | The low voltage fault ride-through (FRT) requirement $\therefore$   | 21  |

|               | 2.4                | Review  | v of over-voltage mitigation methods                                | 23  |

|               |                    | 2.4.1   | Wind farm output power reduction techniques                         | 24  |

|               |                    | 2.4.2   | Dedicated energy dissipation circuits on<br>shore (E) $\ldots$ .    | 28  |

|               |                    | 2.4.3   | Hybrid solutions                                                    | 29  |

|               |                    | 2.4.4   | Conclusions concerning the different methods $\ldots \ldots \ldots$ | 30  |

|               |                    | 2.4.5   | DBS concept generalization: The Energy Diverting Converter          | 32  |

|               | 2.5                | Summ    | ary                                                                 | 33  |

| 3 | The | e Dyna | amic Braking System                                               | <b>3</b> 4 |

|---|-----|--------|-------------------------------------------------------------------|------------|

|   | 3.1 | Gener  | al concepts                                                       | 35         |

|   |     | 3.1.1  | Base quantities for variables expressed in per unit $\ . \ . \ .$ | 35         |

|   |     | 3.1.2  | DBS circuit structure for different HVDC system                   |            |

|   |     |        | configurations                                                    | 35         |

|   |     | 3.1.3  | Braking resistor arrangement                                      | 36         |

|   |     | 3.1.4  | Operation regions for the DBS                                     | 37         |

|   |     | 3.1.5  | Periods and frequencies used to describe the operation of         |            |

|   |     |        | the DBS circuits                                                  | 39         |

|   | 3.2 | The H  | IVDC chopper DBS with lumped resistive element                    | 39         |

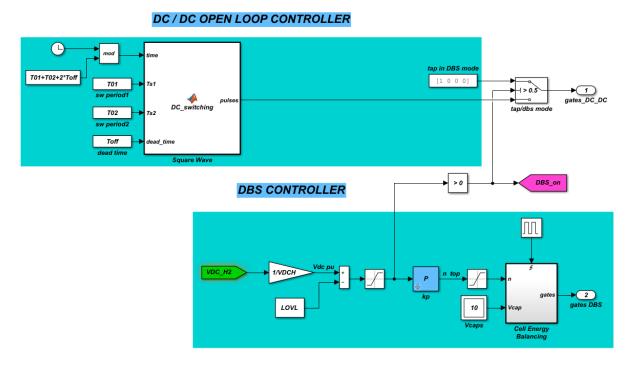

|   |     | 3.2.1  | Control strategy                                                  | 40         |

|   |     | 3.2.2  | Braking resistor value                                            | 41         |

|   | 3.3 | The n  | nultilevel chopper DBS with distributed resistive element         | 42         |

|   |     | 3.3.1  | Control strategy                                                  | 44         |

|   |     | 3.3.2  | Braking resistor value                                            | 46         |

|   |     | 3.3.3  | Cell capacitor sizing                                             | 47         |

|   | 3.4 | The h  | alf-bridge multilevel DBS circuit with lumped resistive element   | 48         |

|   |     | 3.4.1  | Trapezoidal waveforms for power modulation                        | 49         |

|   |     | 3.4.2  | Trapezoidal power modulation with the half-bridge                 |            |

|   |     |        | multilevel DBS                                                    | 51         |

|   |     | 3.4.3  | Controller implementation                                         | 58         |

|   |     | 3.4.4  | Cell capacitor sizing                                             | 61         |

|   | 3.5 | The fu | ull-bridge multilevel DBS circuit with lumped resistive element   | 62         |

|   |     | 3.5.1  | Trapezoidal power modulation with the full-bridge                 |            |

|   |     |        | multilevel DBS                                                    | 64         |

|   |     | 3.5.2  | Controller implementation                                         | 69         |

|   |     | 3.5.3  | Cell capacitor sizing                                             | 73         |

|   |     | 3.5.4  | Alternative cell configuration: the sparse bridge $\ldots$ .      | 73         |

|   | 3.6 | Design | n parameters selection for the half-bridge and full-bridge        |            |

|   |     | multil | evel circuits                                                     | 75         |

|   |     | 3.6.1  | Trade-offs analysis                                               | 78         |

|   | 3.7 | Econo  | omical considerations                                             | 80         |

|   |     | 3.7.1  | Braking resistor                                                  | 80         |

|   |     | 3.7.2  | Semiconductor switches                                            | 81         |

|   |     | 3.7.3  | Cell capacitors                                                   | 82         |

|   | 3.8 | Summ   | hary of the chapter                                               | 83         |

| 4 | Dyr | namic  | Braking Systems: Simulation studies                               | 85         |

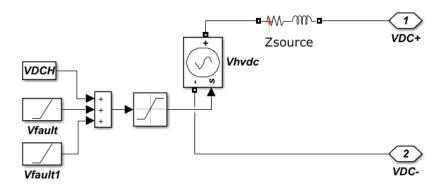

|   | 4.1 |        | l of the HVDC interconnector                                      | 85         |

|   |     | 4.1.1  | VSC station equivalent averaged model                             | 86         |

|   |     | 4.1.2  | HVDC cable equivalent model                                       | 87         |

|   |     |        | *                                                                 |            |

|          |     | 4.1.3  | Full size interconnector scaling down                                                                                                                                        |

|----------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |     | 4.1.4  | Fault ride-through event simulation                                                                                                                                          |

|          | 4.2 | Evalua | ation of the fault ride-through event using DBS $\ldots \ldots \ldots 90$                                                                                                    |

|          |     | 4.2.1  | Onshore AC grid fault                                                                                                                                                        |

|          |     | 4.2.2  | Operation of the HVDC chopper DBS                                                                                                                                            |

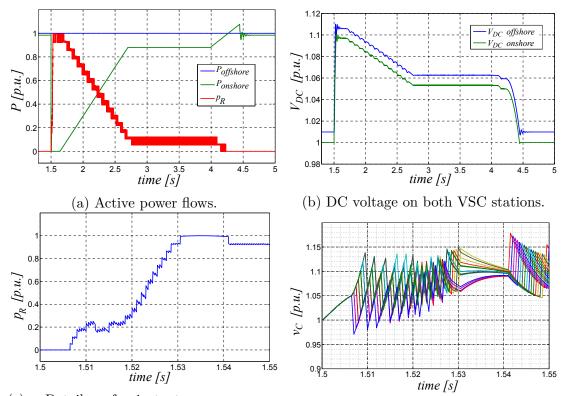

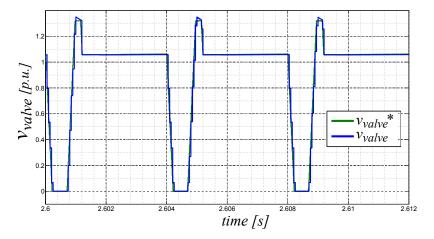

|          |     | 4.2.3  | Operation of the multilevel chopper DBS                                                                                                                                      |

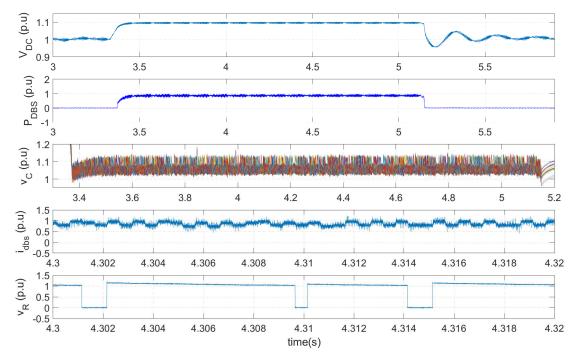

|          |     | 4.2.4  | Operation of the half-bridge DBS                                                                                                                                             |

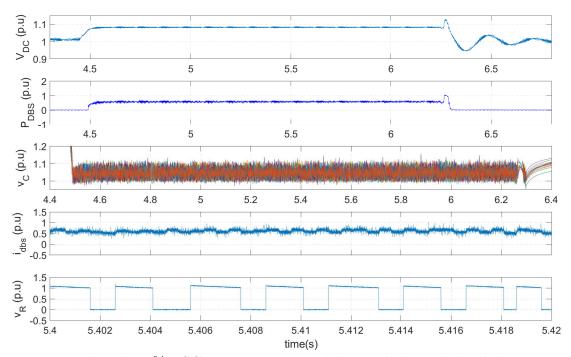

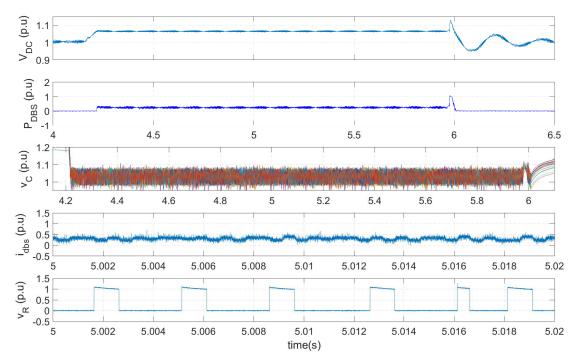

|          |     | 4.2.5  | Operation of the full-bridge multilevel DBS 99                                                                                                                               |

|          | 4.3 | Comp   | arison of the four DBS circuits $\ldots \ldots 104$                               |

|          |     | 4.3.1  | DBS valve voltage $dv/dt$ and current $\ldots \ldots \ldots$ |

|          |     | 4.3.2  | DC voltage during the fault $\ldots \ldots 105$                                                               |

|          |     | 4.3.3  | Number and rating of semiconductor switches $\ldots \ldots \ldots 106$                                                                                                       |

|          |     | 4.3.4  | Cell capacitors $\ldots \ldots 106$                                               |

|          |     | 4.3.5  | Conclusions                                                                                                                                                                  |

|          | 4.4 | Summ   | ary of the chapter $\ldots \ldots \ldots$                    |

| <b>5</b> | Exp | erime  | ntal test platform 111                                                                                                                                                       |

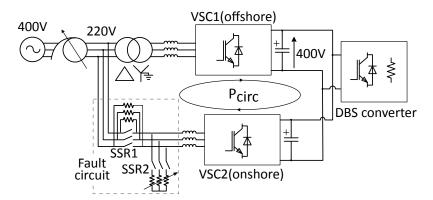

|          | 5.1 | Scaled | l-down VSC-HVDC system                                                                                                                                                       |

|          |     | 5.1.1  | Isolation transformer $\ldots \ldots 113$                                                       |

|          |     | 5.1.2  | DC link pre-charge circuit                                                                                                                                                   |

|          |     | 5.1.3  | Fault emulation circuit                                                                                                                                                      |

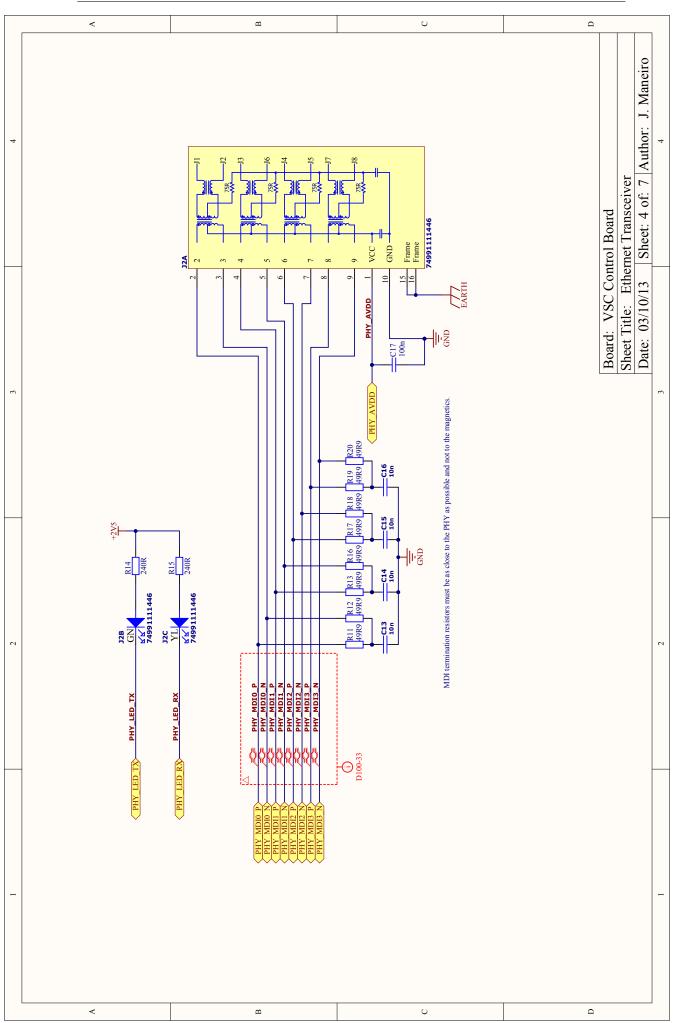

|          |     | 5.1.4  | Voltage source converter modules                                                                                                                                             |

|          |     | 5.1.5  | Braking resistors                                                                                                                                                            |

|          |     | 5.1.6  | DC voltage supplies                                                                                                                                                          |

|          |     | 5.1.7  | Fault triggering mechanism                                                                                                                                                   |

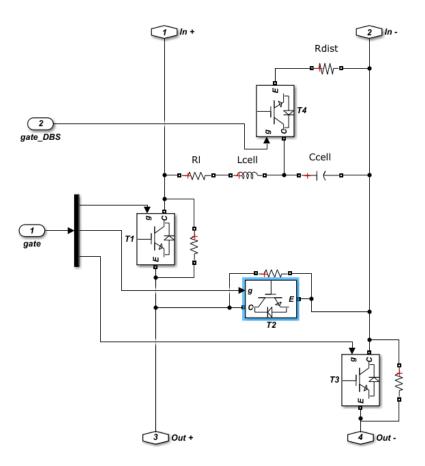

|          | 5.2 | Recon  | figurable DBS power cells                                                                                                                                                    |

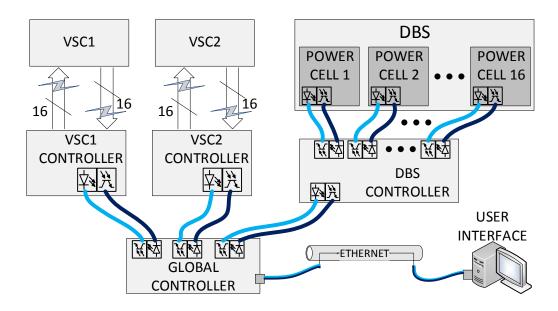

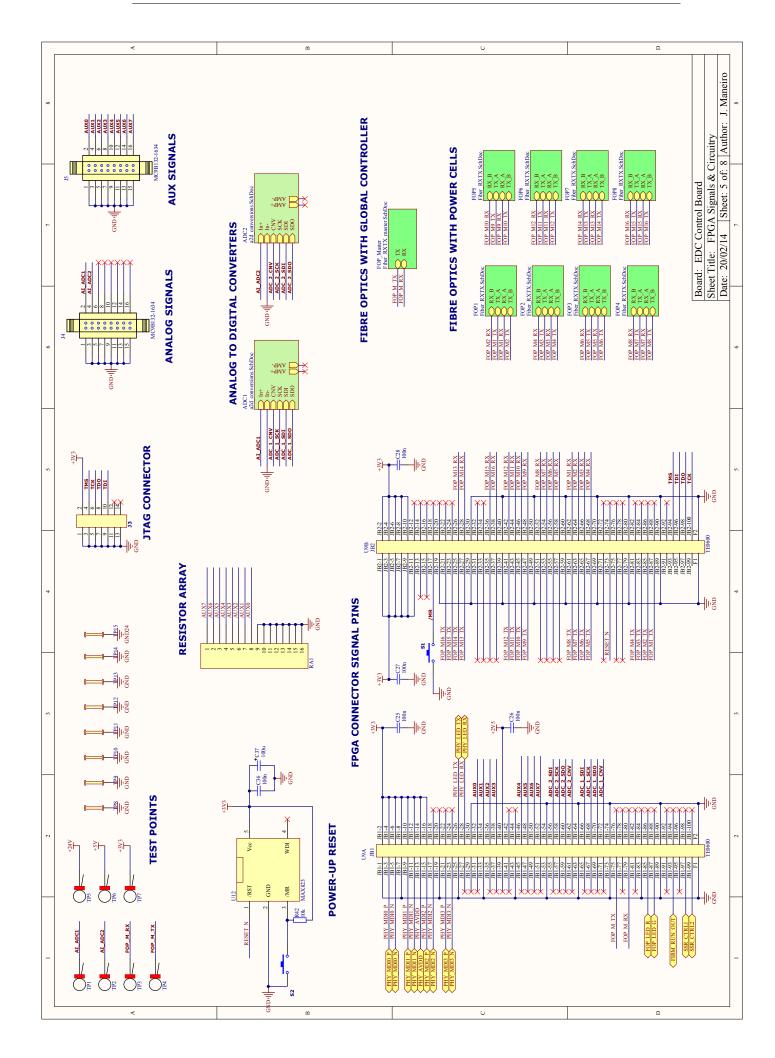

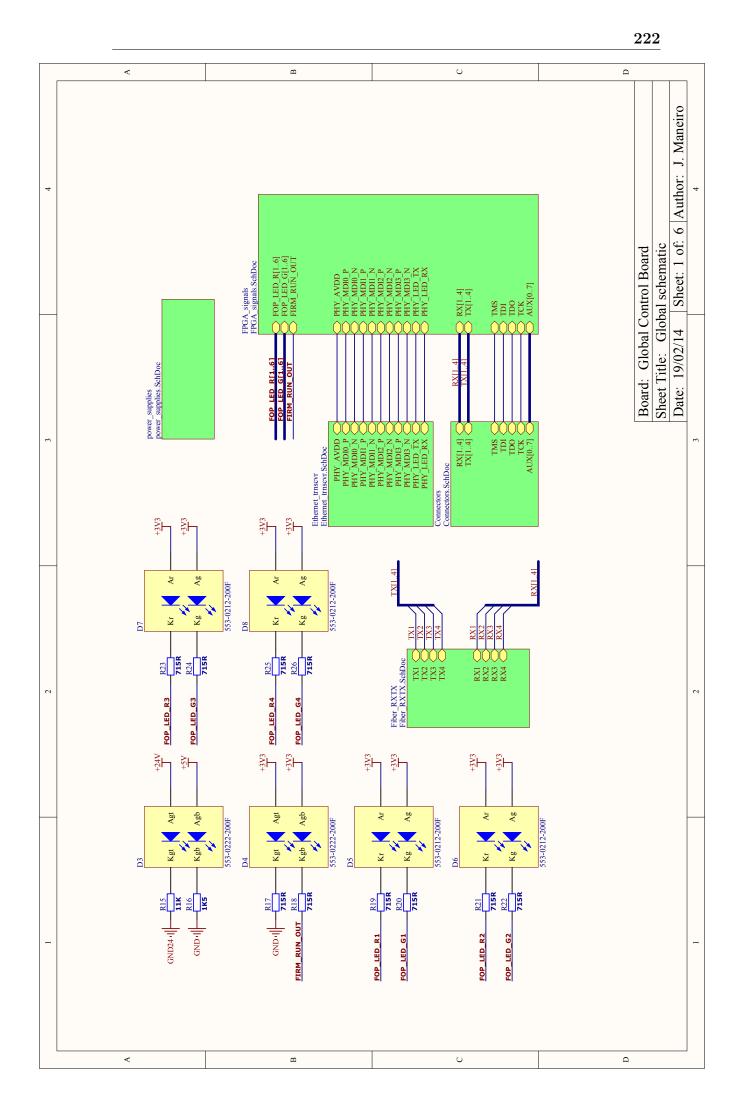

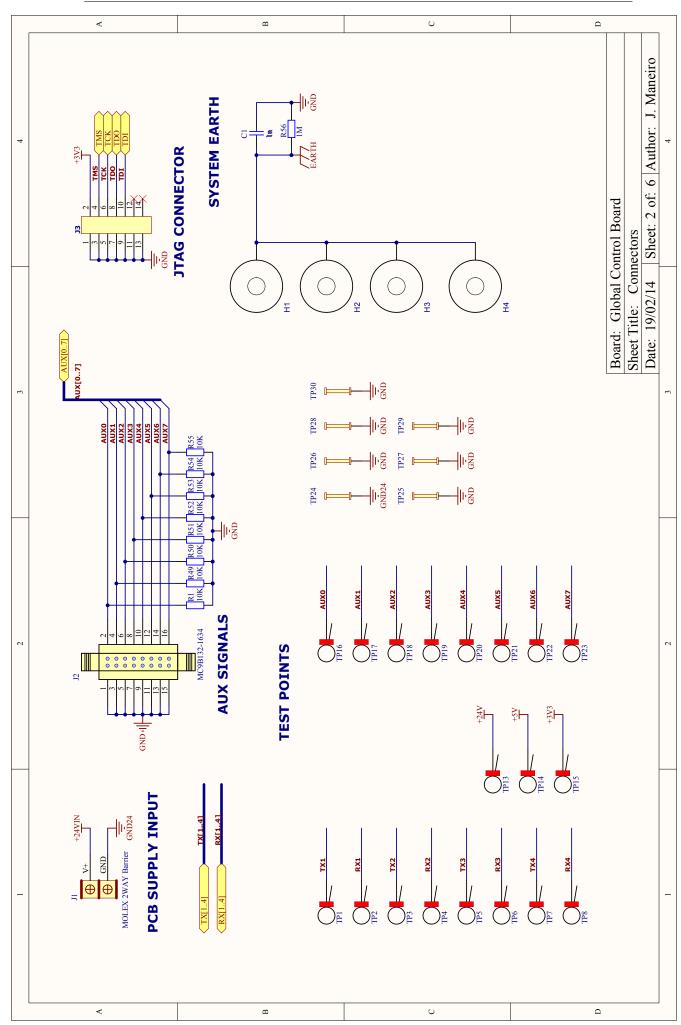

|          | 5.3 | Contr  | ol boards and user interface                                                                                                                                                 |

|          |     | 5.3.1  | Control boards                                                                                                                                                               |

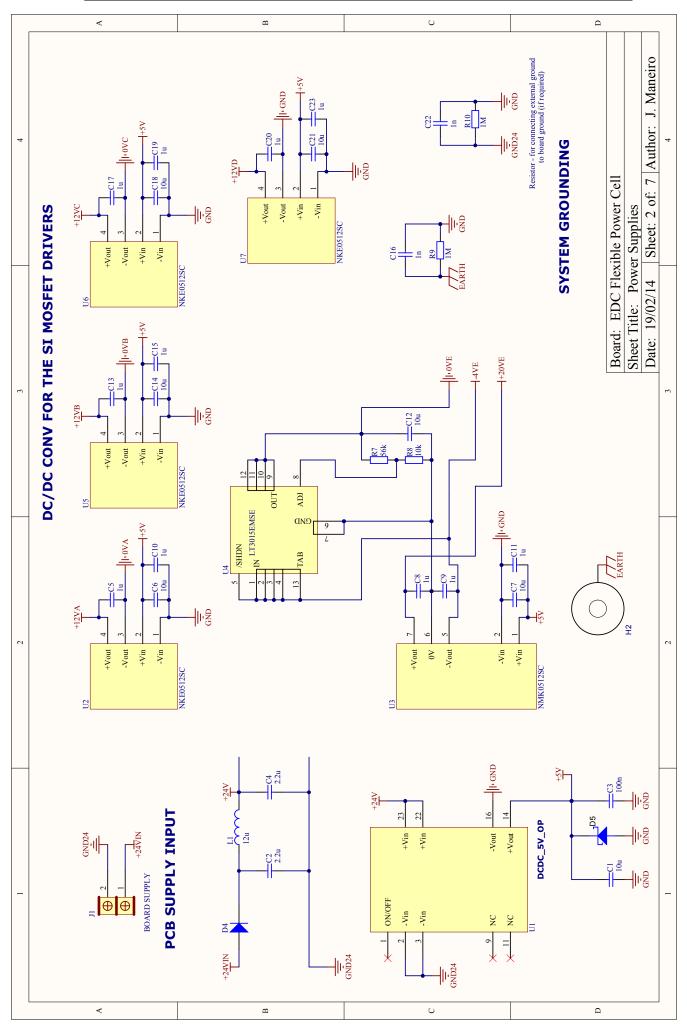

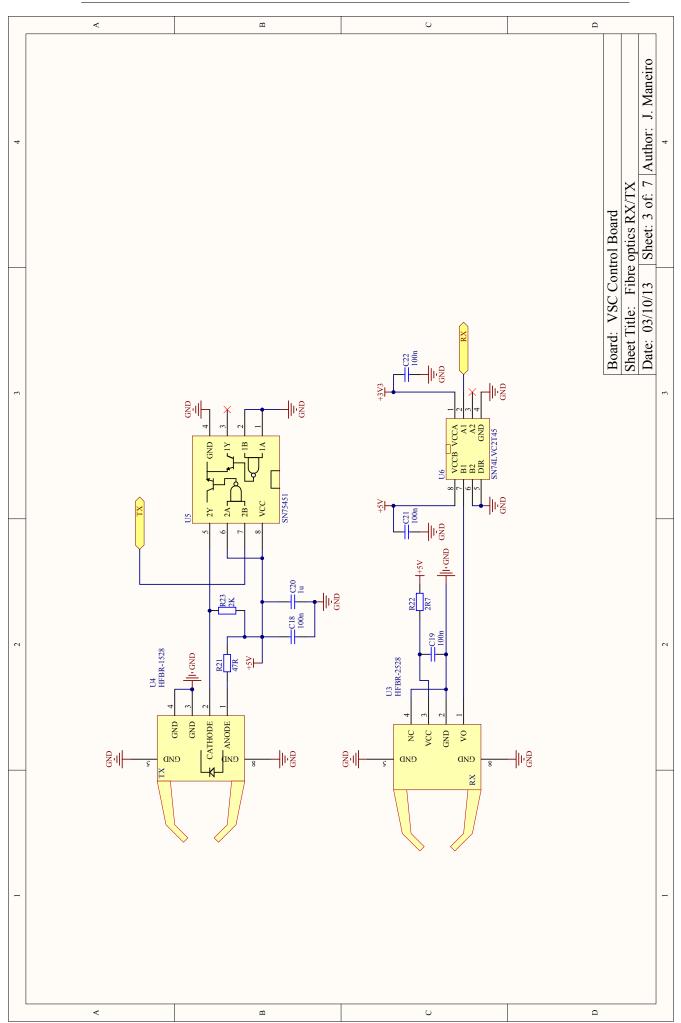

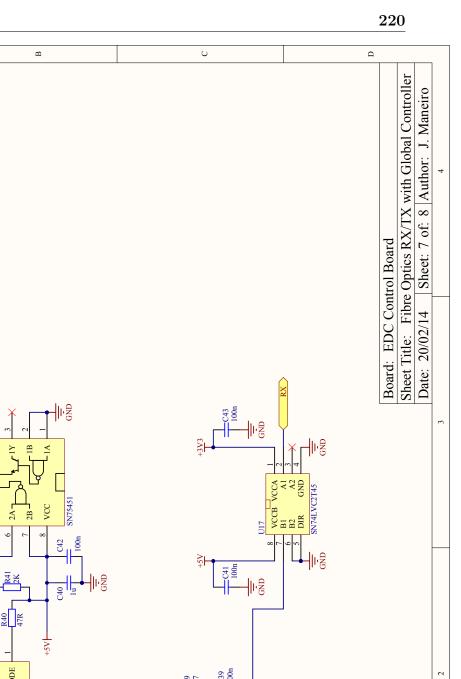

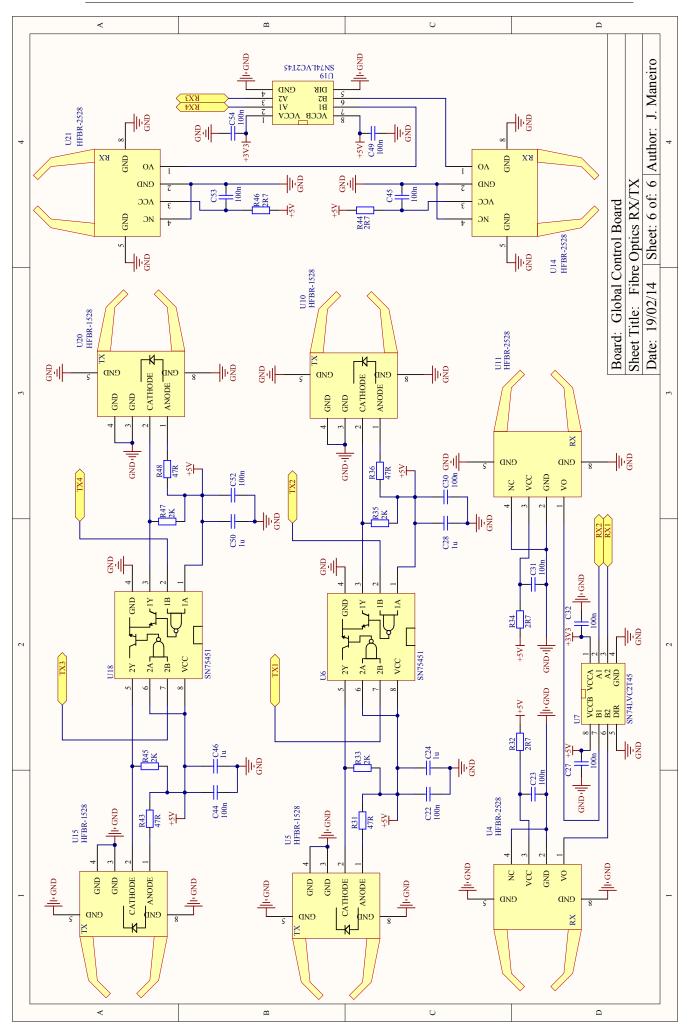

|          |     | 5.3.2  | Communication network                                                                                                                                                        |

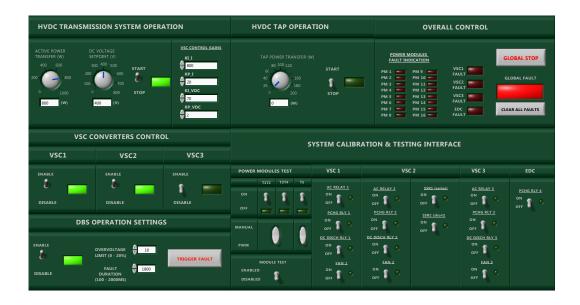

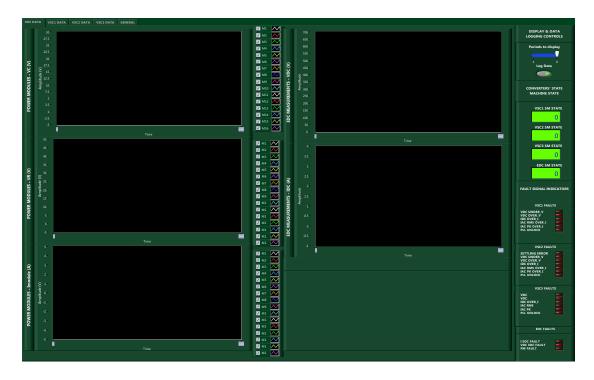

|          |     | 5.3.3  | User interface $\ldots \ldots 125$                                                       |

|          | 5.4 | Summ   | ary of the chapter $\ldots \ldots 129$                                            |

| 6        | Exp | erime  | ntal evaluation of DBS circuits 131                                                                                                                                          |

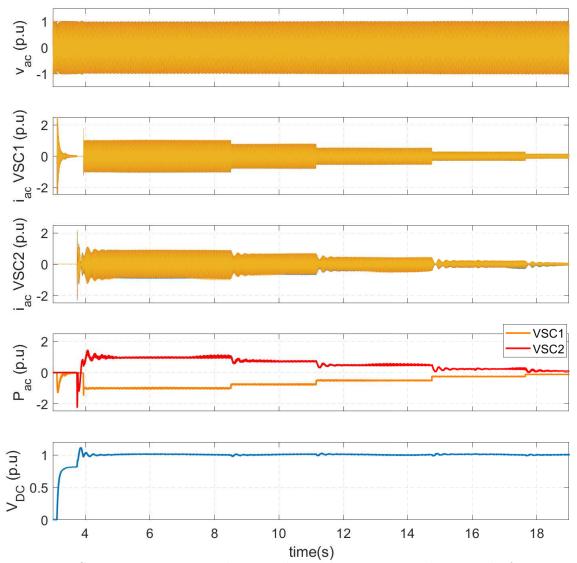

|          | 6.1 | Test p | latform configuration for the tests                                                                                                                                          |

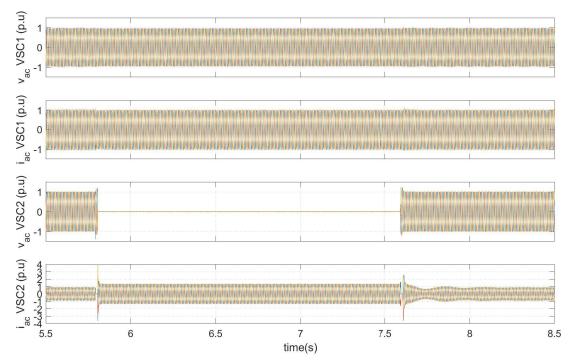

|          |     | 6.1.1  | Malfunction during operation of the fault triggering circuit                                                                                                                 |

|          |     |        | affecting VSC2 $\ldots$ 136                                                                                                                                                  |

|          | 6.2 | Evalua | ation of the HVDC chopper circuit: $DBS#1 \dots 139$                                                                                                                         |

|          | 6.3 | Evalua | ation of the multilevel chopper circuit: $DBS#2 \dots 142$                                                                                                                   |

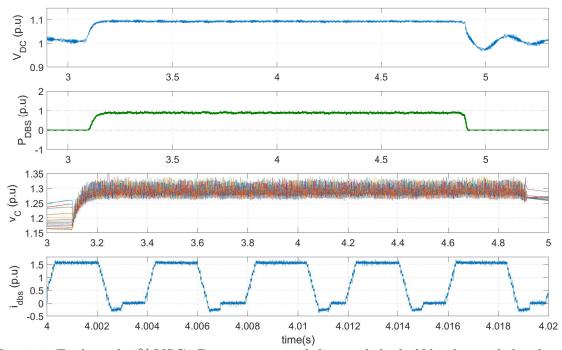

|          | 6.4 | Evalua | ation of the half-bridge multilevel circuit: DBS#3 145                                                                                                                       |

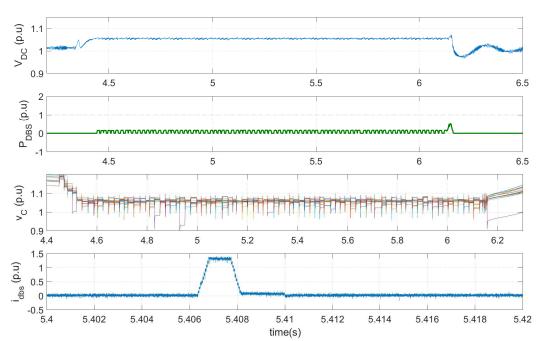

|          | 6.5 | Evalua | ation of the full-bridge multilevel circuit: $DBS#4 \dots 149$                                                                                                               |

|          | 6.6 | Summ   | ary of the chapter $\ldots \ldots 153$                                                   |

| <b>7</b>                  | An    | An Energy Diverting Converter: added functionality to the DBS                                             |     |  |  |

|---------------------------|-------|-----------------------------------------------------------------------------------------------------------|-----|--|--|

|                           | circ  | uit                                                                                                       | 154 |  |  |

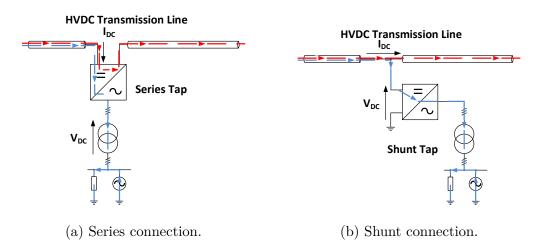

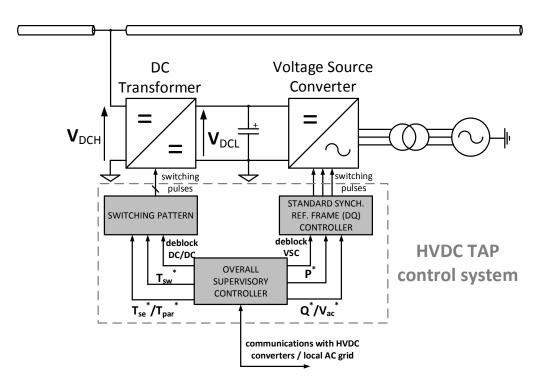

|                           | 7.1   | HVDC tapping $\ldots \ldots \ldots$ | 154 |  |  |

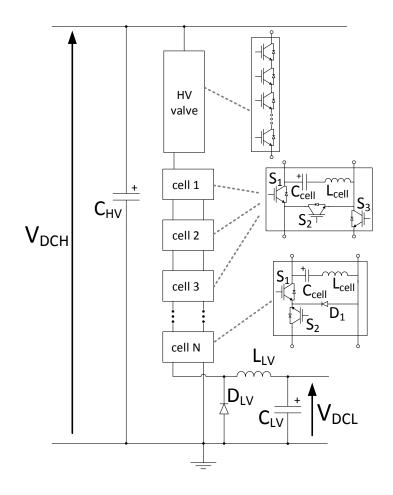

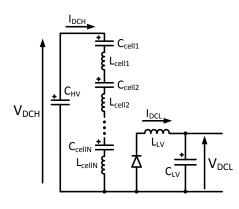

|                           |       | 7.1.1 The cascaded resonant DC transformer circuit                                                        | 156 |  |  |

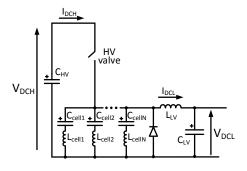

|                           | 7.2   | The HVDC tap with dynamic braking capability                                                              | 170 |  |  |

|                           |       | 7.2.1 The modified cascaded resonant DC transformer circuit                                               | 172 |  |  |

|                           | 7.3   | Summary of the chapter                                                                                    | 174 |  |  |

| 8                         | Con   | clusions and recommendations for further work                                                             | 177 |  |  |

|                           | 8.1   | Conclusions                                                                                               | 177 |  |  |

|                           | 8.2   | Recommendations for further work                                                                          | 179 |  |  |

| Re                        | efere | nces                                                                                                      | 181 |  |  |

| $\mathbf{A}$              | ppen  | dix A Derivations for the modulation strategy in half and                                                 | ł   |  |  |

|                           | full  | bridge DBS circuits                                                                                       | 190 |  |  |

|                           | A.1   | Expressions for full power dissipation with half-bridge circuit                                           | 190 |  |  |

|                           | A.2   | Expressions for amplitude modulation with half-bridge circuit $~$ .                                       | 193 |  |  |

|                           | A.3   | Expressions for full power dissipation with full-bridge circuit                                           | 196 |  |  |

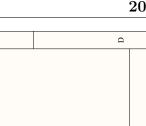

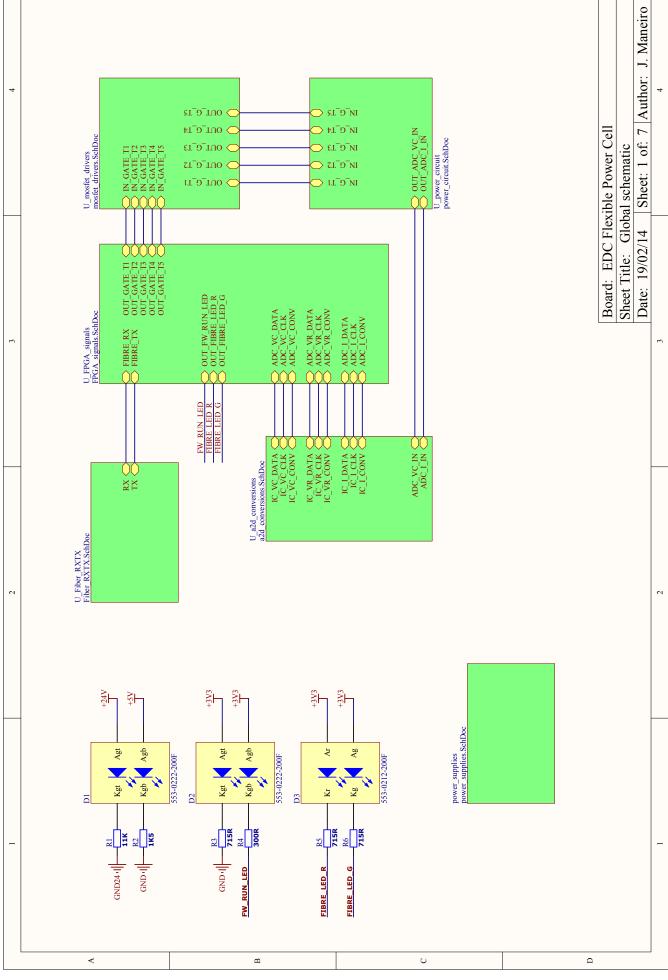

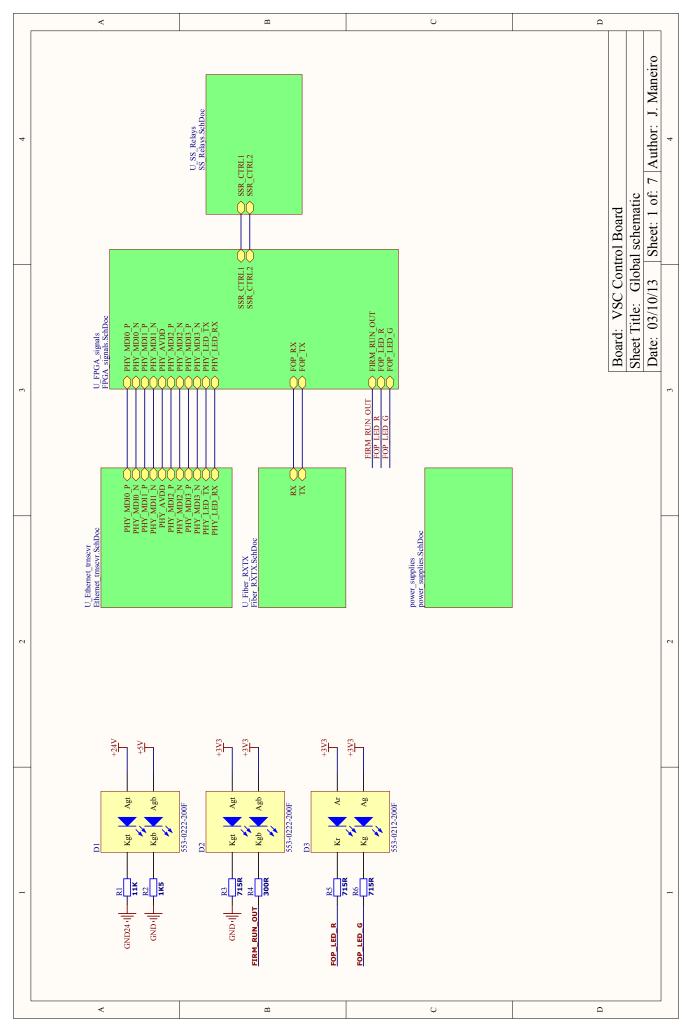

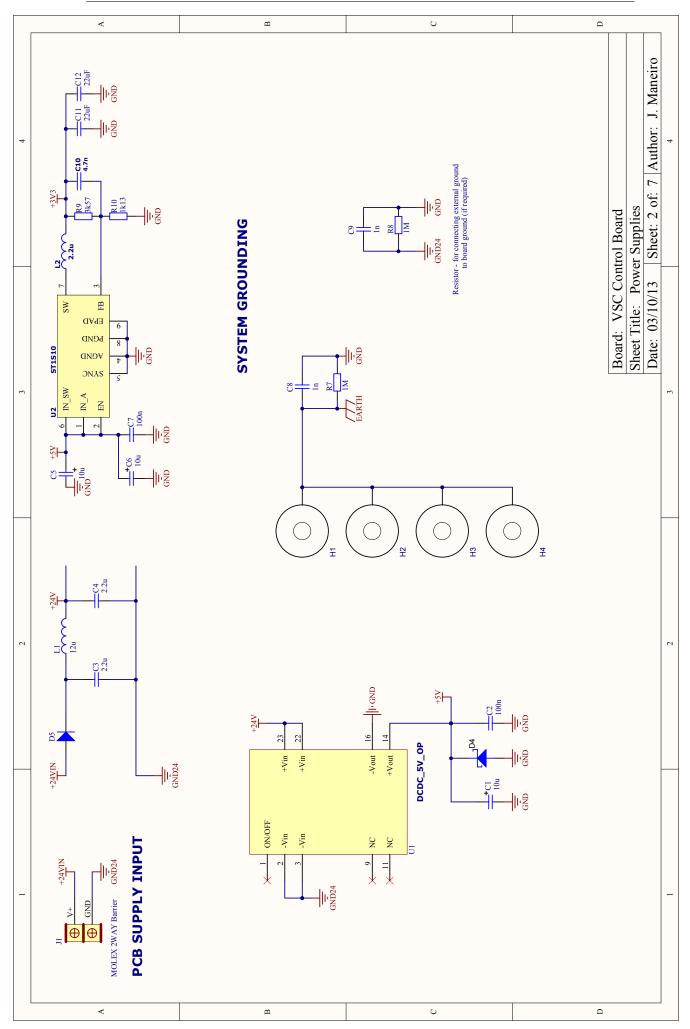

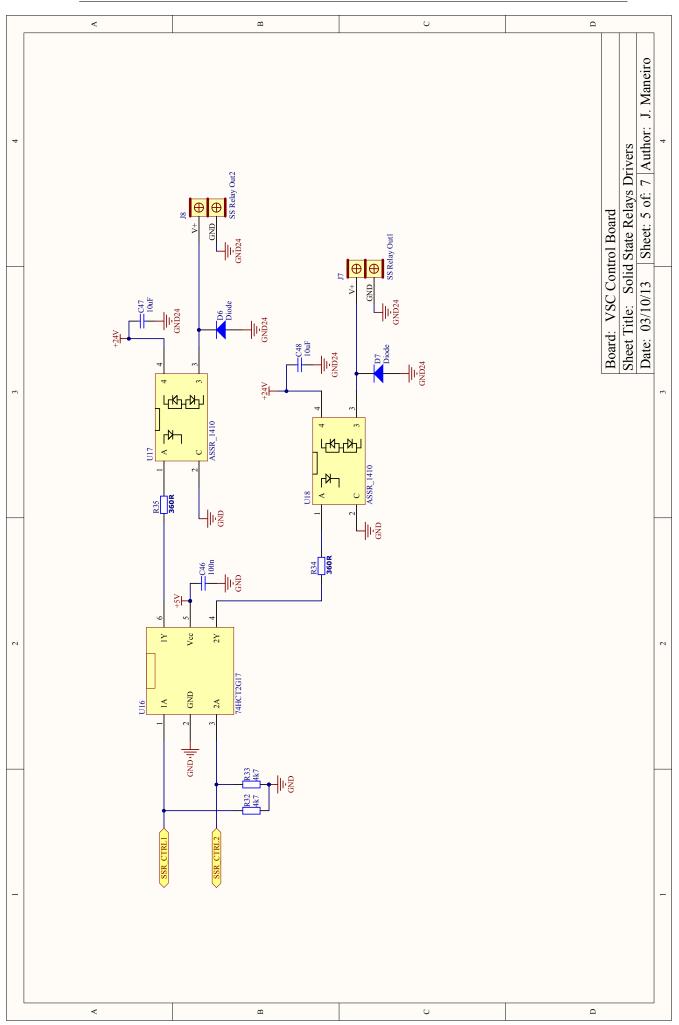

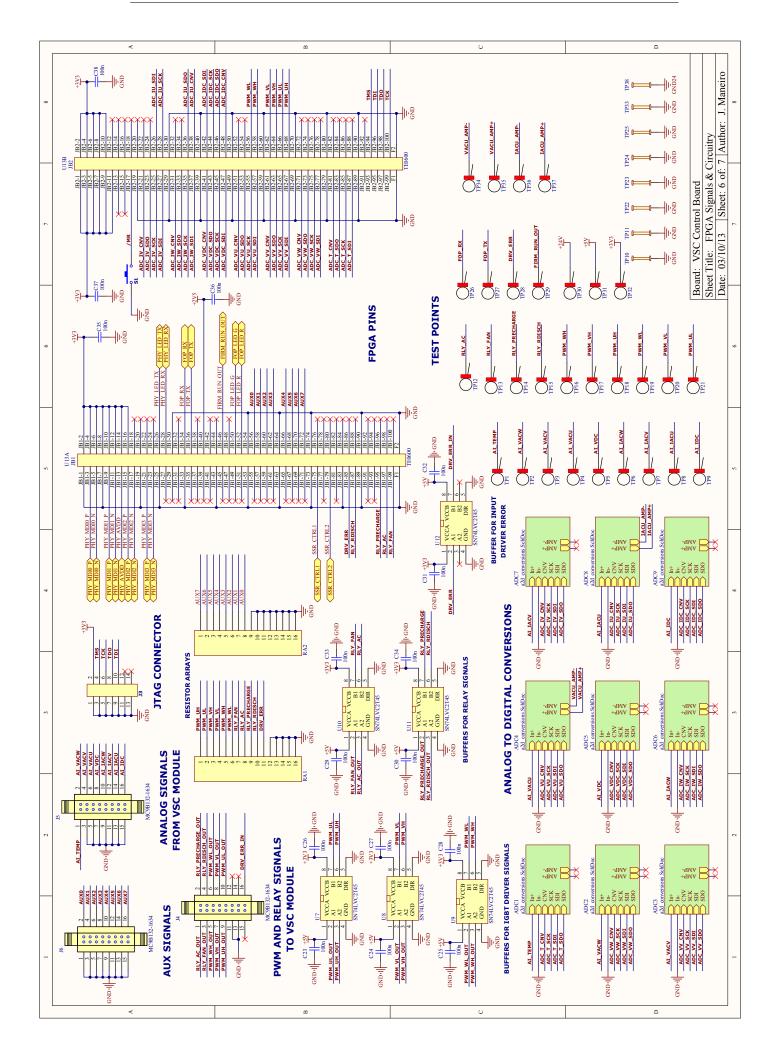

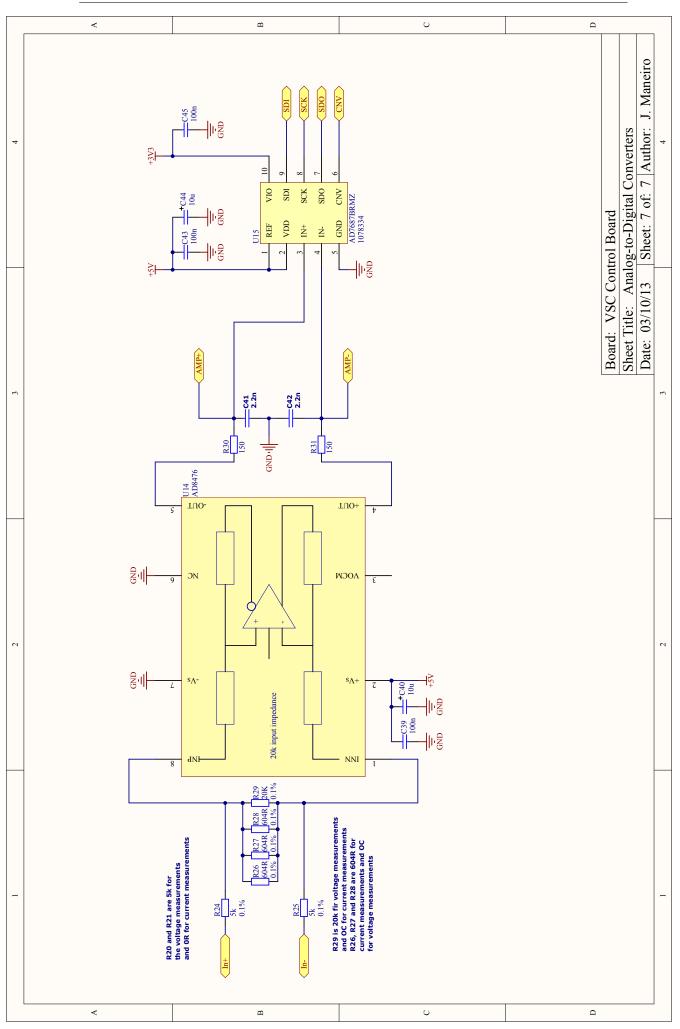

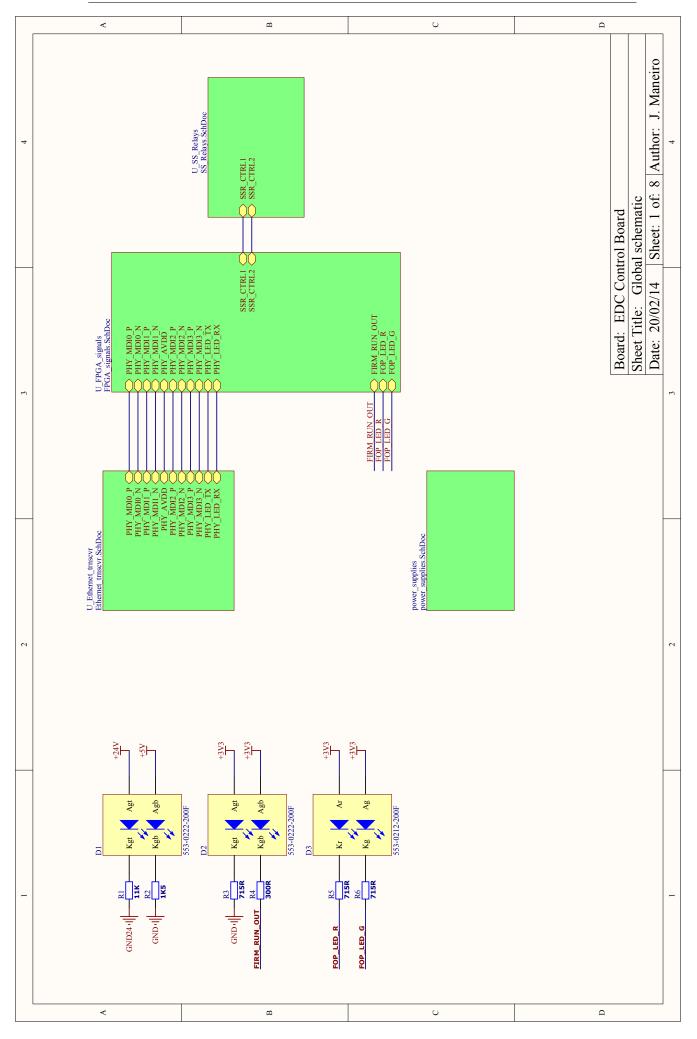

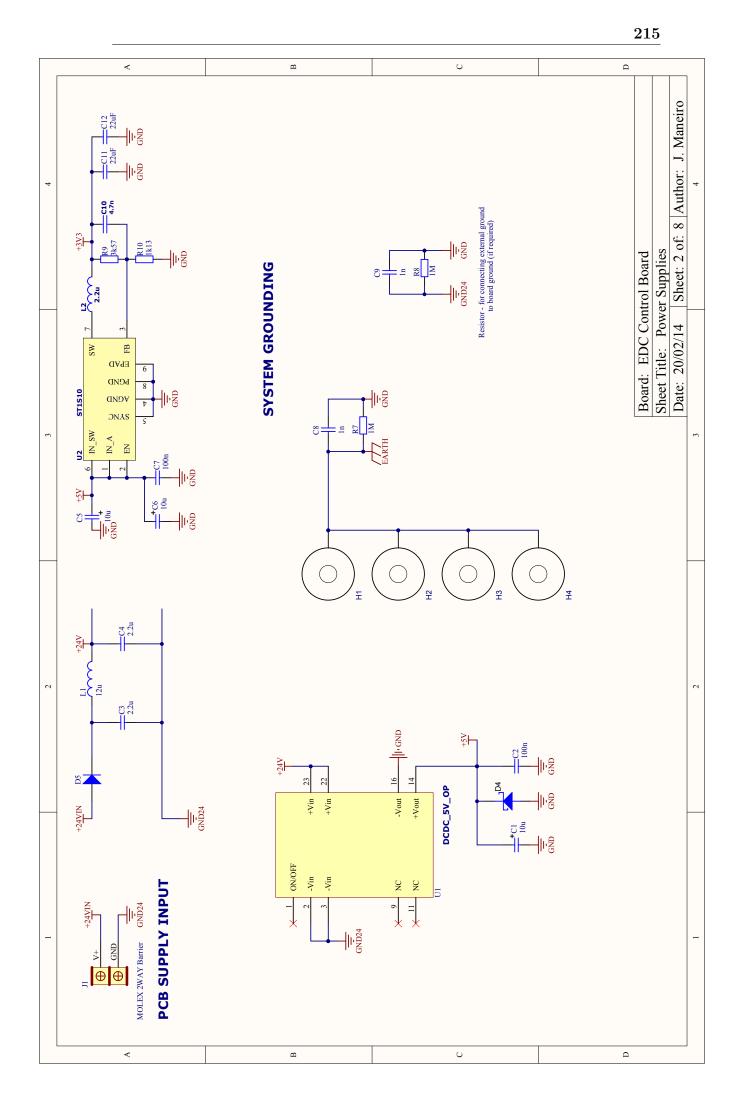

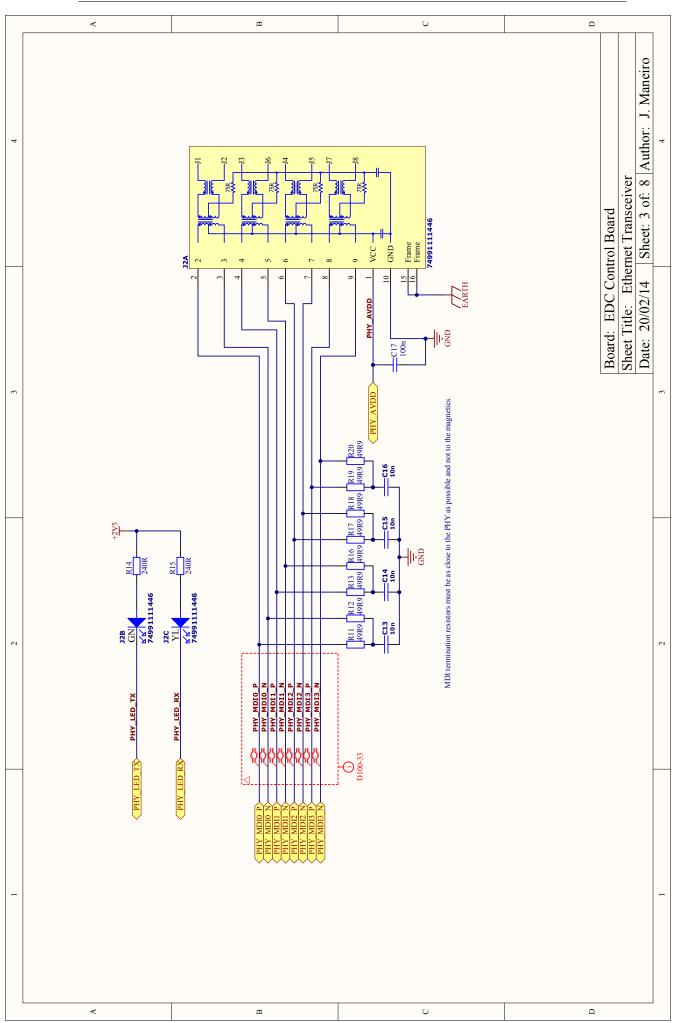

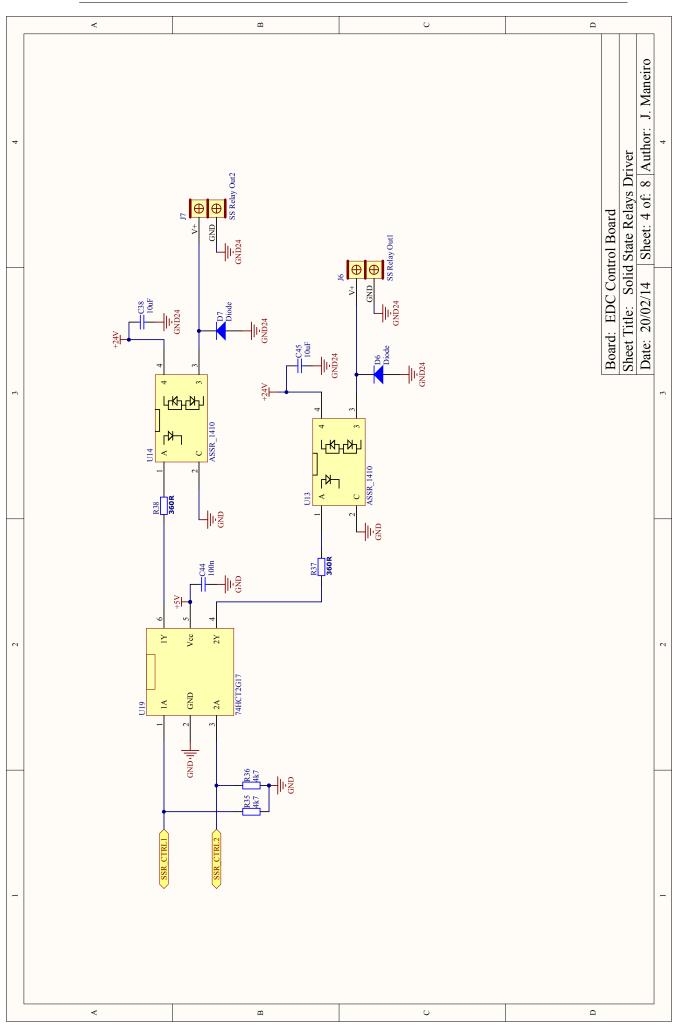

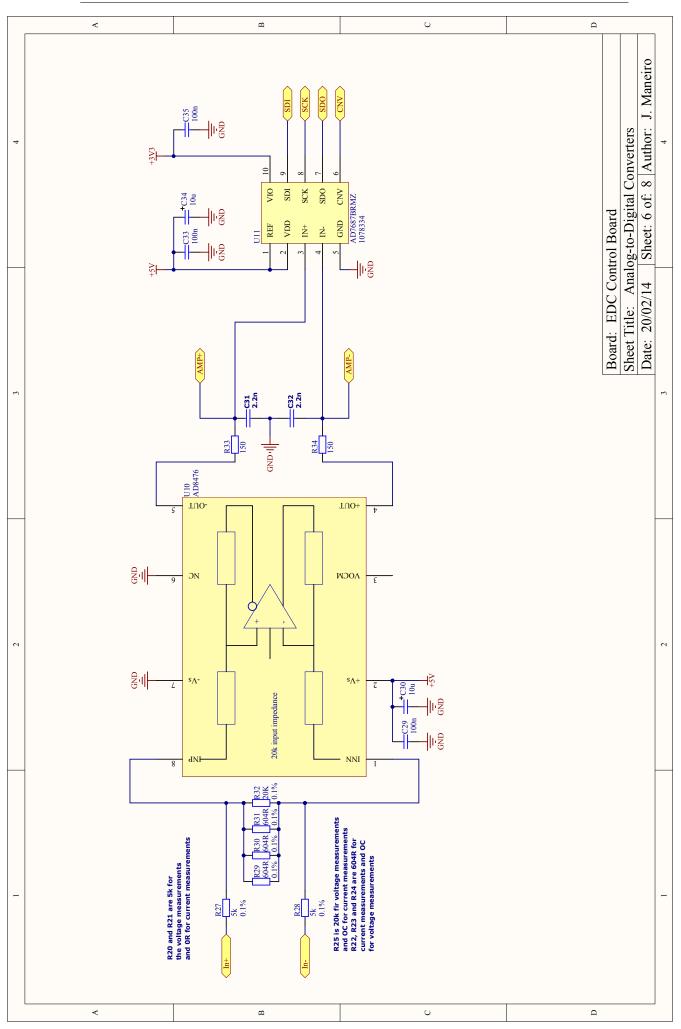

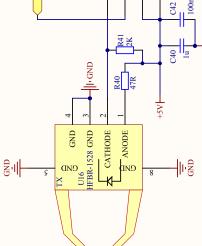

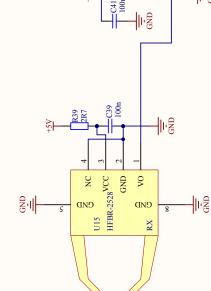

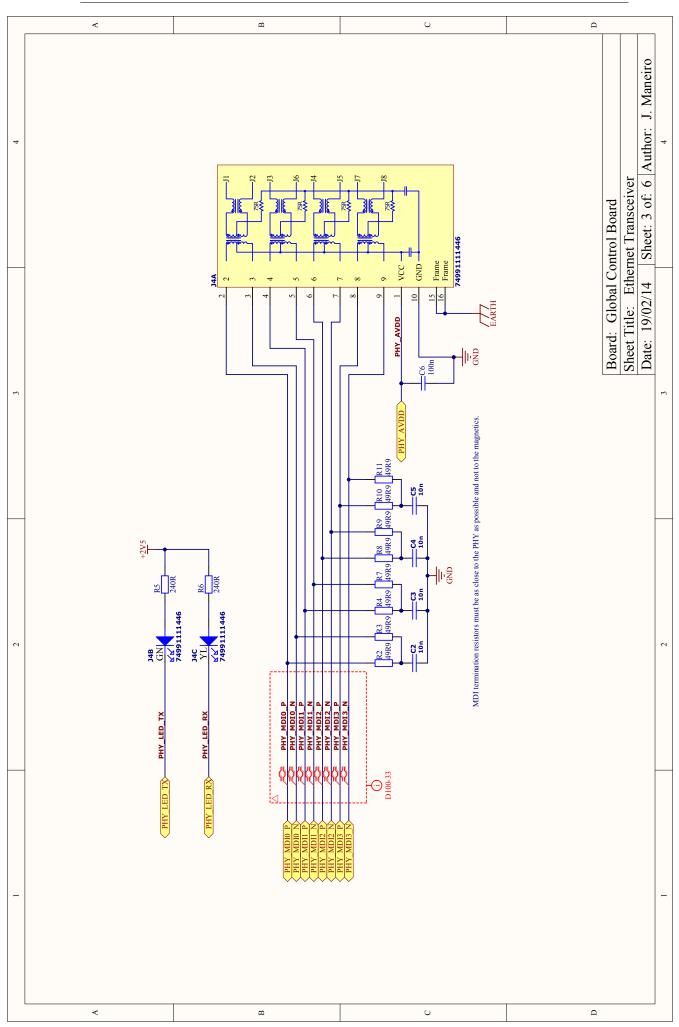

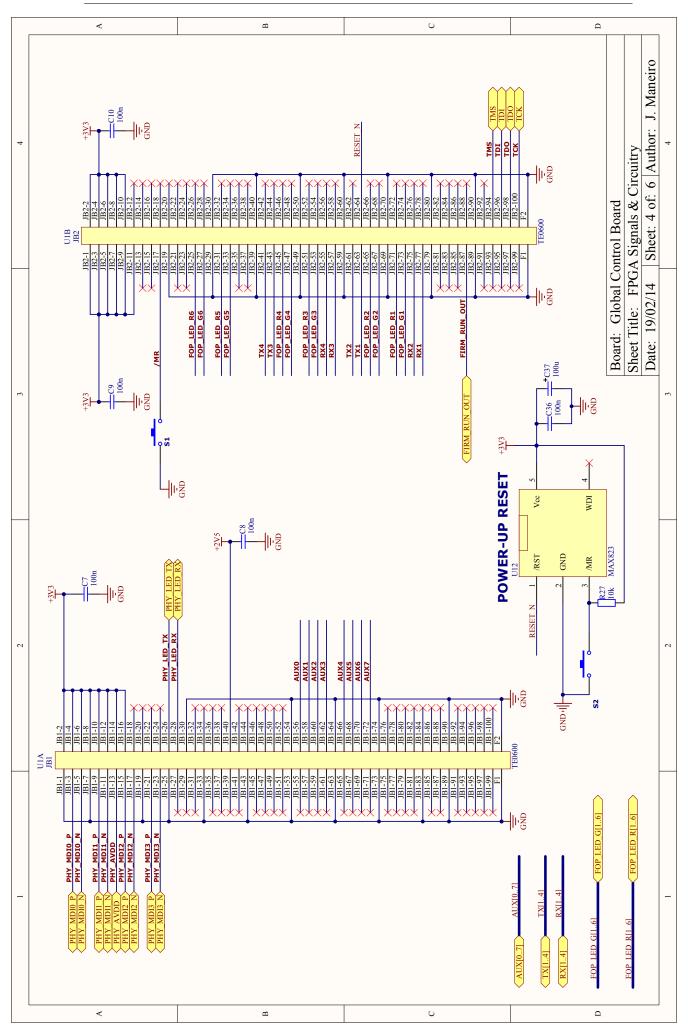

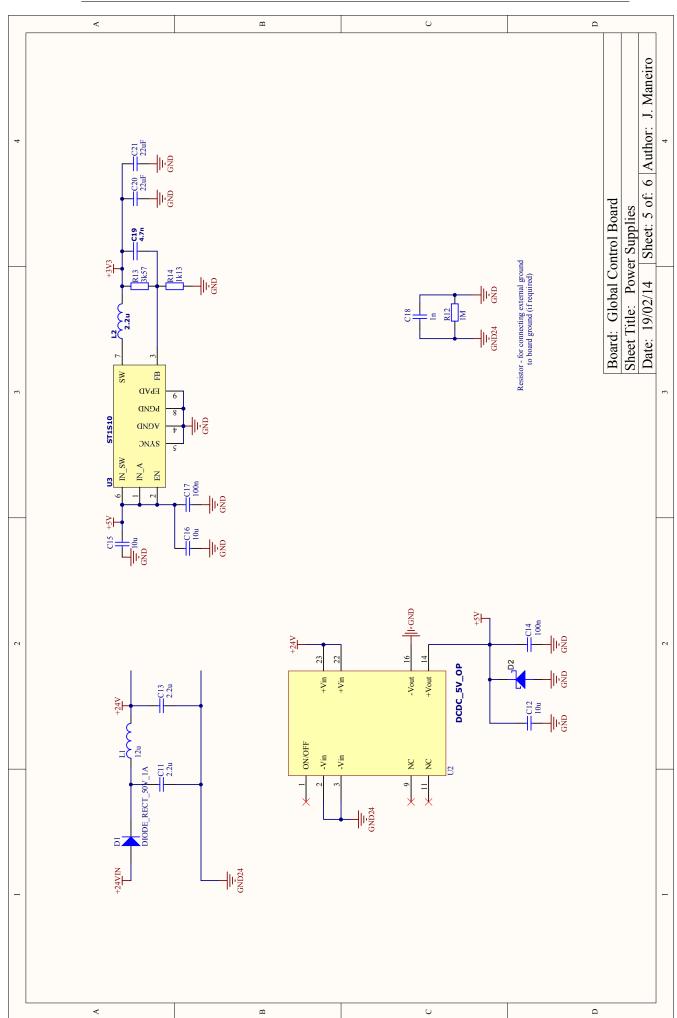

| $\mathbf{A}_{\mathbf{j}}$ | ppen  | dix B Laboratory test platform PCB schematics                                                             | 199 |  |  |

| $\mathbf{A}_{]}$          | ppen  | dix C Laboratory test platform data packets fo                                                            | r   |  |  |

|                           | com   | munications                                                                                               | 228 |  |  |

| $\mathbf{A}$              | ppen  | dix D Simulation models                                                                                   | 237 |  |  |

|                           | D.1   | DBS circuit simulations from Chapter 4                                                                    | 237 |  |  |

|                           |       | D.1.1 General HVDC interconnector                                                                         | 237 |  |  |

|                           |       | D.1.2 HVDC chopper DBS circuit (DBS#1) $\ldots \ldots \ldots$                                             | 240 |  |  |

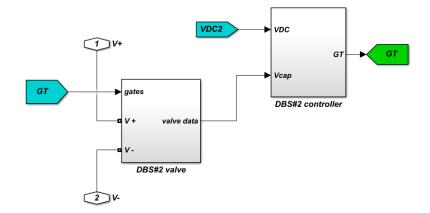

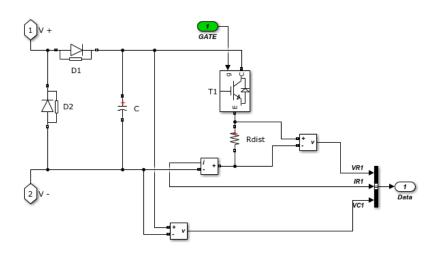

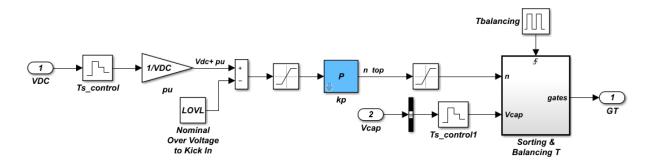

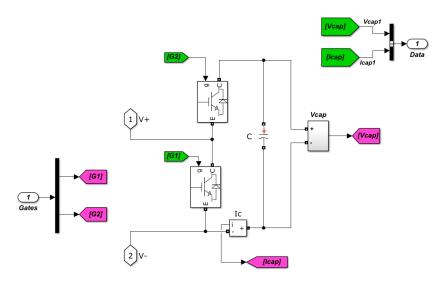

|                           |       | D.1.3 Multilevel chopper DBS circuit (DBS#2)                                                              | 241 |  |  |

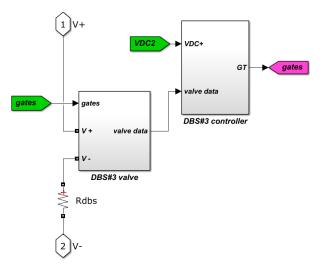

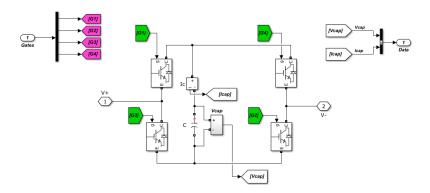

|                           |       | D.1.4 Half-bridge multilevel DBS circuit (DBS#3) $\ldots \ldots$                                          | 242 |  |  |

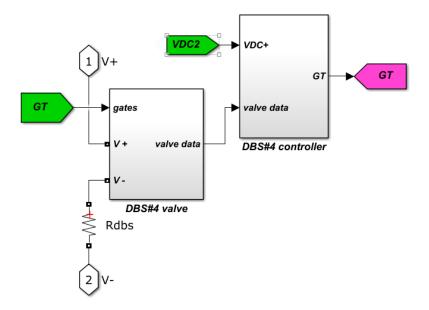

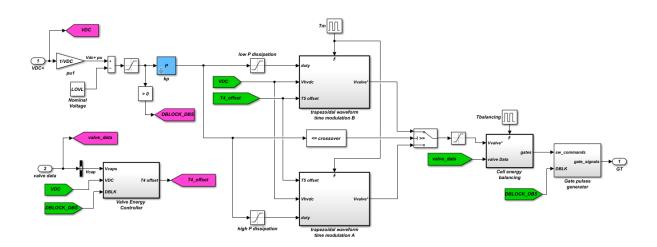

|                           |       | D.1.5 Full-bridge multilevel DBS circuit (DBS#4) $\ldots \ldots$                                          | 243 |  |  |

|                           | D.2   | HVDC tap circuit simulations from Chapter 7 $\ldots \ldots \ldots$                                        | 244 |  |  |

|                           |       | D.2.1 HVDC tap simulation model                                                                           | 244 |  |  |

|                           |       | D.2.2 HVDC tap integrating DBS functionality simulation from                                              |     |  |  |

|                           |       | Chapter 7                                                                                                 | 246 |  |  |

|                           |       |                                                                                                           |     |  |  |

# List of figures

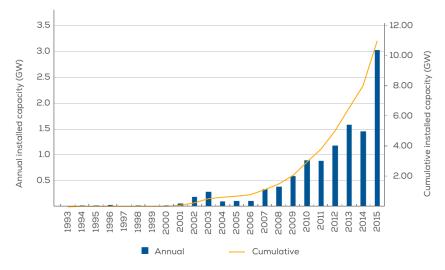

| 2.1  | Evolution of offshore wind power installed capacity in Europe       | 9  |

|------|---------------------------------------------------------------------|----|

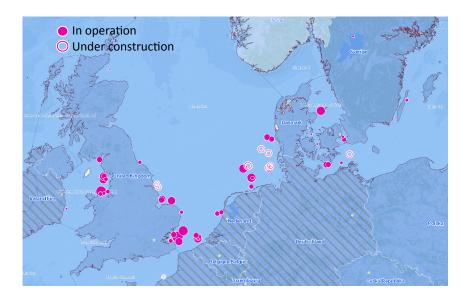

| 2.2  | Offshore wind farms in Europe                                       | 9  |

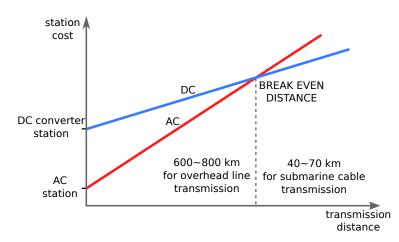

| 2.3  | Break-even distance AC vs DC                                        | 10 |

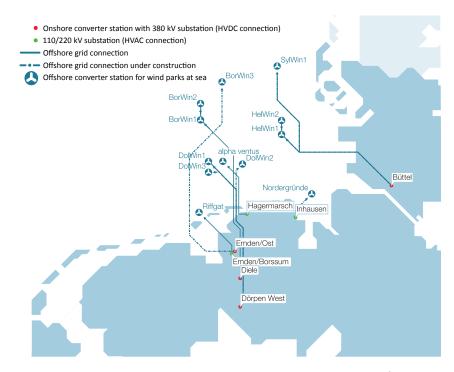

| 2.4  | German offshore interconnection projects by Tennet                  | 11 |

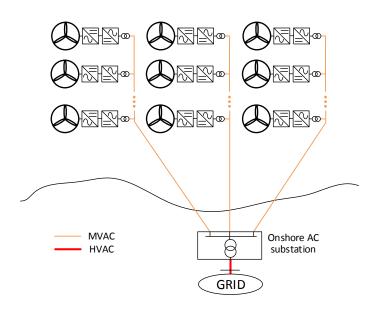

| 2.5  | MVAC interconnection of an OWF                                      | 12 |

| 2.6  | HVAC interconnection of an OWF                                      | 12 |

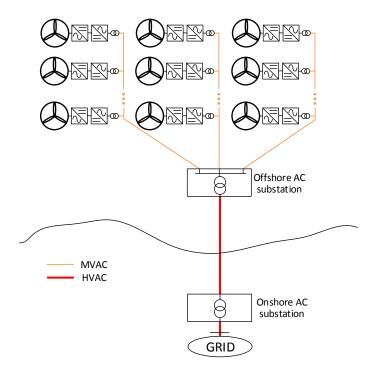

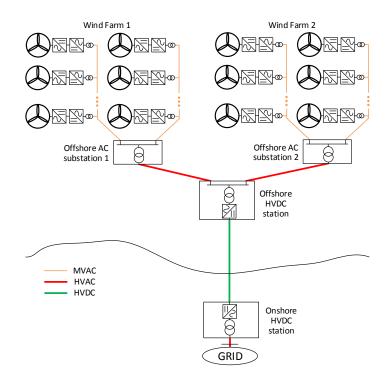

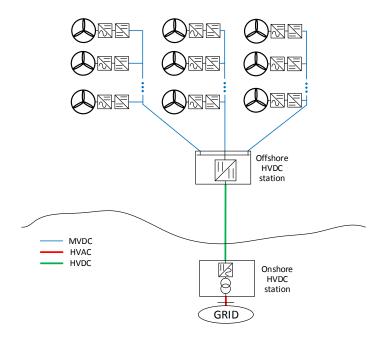

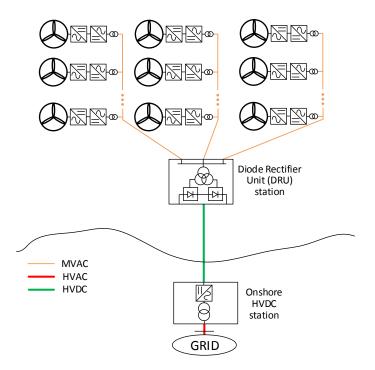

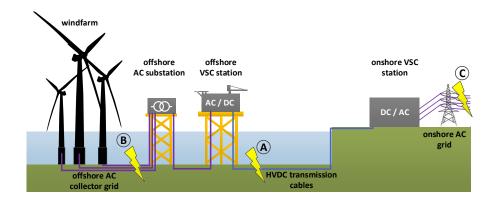

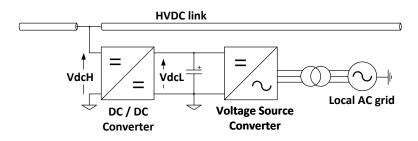

| 2.7  | HVDC interconnection of an OWF                                      | 13 |

| 2.8  | Detail of the state of the art voltage source converter of the type |    |

|      | modular multilevel converter (MMC)                                  | 15 |

| 2.9  | HVDC interconnector using an offshore DC collector grid             | 16 |

| 2.10 | HVDC interconnection using a diode rectifier station offshore       | 17 |

| 2.11 | Possible fault locations in the wind farm HVDC connector            | 20 |

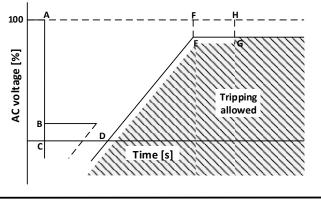

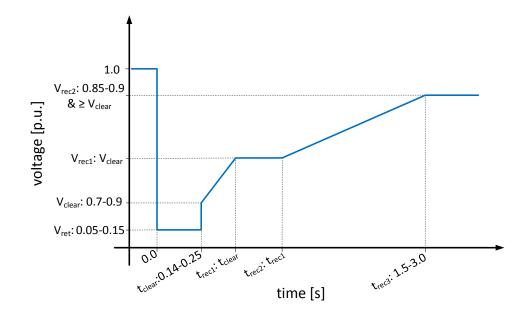

| 2.12 | Fault ride through requirement in different grid codes              | 22 |

| 2.13 | Fault ride through profile proposal by entso-e                      | 23 |

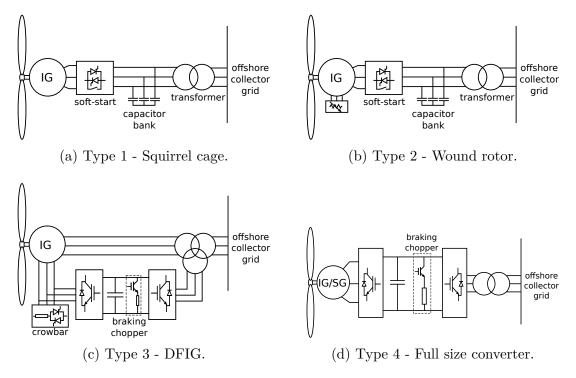

| 2.14 | Different types of wind turbine generators                          | 24 |

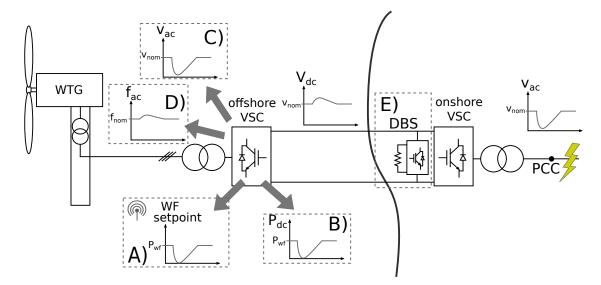

| 2.15 | Summary of DC over-voltage mitigation methods during FRT            |    |

|      | event: A) Wind farm set-point change via telecommunications,        |    |

|      | B) Active power reduction in offshore VSC station, C) Offshore      |    |

|      | voltage reduction, D) Offshore frequency increase, E) Dynamic       |    |

|      | Braking System.                                                     | 24 |

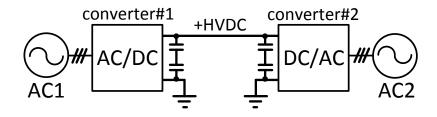

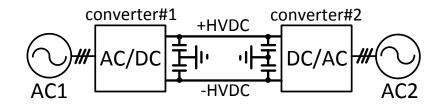

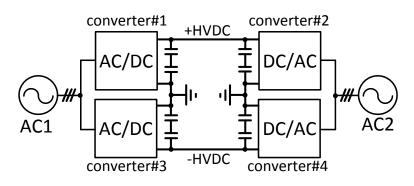

| 3.1  | Different HVDC system configurations                                | 36 |

| 3.2  | DBS arrangement for different HVDC system configurations            | 37 |

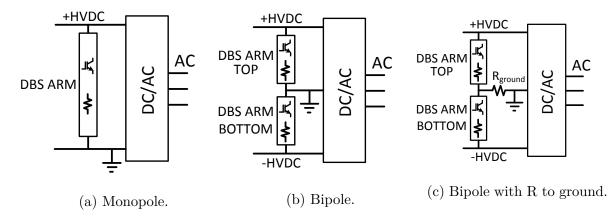

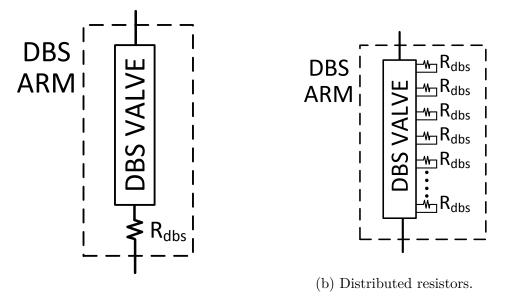

| 3.3  | Different braking resistor arrangements                             | 38 |

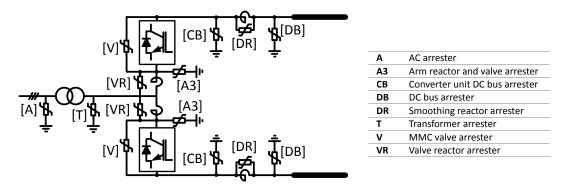

| 3.4  | Typical VSC-HVDC converter station arrester locations               | 38 |

| 3.5  | Basic structure of the HVDC chopper DBS circuit                     | 40 |

| 3.6  | Valves of series connected IGBTs                                    | 41 |

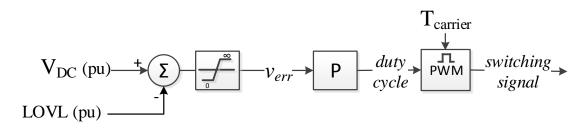

| 3.7  | Block diagram of the HVDC chopper DBS proposed controller           | 41 |

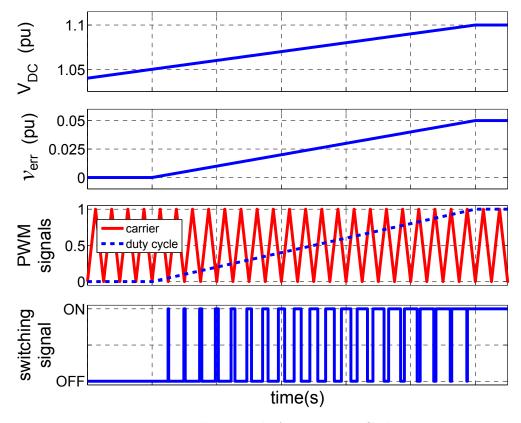

| 3.8  | Internal controller signals for the HVDC chopper circuit            | 42 |

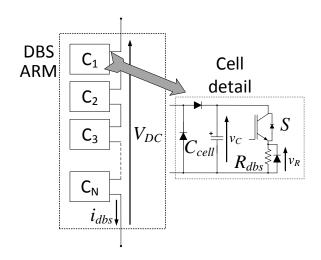

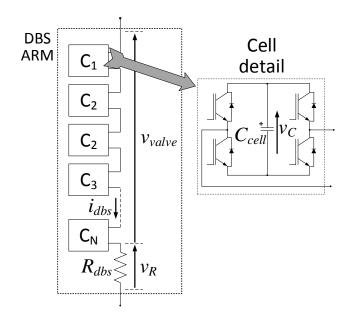

| 3.9  | Arm structure of the multilevel chopper DBS circuit                 | 43 |

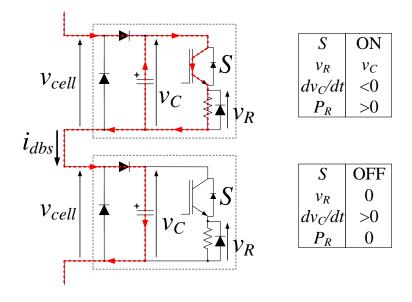

| 3.10 | Possible commutation states for the multilevel chopper DBS cells.   | 44 |

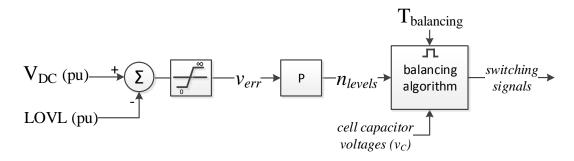

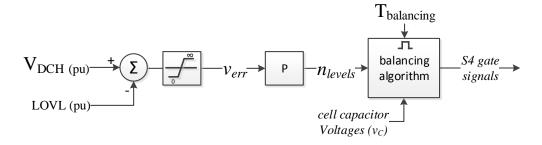

| 3.11 | Block diagram of the multilevel chopper DBS proposed controller.    | 44 |

| 0    |                                                                     |    |

| 3.12 | Flow diagram for balancing algorithm in the multilevel chopper               |    |

|------|------------------------------------------------------------------------------|----|

|      | circuit                                                                      | 45 |

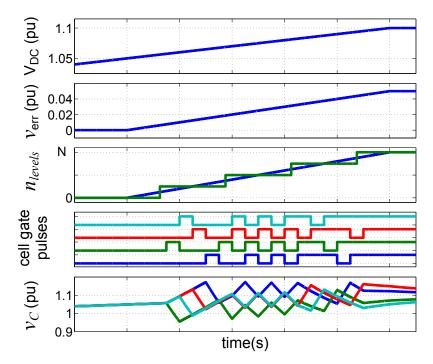

| 3.13 | Internal controller signals for the multilevel chopper circuit               | 46 |

| 3.14 | Capacitor balancing signals detail in the multilevel chopper circuit.        | 47 |

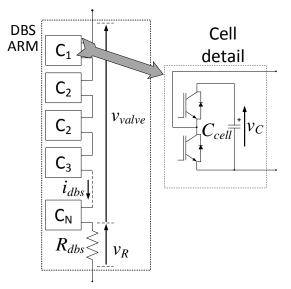

| 3.15 | Arm structure of the half-bridge multilevel DBS circuit                      | 49 |

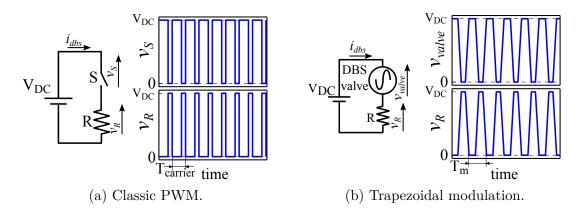

| 3.16 | Comparison between classic PWM and trapezoidal modulation                    | 50 |

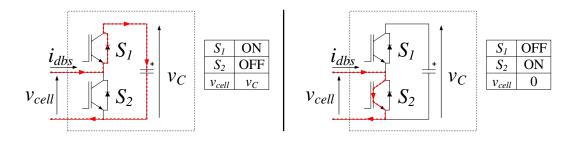

| 3.17 | Possible commutation states of the half-bridge cells                         | 51 |

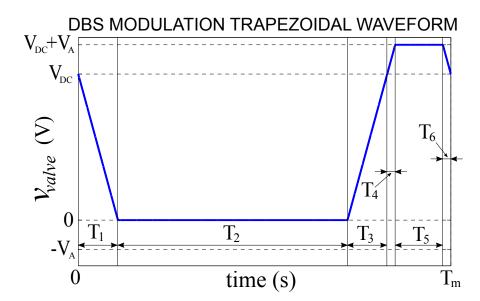

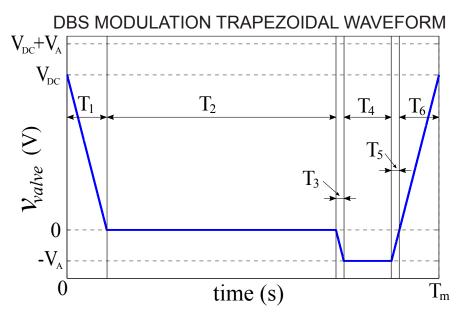

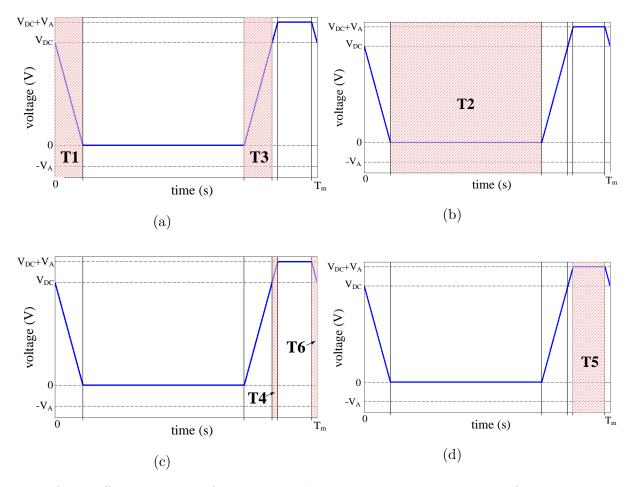

| 3.18 | Trapezoidal pulse for the half-bridge multilevel DBS modulation              | 52 |

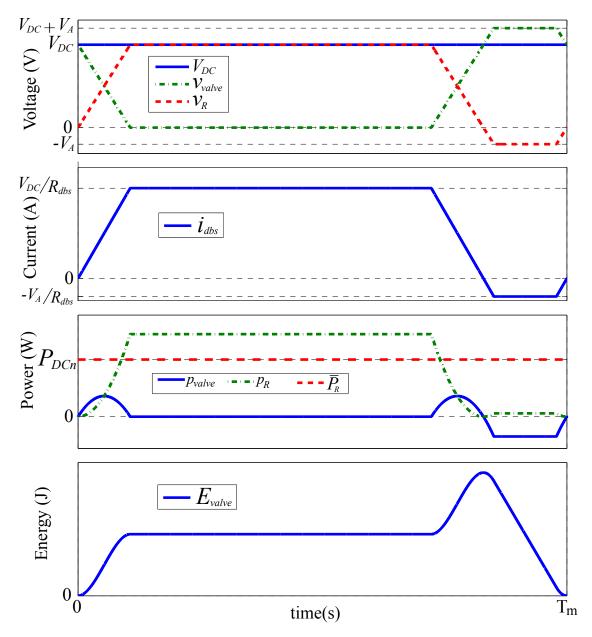

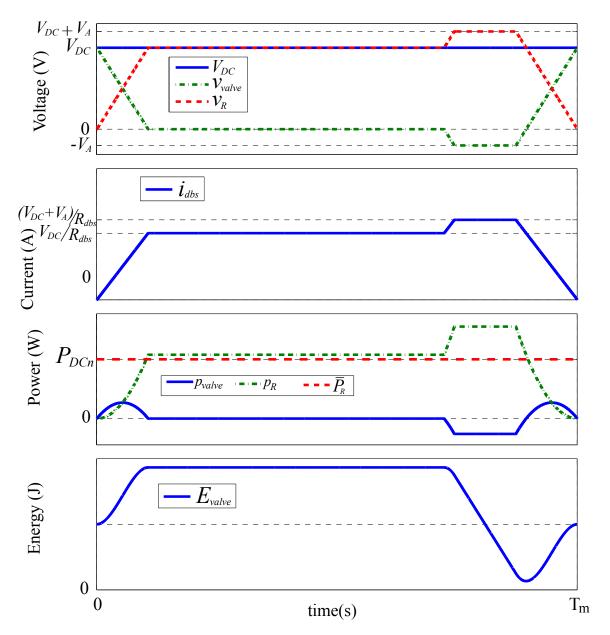

| 3.19 | Detail of the DBS arm waveforms over one modulation period with              |    |

|      | the half-bridge multilevel DBS.                                              | 53 |

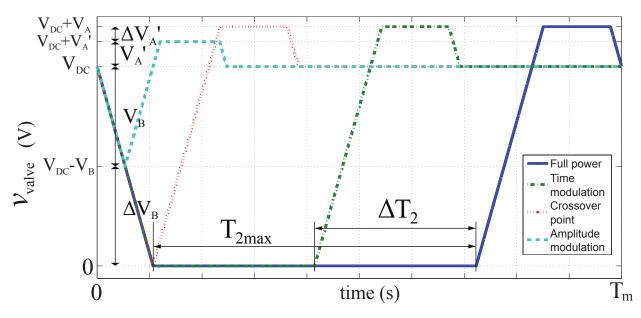

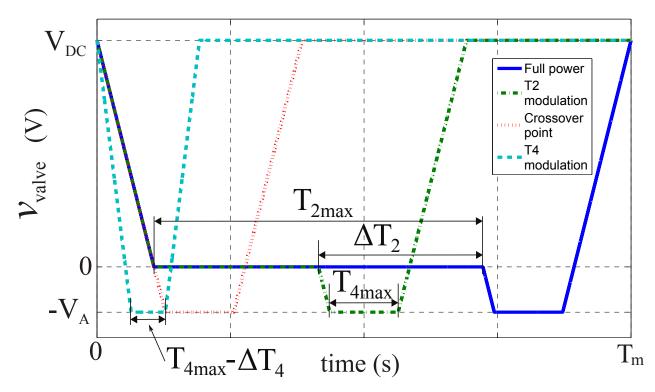

| 3.20 | Valve trapezoidal voltage for different operation regions of the             |    |

|      | modulation strategy.                                                         | 54 |

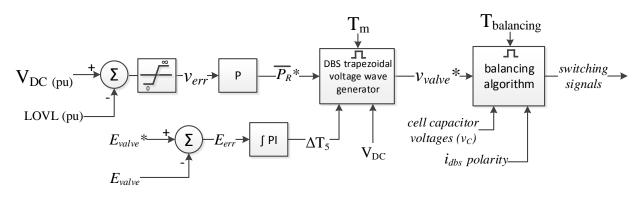

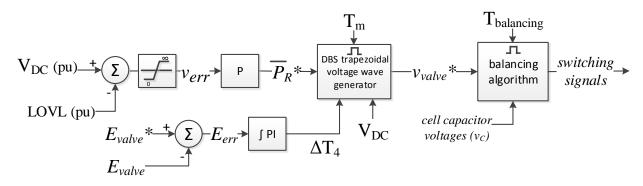

| 3.21 | Block diagram of the half-bridge multilevel DBS proposed controller.         | 58 |

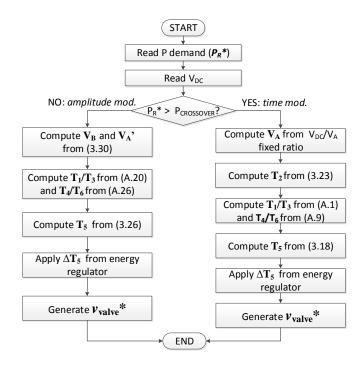

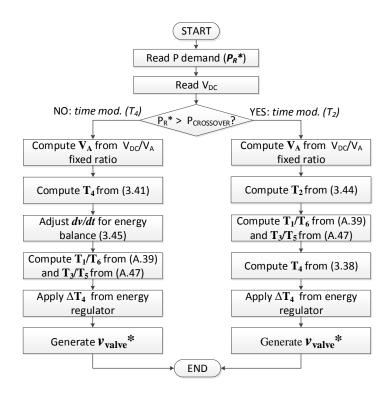

| 3.22 | Flow diagram for the trapezoidal generation function                         | 59 |

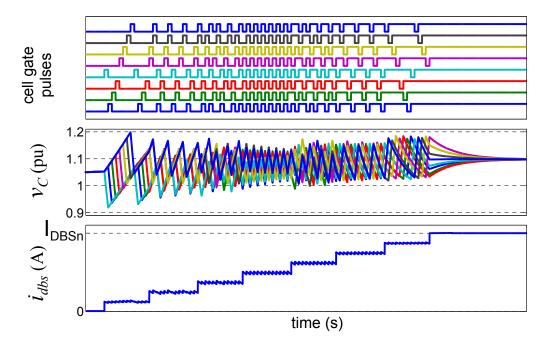

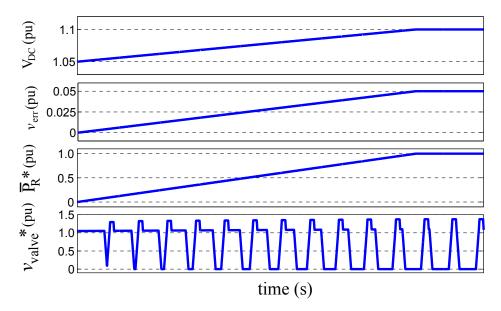

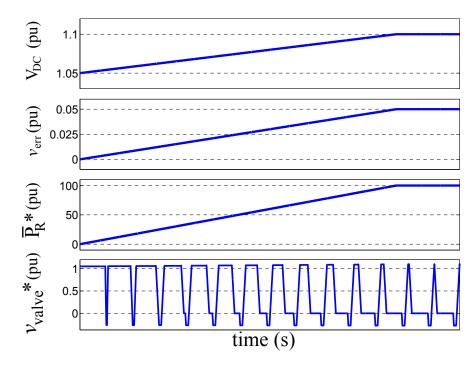

| 3.23 | Internal controller signals for the half-bridge multilevel circuit           | 60 |

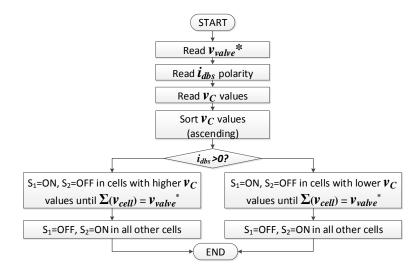

| 3.24 | Flow diagram for balancing algorithm in half-bridge multilevel               |    |

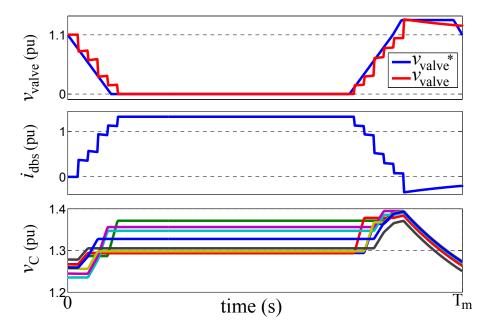

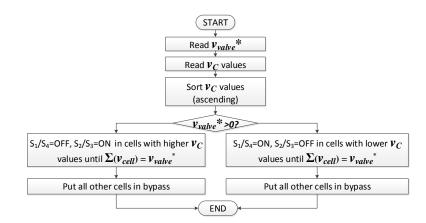

|      | circuit                                                                      | 61 |

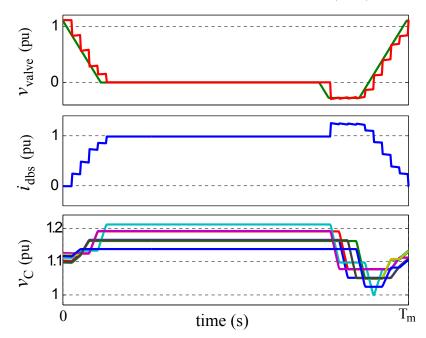

| 3.25 | Capacitor balancing signals detail in the half-bridge multilevel             |    |

|      | circuit                                                                      | 61 |

| 3.26 | Basic structure of the full-bridge multilevel DBS circuit                    | 63 |

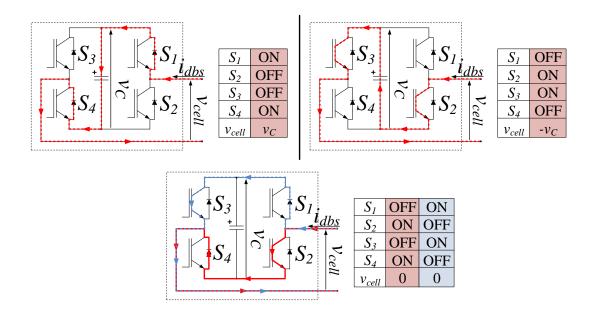

| 3.27 | Possible commutation states of the full-bridge cells                         | 63 |

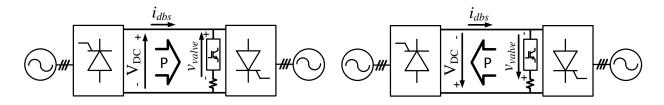

| 3.28 | Full-bridge multilevel DBS in classical HVDC scheme during power             |    |

|      | reversal                                                                     | 64 |

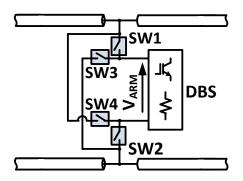

| 3.29 | Mechanical switches arrangement to reverse arm voltage polarity              |    |

|      | in DBS circuits                                                              | 64 |

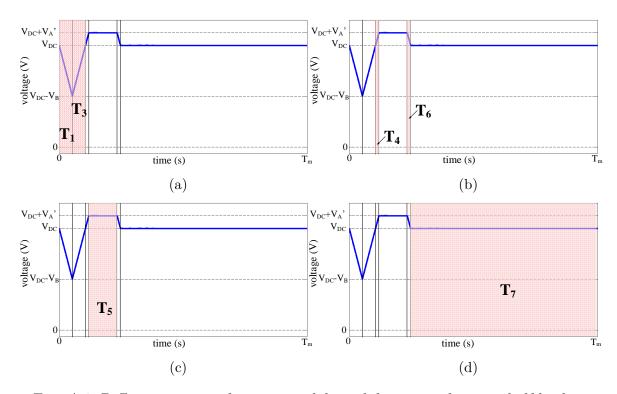

| 3.30 | Trapezoidal pulse for the full-bridge multilevel DBS modulation              | 65 |

| 3.31 | Detail of the DBS arm waveforms over one modulation period with              |    |

|      | the full-bridge multilevel DBS                                               | 66 |

| 3.32 | Valve trapezoidal voltage for different operation regions of the             |    |

|      | modulation strategy.                                                         | 67 |

| 3.33 | Block diagram of the full-bridge multilevel DBS proposed controller.         | 70 |

| 3.34 | Flow diagram for the trapezoidal generation function                         | 71 |

| 3.35 | Internal controller signals for the full-bridge multilevel circuit           | 72 |

| 3.36 | Flow diagram for balancing algorithm in full-bridge multilevel DBS.          | 73 |

| 3.37 | eq:Capacitor balancing signals detail in the full-bridge multilevel circuit. | 73 |

| 3.38 | Different cell operation characteristic                                      | 74 |

| 3.39 | Sparse bridge cell                                                           | 74 |

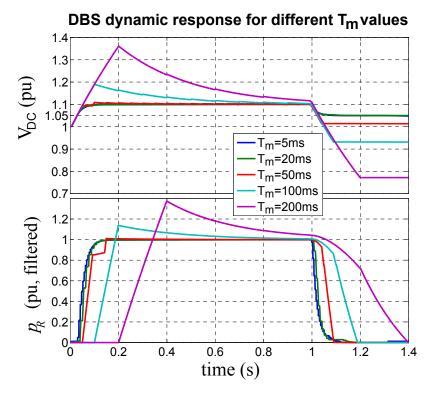

| 3.40 | DBS dynamic response for different values of modulation period $T_m$ .       | 77 |

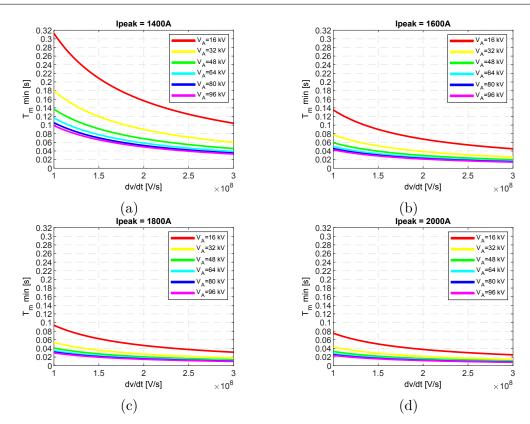

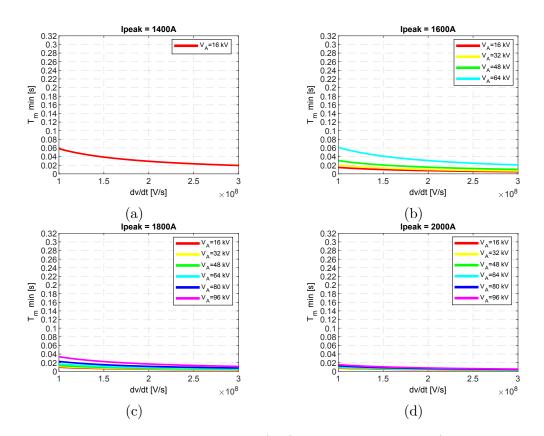

| 3.41 | Minimum modulation period $(T_m)$ as a function of $dv/dt$ and $V_A$ for<br>different values of DBS peak current in the half-bridge multilevel |          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.42 | DBS                                                                                                                                            | 79       |

| 3.43 | DBS.    .    .    .    .    .      Lumped braking resistors for Borwin 1 project    .    .    .    .                                           | 79<br>80 |

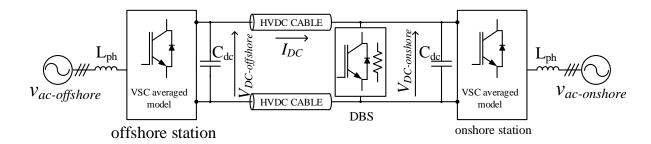

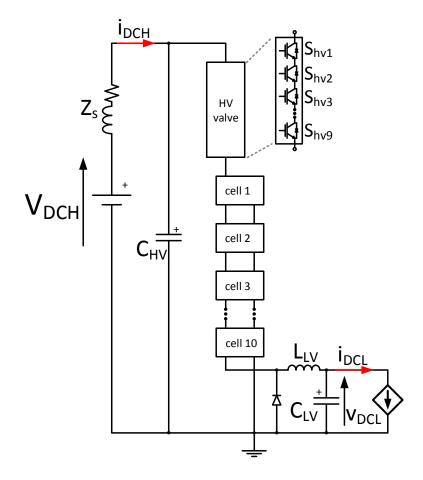

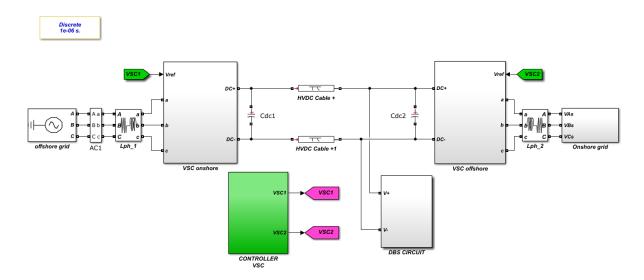

| 4.1  | HVDC interconnector model used in simulations.                                                                                                 | 86       |

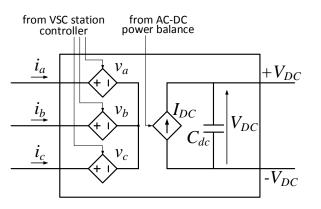

| 4.2  | Averaged model of the VSC station                                                                                                              | 86       |

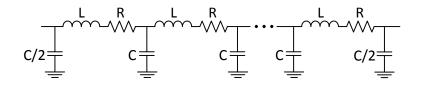

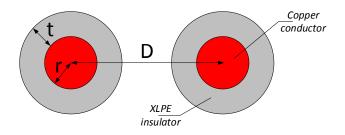

| 4.3  | Equivalent cable model based on $\pi$ -sections                                                                                                | 87       |

| 4.4  | Simplified cable layers for the RLC parameters estimation                                                                                      | 88       |

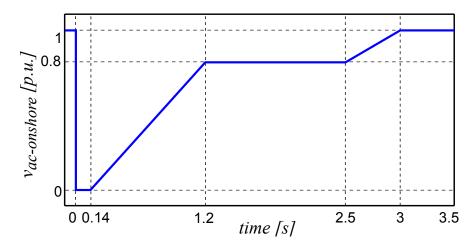

| 4.5  | Voltage-time profile used for emulating the onshore grid fault                                                                                 | 90       |

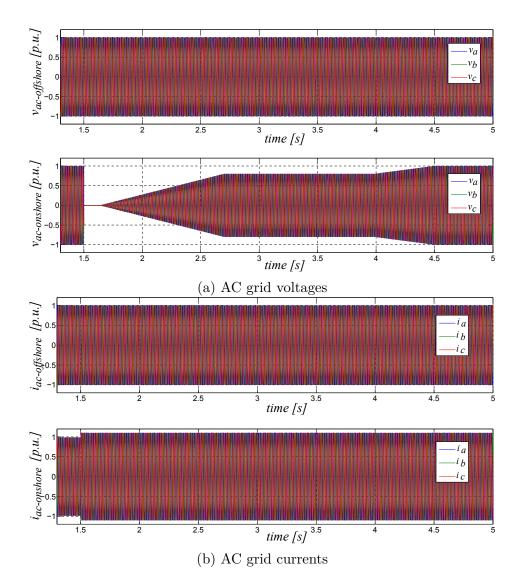

| 4.6  | AC grid waveforms both onshore and offshore during the specified                                                                               |          |

|      | fault event.                                                                                                                                   | 92       |

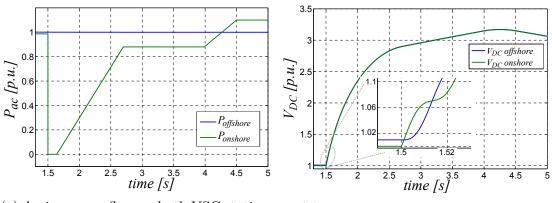

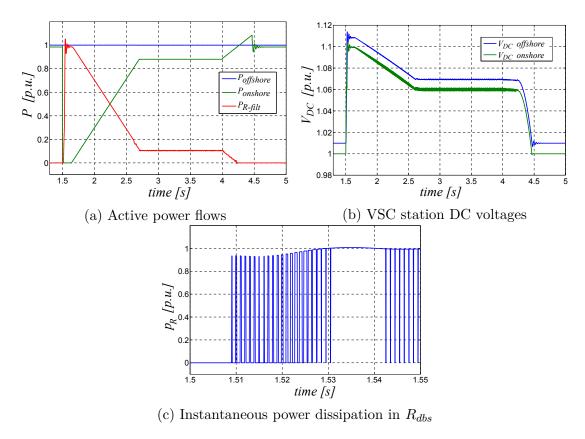

| 4.7  | Active power flow and DC voltage during a fault with no DBS in                                                                                 |          |

|      | operation.                                                                                                                                     | 92       |

| 4.8  | Simulation results with the HVDC chopper circuit (DBS#1)                                                                                       | 94       |

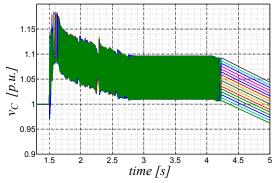

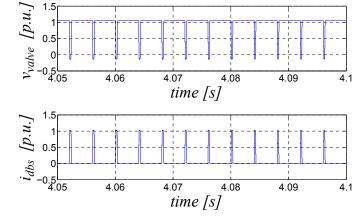

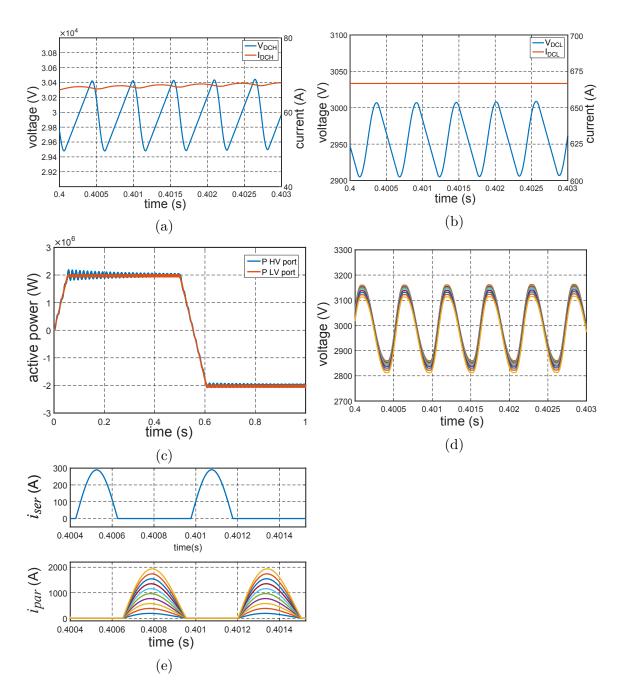

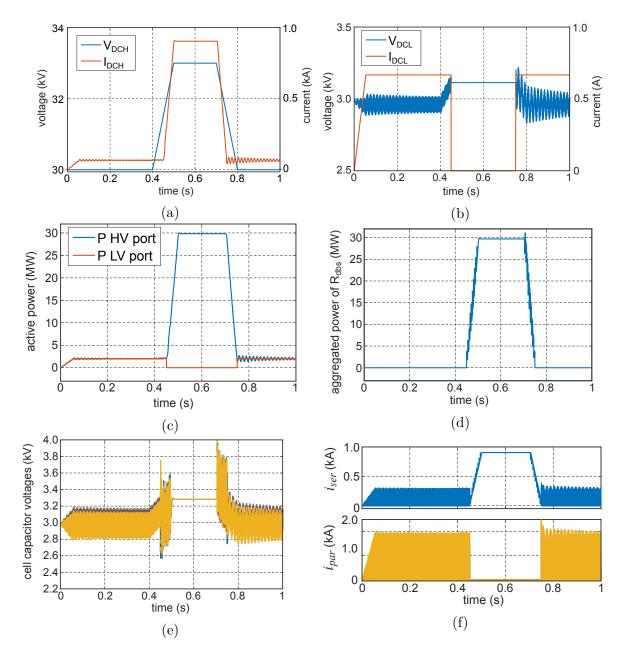

| 4.9  | Simulation results with the multilevel chopper circuit (DBS#2)                                                                                 | 96       |

| 4.10 | Quantization effect in the DBS $\#3$ valve voltage with the controller                                                                         |          |

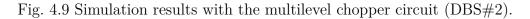

|      | demand (green) and the real DBS valve voltage (blue)                                                                                           | 97       |

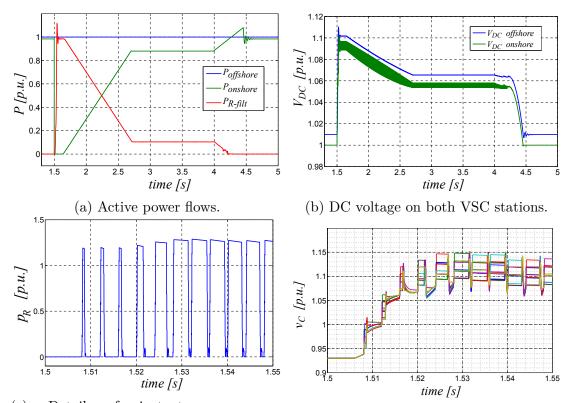

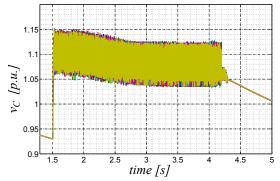

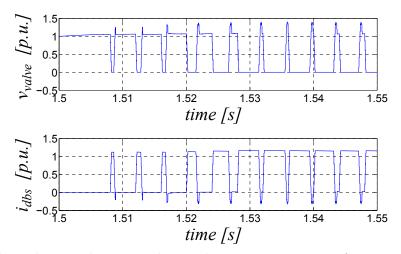

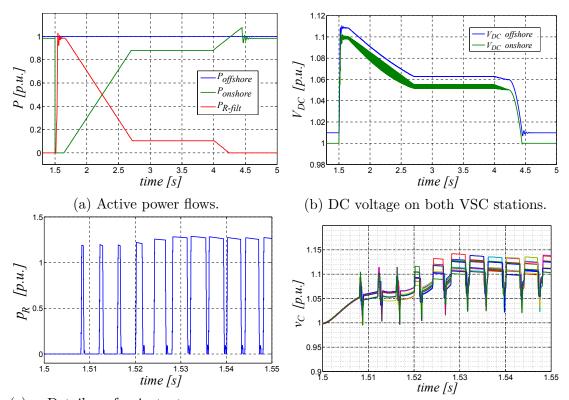

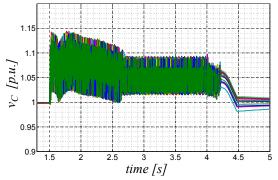

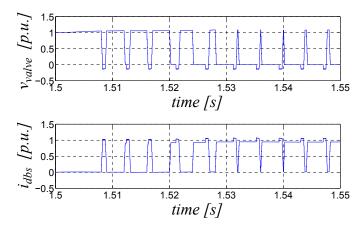

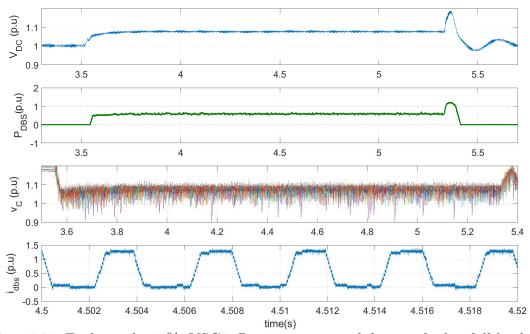

| 4.11 | Simulation results with the half-bridge multilevel circuit (DBS#3).                                                                            | 98       |

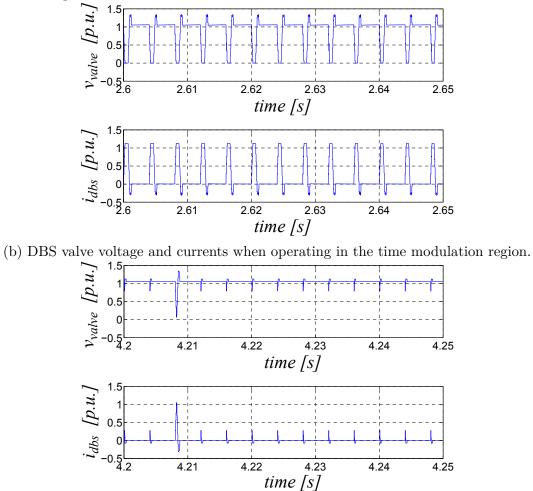

| 4.12 | Detail of the different modulation regions during the DBS#3 operation                                                                          | 100      |

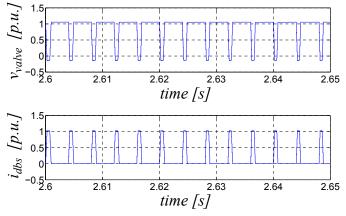

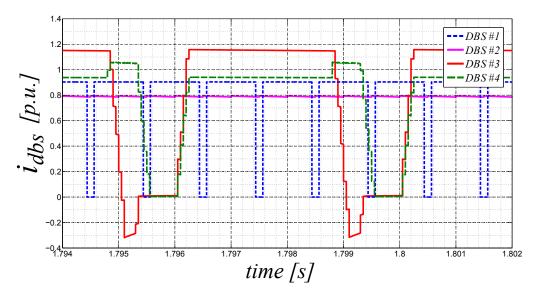

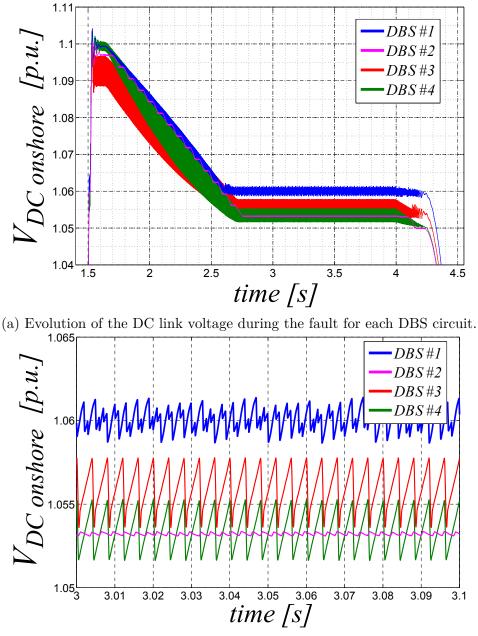

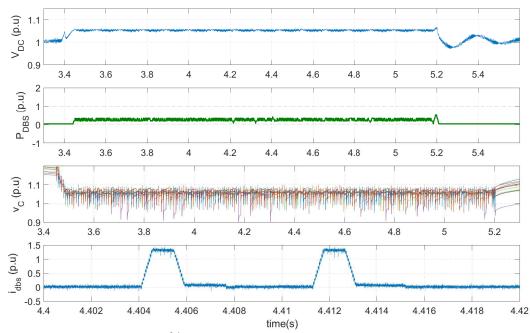

| 4.13 | Simulation results with the full-bridge multilevel circuit (DBS#4).                                                                            | 102      |

|      | Detail of the different modulation regions during the DBS#4                                                                                    |          |

|      | operation.                                                                                                                                     | 103      |

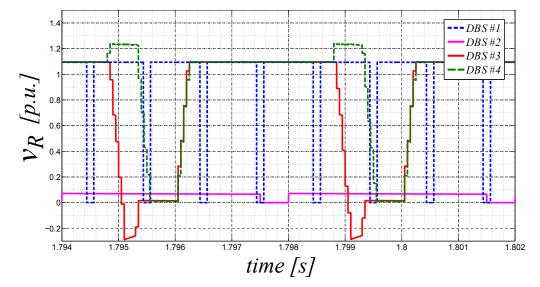

| 4.15 | Comparison of the voltage across the braking resistor in each DBS                                                                              |          |

|      | circuit                                                                                                                                        | 105      |

| 4.16 | Comparison of the current absorbed by each DBS circuit                                                                                         | 105      |

| 4.17 | Detail of the different modulation regions during the $DBS#4$                                                                                  |          |

|      | operation                                                                                                                                      | 107      |

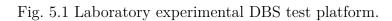

| 5.1  | Laboratory experimental DBS test platform                                                                                                      | 112      |

| 5.2  | (a) Scaled-down model of VSC-HVDC connector and (b) VSC                                                                                        |          |

|      | power module                                                                                                                                   | 112      |

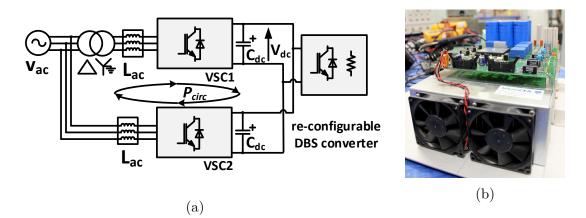

| 5.3  | Detailed laboratory test platform electrical diagram                                                                                           | 114      |

| 5.4  | Braking resistors used in the test platform.                                                                                                   | 115      |

| 5.5  | Simulation results for the fault emulation mechanism                                                                                           | 118      |

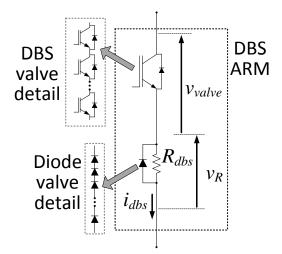

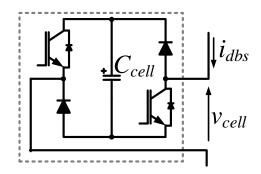

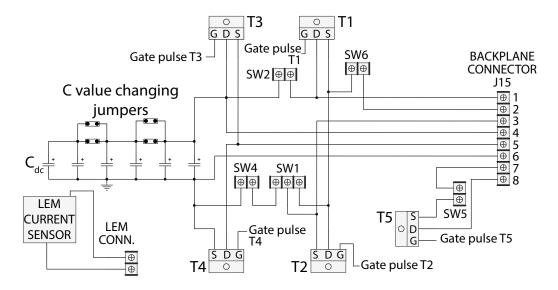

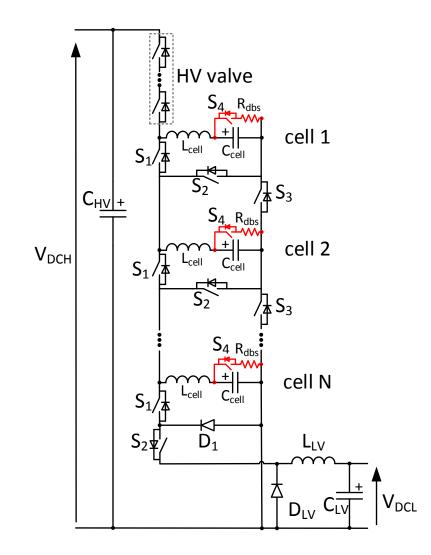

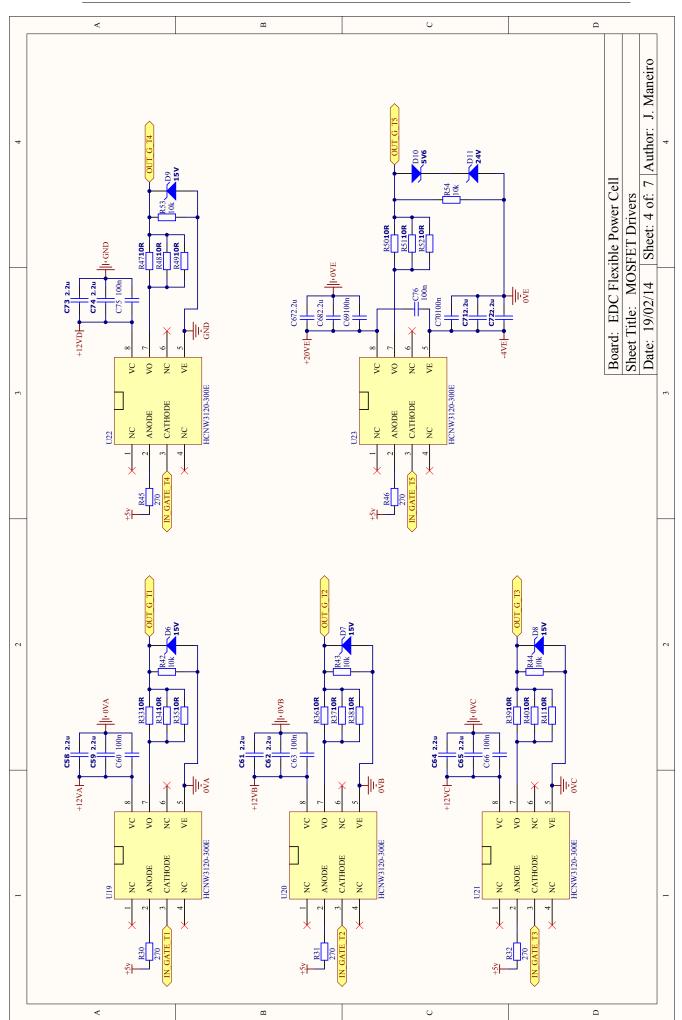

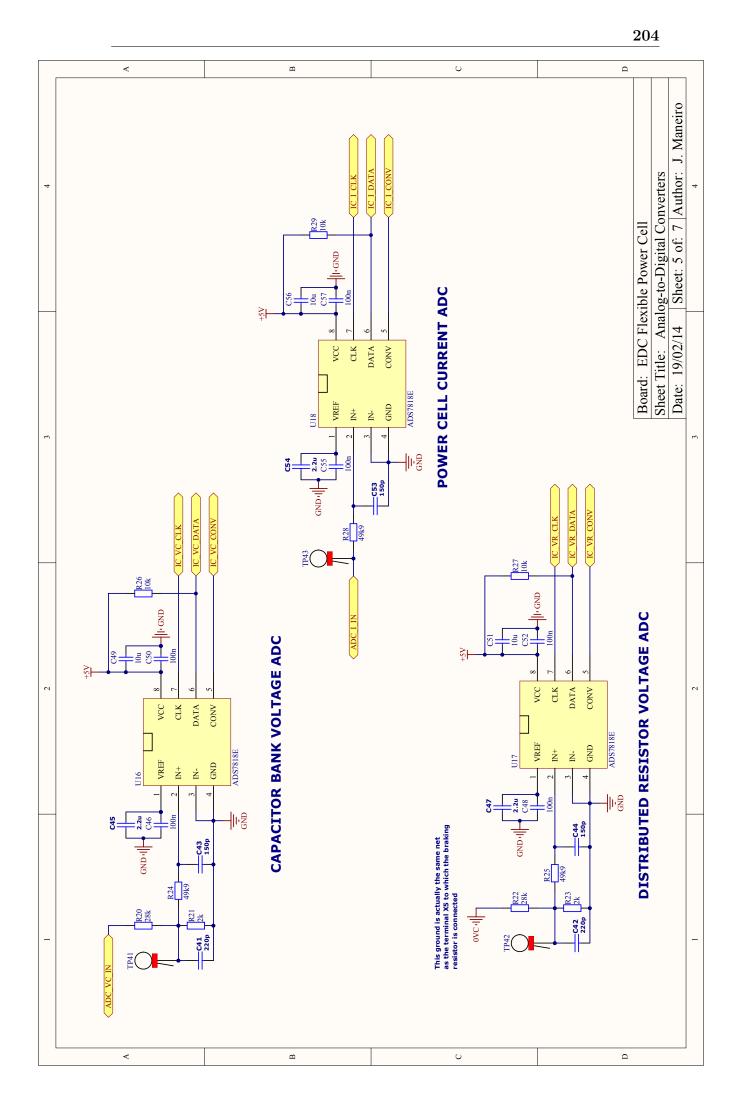

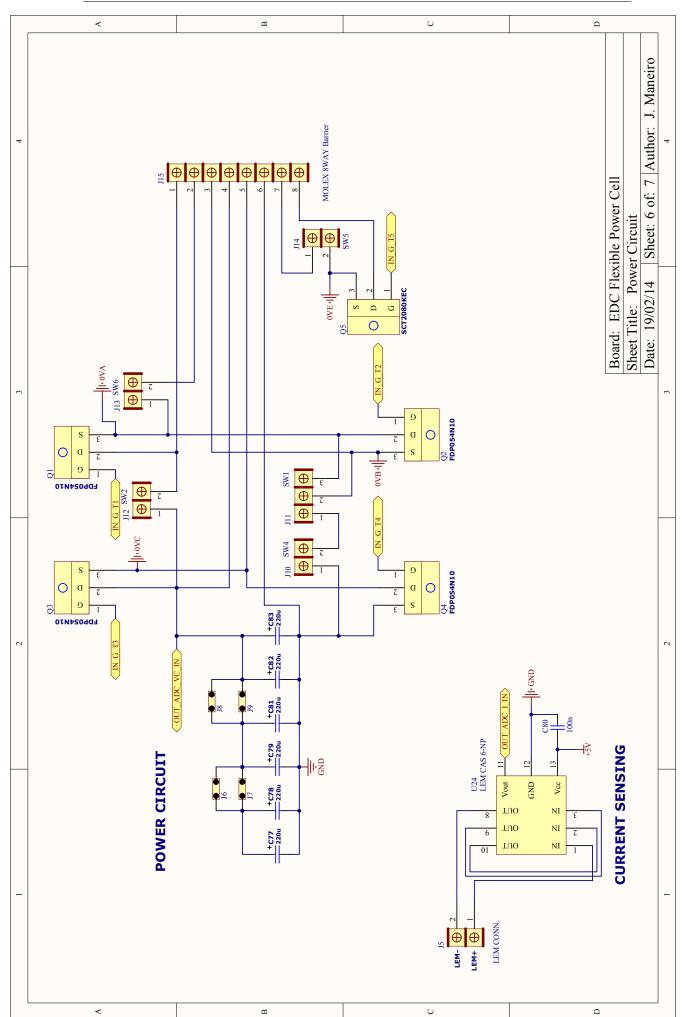

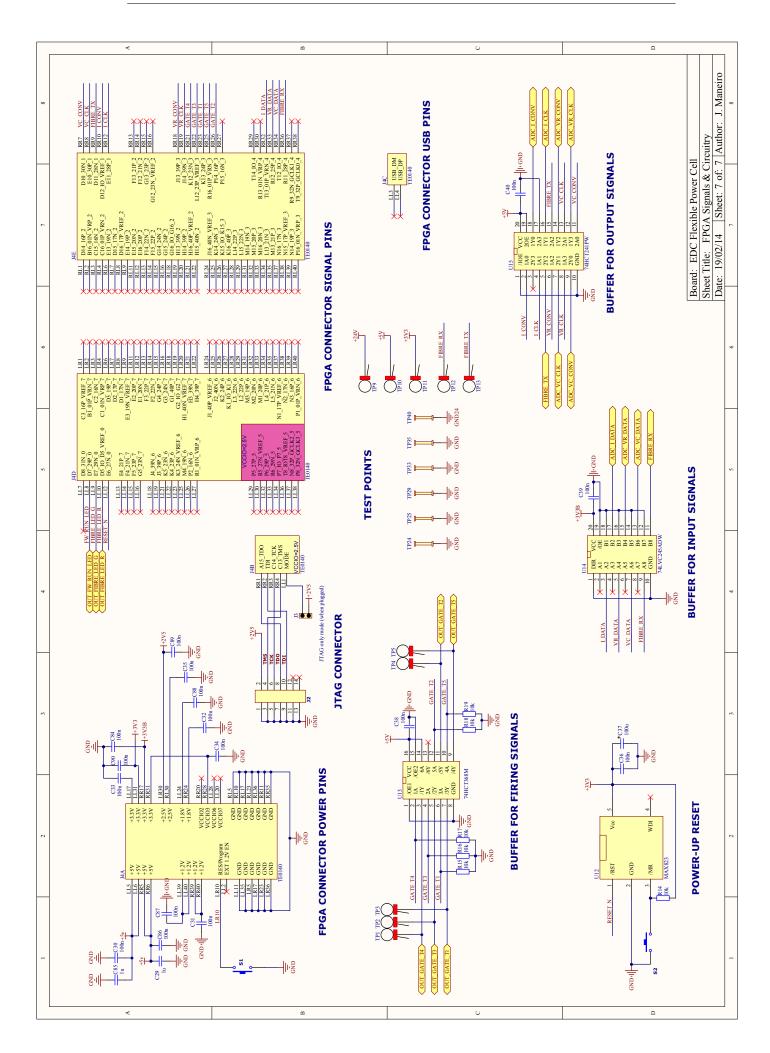

| 5.6  | Power circuit diagram of the flexible power cell                                                                                               | 119      |

| 5.7        | Screw terminal connections in the flexible power cell for the different DBS configurations. | 120               |

|------------|---------------------------------------------------------------------------------------------|-------------------|

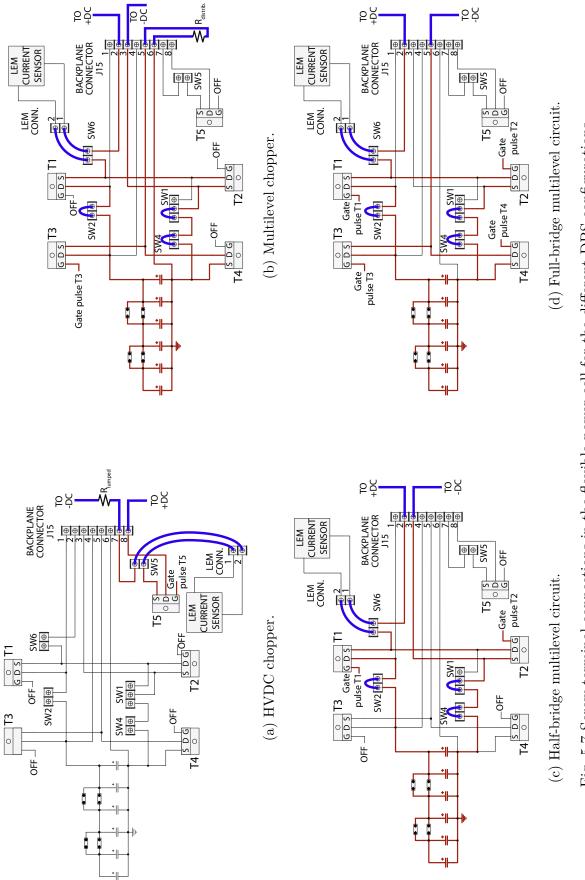

| 5.8        | 0                                                                                           | 120               |

| 5.8<br>5.9 | Configuration of the power cells to build the four DBS circuits<br>Flexible power cell      | $\frac{121}{122}$ |

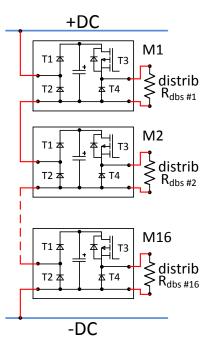

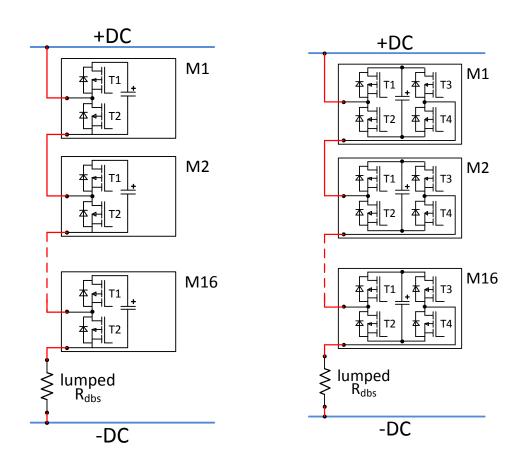

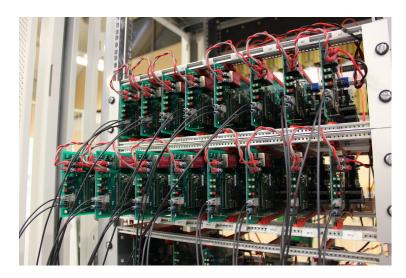

|            | Modular arrangement of the DBS power cells for the DBS circuits                             | 122               |

| 5.10       | implementation.                                                                             | 122               |

| 5 11       | Different control boards in the test platform.                                              | 122               |

|            | Test platform communication network detail                                                  | 125               |

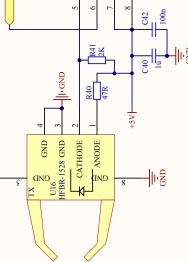

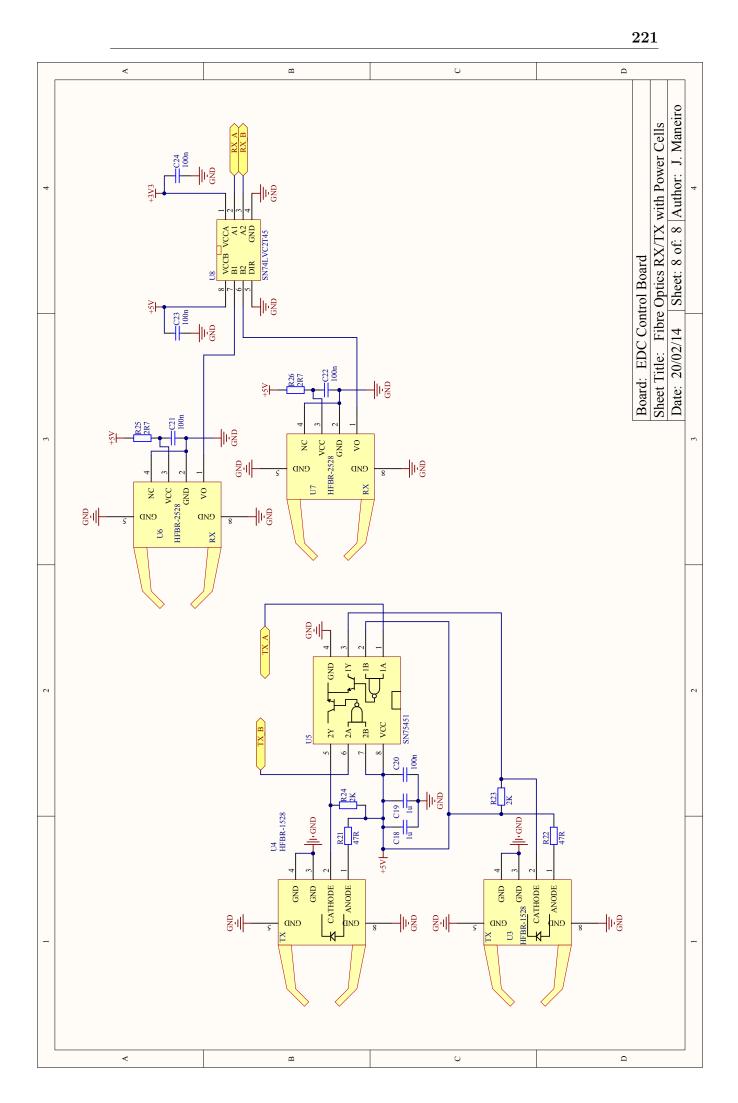

|            | View of the different communication interfaces.                                             | 126               |

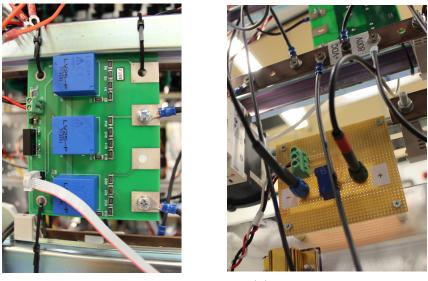

|            | External sensor boards in the DBS converter.                                                | 127               |

|            | User interface implemented in LabVIEW                                                       | 128               |

|            |                                                                                             |                   |

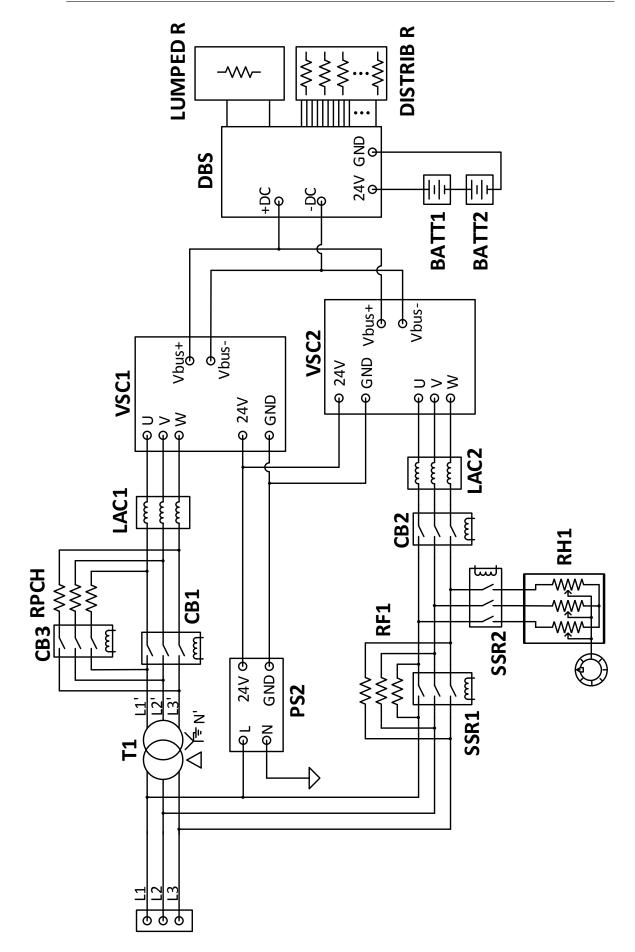

| 6.1        | Reminder of the experimental test platform diagram                                          | 131               |

| 6.2        | Start-up sequence and power demand variation in the test platform.                          | .133              |

| 6.3        | AC fault in the test platform with DBS disabled                                             | 134               |

| 6.4        | VSC1 and VSC2 AC waveforms for successful fault ride-through                                |                   |

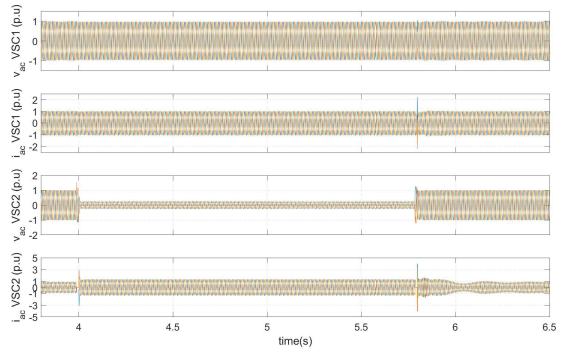

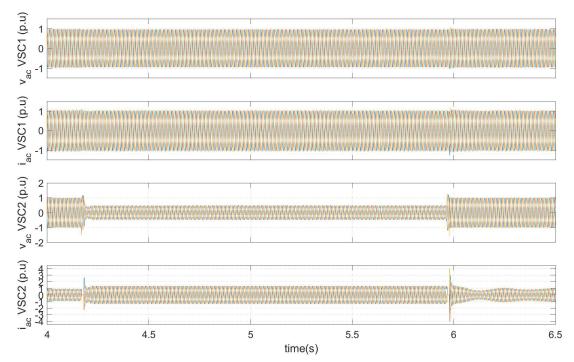

|            | with VSC2's P injection capability reduced to 0%                                            | 135               |

| 6.5        | VSC1 and VSC2 AC waveforms for successful fault ride-through                                |                   |

|            | with VSC2's P injection capability reduced to 30%                                           | 136               |

| 6.6        | VSC1 and VSC2 AC waveforms for successful fault ride-through                                |                   |

|            | with VSC2's P injection capability reduced to $60\%$ .                                      | 136               |

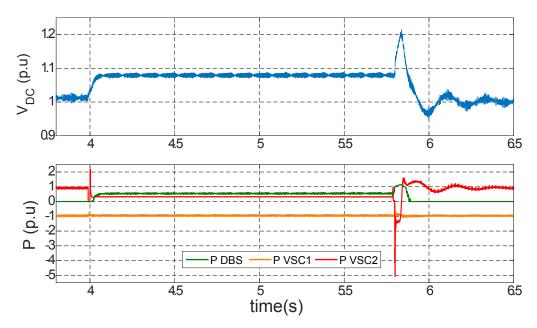

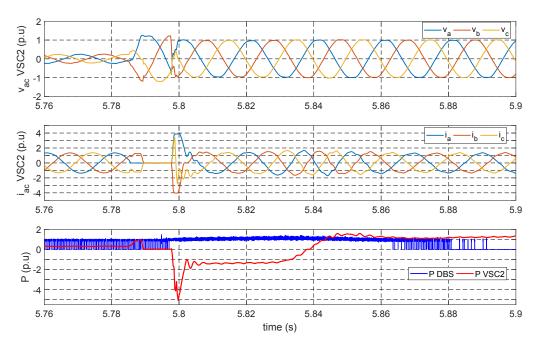

| 6.7        | VSC2 malfunction during commutation of the fault circuit                                    |                   |

|            | contactors                                                                                  | 137               |

| 6.8        | Detailed view of relevant waveforms during the fault circuit                                |                   |

|            | commutation that generates the DC over-voltage                                              | 138               |

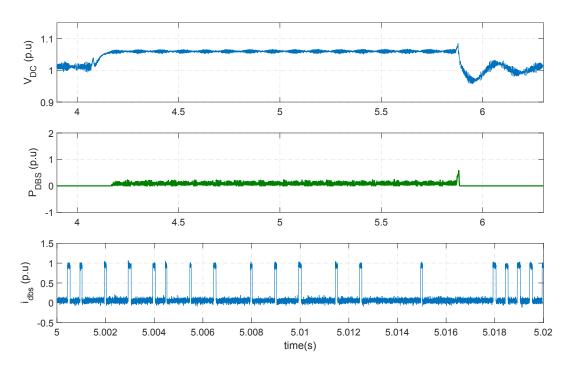

| 6.9        | Fault with 0% VSC2 P injection capability and the HVDC chopper                              |                   |

|            | DBS in operation                                                                            | 140               |

| 6.10       | Fault with $30\%$ VSC2 P injection capability and the HVDC                                  |                   |

|            | chopper DBS in operation                                                                    | 141               |

| 6.11       | Fault with $60\%$ VSC2 P injection capability and the HVDC                                  |                   |

|            | chopper DBS in operation                                                                    | 141               |

| 6.12       | Fault with $75\%$ VSC2 P injection capability and the HVDC                                  |                   |

|            | chopper DBS in operation                                                                    | 142               |

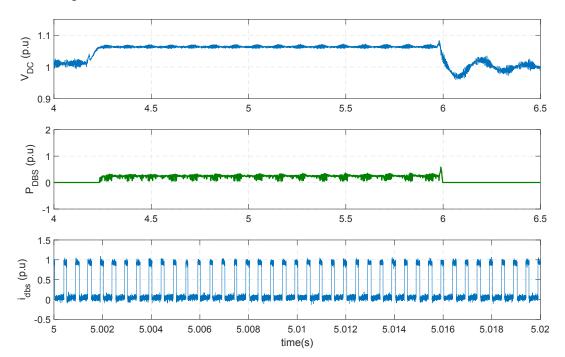

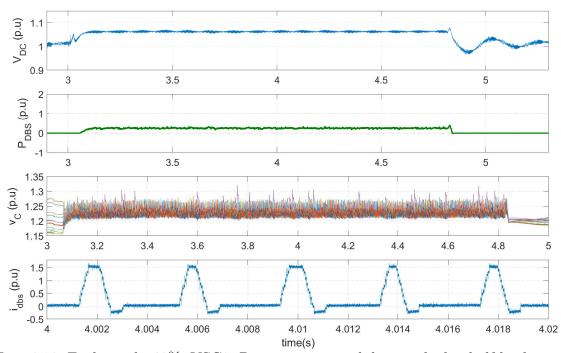

| 6.13       | Fault with 0% VSC2 P injection capability and the multilevel                                |                   |

|            | chopper DBS in operation                                                                    | 143               |

| 6.14       | Fault with $30\%$ VSC2 P injection capability and the multilevel                            |                   |

|            | chopper DBS in operation                                                                    | 143               |

| 6.15       | Fault with $60\%$ VSC2 P injection capability and the multilevel                            |                   |

|            | chopper DBS in operation                                                                    | 144               |

| 6.16       | Fault with $75\%$ VSC2 P injection capability and the multilevel                            |                   |

|            | chopper DBS in operation.                                                                   | 144               |

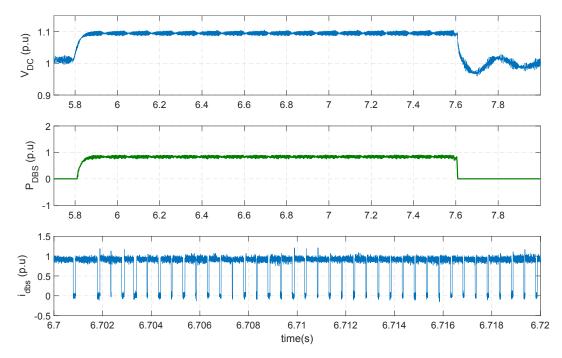

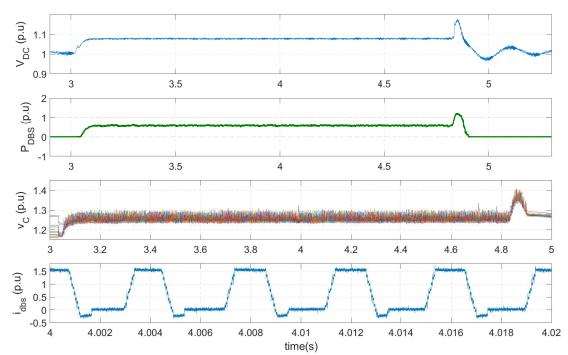

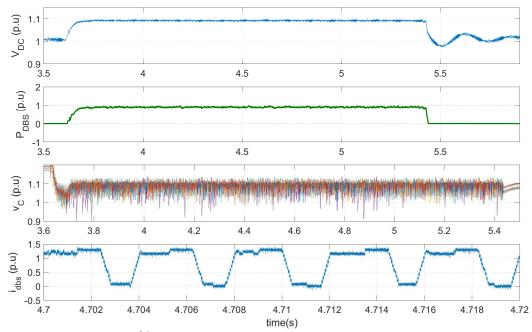

| 6.17 Fault with 0% VSC2 P injection capability and the half-bridge                                                                 |     |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| multilevel DBS in operation                                                                                                        | 47  |

| 6.18 Fault with $30%$ VSC2 P injection capability and the half-bridge                                                              |     |

| multilevel DBS in operation                                                                                                        | 47  |

| 6.19 Fault with $60%$ VSC2 P injection capability and the half-bridge                                                              |     |

| multilevel DBS in operation                                                                                                        | 48  |

| 6.20 Fault with $75%$ VSC2 P injection capability and the half-bridge                                                              |     |

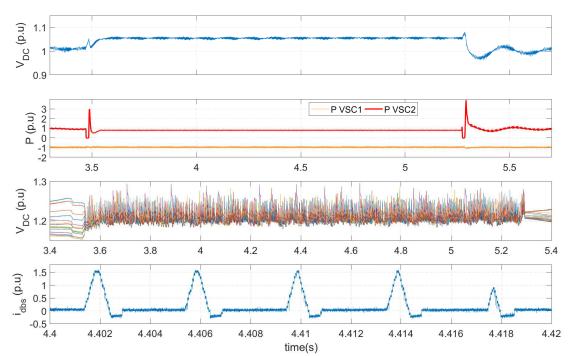

| multilevel DBS in operation                                                                                                        | 48  |

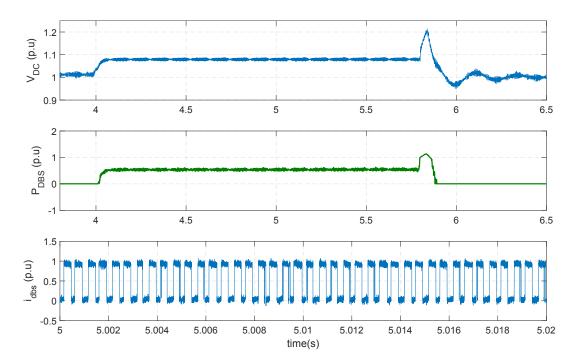

| 6.21 Fault with 0% VSC2 P injection capability and the full-bridge                                                                 |     |

| multilevel DBS in operation                                                                                                        | 50  |

| 6.22 Fault with 30% VSC2 P injection capability and the full-bridge                                                                |     |

| multilevel DBS in operation                                                                                                        | 51  |

| 6.23 Fault with $60%$ VSC2 P injection capability and the full-bridge                                                              |     |

| multilevel DBS in operation                                                                                                        | 52  |

| 6.24 Fault with 75% VSC2 P injection capability and the full-bridge                                                                |     |

| multilevel DBS in operation                                                                                                        | 52  |

|                                                                                                                                    |     |

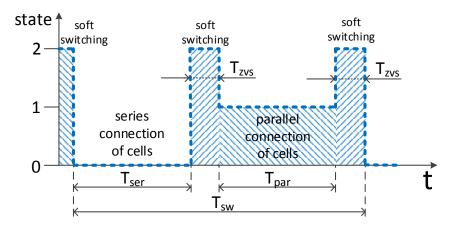

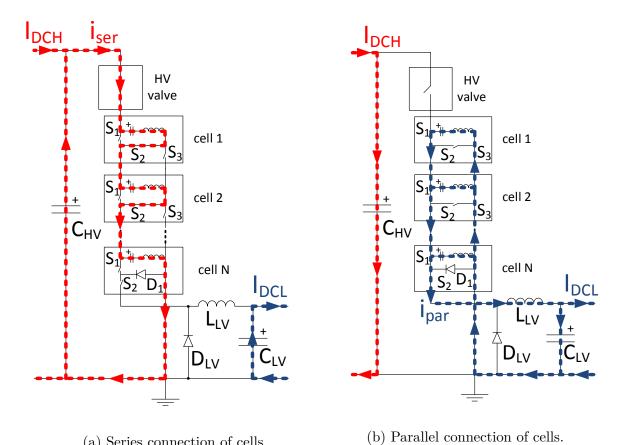

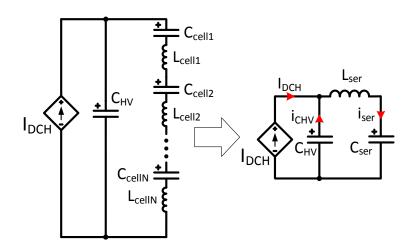

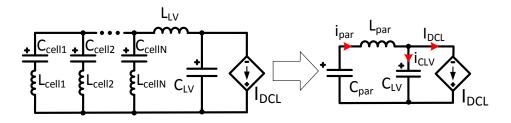

|                                                                                                                                    | .55 |

|                                                                                                                                    | .56 |

|                                                                                                                                    | .57 |

|                                                                                                                                    | .58 |

|                                                                                                                                    | .59 |

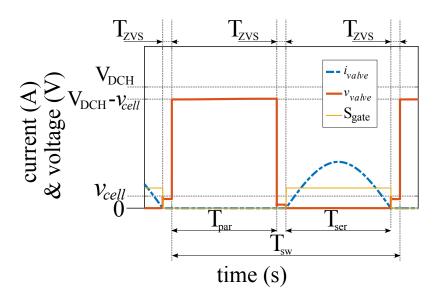

|                                                                                                                                    | .60 |

|                                                                                                                                    | .61 |

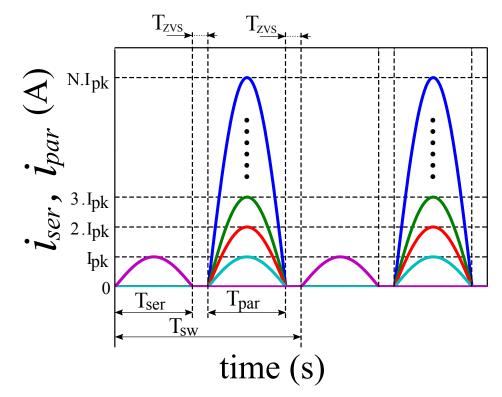

| 7.8 Characteristic of ideal switch currents during the series/parallel                                                             | ~ . |

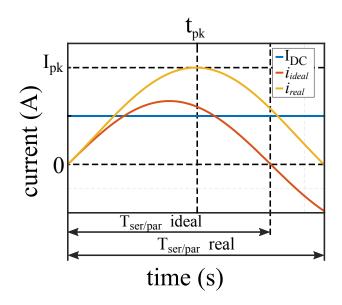

|                                                                                                                                    | .64 |

| 7.9 Variation in the resonant subinterval duration introduced by the                                                               | ~ ~ |

| 1                                                                                                                                  | .66 |

| 6 6                                                                                                                                | .68 |

| -                                                                                                                                  | .69 |

| 1                                                                                                                                  | .69 |

| 7.13 Simulation results for the resonant DC transformer in monopole                                                                |     |

| 5                                                                                                                                  | .71 |

| 7.14 Cascaded resonant DC transformer integrating dynamic braking                                                                  |     |

| 0                                                                                                                                  | 72  |

| 7.15 Additional control function for the DC transformer integrating                                                                |     |

|                                                                                                                                    | .73 |

| 7.16 Simulation results for the resonant DC transformer in monopole                                                                |     |

| configuration. $\ldots \ldots 1$ | 75  |

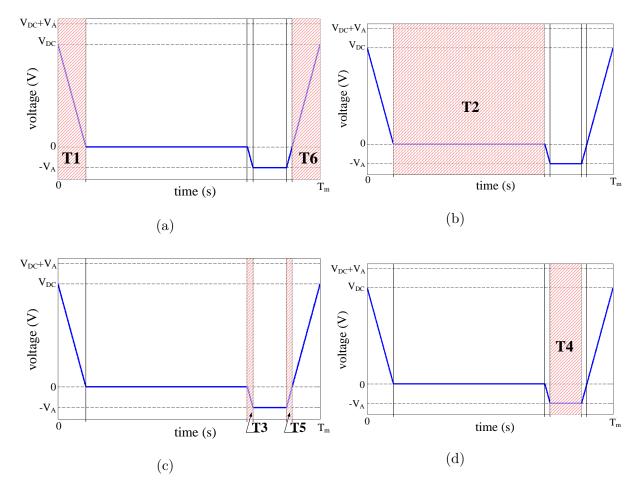

|               | t regions for trapezoidal modulation analysis in half-bridge | 101 |

|---------------|--------------------------------------------------------------|-----|

|               |                                                              | 191 |

|               | t regions for trapezoidal modulation analysis in half-bridge |     |

|               | el DBS: amplitude modulation region                          | 194 |

|               | t regions for trapezoidal modulation analysis in full-bridge |     |

| multilev      | el DBS                                                       | 196 |

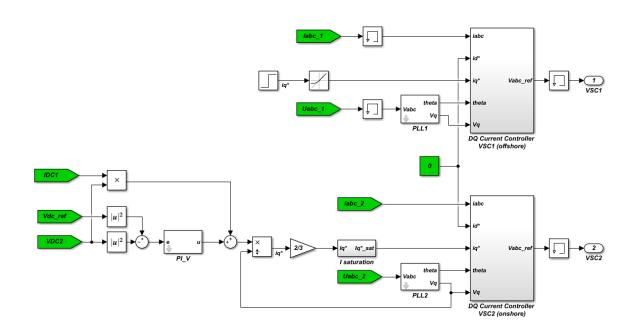

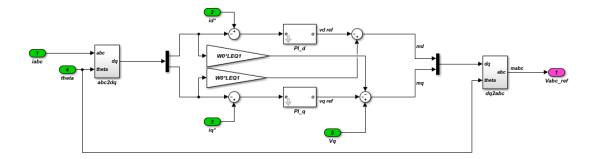

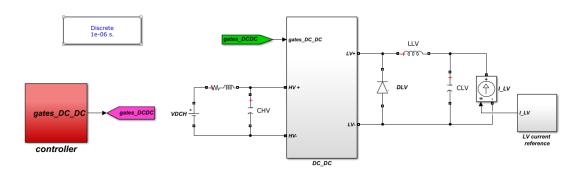

| D.1 Global s  | simulation block diagram.                                    | 237 |

| D.2 Average   | model of VSC stations.                                       | 238 |

|               | 0                                                            | 239 |

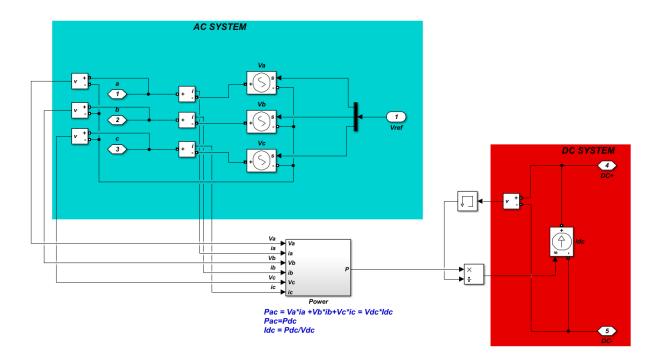

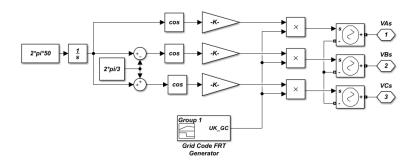

| D.4 VSC sta   | tion controller                                              | 239 |

| D.5 Detail of | f the inner current control loop                             | 239 |

| D.6 Detail of | f the inner current control loop                             | 240 |

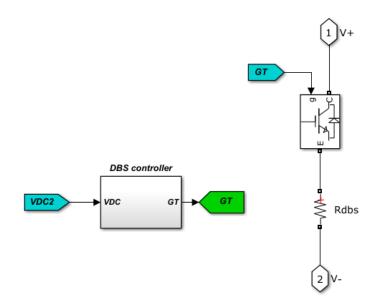

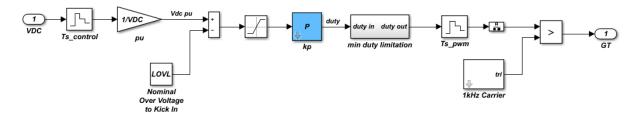

| D.7 Global o  | liagram of the HVDC chopper DBS                              | 240 |

| D.8 Controll  | er detail for the HVDC chopper DBS                           | 240 |

| D.9 Global o  | liagram of the multilevel chopper DBS                        | 241 |

| D.10 Cell det | ail for the multilevel chopper DBS                           | 241 |

| D.11 Controll | er detail for the multilevel chopper DBS                     | 241 |

| D.12 Global o | liagram of the half-bridge multilevel DBS                    | 242 |

| D.13 Cell det | ail for the half-bridge multilevel DBS                       | 242 |

| D.14 Controll | er detail for the half-bridge multilevel DBS                 | 242 |

| D.15 Global o | liagram of the full-bridge multilevel DBS                    | 243 |

| D.16 Cell det | ail for the full-bridge multilevel DBS                       | 243 |

| D.17 Controll | er detail for the full-bridge multilevel DBS                 | 243 |

| D.18 Global o | liagram of the HVDC tap simulation.                          | 244 |

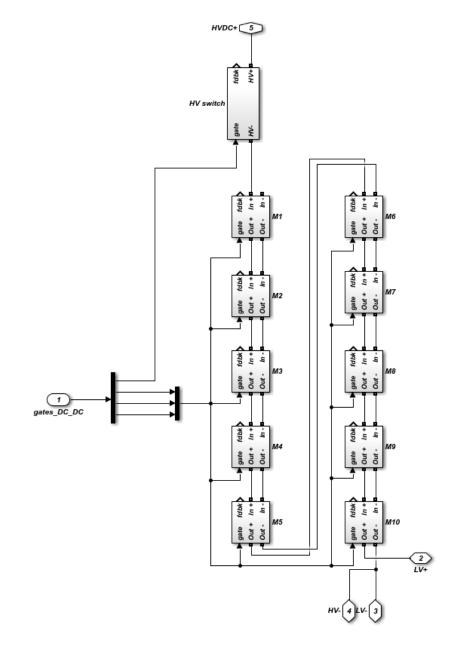

| D.19 Detail o | f the DC-DC converter internal diagram                       | 245 |

| D.20 Detail o | f the DC-DC converter cell                                   | 246 |

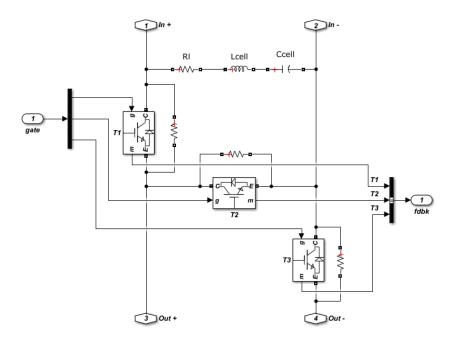

| D.21 Controll | er detail for the DC-DC converter                            | 246 |

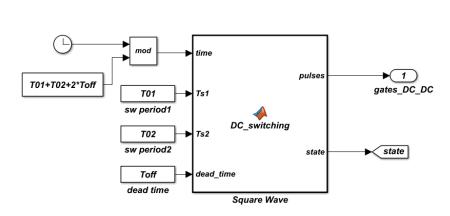

| D.22 Detail o | f the high-voltage DC link for the HVDC tap integrating      |     |

| DBS sin       | nulations.                                                   | 247 |

| D.23 Modified | d cell including the distributed chopper circuit             | 247 |

| D.24 Controll | er detail for the DC-DC converter integrating DBS            |     |

| function      | ality                                                        | 248 |

# List of tables

| 3.1 | Limits of the DBS operation for this research project                   | 39   |

|-----|-------------------------------------------------------------------------|------|

| 3.2 | Characteristics of braking resistors for the different DBS circuits.    | 81   |

| 3.3 | Comparison of semiconductor requirements in the four DBS circuits.      | . 82 |

| 3.4 | Total stored energy for multilevel DBS circuits                         | 83   |

| 4.1 | Parameters of the reduced scale model used in simulations               | 89   |

| 4.2 | DC cable parameters                                                     | 90   |

| 4.3 | DBS#1 circuit dimensioning                                              | 93   |

| 4.4 | DBS#2 circuit dimensioning                                              | 95   |

| 4.5 | DBS#3 circuit dimensioning                                              | 96   |

| 4.6 | DBS#4 circuit dimensioning                                              | 101  |

| 4.7 | Braking resistor requirements in the four simulated circuits. $\ . \ .$ | 106  |

| 4.8 | Semiconductor requirements in the four simulated circuits               | 107  |

| 4.9 | Total stored energy for multilevel DBS circuits                         | 108  |

| 5.1 | Main laboratory test platform parameters                                | 112  |

| 5.2 | Main laboratory test platform components                                | 113  |

| 5.3 | Flexible power cell main components                                     | 118  |

| 5.4 | Laboratory test platform measurements detail                            | 126  |

| 5.5 | Data transmission bandwidths in the communication network               | 126  |

| 6.1 | Test platform set-up parameters for the tests                           | 132  |

| 6.2 | PI controller gains for the VSC stations in the test platform           | 132  |

| 6.3 | P and PI controller gains for DBS converters in the test platform.      | 132  |

| 6.4 | Parameters used with the DBS#1 circuit during the tests                 | 140  |

| 6.5 | Parameters used with the DBS#2 circuit during the tests                 | 142  |

| 6.6 | Parameters used with the DBS#3 circuit during the tests                 | 146  |

| 6.7 | Parameters used with the DBS#4 circuit during the tests                 | 149  |

| 7.1 | Switching states of the circuit switches                                | 159  |

| 7.2 | System parameters for the HVDC tap simulation model                     | 170  |

| 7.3 | Additional parameters for the HVDC tap+DBS simulation model.            | 174  |

| D.1 | PI controller gains for VSC stations.                                   | 238  |

# List of acronyms and symbols

#### Acronyms

- AC Alternating current

- ADC Analogue to digital converter

- CSC Current source converter

- DBS Dynamic braking system

- DC Direct current

- EDC Energy diverting converter

- PCB Printed circuit board

- EMI Electro magnetic interference

- FRT Fault ride-through

- HDL Hardware description language

- HVAC High voltage alternating current

- HVDC High voltage direct current

- IGBT Insulated gate bipolar transistor

- $LCC\;$  Line commutated converter

- LOVL Lower over-voltage limit

- $MMC/M^2C$  Modular multilevel converter

- MTDC Multi-terminal direct current

- MVAC Medium voltage alternating current

- MVDC Medium voltage direct current

- OWF Offshore wind farm

- PCB Printed circuit board

- PLL Phase-locked loop

- PWM Pulse-width modulation

- RES Renewable energy sources

- DFIG Doubly fed induction generator

- SI International system of units

- STATCOM Static synchronous compensator

- SVC Static VAR compensator

- TSO Transmission system operator

- UOVL Upper over-voltage limit

- VSC Voltage source converter

- VSC HVDC Voltage source converter based high voltage direct current

- $WTG\,$  Wind turbine generator

- XLPE Cross-linked polyethylene

# Chapter 1

# Introduction

## 1.1 Context

In the 1880s Nikola Tesla and Thomas Edison fought their famous *War of Currents*. The result is well known, with the alternating current (AC) winning the final battle over the direct current (DC) and, with a few exceptions, imposing itself as the technology of choice for the widespread deployment of electrical grids around the world over the next century.

Nonetheless, during the 20th century the high-voltage power conversion industry thrived, firstly using mercury arc technology in the early 1950s and later with their solid state replacement, the thyristor valves, from the late 1960s onwards. These devices facilitated the implementation of line commutated converters (LCC) to perform a high voltage AC to DC conversion. Electrical power transmission using DC experienced a resurrection, with the revolutionary high-voltage DC (HVDC) transmission representing a more economical option for bulk, long distance power transmission.

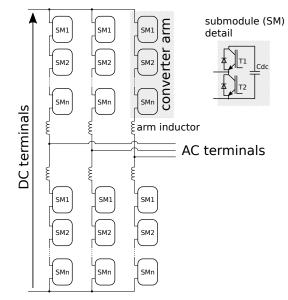

A second revolution in the HVDC market has taken place more recently, with the proposition in the early 2000s of the modular multilevel converter (MMC) concept. The first project to be commissioned using this technology was the Trans Bay Cable in 2010, a submarine DC cable transmission in the San Francisco Bay. With the MMC station power losses getting closer to those of a conventional LCC (around 1% against 0.7%), a smaller station footprint and lower cost, MMC technology has rapidly found its own place in the HVDC market, in particular for the interconnection of offshore wind.

In parallel, the commitments to reduce  $CO_2$  emissions and fight climate change, by reaching at least a 20% renewable energy share by 2020 in Europe, have encouraged investment in renewable energy sources (RES). This has fuelled an incredibly fast deployment of offshore wind generation in Europe with the North Sea being seen as the centre of this activity.

The interconnection of offshore wind farms using submarine cables has found

in HVDC transmission a more economical alternative to conventional HVAC as the distance from shore increases. MMC has found itself as an ideally suited conversion technology for the interconnection of clusters of increasingly larger and more distant offshore wind farms. At the time of writing, 6 such HVDC connections are operational in the North Sea and 3 more are in the commissioning or construction stage, and expected to enter operation in the coming three years.

With power ratings ranging from 400 MW to 916 MW, these HVDC connectors are comparable to conventional power plants. Their integration in the national grids starts posing some basic network security and stability issues, and grid codes have evolved to regulate it. Fault ride-through is one of the principal and most challenging requirements to be observed. A dynamic braking system (DBS), which takes its name from traditional braking choppers in motor drives, is currently included within the onshore MMC station to prevent a transient over-voltage in the HVDC link during a low voltage dip in the onshore AC grid. The term energy diverting converter (EDC) was coined during this research project as a generalization of the DBS concept. An EDC can extract the totality or a fraction of the power flowing through the DC link, and provides the same over-voltage protection with some additional functionality of interest for the operation of the HVDC system.

Since 2007, GE grid solutions (former Areva T&D and Alstom Grid) has been actively engaged in the development of modular multilevel converter (MMC) solutions for the HVDC market. In February 2013 the reward to the R&D efforts arrived in the form of a contract to supply a complete MMC conversion scheme for the Dolwin 3 offshore interconnector in Germany. As part of the deliverables, a dynamic braking solution was to be included within the onshore conversion station to provide the required fault-ride through capability for the interconnector.

## **1.2** Aims and objectives

Therefore, this research work kicked-off with the aim to investigate the design and technical and economic application of Energy Diverting Converters with added functionality. In doing so, the following research objectives were set:

- 1. To compare the technical performance of different electrical circuits suitable for the implementation of a dynamic braking system.

- 2. To develop control and modulation techniques to regulate the power diverted from the HVDC line by each circuit.

- 3. To design and build a low power DC grid in order to experimentally validate the developed control system and modulation techniques.

- 4. To investigate the DBS performance experimentally.

- 5. To explore the potential to implement energy diverting converters, which include extra functionality, in order to increase the DBS attractiveness from a commercial perspective.

## **1.3** Organisation of the thesis

In particular, the outcomes of this work are presented in the different chapters of the thesis as follows:

#### Chapter 2

The chapter reviews the current technical solutions for the connection of offshore wind generation to onshore AC grids. The requirements for the integration into national AC grids of the generated power using HVDC transmission are presented, as well as a review of the existing literature on fault-ride through capability provision for such connections.

#### Chapter 3

The principle and operation of a DBS as well as some general concepts common to all DBS circuits are described. Four implementations of a DBS using different circuits are investigated: the HVDC chopper, the multilevel chopper, the half-bridge multilevel and the full-bridge multilevel circuits. The controlled dissipation of power in the resistive elements requires a different approach in each circuit. A suitable control methodology for each circuit is derived and explained. For the complicated stored energy balancing in the half-bridge and full-bridge circuits the use of trapezoidal modulations is explored in great detail. A comparison of the circuits in terms of device ratings, as well as a trade-off analysis are performed at the end of the chapter.

#### Chapter 4

In order to evaluate the performance of the four DBS circuits and proposed control strategies during a fault ride-through event, simulation models are implemented. This chapter presents the results of these simulations and comments on the technical performance of each circuit and relative merits of the different control strategies.

#### Chapter 5

For a more realistic experimental validation of the control strategies running in digital control hardware, a low-power test platform was built. This chapter describes its physical implementation, with the scaled-down model of an HVDC system as well as the fault triggering mechanism to physically emulate a fault ride-through event. The flexible power cell, distributed control hardware, fibre optics communication, user interface and data logging and display interfaces, all of which was specifically designed by the author for this research project, are also described.

#### Chapter 6

The experimental results obtained with the test platform are presented in the chapter. For each circuit, the platform settings during each test are detailed. The different waveforms, logged during a successful fault ride-through event, are displayed and discussed to validate the performance of each control strategy.

#### Chapter 7

This chapter explores the Energy Diverting Circuits, which integrate some extra functionality that complements the DC over-voltage mitigation. Here the HVDC tapping function has been investigated. The novel circuit topologies developed and required control techniques are also derived and explained.

#### Chapter 8

The last chapter concludes on the findings and contributions made by this research work. A recommendation is also made on further research opportunities arising from the work here presented.

## **1.4** List of publications based on this work

#### Based on Chapters 3 to 6

J. Maneiro, S. Tennakoon, C. Barker, and F. Hassan, "Energy diverting converter topologies for HVDC transmission systems," *Power Electronics* and Applications (EPE), 15th European Conference on, pp. 1–10, Sept 2013.

#### Based on Chapter 7

1. J. Maneiro, S. Tennakoon, and C. Barker, "Scalable shunt connected HVDC tap using the DC transformer concept," *Power Electronics and Applications*

(EPE'14-ECCE Europe), 16th European Conference on, pp. 1–10, Aug 2014. \*Received the Outstanding young EPE member award

- C. Davidson, K. Dyke, J. Maneiro, D. Trainer, and N. Okaeme, "Converter circuit," Patent EP 2 834 896 (B1), May 25, 2016.

- J. Maneiro and C. Barker, "DC/DC converter," Patent EP 2 905 885 (B1), Aug 12, 2015

## **1.5** Thesis contributions

The work presented in this thesis has made a number of contributions which can be summarised as follows:

- Analysis of DBS circuits: The use of DBS for DC over-voltage protection had previously been presented in literature but always from a simplified perspective considering an ideal switch with a series resistor. The author provides in this work a thorough investigation on the working mechanism of four different implementations of a DBS circuit, three of them using modular multilevel structures, in sections 3.2, 3.3, 3.4 and 3.5. Control strategies, not previously disclosed in literature, have been developed in sections 3.2.1, 3.3.1, 3.4.3 and 3.5.3.

- Energy balancing of modular DBS: The key aspect for operating multilevel circuits is the energy balancing. The author has developed a novel modulation strategy based on trapezoidal waveforms to operate DBS circuits using half-bridge and full-bridge cells. These are described in sections 3.4.2 and 3.5.2, where a detailed analysis of the naturally achieved energy balance is also investigated. The full derivation of the presented expressions is included in Appendix A.

- **Circuit dimensioning and trade-offs:** The sizing of the main DBS circuit elements: number and rating of semiconductors, resistors and capacitors, which impacts the required capital expenditure, is analysed in Chapter 3. Design trade-offs, crucial to tailoring the converter design, are identified in section 3.6 for the half-bridge and full-bridge multilevel circuits. These affect the converter's performance in terms of required number of cells, capacitor size, switching frequency, EMI performance and the choice of semiconductor devices. Economical aspects are briefly discussed in section 3.7

- Laboratory test platform: In order to test the designed DBS circuits under FRT conditions, a test set-up was constructed by the author as described in Chapter 5. This allowed for the testing of the DBS circuits with their control strategies implemented in real hardware. Experimental data is obtained and the proposed converter design and control strategies are validated, with all

the results presented in Chapter 6. The entire test platform was fully designed and built by the author for this research project, including PCB design and development of all the communication protocols, PC software to implement the human-machine interface and the firmware for all the control cards.

**Energy Diverting Converters:** The addition of extra functionalities in DBS circuits to implement EDCs had great innovation potential. The result of this work gave place to two patents [1, 2].

Based on the Marx converter principle the author develops the *Cascaded* resonant *DC* transformer circuit in section 7.1.1. A thorough analysis of the operation principle and component sizing for the circuit is performed in the thesis. This work resulted in a publication [3] which received the *Outstanding young EPE member award* by the European Power Electronics and Drives Association and the patent "*DC/DC converter*" [2].

# Chapter 2

# Review of grid integration of offshore wind farms

Global warming due to human greenhouse gas emissions is the most plausible cause behind the accelerated earth surface temperature increase and climate change experienced since the mid  $20^{\text{th}}$  century [4]. International initiatives such as the United Nations Framework Convention on Climate Change, the Kyoto Protocol and more recently the Paris Agreements set targets for a reduction of greenhouse gas emission and mitigation of climate change effects.

Renewable Energy Sources (RES) play a vital role to reach the goals concerning CO<sub>2</sub> emissions reduction. At a European level, the European Union (EU) Renewable Energy Directive, published in 2009, targets 20% of the energy needs to be supplied by RES by 2020. This figure increases to 27% under the new 2030 Framework for climate and energy [5]. These regulations have provided the perfect breeding ground for an exceptional expansion of wind and solar energy in Europe over the last decade. In 2016 for example 86% of all the EU's new installed capacity was from renewables, with a total 21.1 GW of power installed (59.2% wind and 31.8% solar). By the end of 2016, wind and solar power already accounted for 17% and 11% of the EU's total installed power mix respectively, and wind power overtook coal as the second largest form of installed generation capacity. Wind power also covered an impressive 10.4% of the total energy demand in Europe [6]<sup>1</sup>.

Even if onshore plants remain as the main type of installed wind generation capacity, offshore wind is catching up fast. In 2015 for example, offshore

<sup>&</sup>lt;sup>1</sup>Wind Europe, previously known as European Wind Energy Association (EWEA), is a non-profit association gathering together manufacturers, electricity providers, research institutions and universities among others, with the goal of promoting wind power in Europe. References from this organization are used throughout the chapter to provide figures for renewable energy installation and production in Europe. The key figures have been validated with the data available at the European Statistical Office (EUROSTAT) portal: https://ec.europa.eu/eurostat

wind installations more than doubled with respect to 2014, whereas onshore installations decreased by 7.8% [7]. Allowing the use of larger turbine sizes and with stronger and steadier winds, large offshore wind farm (OWF) projects are being commissioned in Europe, with the main focus in the North Sea. This new type of installations require a complete new approach for grid interconnection. Large distances from the shore and the use of submarine cables made the industry turn towards DC transmission. HVDC interconnectors using VSC converters are now the state of the art solution for grid integration of several offshore farms with power ratings approaching now 1 GW.

However the large size of these new interconnections starts posing some basic grid security issues, and grid codes have started to be more strict concerning the operation of such large offshore wind installations. One such aspect covered by grid codes is the fault ride-through (FRT) requirement. A new range of solutions are proposed to provide such capability in HVDC interconnectors, with the dynamic braking systems (DBS) being the preferred solution in current offshore projects. The rest of the chapter gives a critical review of the current state of the technology in this area.

## 2.1 Offshore wind generation

The interest in offshore wind resources is steadily gaining momentum around the globe. The stronger and steadier winds available offshore translate into a higher power production: a 10% in the wind speed theoretically leads to a 33% increase in the wind power reaching the turbine blades according to relation 2.1:

$$P = \frac{1}{2}\rho A V^3 \tag{2.1}$$

Where,

- $\rho$ : air density  $(kg/m^3)$

- A: area covered by the turbine blades  $(m^2)$

- V: wind speed (m/s)

Offshore wind located far from the coast does not generate any noticeable visual or noise pollution, and therefore encounters less opposition from the population. Offshore wind also presents a reduced impact to local fauna, specially concerning birds' habitat disturbance and injury. In addition, some European countries such as Germany, are running out of suitable onshore locations. In Europe offshore wind installations have been steadily growing since the installation of the first OWF in Denmark in 1991 [8]. Fig. 2.1 shows the evolution of the installed capacity in Europe over the last two decades. By the end of 2016, 12.6 GW of offshore wind were connected to the grid in Europe, 72% located in the North sea [9]. The UK and Germany are the two leading countries in terms of installed offshore capacity with 41% and 32.5% share respectively [9]. Fig. 2.2 presents a map of all the current OWF projects in operation and under construction, where the concentration around these two countries is clearly observed.

Fig. 2.1 Evolution of offshore wind power installed capacity in Europe, (Source: The European wind energy association, [7], 2016)

Fig. 2.2 Offshore wind farms in Europe (Source: European commission, [10], 2016).

## 2.2 Grid integration of offshore wind farms

The offshore industry has rapidly evolved towards larger projects in terms of rated power, size of the wind turbine generators (WTG) and distance from the shore in recent years. This evolution has also been accompanied by an adaptation of the electrical interconnection schemes with the onshore AC grids. While in the case of wind locations close to shore, AC submarine cables are still the cheaper option, for projects farther offshore DC has imposed itself as the best suited transmission technology. Fig. 2.3 presents the well known graph where the break-even distance for which DC becomes a more cost effective solution for both overhead line and cable power transmission is presented. However, the exact break-even distance for a particular project depends on a number of factors such as wind conditions, size of the wind farms, cost of energy and others.

In Fig. 2.2 it is observed that most offshore wind projects in Germany are located far away from the coastline. This is the reason why several wind farm interconnections using the HVDC technology have been commissioned and are already in operation. A map of offshore wind interconnection projects in Germany is displayed in Fig. 2.4.

Fig. 2.3 Break-even distance AC against DC.

#### 2.2.1 AC interconnection of offshore wind farms

Power transmission using AC is the most common method in electrical grids, and it was the natural choice as well as a relatively simple and economic way for connecting the first offshore wind projects. The first generation of wind farms commissioned in the 90's were located very close to shore in Denmark and the Netherlands. They also generated relatively low power levels. These first projects relied on medium voltage AC (MVAC) as the transmission technology. As displayed in Fig. 2.5, the generator output voltage is stepped up by a transformer within the turbine to a voltage level in the range of 10-36 kV. This voltage is used

Fig. 2.4 German offshore interconnection projects by Tennet (Source: Tennet, [11], 2014).

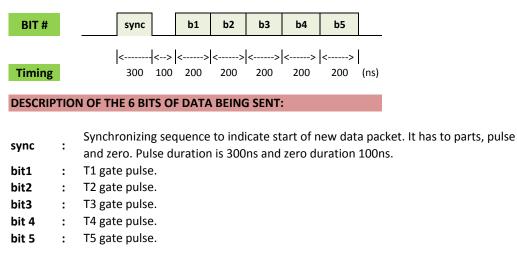

for both the interconnection of the turbines in the arrays and also to export the power to shore. In this way the need for an offshore AC substation on a platform is avoided. One of the largest projects using this technology is the Egmond aan Zee wind farm in the Netherlands, commissioned in 2006 with a power rating of 108 MW and 14 km away from shore.