# A Novel Power-Scalable Wideband Power Amplifier Linearization Technique

by

## Yushi Hu

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2019

© Yushi Hu 2019

## Examining Committee Membership

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

| External Examiner:        | Thomas Johnson<br>Associate Professor, School of Engineering,<br>University of British Columbia                                                                                                                |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Supervisor:               | Slim Boumaiza<br>Professor, Dept. of Electrical and Computer Engineering,<br>University of Waterloo                                                                                                            |

| Internal Members:         | John Long<br>Professor, Dept. of Electrical and Computer Engineering,<br>University of Waterloo<br>David Nairn<br>Associate Professor, Dept. of Electrical and Computer Engineering,<br>University of Waterloo |

| Internal-External Member: | Patricia Nieva                                                                                                                                                                                                 |

| Professor, Dept. of Mechanical and Mechatronics Engineering,<br>University of Waterloo | Aember: Pat | Patricia Nieva                       |        |               |              |

|----------------------------------------------------------------------------------------|-------------|--------------------------------------|--------|---------------|--------------|

| University of waterioo                                                                 |             | Professor, Dept.<br>University of Wa | and Me | echatronics 1 | Engineering, |

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Global mobile traffic is expected to continue to increase at an astonishing rate in the future, due to the ever-increasing number of mobile phone subscribers and the adoption of smart devices which generate significantly more mobile traffic. To satisfy this growth in demand, it is envisioned that future 5th Generation (5G) mobile networks will utilize lower powered small-cell base stations and base stations with large antenna arrays to greatly improve network coverage and capacity. A power amplifier (PA) is a critical component in a base station's transmitter, required to boost the signal power such that it is high enough for transmission to the intended receiver. The design of the PA for 5G base stations, however, presents new challenges to designers.

When driven with modern wideband communication signals, the PA must be both efficient and linear in order to minimize power consumption, improve reliability, maintain transmission accuracy, and avoid interference with neighbouring signals. In conventional high-powered macrocell base station designs, the aforementioned requirements are usually satisfied using a two-step procedure. First, the PA is designed using a Doherty power amplifier (DPA) topology, which has high efficiency, but poor linearity. Then, digital predistortion (DPD) linearization techniques are applied to ensure that the DPA attains the required linearity performance. However, for the lower-powered PAs needed in small cells and large antenna arrays, the relatively high power overhead of DPD techniques, which does not scale down as the power range of the PA decreases, make them unattractive PA linearization solutions.

In response, a new PA linearization technique is proposed and developed in this thesis. It is based on the design and addition of a linearization amplifier (LA), an approach which can help the PA attain the required linearity even when it is driven with modern communication signals with very wide bandwidths. Of particular note, the LA's power consumption is relatively low, it scales with the PA's power range, and it does not increase with signal bandwidth. These qualities make it highly suitable for use with PAs in future 5G small-cell base stations and base stations with large antenna arrays.

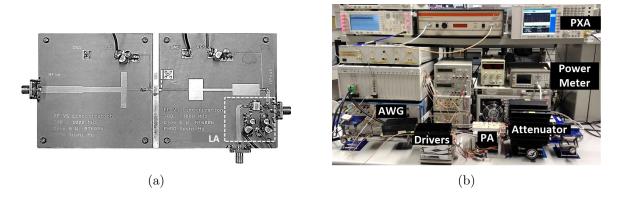

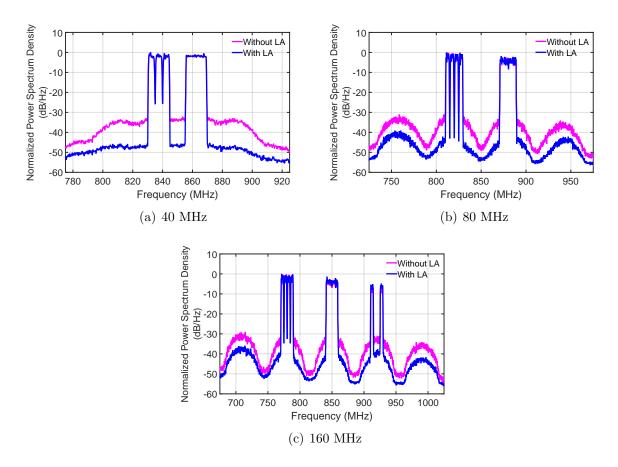

To validate the proposed technique's effectiveness, a prototype circuit was designed, fabricated and applied to a high peak efficiency 6 W class AB PA with a centre frequency of 850 MHz. When stimulated by a wideband 40 MHz signal, the PA's adjacent channel leakage ratio (ACLR) was improved by up to 13 dB after the addition of the LA. This enabled the PA to achieve an ACLR of about -45 dBc without the use of any other linearization techniques. Significant ACLR improvements were also observed for signals with even wider bandwidths of up to 160 MHz. Moreover, it was shown that the LA could

be used in conjunction with a simple predistorter to further improve the efficiency and linearity of the class AB PA.

Next, the LA is augmented with a conventional DPA design to form a new linear DPA topology that was able to achieve a better linearity-efficiency trade-off compared to the linearized class AB PA. To accomplish this, a study of the interactions between the LA and DPA circuitries was conducted and a design strategy was developed to determine the circuit parameters that maximized ACLR improvement while minimizing power consumption. For validation purposes, this strategy was applied to design a proof-of-concept prototype with a centre frequency of 800 MHz and a peak envelope power of 12 W. With the addition of the LA, a more than 11 dB improvement of the ACLR was obtained at the prototype's output when it was driven with signals with up to 40 MHz of modulation bandwidth: an ACLR of about -45 dBc or better was achieved over wide average power range. As expected, the efficiency of the linear DPA topology remained significantly higher than the linearized class AB PA for all signals tested.

Another challenge faced in particular by PAs in a large antenna array, is that it will experience dynamic load impedance variations due to antenna coupling. This unwanted variation in the load impedance can cause instability and significant distortions at the output of the PA that is difficult to remedy using conventional techniques. To address these issues, it is shown in the last part of this thesis that the LA can be used to mitigate this problem by minimizing the amount of load impedance variation seen by the PA due to antenna coupling, such that it remains closer to its optimal value, and by maintaining excellent linearization across a wide range of load impedance values.

#### Acknowledgements

I would like to say how grateful I am to Prof. Slim Boumaiza for giving me the opportunity to conduct research under his supervision during my time as a PhD student. His support, insights and guidance have helped me develop as a researcher during this exciting period of time. Aside from my supervisor, I would also like to thank my committee members, Prof. Johnson, Prof. Long, Prof. Nairn, and Prof. Nieva for reviewing my thesis and providing valuable feedback.

I am very grateful for the generous financial support I received through the Ontario Graduate Scholarship program and the University of Waterloo, and I would like to acknowledge the support of Wolfspeed Inc. and Keysight Inc. for donating the large-signal transistor models and Advanced Design System software, respectively.

Thanks should also go to Yujuan Zhang for providing me with the model of the antenna array used in Section 5.4, and I would like to thank Sarah Wallace, Dr. Hamed Golestaneh, and Dr. Xiao-Hu Fang for proofreading some of the sections of this thesis.

I have been blessed to have wonderful friends during my time as a PhD student, and they have made my life more rich and enjoyable in many ways. For example, their constant support, encouragements, and prayers have given me strength to persevere through the numerous failures I encountered; their willingness to discuss anything with me has helped me grow and laugh; and their constantly asking me when I will be finished with my PhD has helped me become more focused and organized. I look forward to many more years of friendship with all of them.

I was fortunate to be born to great parents who have made countless sacrifices for me. I can never thank them enough. My wife, Dr. Sharon Liang, has been patient with me even when I was stressed and became difficult to deal with. She has helped me become a better person, and I am forever grateful that I am able to share my life with her. I would also like to thank my son, Gabriel Hu, who is the cutest baby in the world. He has been a great source of joy and motivation to me. Last, but certainly not least, I would like to thank God for giving me peace, hope, and purpose throughout this time. None of this would be possible without Him.

# **Table of Contents**

| Li       | st of                  | Table   | s                                                  |     | xi    |

|----------|------------------------|---------|----------------------------------------------------|-----|-------|

| Li       | st of                  | Figur   | es                                                 |     | xii   |

| A        | crony                  | yms     |                                                    | 2   | xviii |

| 1        | Intr                   | oducti  | ion                                                |     | 1     |

|          | 1.1                    | Motiv   | $\operatorname{ration}$                            | · • | 1     |

|          | 1.2                    | Thesis  | s Objective                                        |     | 4     |

|          | 1.3                    | Thesis  | s Outline                                          |     | 5     |

| <b>2</b> | $\mathbf{P}\mathbf{A}$ | Efficie | ency Enhancement and Linearization Techniques      |     | 6     |

|          | 2.1                    | PA Ef   | fficiency                                          |     | 6     |

|          |                        | 2.1.1   | Ideal Field Effect Transistor                      |     | 7     |

|          |                        | 2.1.2   | Efficiency of Conventional PA Topologies           |     | 7     |

|          | 2.2                    | Back-o  | off Efficiency Enhancement Techniques              |     | 10    |

|          |                        | 2.2.1   | Envelope Tracking                                  |     | 10    |

|          |                        | 2.2.2   | Outphasing                                         |     | 11    |

|          |                        | 2.2.3   | Doherty Amplifier                                  |     | 13    |

|          | 2.3                    | PA Di   | istortions                                         |     | 15    |

|          |                        | 2.3.1   | Effects of PA Distortions on Communication Signals |     | 16    |

|   |     | 2.3.2   | Sources of Distortion                                                                | 18 |

|---|-----|---------|--------------------------------------------------------------------------------------|----|

|   |     | 2.3.3   | Additional Sources of Distortions in Back-Off Efficiency Enhance-<br>ment Topologies | 22 |

|   | 2.4 | PA Li   | nearization Techniques                                                               | 25 |

|   |     | 2.4.1   | Feedback                                                                             | 26 |

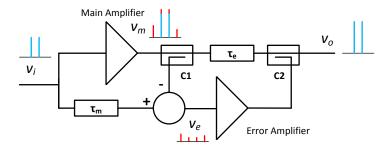

|   |     | 2.4.2   | Feedforward                                                                          | 26 |

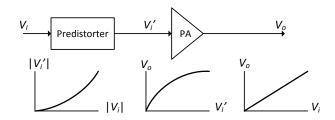

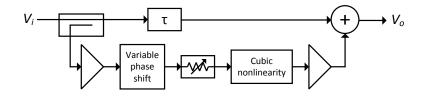

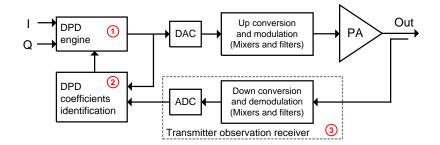

|   |     | 2.4.3   | Predistortion                                                                        | 29 |

|   |     | 2.4.4   | Derivative Superposition                                                             | 31 |

|   |     | 2.4.5   | Circuit Level Linearization Techniques                                               | 32 |

|   | 2.5 | Summ    | ary                                                                                  | 34 |

| 3 | Pow | ver-Sca | alable Wideband PA Linearization Technique                                           | 36 |

|   | 3.1 | Propo   | sed PA Linearization Technique                                                       | 36 |

|   |     | 3.1.1   | Linearity Improvement Mechanisms for Intermodulation Distortions                     | 38 |

|   |     | 3.1.2   | Linearity Improvement for In-band Distortions                                        | 41 |

|   | 3.2 | Linear  | rization Amplifier Design                                                            | 42 |

|   |     | 3.2.1   | LA Realization Using Negative Feedback                                               | 42 |

|   |     | 3.2.2   | Power Consumption of LA and Overall Efficiency                                       | 44 |

|   | 3.3 | Main    | PA and LA Co-design                                                                  | 45 |

|   |     | 3.3.1   | PA and LA design                                                                     | 46 |

|   |     | 3.3.2   | Linearization Analysis Using a Two-tone Input                                        | 46 |

|   |     | 3.3.3   | Linearization Under Modulated Signals                                                | 49 |

|   | 3.4 | Measu   | rement Results                                                                       | 49 |

|   | 3.5 | Joint   | Linearization with RF Predistortion                                                  | 53 |

|   | 3.6 | Concl   | usion                                                                                | 57 |

| 4        | Dol | nerty I | Distortion Reduction Using a Linearization Amplifier                    | <b>58</b> |

|----------|-----|---------|-------------------------------------------------------------------------|-----------|

|          | 4.1 | Propo   | sed Topology                                                            | 58        |

|          |     | 4.1.1   | Linearization Improvement by the Impedance Inverter                     | 59        |

|          |     | 4.1.2   | Correction Current Reduction                                            | 62        |

|          |     | 4.1.3   | Comparison to Linear N-Way DPAs                                         | 63        |

|          |     | 4.1.4   | Effects of LA on Carrier and Peaking Transistors $\ldots \ldots \ldots$ | 64        |

|          | 4.2 | DPA a   | and LA design and Simulation                                            | 68        |

|          |     | 4.2.1   | Linearization with CW Stimulus                                          | 70        |

|          |     | 4.2.2   | Linearization with Two-Tone Stimulus                                    | 73        |

|          |     | 4.2.3   | Linearization Under Modulated Signals                                   | 74        |

|          | 4.3 | Measu   | rements                                                                 | 75        |

|          | 4.4 | Conclu  | usion                                                                   | 80        |

| <b>5</b> | Des | ensitiz | ing the PA to the Effects of Antenna Coupling                           | 82        |

|          | 5.1 |         | na Coupling in Massive MIMO and Its Effects on the PA's Load lance      | 82        |

|          | 5.2 | Analy   | sis of Load Impedance Variation with LA                                 | 84        |

|          | 5.3 |         | rization of Massive MIMO PAs in the Presence of Antenna Coupling the LA | 88        |

|          | 5.4 | Simula  | ated Performance with a Four-Element Array Antenna                      | 90        |

|          |     | 5.4.1   | Performance with Various Input Signal Phases                            | 91        |

|          |     | 5.4.2   | Performance with Various Input Signal Magnitudes                        | 93        |

|          | 5.5 | Conclu  | usion                                                                   | 95        |

| 6        | Cor | nclusio | n                                                                       | 96        |

|          | 6.1 | Summ    | nary of Contributions                                                   | 97        |

|          | 6.2 | Future  | e Work                                                                  | 98        |

|          | 6.3 | List of | f Relevant Publications                                                 | 99        |

| References                   | 100 |

|------------------------------|-----|

| APPENDICES                   | 108 |

| A IMD3 Improvement Breakdown | 109 |

# List of Tables

| 1.1 | Small cells and macrocell base station range and power levels [11]                                   | 3   |

|-----|------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Linear DPA performance                                                                               | 35  |

| 3.1 | Measured PA performance with and without LA at 850 MHz                                               | 52  |

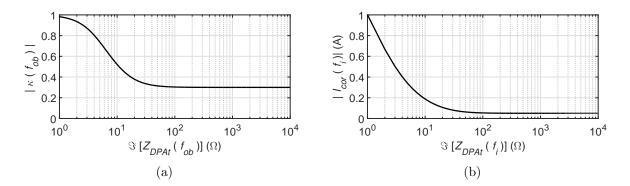

| 4.1 | Maximum Linearity Improvement with the LA                                                            | 78  |

| 4.2 | DPA Performance When -45 dBc ACLR was Achieved $\ \ldots \ \ldots \ \ldots \ \ldots$                 | 79  |

| 4.3 | Comparison with Other Linear DPAs                                                                    | 80  |

| 4.4 | Performance When -45 dBc ACLR is achieved                                                            | 80  |

| A.1 | Calculated and simulated IMD3 reduction with tones at 840 and 860 MHz and an output power of 30 dBm. | 111 |

# List of Figures

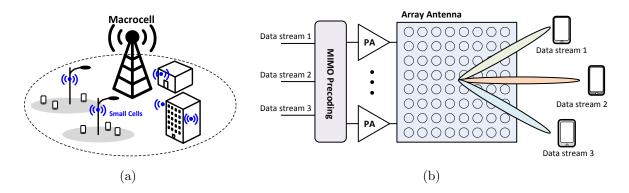

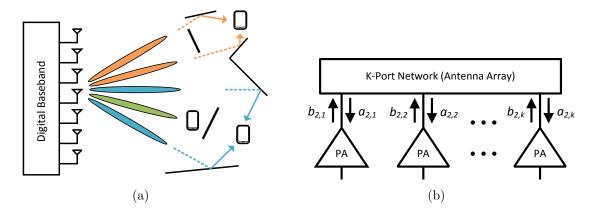

| 1.1  | Illustration of (a) small cells in HetNet and (b) large antenna arrays used<br>in a transmitter in a massive MIMO system                                         | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

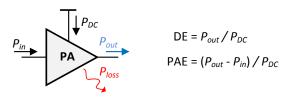

| 2.1  | Illustration of PA efficiency.                                                                                                                                   | 6  |

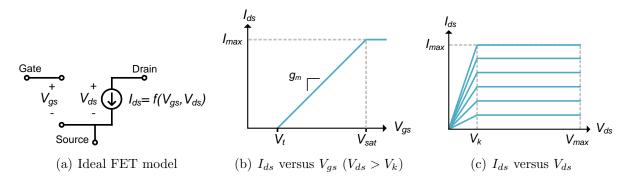

| 2.2  | Ideal FET model characteristic.                                                                                                                                  | 7  |

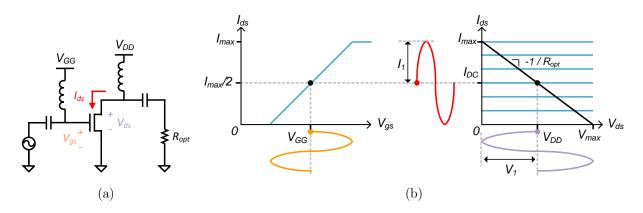

| 2.3  | A (a) simplified class A PA schematic and its (b) gate and drain waveforms with a sinusoidal input. $V_k$ is assumed to be zero to further simplify the analysis | 8  |

| 2.4  | analysis                                                                                                                                                         | 9  |

|      |                                                                                                                                                                  | 9  |

| 2.5  | A (a) simplified class B PA schematic and its (b) gate and drain waveforms with a sinusoidal input. $V_k$ is assumed to be zero to further simplify the          | 0  |

|      | analysis.                                                                                                                                                        | 9  |

| 2.6  | Simplified ET system block diagram.                                                                                                                              | 11 |

| 2.7  | Simplified outphasing system.                                                                                                                                    | 12 |

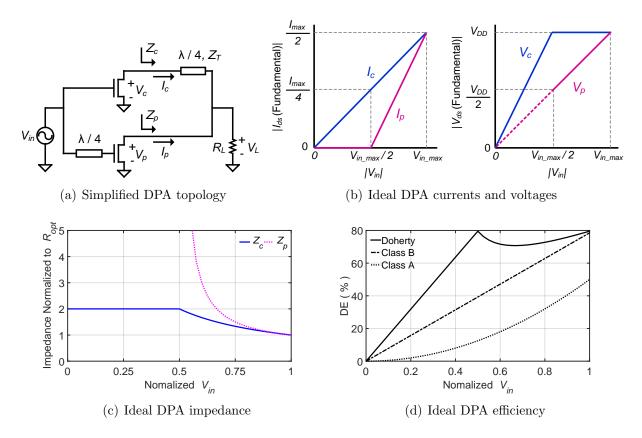

| 2.8  | Simplified DPA topology and its ideal performances.                                                                                                              | 14 |

| 2.9  | Illustration of a) 16-QAM constellation, b) AM-AM and AM-PM of a linear (dashed line) and nonlinear (solid line) PA, and c) error vector.                        | 16 |

| 2.10 | Expected output spectrum distortions with a two-tone input                                                                                                       | 17 |

|      |                                                                                                                                                                  |    |

| 2.11 | Illustration of (a) ACLR and (b) dynamic distortions                                                                                                             | 18 |

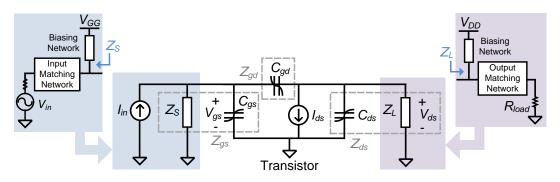

| 2.12 | Simplified PA schematic for quasistatic distortion analysis                                                                                                      | 18 |

| 2.13 | Frequency domain equivalent circuit of the PA                                                                                                                    | 19 |

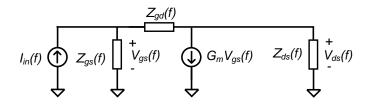

| 2.14 | Simulated (a) $I_{ds}$ versus $V_{gs}$ of a 6 W GaN transistor and its (b) large-signal short-circuit transconductance.                                          | 20 |

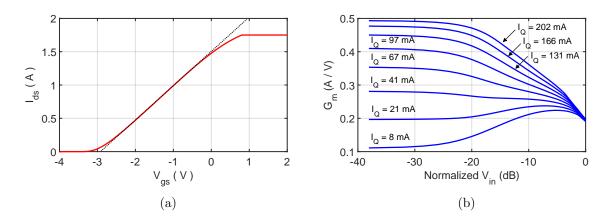

| 2.15 | Simulated (a) $I_{ds}$ versus $V_{ds}$ of a 6 W GaN transistor and (b) an illustration of distortion due to the knee region.                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

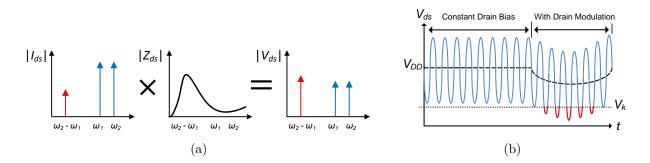

| 2.16 | Illustration of the (a) generation and (b) effects of unwanted low frequency drain modulation                                                                                                                          |

| 2.17 | Variation of the (a) phase and (b) magnitude of DPA gain due to frequency dispersion of the quarter-wave transformer.                                                                                                  |

| 2.18 | Drain voltage of the carrier transistor for various (a) phase and (b) gain offsets between the peaking and carrier transistor current. ( $\Delta \phi$ is how much $\angle I_p$ deviates from its ideal value.)        |

| 2.19 | Illustration of negative feedback                                                                                                                                                                                      |

| 2.20 | Feedforward amplifier configuration                                                                                                                                                                                    |

| 2.21 | Predistortion system configuration.                                                                                                                                                                                    |

| 2.22 | Simplified schematic of a cubic predistorter.                                                                                                                                                                          |

| 2.23 | DPD based transmitter architecture                                                                                                                                                                                     |

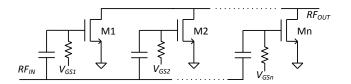

| 2.24 | Simplified schematic of a DS amplifier.                                                                                                                                                                                |

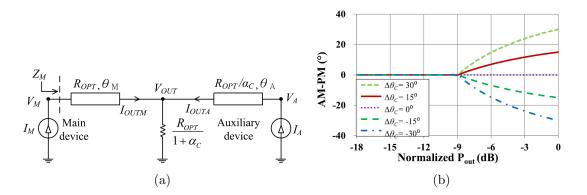

| 2.25 | The a) circuit diagram and b) AM-PM of the DPA proposed in [66]. Reprinted from [66]                                                                                                                                   |

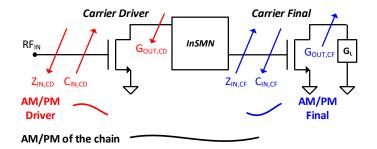

| 2.26 | Graphical representation of the method proposed in [68]. Reproduced from [68]                                                                                                                                          |

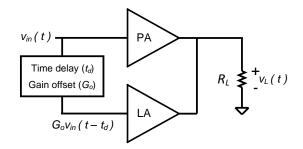

| 3.1  | Simplified topology of the LA and PA.                                                                                                                                                                                  |

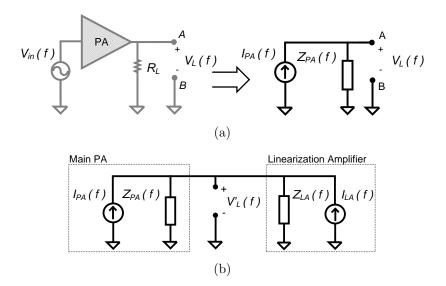

| 3.2  | (a) The PA and its Norton equivalent with the (b) Norton equivalent of the PA and LA                                                                                                                                   |

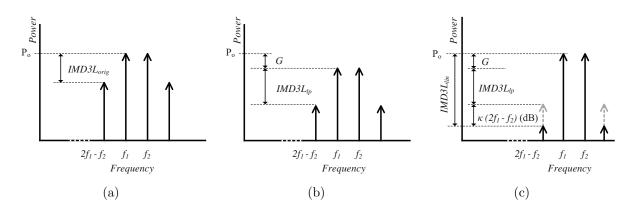

| 3.3  | Expected output frequency spectrum with: (a) an output power of $P_o \mathrm{dBm}$ with PA only, (b) output power of $(P_o - G) \mathrm{dBm}$ with PA only, and (c) output power of $P_o \mathrm{dBm}$ with PA and LA. |

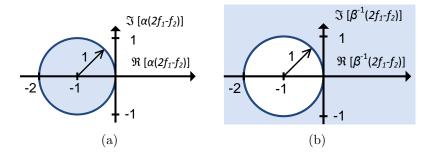

| 3.4  | Desired values for $\alpha(2f_1 - f_2)$ and $\beta^{-1}(2f_1 - f_2)$ are highlighted in (a) and (b), respectively.                                                                                                     |

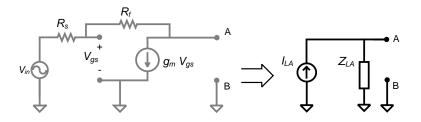

| 3.5  | LA realized through negative feedback and its Norton equivalent                                                                                                                                                        |

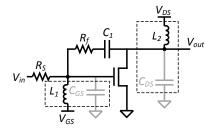

| 3.6  | LA schematic with negative feedback                                                                                                                                                                                    |

| 3.7  | Complete schematic of the PA and LA                                                                                                                                                                                    |

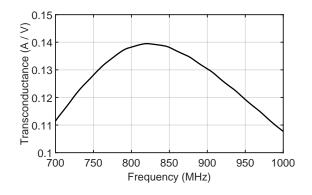

| 3.8  | Simulated small-signal transconductance of the LA                                                                                                                                                                                                                                                                                                       | 47 |

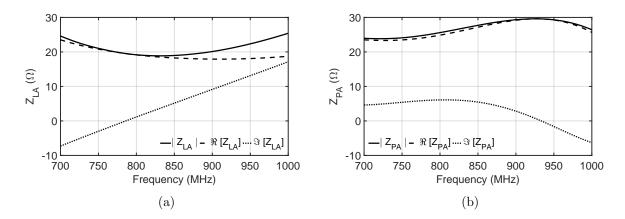

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | Simulated small-signal output impedances of the (a) LA and (b) PA. $\ . \ .$                                                                                                                                                                                                                                                                            | 48 |

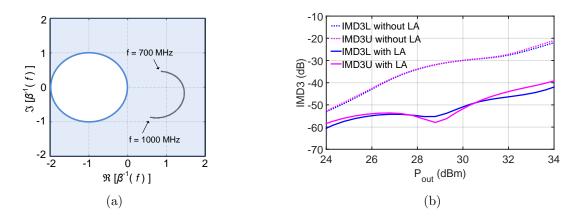

| 3.10 | Simulated a) $\beta^{-1}(f)$ profile and b) IMD3 of the PA with a two-tone input signal with tones 1 and 2 at 840 and 860 MHz, respectively                                                                                                                                                                                                             | 48 |

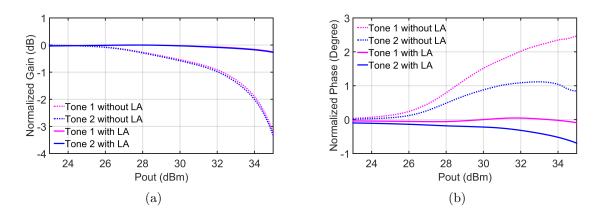

| 3.11 | Simulated and normalized (a) magnitude and (b) phase of the gain of the PA with a two-tone input signal with tones 1 and 2 at 840 MHz and 860 MHz, respectively                                                                                                                                                                                         | 49 |

| 3.12 | Simulated PA output spectrum with a 40 MHz bandwidth modulated signal                                                                                                                                                                                                                                                                                   | 50 |

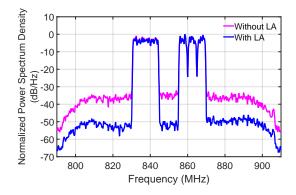

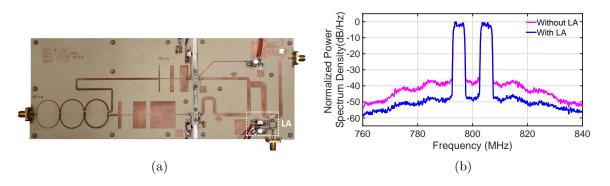

| 3.13 | Photograph of a) fabricated PA with LA and b) measurement setup                                                                                                                                                                                                                                                                                         | 50 |

| 3.14 | Measured PA output frequency spectrum with various modulated signals                                                                                                                                                                                                                                                                                    | 51 |

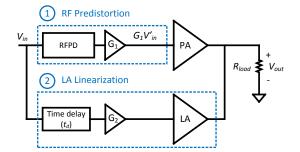

| 3.15 | Topology of joint linearization                                                                                                                                                                                                                                                                                                                         | 53 |

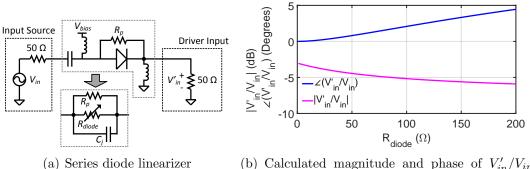

| 3.16 | RF predistorter schematic and calculated performance $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                      | 54 |

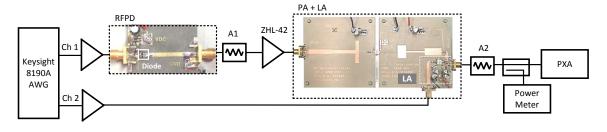

| 3.17 | Diagram of measurement setup                                                                                                                                                                                                                                                                                                                            | 54 |

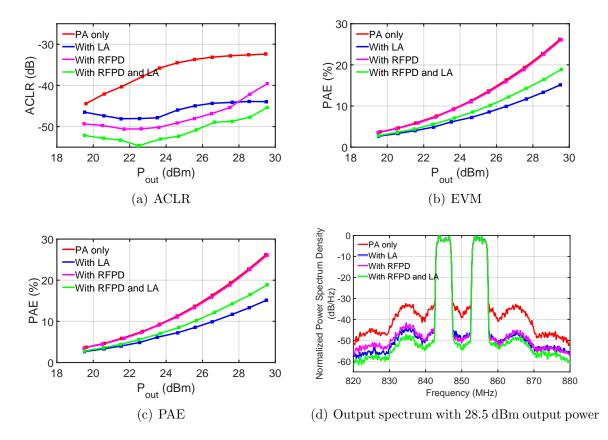

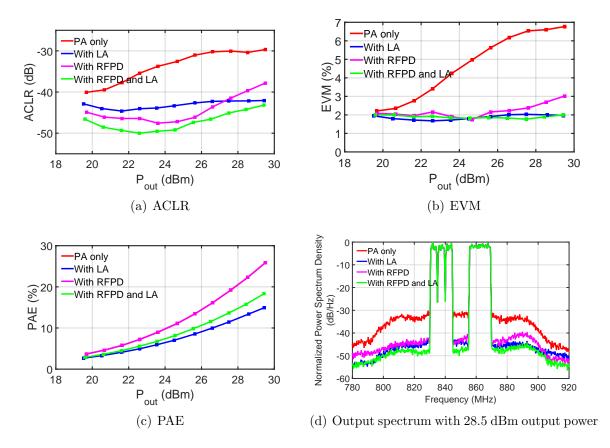

| 3.18 | Measured performance of the different linearization configurations with a 15 MHz WCDMA signal                                                                                                                                                                                                                                                           | 55 |

| 3.19 | Measured performance of the different linearization configurations with a 40 MHz WCDMA signal                                                                                                                                                                                                                                                           | 56 |

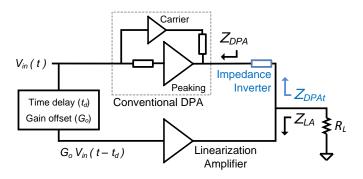

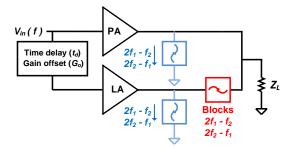

| 4.1  | Block diagram of the linear DPA topology.                                                                                                                                                                                                                                                                                                               | 59 |

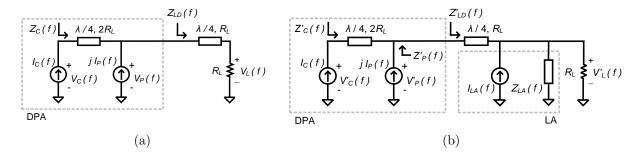

| 4.2  | Equivalent circuit schematic of the DPA (a) without and (b) with the LA.                                                                                                                                                                                                                                                                                | 59 |

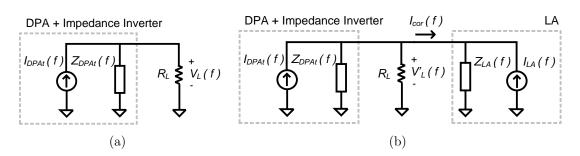

| 4.3  | Calculated a) $ \kappa(f_{ob}) $ for various $Z_{DPAt}(f_{ob})$ values with $Z_{LA}(f_{ob}) = R_L/3$ ,<br>$I_{LA}(f_{ob}) = 0.01 A$ , $R_L = 20 \Omega$ , and $V_L(f_{ob}) = 1V = I_{DPAt}(f_{ob})[Z_{DPAt}(f_{ob})  R_L]$<br>and b) LA correction current for various $Z_{DPAt}(f_i)$ values with $V_L(f_i) - V'_L(f_i) = 1 V$ and $R_L = 20 \Omega$ . | 61 |

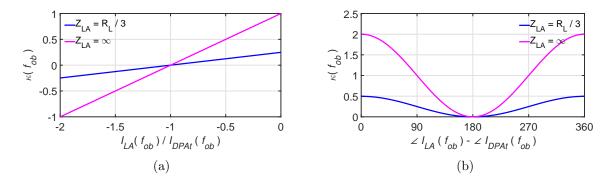

| 4.4  | $\kappa(f_{ob})$ versus (a) $I_{LA}(f_{ob})/I_{DPAt}(f_{ob})$ and (b) phase of $I_{LA}(f_{ob}) - I_{DPAt}(f_{ob})$ (with their magnitudes being equal).                                                                                                                                                                                                 | 63 |

| 4.5  | Equivalent circuit schematic of the DPA (a) without and (b) with the LA.                                                                                                                                                                                                                                                                                | 65 |

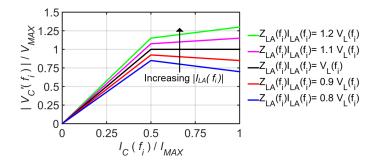

| 4.6  | Calculated $ V'_{C}(f_{i}) /V_{MAX}$ with various magnitudes of $I_{LA}(f_{i})$                                                                                                                                                                                                                                                                         | 65 |

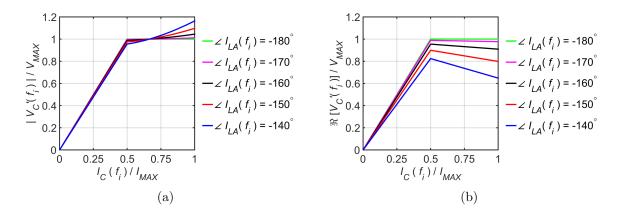

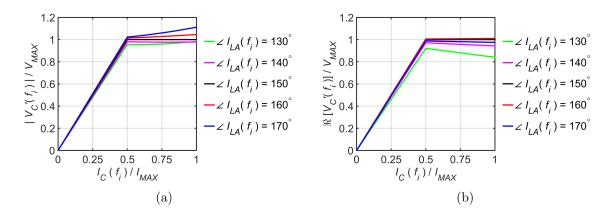

| 4.7  | Calculated (a) $ V'_{C}(f_{i}) /V_{MAX}$ and (b) $\Re[V'_{C}(f_{i})]/V_{MAX}$ with $Z_{LA}(f_{i}) = R_{L}/3$ , phase of $I_{C}(f_{i})$ set to 0°, and various phases of $I_{LA}(f_{i})$ .                                                                                                                                                               | 66 |

| 4.8  | Calculated (a) $ V'_C(f_i) /V_{MAX}$ and (b) $\Re[V'_C(f_i)]/V_{MAX}$ with $ Z_{LA}(f_i)  =  R_L/3 $ , phase of $Z_{LA}(f_i)$ set to 30°, phase of $I_C(f_i)$ set to 0°, and various phases of $I_{LA}(f_i)$ .                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

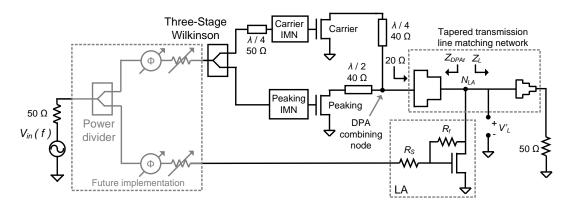

| 4.9  | Simplified schematic of the proposed linear DPA topology                                                                                                                                                                                                                          |

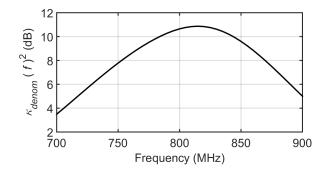

| 4.10 | Simulated $\kappa_{denom}(f)^2$ versus frequency                                                                                                                                                                                                                                  |

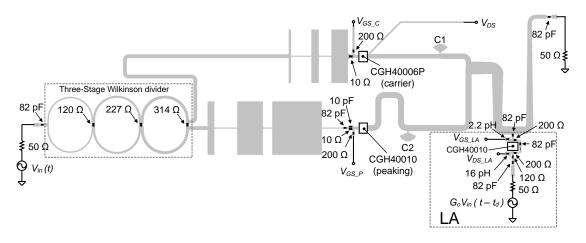

| 4.11 | Schematic of the fabricated linear DPA                                                                                                                                                                                                                                            |

| 4.12 | Simulated phase of $V_L(800 \text{ MHz})$ and $V_L'(800 \text{ MHz})$ for different $t_d$ values.                                                                                                                                                                                 |

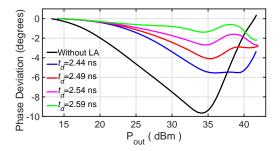

| 4.13 | Simulated (a) PAE, of the linear DPA, with the LA's power consumption factored in, for various $t_d$ values, and the (b) phase of LA's open circuit voltage and $V_L(800 \text{ MHz})$ for different $t_d$ values                                                                 |

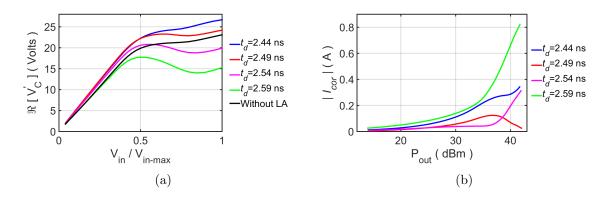

| 4.14 | Simulated (a) real part of $V'_C(800 \text{ MHz})$ and (b) magnitude of the correction current from the LA for different $t_d$ values                                                                                                                                             |

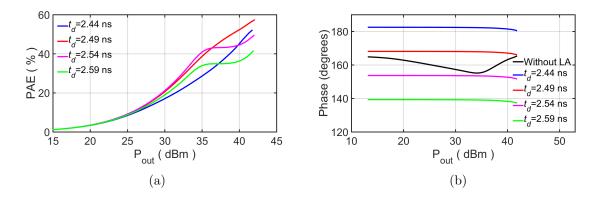

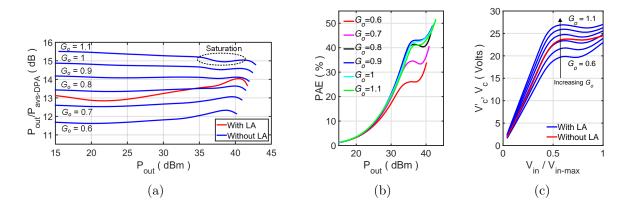

| 4.15 | Simulated (a) $P_{out}/P_{avs-DPA}$ , where $P_{avs-DPA}$ is the power available at the input of the DPA, the (b) DPA's PAE, with the LA's power consumption factored in, for various $G_o$ settings, and (c) the magnitude of $V'_C(800 \text{ MHz})$ for various $G_o$ settings |

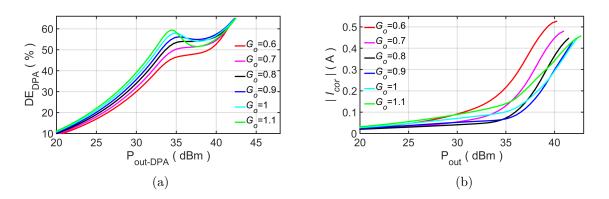

| 4.16 | Simulated (a) DE of the DPA (without the LA consumption), $DE_{DPA}$ , versus the output power of the DPA only (without the power from the LA), $P_{out-DPA}$ and (b) magnitude of the correction current from the LA for different $G_o$ values.                                 |

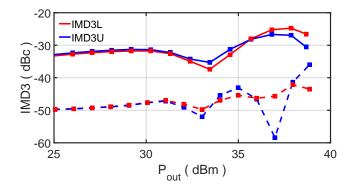

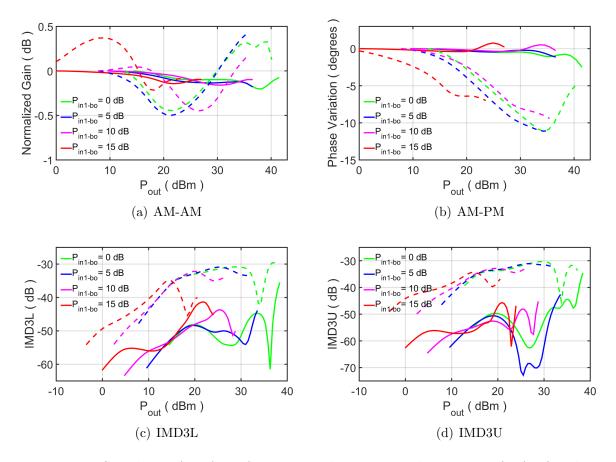

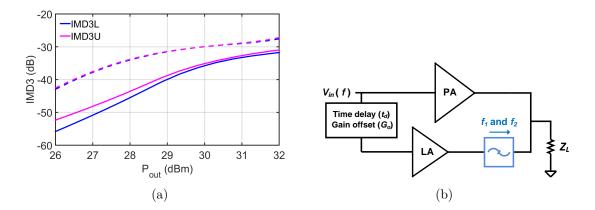

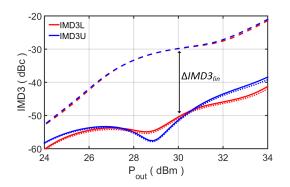

| 4.17 | Simulated IMD3 with (solid line) and without (dashed line) the LA with input tones at 795 and 805 MHz                                                                                                                                                                             |

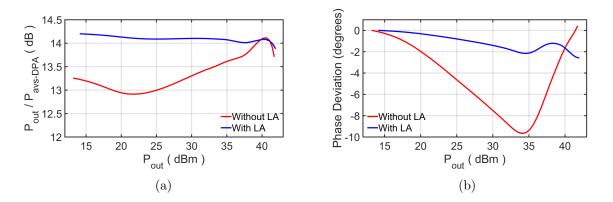

| 4.18 | Simulated (a) $P_{out}/P_{avs-DPA}$ and (b) phase deviation of the output voltage for the case with and without the LA and $t_d$ and $G_o$ of 2.56 ns and 0.9, respectively.                                                                                                      |

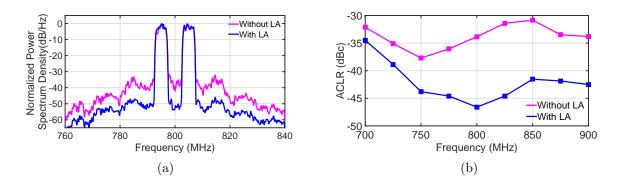

| 4.19 | Simulated DPA (a) output spectrum and (b) output ACLR versus frequency when the DPA is driven by a 15 MHz signal with 8.3 dB PAPR                                                                                                                                                 |

| 4.20 | The (a) picture of fabricated fully analog linear DPA and (b) measured DPA output spectrums when stimulated by a 15 MHz modulation bandwidth signal with 8.3 dB PAPR and 32 dBm output power.                                                                                     |

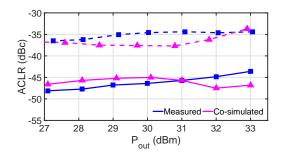

| 4.21 | Measured and co-simulated ACLR when the DPA is stimulated by a 15 MHz modulation bandwidth signal with 8.3 dB PAPR for the case with (solid line) and without (dashed line) the LA.                                                                                               |

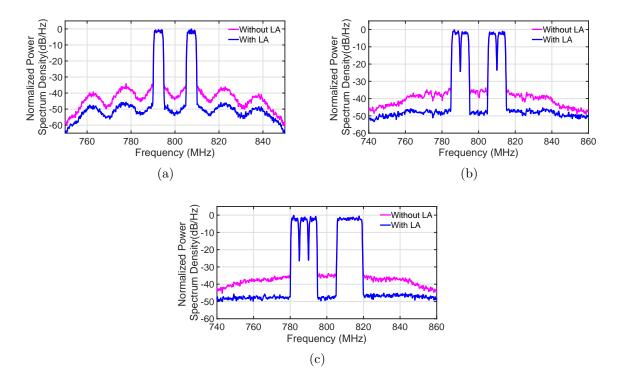

| 4.22 | Measured DPA output spectrums when stimulated by a (a) 20 MHz, (b) 30 MHz and (c) 40 MHz WCDMA signal at the average output power level were -45 dBc of ACLR is achieved.                                                                                                | 76 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

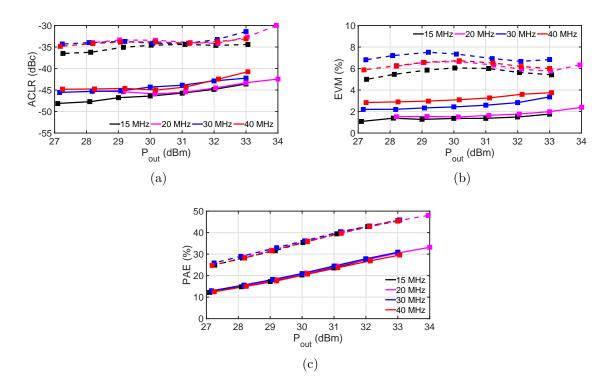

| 4.23 | Measured (a) ACLR, (b) EVM, and c) PAE of the DPA with (solid line) and without (dashed line) the LA versus average output power. Note that the PAE figures with LA include the power consumption of the LA                                                              | 77 |

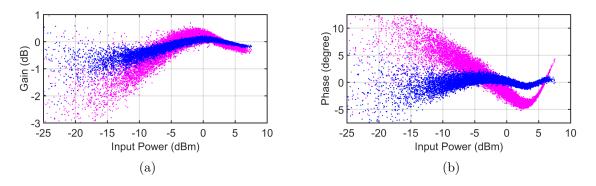

| 4.24 | Measured (a) gain and (b) phase distortion when stimulated by a 15 MHz WCDMA signal for the case with (blue) and without (magenta) the LA. $$ .                                                                                                                          | 79 |

| 5.1  | Illustration of a) digital beamforming reproduced from [8], where different colors represent different signals, and b) an antenna array with multiple PAs reproduced from [73].                                                                                          | 83 |

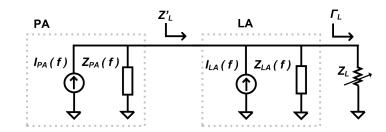

| 5.2  | Equivalent circuit of the PA and LA used for load impedance variation analysis.                                                                                                                                                                                          | 84 |

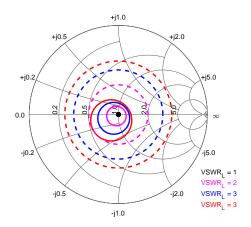

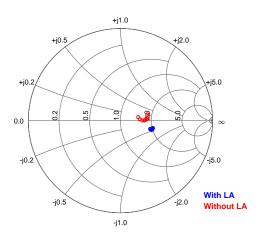

| 5.3  | Calculated $Z'_L$ (solid line) and $Z_L$ (dashed line) for various $VSWR_L$ values.<br>The impedances are plotted on a Smith chart that is normalized to $Z_{Lo}$ .                                                                                                      | 86 |

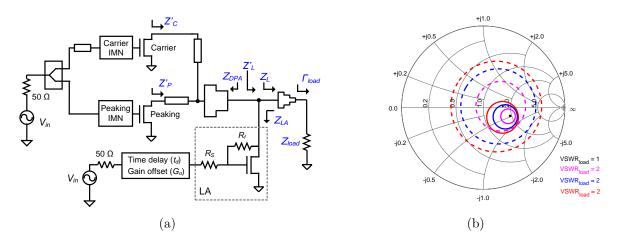

| 5.4  | The (a) topology of the DPA and LA and the (b) simulated carrier transistor impedances for various $VSWR_{load}$ values for the case with (solid line) and without (dashed line) the LA. The impedances are plotted on a Smith chart that is normalized to 50 $\Omega$ . | 86 |

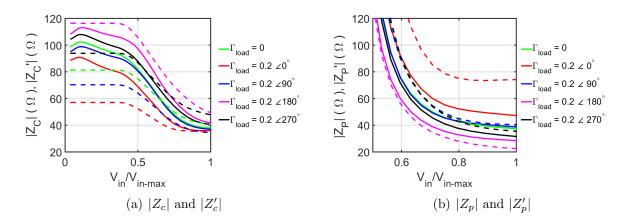

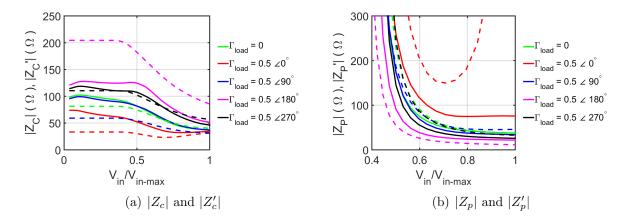

| 5.5  | Simulated impedance seen by the (a) carrier and (b) peaking transistor for the case with (solid line) and without (dashed line) the LA and $ \Gamma_{load}  = 0.2$ .                                                                                                     | 87 |

| 5.6  | Simulated impedance seen by the carrier and peaking transistor for the case with (solid line) and without (dashed line) the LA and $ \Gamma_{load}  = 0.5.$                                                                                                              | 87 |

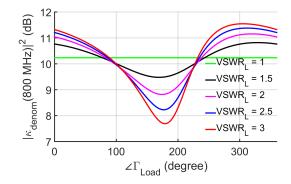

| 5.7  | Calculated $ \kappa_{denom}(800MHz) ^2$ for various $VSWR_L$ values                                                                                                                                                                                                      | 88 |

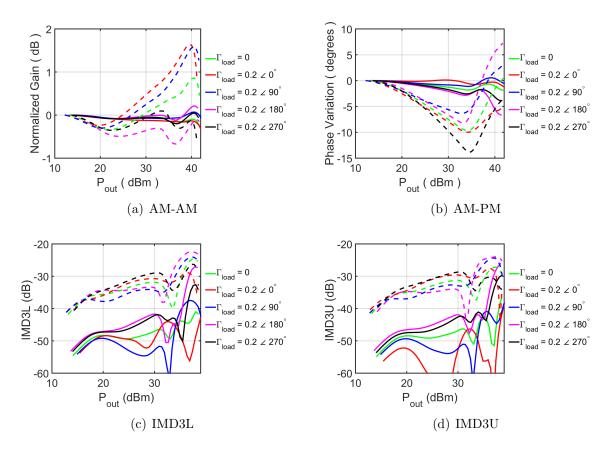

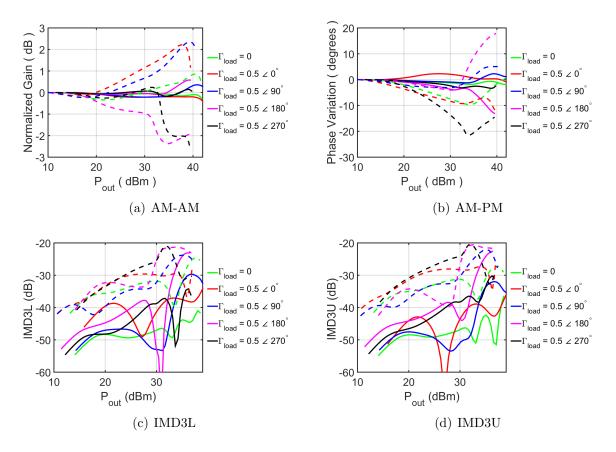

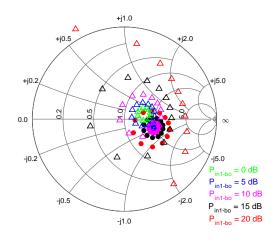

| 5.8  | Simulated AM-AM, AM-PM, and IMD3s across $Z_{load}$ for the case with (solid line) and without (dashed line) the LA                                                                                                                                                      | 89 |

| 5.9  | Simulated AM-AM, AM-PM, and IMD3s across $Z_{load}$ for the case with (solid line) and without (dashed line) the LA                                                                                                                                                      | 90 |

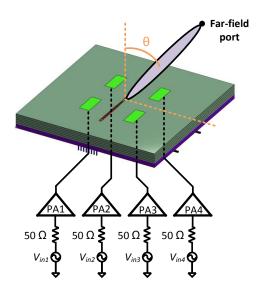

| 5.10 | Illustration of the simulation setup used to observe the performance of an $2 \times 2$ array antenna at a far-field point                                                                                                                                               | 91 |

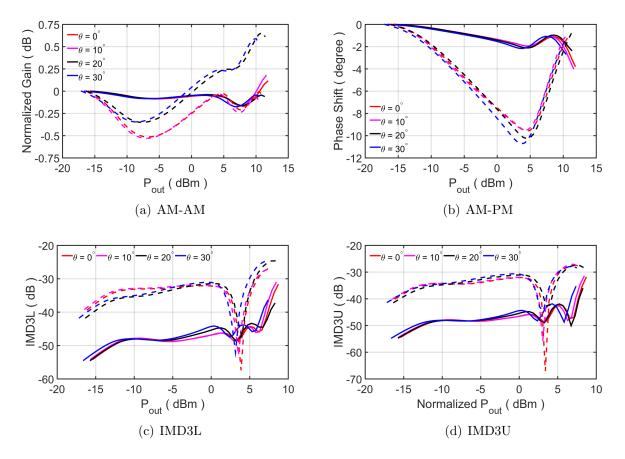

| 5.11 | Simulated AM-AM, AM-PM, and IMD3s at the far-field port for the case with (solid line) and without (dashed line) the LA for various beam angles.                                                                                                                         | 92 |

| 5.12 | Impedance seen by the carrier transistor in the array antenna PAs for the case with and without the LA as $\theta$ is swept from zero to 30° in steps of 10°.                                                     | 93  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.13 | Impedance seen by the carrier transistor in the PA1 for the case with (circle) and without (triangle) the LA for various $P_{out1-bo}$ and $\angle V_{in1}$ values                                                | 93  |

| 5.14 | Simulated AM-AM, AM-PM, and IMD3s at the output of PA1 for the case with (solid line) and without (dashed line) the LA for various $V_{in1}$ magnitudes. $\angle V_{in1}$ was set to 180° for this test           | 94  |

| A.1  | 860 MHz, respectively, for the case with (solide line) and without (dashed line) the LA and filter, and an b) illustration of the setup used for the                                                              | 110 |

| A.2  | Simulation setup used to find the PA and LA's Norton currents at the IMD3 frequencies                                                                                                                             | 110 |

| A.3  | Simulated IMD3L and IMD3U with tones 1 and 2 at 840 MHz and 860 MHz, respectively, for the case with (solid line) and without (dashed line) the LA. Also plotted is the calculated IMD3L and IMD3U (short dashes) | 111 |

## Acronyms

5G 5th Generation.

ACLR adjacent channel leakage ratio.

**ADS** Advanced Design System.

**AM-AM** amplitude-to-amplitude.

$\mathbf{AM-PM}$  amplitude-to-phase.

AWG arbitrary waveform generator.

${\bf CMOS}$  complimentary metal-oxide-semiconductor.

**CW** continuous wave.

DC direct current.

**DE** drain efficiency.

**DPA** Doherty power amplifier.

**DPD** digital predistortion.

**DS** derivative superposition.

EA envelope amplifier.

**EM** electromagnetic.

**ET** envelope tracking.

EVM error vector magnitude.

**FET** field-effect transistor.

FFW Feedforward.

GaN gallium nitride.

**IC** integrated circuit.

**IMD** intermodulation distortions.

IMD2 second-order intermodulation distortion.

IMD3 third-order intermodulation distortion.

IMD3L lower third-order intermodulation distortion.

IMD3U upper third-order intermodulation distortion.

IMD5 fifth-order intermodulation distortion.

LA linearization amplifier.

LTE Long-Term Evolution.

MIMO multiple-input, multiple-output.

MMIC monolithic microwave integrated circuit.

**mmWave** millimeter wave.

**PA** power amplifier.

**PAE** power added efficiency.

**PAPR** peak-to-average power ratios.

**PDF** probability distribution function.

**QAM** quadrature amplitude modulation.

**RF** radio frequency.

${\bf RFPD}~{\rm RF}$  predistortion.

$\mathbf{TOR}\xspace$  transmitter observation receiver.

$\mathbf{VSWR}\,$  voltage standing wave ratio.

WCDMA Wideband Code Division Multiple Access.

## Chapter 1

## Introduction

## 1.1 Motivation

Currently, there are more than 5 billion unique mobile phone subscribers in the world. This means that more than two-thirds of the world's population now has a mobile subscription and can access a mobile network. It is easy to see why mobile networks have become such an integral part of our lives. For example, they have allowed us to stay connected with each other and access the internet across a very wide geographic area. In the future, it is expected that the number of mobile subscribers will continue to increase, reaching 5.9 billion by the year 2025 [1]. At the same time, more and more mobile users are adopting smart devices like smartphones, which generate significantly more mobile traffic compared to basic-featured cell phones because they allow the users to enjoy a variety of bandwidthhungry mobile applications such as video streaming. For instance, an average smartphone in 2018 uses about 5.6 GB of data per month, and it is estimated that this number will increase to 21 GB per month by the end of 2024 due to increased video viewing time, more embedded video content, and higher video resolutions with more demanding formats (e.g., augmented/virtual reality) [2]. Both the rising number of smartphone users and the increasing data usage by these smart devices have driven global mobile traffic to grow at an astonishing rate. According to a report by Ericsson, global mobile data traffic in Q3 2018 grew close to 79 percent year-on-year, and is expected to be five times higher, reaching 136 exabytes per month by the end of 2024 [2].

In response, mobile networks have had to evolve rapidly to accommodate this explosive growth in data traffic. At present, mobile networks are moving towards a heterogeneous solution, termed HetNet where small-cell base stations (small cells) are deployed alongside

Figure 1.1: Illustration of (a) small cells in HetNet and (b) large antenna arrays used in a transmitter in a massive MIMO system.

traditional macrocell base stations to improve network coverage and capacity [3]. Compared to macrocell base stations, small cells are smaller, shorter ranged, lower powered, less expensive, and can be more easily installed. This allows them to be sited in densely populated urban areas to improve network capacity (more cells covering fewer users), and in areas not covered by the macrocell base stations (such as certain rural or indoor areas) to improve network coverage. Another advantage of using small cells is that the average distance between the user and the base station is now shorter. This helps to improve both the data rate and energy efficiency [4].

The addition of small cells alone, however, is not enough to satisfy the orders of magnitude increase in mobile data traffic predicted for the future. Hence, it has been envisioned that 5th Generation (5G) systems will make use of massive MIMO technology at sub-6-GHz frequencies to enable each base station to serve multiple, spatially separated users using the same time and frequency resource. By doing this, the capacity of the network will be increased without requiring additional base stations or spectrum [5]. Massive MIMO technology relies on the use of a large number of antennas in an antenna array to accomplish spatial multiplexing where each spatial channel carries independent information as illustrated in Fig. 1.1(b). It is also anticipated that 5G systems will expand into the underutilized millimeter wave (mmWave) frequencies where a large amount of spectrum is still available [6]. This will allow service providers to significantly increase their channel bandwidth, translating to higher data transfer rates. A key enabler for mmWave transmission is the use of massive MIMO systems with large antenna arrays to focus the transmitted signal into a narrow beam aimed at the user. This could effectively increase the gain of the transmitting and receiving antennas and partially overcome the higher path-loss at

| Cell Type  | Cell Radius (km) | Output Power (W) |

|------------|------------------|------------------|

| Pico Cell  | 0.1 to 0.2       | 0.25 to 1        |

| Micro Cell | 0.2 to 2         | 1 to 10          |

| Macro Cell | 8 to 30          | 10  to  >50      |

Table 1.1: Small cells and macrocell base station range and power levels [11]

mmWave frequencies [7]. Note that, compared to sub-6-GHz massive MIMO systems, it is anticipated that mmWave massive MIMO systems will use analog/hybrid beamforming instead of full digital beamforming. This means mmWave massive MIMO will be less flexible and will have lower user multiplexing capability [8].

Notice from Fig. 1.1(b) that in a large antenna array, each antenna needs to be driven by a power amplifier (PA). The PA is a critical component in a base station's transmitter because it is used to boost the power of the communication signal such that it is high enough for transmission to the receiver. The PA must operate efficiently, as they are the largest energy consumer in the transmitter chain. Furthermore, they should operate linearly in order to minimize signal distortion and interference with signals in neighbouring frequency bands. To achieve both these goals, a two-step procedure is usually taken. Firstly, the PA is designed using topologies or classes of operation which optimize peak power and back-off power efficiency at the cost of linearity. It is important for the PA to have high efficiency at power back-off because modern communication signals have high peak-to-average power ratios (PAPR) [9]. As a result, the PA is expected to operate in back-off power the majority of the time. Then, linearization techniques are introduced to ensure that the PA attains the required linearity performance. Predistortion techniques, in particular digital predistortion (DPD) variations [10], have become the preferred linearization approach for high powered macrocell base station PAs. These approaches have benefited from advancements in digital signal processors and allow for excellent linearization.

The recent trend towards small cells and large antenna arrays, however, means that the PAs will now be lower powered than those in conventional macrocell base stations. This could render existing DPD techniques unattractive due to the relatively high power overheads that do not scale down with power range. To illustrate this point, the typical cell radius and PA power of several different categories of small-cell and macrocell base stations are given in Table 1.1. The base station's output power can vary from tens and hundreds of watts for a macrocell down to a few watts for a pico or micro cell. Now, a typical DPD system can require a few watts of power consumption [12]. So, it would not significantly decrease the efficiency of a high powered macrocell PA because its power consumption is small compared to the macrocell's output power. However, for low powered PAs the power consumption of DPD becomes relatively large and would significantly decrease the PA's overall efficiency, giving a poor trade-off between linearity and efficiency. This problem is exacerbated when we consider using DPD to linearize large antenna array systems. Firstly, the power range of the PAs in a large antenna array is further reduced. The greater the number of antennas, the lower the power required from each PA. Secondly, the cost of DPD would be multiplied by the number of PAs in the system if each PA is linearized using DPD. Lastly, DPD techniques for large antenna array systems must be even more complex because, in addition to the nonlinearity of each PA, the coupling between the antennas add another source of distortion in the antenna array system that must be mitigated by the DPD in order to attain the required linearity.

### 1.2 Thesis Objective

In light of the fact that conventional linearization techniques used for macrocell PAs are no longer attractive for PAs in small cells and large antenna arrays, the objective of this thesis is to develop a PA linearization technique which is more suitable for these emerging applications. The following steps will be taken towards the achievement of this goal:

- 1. Develop a novel linearization technique which possesses the following attributes:

- Its power consumption should be relatively low and *scalable* compared to the PA's output power. In other words, the power consumption of the linearization circuitry should decrease as the power range of the PA decreases. This ensures that the overall efficiency of the PA is not degraded when the power range of the PA is scaled down.

- It should enable the PA to meet the linearity requirements of modern communication standards when driven with wideband signals.

- 2. Verify the new linearization technique by developing a design strategy and applying it to a conventional class AB PA as a proof of concept.

- 3. Develop a design strategy to apply the proposed linearization technique to a high back-off efficiency Doherty power amplifier (DPA) topology to further improve the PA's linearity-efficiency trade-off.

- 4. Investigate the proposed technique's capacity to counter the unwanted effects of coupling between the antennas in a large antenna array system.

## 1.3 Thesis Outline

Chapter 2 shows that conventional PA designs will have low efficiency when driven with modern communication signals, highlighting the need for PA topologies with high efficiency at power back-off. An overview of some popular back-off efficiency enhancement topologies are given here. The effects and sources of PA distortions are also briefly discussed, to emphasize the importance of PA linearization techniques, and an overview of existing PA linearization techniques is provided.

Chapter 3 introduces a novel PA linearization technique suitable for low powered PAs that is based on the design and addition of a linearization amplifier (LA). The technique is analyzed in detail and used to linearize a class AB PA. The design of a proof of concept prototype is also presented, and measurement results of the prototype are shown to validate the technique's effectiveness. In addition, a joint-linearization setup is created by using the LA in conjunction with a simple predistorter, and measurement results demonstrate that the joint-linearization configuration is able to further improve linearity and reduce power consumption.

In Chapter 4, the LA is augmented with a high back-off efficiency DPA topology to form a new linear DPA topology. A study of the interaction between the LA and the DPA is detailed here, as well as the design method developed from the study. The design of a proof-of-concept prototype is also presented, and measurement results show that the new linear DPA topology is capable of achieving high efficiency and linearity when stimulated by wideband modulated signals.

Next, in Chapter 5, the LA is studied for its capacity to remedy the unwanted dynamic load impedance variations caused by antenna coupling in large array antennas. Initial simulation results are provided to validate the analysis.

Finally, Chapter 6 concludes the thesis by summarizing the contributions of this work and discussing possible directions for future research.

## Chapter 2

# PA Efficiency Enhancement and Linearization Techniques

### 2.1 PA Efficiency

The power efficiency of the PA characterizes how well it converts the power supplied to it into useful output signal power. This is a critical design parameter because the PA is one of the largest power consumers in the transmitter, and a low efficiency PA can consume an excessive amount of power. Furthermore, the wasted energy is converted into heat which can reduce the PA's reliability and require additional cooling. One common measure of power efficiency is drain efficiency (DE), defined as the ratio between the desired output signal power  $P_{out}$  to the input DC power  $P_{DC}$ . Another measure of power efficiency, power added efficiency (PAE), also takes into consideration the input signal power  $P_{in}$ . The two measures of efficiency are given in Fig. 2.1. For the analysis in this section it will be assumed that the PA's gain is high such that  $P_{out} \approx P_{out} - P_{in}$ . Hence, the two efficiency measures converge, and DE alone can be used to characterize efficiency.

Figure 2.1: Illustration of PA efficiency.

Figure 2.2: Ideal FET model characteristic.

#### 2.1.1 Ideal Field Effect Transistor

The field-effect transistor (FET) is the most common transistor used in base station PA designs, and the efficiency analysis in this section will use, for simplicity and clarity, the ideal FET model shown in Fig. 2.2(a) [13]. The relationship between the gate source voltage  $(V_{gs})$  and drain source current  $(I_{ds})$  is given in Fig. 2.2(b) for a drain source voltage  $(V_{ds})$  greater than the knee voltage  $V_k$ . As can be seen, when  $V_t < V_{gs} < V_{sat}$ , where  $V_t$  is the threshold voltage, the ideal transistor behaves as a voltage-controlled current source with a transconductance of  $g_m$ . Unlike small-signal amplifiers, the PA is designed to utilize the maximum current and voltage swing of a transistor. Hence, the saturation current  $(I_{max})$ , breakdown voltage  $(V_{max})$ , as well as  $V_k$  are specified. For efficiency analysis,  $V_k$  will be assumed to be zero to further simplify the analysis.

In reality, the transistor will include parasitic elements,  $g_m$  is not constant,  $V_k$  is not zero, and the input and output impedances are not infinite. These nonidealities will be become more critical when we look at the sources of PA distortions later on in Section 2.3.2.

#### 2.1.2 Efficiency of Conventional PA Topologies

**Class A** One of the simplest PA topologies is the class A PA. The schematic of the class A PA and its waveforms with a sinusoidal input are shown in Fig. 2.3. Notice that the gate  $(V_{GG})$  and drain  $(V_{DD})$  bias are set such that the direct current (DC) current and voltage at the drain are  $I_{max}$  and  $V_{max}/2$ , respectively, and the load resistance  $R_{opt}$  is set to  $V_{max}/I_{max}$  to ensure maximum  $V_{ds}$  swing and, therefore, maximum possible output power from the transistor. The DC power consumption  $(P_{DC-A})$  and output power  $(P_{out-A})$  of

Figure 2.3: A (a) simplified class A PA schematic and its (b) gate and drain waveforms with a sinusoidal input.  $V_k$  is assumed to be zero to further simplify the analysis.

the class A PA can be found to be  $V_{max}I_{max}/4$  and  $V_1I_1/2$ , respectively, where  $V_1$  and  $I_1$  are the amplitudes of  $V_{ds}$  and  $I_{ds}$ , respectively, at the sine wave frequency. Then, the DE of the class A PA  $(DE_A)$  can be derived to be

$$DE_{A} = \frac{P_{out-A}}{P_{DC-A}} = \frac{2V_{1}I_{1}}{V_{max}I_{max}}.$$

(2.1)

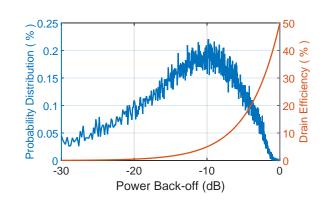

The efficiency of the class A PA is highest at maximum output power  $(V_1 = V_{max}/2, I_1 = I_{max}/2, \text{ and } DE_A = 50\%)$ . At power back-off, the DE of the class A PA will decrease linearly with output power. The reason why DE drops so quickly is because  $P_{DC-A}$  stays constant regardless of its output power. In fact,  $P_{DC-A}$  stays constant at  $V_{max}I_{max}/4$  even when there is no output power. The DE of a class A PA is next plotted versus power back-off in Fig. 2.4 as well as the probability distribution function (PDF) of a 20 MHz Wideband Code Division Multiple Access (WCDMA) signal with 7.6 dB PAPR. Notice how the majority of the signal is at large power back-off, where the efficiency of the PA is low, and the expected DE can be found to be 9.6% when this WCDMA signal is transmitted through a class A PA. This means that for a mere 1 W of output power more than 10 W of DC power is required by the PA, and more than 9 W of power is wasted.

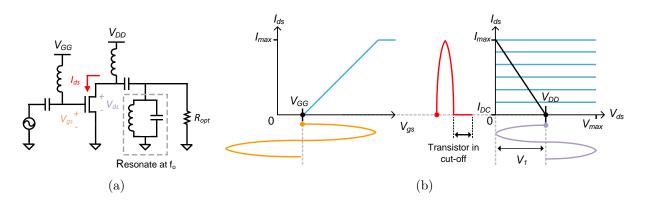

**Class B** The gate bias of the PA can be reduced to improve the PA's peak efficiency performance, leading to more efficient PA operation classes such as the Class B PA. A simplified schematic of a class B PA and its waveforms with a sinusoidal input are shown in Fig. 2.5.  $V_{GG}$  is now set such that the DC value of  $I_{ds}$  is zero when there is no signal input, and as a result, the transistor will only conduct for half of the signal period. This is

Figure 2.4: Class A DE with the PDF of a 20 MHz WCDMA signal with 7.6 dB PAPR.

Figure 2.5: A (a) simplified class B PA schematic and its (b) gate and drain waveforms with a sinusoidal input.  $V_k$  is assumed to be zero to further simplify the analysis.

what enables the class B PA to attain a higher efficiency, but  $I_{ds}$  will now have significant components at harmonic frequencies which should be shorted using, for example, a tank circuit with a resonant frequency at the fundamental frequency  $f_o$ .

The DE of the class B PA can be found through Fourier analysis of the  $I_{ds}$  waveform. The relationship between the amplitude of the fundamental frequency and DC component of  $I_{ds}$  ( $I_{DC}$ ) can be found to be  $I_1/I_{DC} = \pi/2$ , and the DE of the class B PA can be expressed as

$$DE_B = \frac{(V_1 I_1)/2}{V_{DC} I_{DC}} = \frac{\pi}{4} \frac{V_1}{V_{DC}} = \frac{\pi}{4} \frac{V_1}{V_{max}/2}.$$

(2.2)

At peak output power,  $V_1 = V_{max}/2$ , and the DE of the class B PA is 78.5%. This is a significant improvement from the class A PA (50%). Moreover, notice that the class B

PA's DE does not decrease linearly with power as does the class A PA. Rather, it decreases linearly with  $V_1$ , which is proportional to the square root of the output power. If we use a class B PA to amplify the WCDMA signal (whose PDF was shown in Fig. 2.4), we can expect a DE of about 38.4%. This means that the class B PA would consume four times less power than the class A PA.

Class AB and class C PAs also have a lower gate bias, and as a result, better efficiency than the class A PA. The class C PA is even more efficient than the class B PA, but it has the poorest linearity, gain, and maximum output power. The class AB PA, on the other hand, has a higher gain than the class B PA, but it has a lower efficiency. See [14] for a more detailed discussion and comparison between these classes of operation.

### 2.2 Back-off Efficiency Enhancement Techniques

We saw in the previous subsection that the DE of the PA at power back-off can be improved by going to different classes of operation (for example, from class A to class B). The back-off efficiency of these conventional PAs can be further improved using the back-off efficiency enhancement techniques we will discuss next.

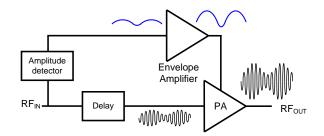

#### 2.2.1 Envelope Tracking

Notice from Eq. (2.2) that if  $V_{DC}$  can be made to decrease with  $V_1$ , such that they are always equal, then DE of a class B PA can be maintained at 78.5% at all output powers. This is the basic idea behind drain modulation techniques where the drain bias of the PA's transistor is modulated with the envelope of the signal to improve power back-off efficiency. The envelope tracking (ET) technique is one of the more popular drain modulation techniques, and a block diagram of the ET system is given in Fig. 2.6. Drain modulation in the ET system is achieved through an envelope amplifier (EA) which modulates the drain supply voltage of the PA according to the signal's magnitude. The EA topology is usually based on a linear and efficient hybrid topology which comprises of a parallel linear voltage source and a highly efficient switched current source [15], and extensive research has been done to further increase its efficiency. For example, by using dual-switch supply, up to 80% efficiency has been achieved by the EA when transmitting WCDMA signals [16]. By increasing the EA efficiency, the efficiency of the overall ET system is increased as well since the efficiency of the ET system is given by  $\eta_{ET} = \eta_{EA}\eta_{PA}$ , where  $\eta_{EA}$  and  $\eta_{PA}$  is the efficiency of the EA and PA, respectively, in the ET system.

Figure 2.6: Simplified ET system block diagram.

Excellent efficiency performance has been achieved by ET systems. For instance, the system in [17] attained about 60 % efficiency with a WCDMA signal.

An advantage of ET is that it is agnostic to the carrier frequency of the PA, and the radio frequency (RF) bandwidth of the ET system is only limited by the RF bandwidth of the PA employed. Hence, if broadband PA topologies such as class J [18] or push pull [19] were used to design the PA then the ET system can achieve high-efficiency performance across an extensive frequency range. The instantaneous modulation bandwidth of a base station ET system, however, is limited by the slew rate or bandwidth of the EA. The envelope of communication signal using IQ modulation is given by  $\sqrt{I^2 + Q^2}$ , where I and Q are the in-phase and quadrature components, respectively. The bandwidth of the envelope signal will be 3-4 times larger than the signal due to the nonlinear transformation, and this high bandwidth requirement can degrade the efficiency and accuracy of the EA [20]. Fortunately, the EA output does not have to faithfully follow the actual envelope in an ET system. Hence, envelope shaping functions have been proposed and used to reduce the bandwidth of the envelope signal [20-22]. This can simplify the EA design and improve its efficiency, but nevertheless, with the modulation bandwidth of communication signals set to dramatically increase in the future the difficulty of designing an efficient EA with very high bandwidth can severely limit the application of ET systems.

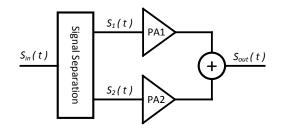

#### 2.2.2 Outphasing

The principle of outphasing modulation, which was proposed in the 1930's [23], can be illustrated using the simplified outphasing system shown in Fig. 2.7. If an amplitude and phase modulated signal is given to the input, such that  $S_{in}(t) = A(t)cos(\omega t + \phi(t))$ , then

Figure 2.7: Simplified outphasing system.

the PA inputs are fixed amplitude signals which can be written as follows:

$$S_{1}(t) = \cos(\omega t + \phi(t) + \cos^{-1}(A(t)))$$

$$S_{2}(t) = \cos(\omega t + \phi(t) - \cos^{-1}(A(t)))$$

(2.3)

If the PAs have a gain of  $G_{pa}$ , then the output voltage is equal to

$$S_{out}(t) = G_{pa}(S_1(t) + S_2(t)) = 2G_{pa}A(t)\cos(\omega t + \phi(t)).$$

(2.4)

Notice how A(t) is effectively encoded into input signals as a differential phase shift, and then recovered at the output using the combiner. For example, the maximum output amplitude is achieved when  $S_1(t)$  and  $S_2(t)$  are in phase, and the output amplitude is zero when they are antiphase. As a result, the input and output of each PA only needs to be phase modulated, and highly efficient nonlinear PAs, like a saturated class B PA, can now be used, ideally, without compromising the output's linearity.

Either an isolated or non-isolated power combiner can be utilized to combine the power of the two PAs in the outphasing system. With a non-isolated combiner, however, the load impedance seen by the PAs will become more reactive as the two outputs become more out of phase. Although no real power is dissipated by the reactive load, the PA that is used to supply reactive power to the reactive load will consume a certain amount of real power. Thus, the outphasing PA's efficiency will be lower at low power levels. This problem can be somewhat remedied by adding a shunt reactance to tune out the reactance seen by the PA for a given amplitude, but this will only maximize the efficiency around that particular amplitude. Nevertheless, through careful selection of the shunt reactance the average efficiency can be improved by as much as a factor of two compared to a class B amplifier [24]. This approach does, however, compromise the linearity of the outphasing system due to the impedance mismatch between the two PAs [25].

Alternatively, isolated combiners, like the Wilkinson power divider or a hybrid combiner, can be used instead which ensures that the both PAs see a constant resistive load at all signal levels. While this improves the linearity of the outphasing system, both PAs will now deliver full power at all output power levels. As a result, efficiency will rapidly decrease at power back-off [26]. Work has been done to try to remedy this problem by replacing the load resistor at the difference port of a 180° hybrid combiner with a converter that can reuse some of the wasted power at power back-off by returning it to the power supply of the PAs [27]. While this technique can improve the PA's efficiency, one of the undesirable consequences is that the impedance of the converter is a function of input power, and can only be matched at one power level. This, in turn, can affect the isolation of the combiner and generate unwanted distortions.

Lastly, a couple of other caveats of the outphasing system should be mentioned here. First the amplitude of PA's input signals are constant versus output power in a conventional outphasing system. Hence, the gain of the outphasing amplifier is reduced at power back-off, and this can significantly decrease the overall PAE of the outphasing system if the gain of the PAs are not high enough [28]. Secondly, the bandwidths of the input signals are expanded due to the inverse cosine operation, and will stretch into the adjacent channels. Any mismatches in the phase and gain of the two PAs means that these out-of-band components will not be perfectly cancelled, and will thus introduce new distortions at the output. In most practical situations, additional calibration and a feedback loop are required to compensate for these mismatches [29].

#### 2.2.3 Doherty Amplifier

While drain modulation improves back-off efficiency by decreasing the drain bias, load modulation techniques, on the other hand, improves back-off efficiency through increasing the load resistance, and thus  $V_1$ , at lower output powers. This, as can be seen from Eq. (2.2), can also increase the class B PA's efficiency. The DPA topology is an example of a PA topology which utilizes load modulation to enhance its power back-off efficiency [30], and a simplified DPA topology is shown in Fig. 2.8(a). The impedance seen by the carrier transistor,  $Z_c$ , can be derived to be

$$Z_c = \frac{Z_T^2}{R_L} - Z_T \frac{I_p}{I_c},$$

(2.5)

where  $Z_T$  is the characteristic impedance of the quarter-wave transformer, and  $I_p$  and  $I_c$ are the magnitude of the fundamental currents from the peaking and carrier transistors, respectively. Notice that we can control  $Z_c$  by controlling the value  $I_p$ . The higher  $I_p$  is, the lower the  $Z_c$  is.

Figure 2.8: Simplified DPA topology and its ideal performances.

Next, the ideal DPA voltages and currents are plotted in Fig. 2.8(b), and the ideal impedance seen by the carrier and peaking transistor,  $Z_p$ , are plotted in Fig. 2.8(c). At low output power levels, when  $|V_{in}|$  is below  $V_{in\_max}/2$ , the peaking transistor is off, and  $Z_c$  stays constant at a value of  $2R_{opt}$ . At higher output powers the peaking transistor turns on, and  $I_p$  will cause  $Z_c$  to decrease according to Eq. (2.5). The purpose of decreasing  $Z_c$  is to keep the fundamental voltage at the drain of the carrier transistor  $V_c$  at a constant value of  $V_{DD}$ . If  $V_c$  increases beyond  $V_{DD}$  the transistor will become strongly saturated<sup>1</sup>, and the output will be heavily distorted as a result.

The DE of the DPA is calculated and plotted in Fig. 2.8(d) for the case when both transistors are biased for class B operation. When  $V_{in}$  is less than  $V_{in\_max}/2$ , the peaking amplifier is off and the DE of the DPA increases linearly from zero to 78.5%:  $Z_c$  is double that of a conventional class B PA in this operation region ( $2R_{opt}$  instead of  $R_{opt}$ ). Hence,

<sup>&</sup>lt;sup>1</sup>In practice,  $V_c$  should be less than  $V_{DD}$  to avoid strong saturation due to the non-zero value of  $V_k$ .

the amplitude of the fundamental voltage at the drain of the carrier transistor  $(V_1)$  is also doubled. As a result, the carrier transistor's DE is two times higher than the maximum DE of a class B amplifier when  $V_{in} = V_{in\_max}/2$  according to Eq. (2.2). When  $V_{in}$  is higher than  $V_{in\_max}/2$ , the DE of the DPA becomes a function of both the carrier and peaking amplifier's power consumption. While the DE of the carrier transistor stays constant at 78.5 %, the efficiency of the peaking transistor increases from 39.25 to 78.5 % as  $V_{in}$ increases from  $V_{in\_max}/2$  to  $V_{in\_max}$ . The DE of a class B and class A PA is also plotted on Fig. 2.8(d) for comparison. Notice that at 6 dB power back-off ( $V_{in} = V_{in\_max}/2$ ), the DE of the DPA is 2 and 6.28 times higher than the DE of the class B and class A PA, respectively.

The RF bandwidth of conventional DPAs is limited by its use of a narrowband quarterwave line. However, recent works on three-way DPAs [31], digital DPAs [32,33], and DPAs with modified design methods have significantly increased its bandwidth capability [34–37]. For example, three-way DPAs can achieve over 55 % efficiency at an output back-off of up to 9 dB over a wide frequency range from 0.73-0.98 GHz [31]. In another example, the authors in [34] utilized a wideband impedance inverter to push the DPA's fractional bandwidth to be greater than 50 % (470-803 MHz).

### 2.3 PA Distortions

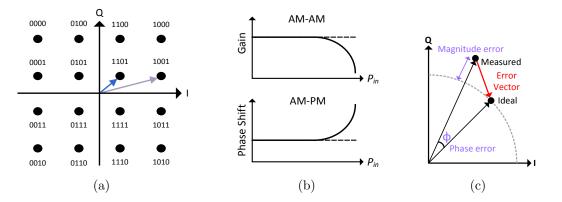

To improve spectral efficiency, modern communication signals use modulation schemes like quadrature amplitude modulation (QAM) which also carries information in the signal amplitude. For example, the constellation diagram of a 16-QAM modulation scheme is given in Fig. 2.9(a). Notice how the symbols representing the bit stream 1101 and 1001 have different magnitudes. As a result, the modulated signal will have a varying amplitude, and this has led to the requirement for PAs which are highly linear versus input signal amplitude such that it maintains the accuracy of the transmitted information and does not generate interference for neighbouring signals.

Unfortunately, PAs have sources of distortions which prevent them from achieving the required linearity. Hence, linearization techniques are necessary in achieving the required PA linearity. In the following subsections, the effects and sources of PA distortion as well as existing linearization techniques used to remedy PA distortions are discussed in brief.

Figure 2.9: Illustration of a) 16-QAM constellation, b) AM-AM and AM-PM of a linear (dashed line) and nonlinear (solid line) PA, and c) error vector.

#### 2.3.1 Effects of PA Distortions on Communication Signals

A PA can have quasi-static as well as dynamic distortions (commonly referred to as memory effects). The Quasi-static distortions of a PA are captured by its steady-state performance, and can be measured using a continuous wave (CW) signal. A perfectly linear PA should have an output voltage amplitude which is a scalar multiple of the input signal. If the input signal is given by  $A \cos(\omega t)$ . Then the linear output can be written as  $KA \cos(\omega t + \phi)$ , where K and  $\phi$  are the constant gain and phase shift of the linear amplifier, respectively. In a nonlinear amplifier, the output is now given as  $K(A)A\cos(\omega t + \phi(A))$ , where the gain K(A) and phase shift  $\phi(A)$  changes versus input signal amplitude, leading to AM-AM and AM-PM distortions, respectively, as shown in Fig. 2.9(b).

Both AM-AM and AM-PM distortions will cause constellation points to deviate from their ideal values, thus reducing signal transmission quality. The amount of deviation caused by the PA distortions can be characterized by the error vector magnitude (EVM), which is defined in percentage as

$$EVM(\%) = 100\% \sqrt{P_{error}/P_{ref}},$$

(2.6)

where  $P_{error}$  and  $P_{ref}$  are the root-mean-square power of the error vector and ideal signal vector, respectively. The error vector is illustrated in Fig. 2.9(c) for one symbol. The higher EVM is, the further away the measured constellation point is from its ideal location.

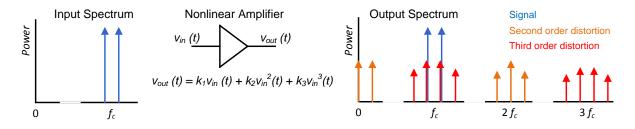

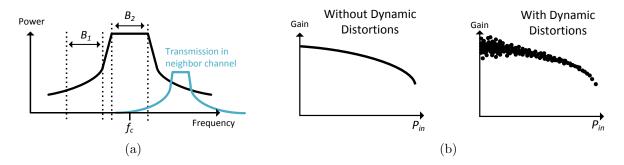

Quasi-static distortions will also cause the frequency spectrum of the signal to expand and generate new frequency components. This can be seen through a two-tone signal test

Figure 2.10: Expected output spectrum distortions with a two-tone input.

with the following input:  $v_{in}(t) = A \cos(\omega_1 t) + A \cos(\omega_2 t)$ , where A is the magnitude of both tones, and  $\omega_1$  and  $\omega_2$  are the frequency of tone 1 and 2, respectively. For a weakly nonlinear PA with AM-AM distortion, its output can be approximately modeled as

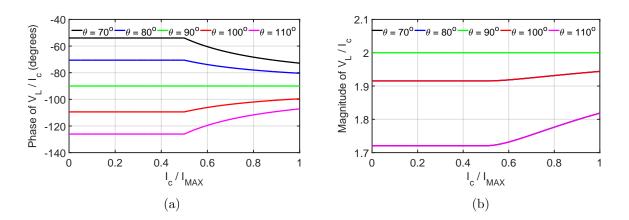

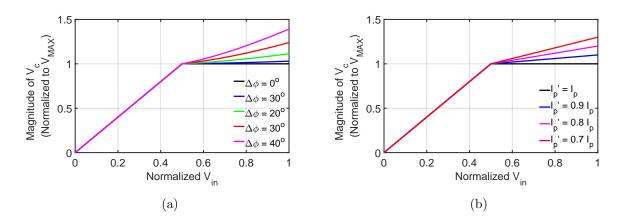

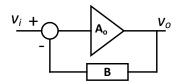

$$v_{out}(t) = k_1 v_{in}(t) + k_2 v_{in}(t)^2 + k_3 v_{in}(t)^3 \dots, \qquad (2.7)$$