# THE FORMAL SPECIFICATION OF A MICROPROCESSOR INSTRUCTION SET

by

Jonathan Bowen

•

Oxford University Computing Laboratory Programming Research Group 8-11 Keble Road Oxford OX1 3QD England Copyright © 1987 Jonathan Bowen

Oxford University Computing Laboratory Programming Research Group 8-11 Keble Road Oxford OX1 3QD England

Electronic mail: bowen@uk.ac.oxford.prg (JANET)

To Jane and Alice

"I only took the regular course ... the different branches of Arithmetic -- Ambition, Distraction, Uglification and Derision."

-- Lewis Carroll

Ovford University Computing Laboratory

# The Formal Specification of a Microprocessor Instruction Set

Jonathan Bowen

## Abstract

The specification language Z is used to define a microprocessor based system in a formal notation. The Motorola 6800 8-bit microprocessor is chosen as an example. Its simplicity allows the entire instruction set to be covered. Memory configuration and interrupts are also included. The use of a formal description language allows the possibility of verification of the instruction set. Additionally, the use of Z combined with informal text is sufficiently readable for the specification to be used for documentation purposes.

#### Contents

# 1. Introduction

## 2. Basic Concepts

- 2.1 Word organisation

- 2.2 Bitwise functions

- 2.3 Shift functions

- 2.4 Arithmetic functions

- 2.5 Test conditions

- 2.6 Hexadecimal notation

#### 3. State

- 3.1 Memory

- 3.2 Registers

- 3.3 System clock

- 3.4 M6800 system

- 3.5 Power-up

- 4. Interrupts

- 5. Instructions

- 5.1 Addressing modes

- 5.2 Accumulator and Memory instructions

- 5.3 Index Register and Stack instructions

- 5.4 Branch and Jump instructions

- 5.5 Condition Code Register instructions

- 5.6 Miscellaneous instructions

- 6. Overall operation

- 7. Conclusion

# 8. Acknowledgements

# 9. References

Appendix A. Example manual pages

Appendix B. Mathematical and Schema notation

#### 1. Introduction

Currently, computer instruction sets are normally documented using tables, semi-formal formulae and informal text. This monograph attempts to show that they may be described just as easily and with more precision using formal specification methods. Microprocessors have been formally specified previously [1]. Often these specifications have been difficult to understand since they have not been designed for documentation purposes. The specification given here concentrates on presenting a specification which is readable by humans as well as computers.

In this monograph, the specification language Z [2-7], developed at the Programming Research Group, is used to define the instruction set for an 8-bit microprocessor, the Motorola 6800. As well as the instruction set, interrupts and memory configuration are also covered. Readers not familiar with the 6800 are referred to its programming manual [8] or instruction set summary card [9]. These may also be used as a comparison with the description given here.

It was felt that a complete microprocessor instruction set should be attempted in order to detect any possible weaknesses in the use of Z for such a task. The relatively simple 6800 processor was chosen because this allowed the entire instruction set of a real microprocessor to be specified. A processor such as one of the 68000 family was deliberately not selected for an initial attempt at such a specification since its greater complexity would either require a good deal more work, or for many features not to be included.

Some of the material covered here is generally useful for any microprocessor based system. Hence any subsequent specifications could draw on this groundwork.

#### 2. Basic Concepts

#### 2.1 Word organisation

Machines such as microprocessors generally manipulate bits. These are organised into non-zero length finite words. By convention, bit positions are numbered from zero up.

Bit  $\cong$  {0, 1} Word  $\cong$  { $\mu$  : N  $\rightarrow$  Bit |  $\mathfrak{m} \rightarrow 0 \land \operatorname{dom} \mu = 0..\mathfrak{m} \rightarrow -1$ }

Often the least significant bit (LSB) and most significant bit (MSB) of a word are of particular interest.

LSB, MSB : Hord  $\rightarrow$  Bit  $\forall \mu$  : Hord  $\bullet$ LSB  $\mu = \mu 0 \land$ MSB  $\mu = \mu \# n - 1$

Each bit pattern in a word uniquely maps to a particular numerical value.

val : Word  $\rightarrow \mathbb{N}$   $\forall \mu : Word +$   $\mathfrak{t}_{\mu} = 1 \Rightarrow val \mu = LSB \mu \wedge$  $\mathfrak{t}_{\mu} > 1 \Rightarrow val \mu = LSB \mu + 2 * val(succ $\mu)$

It is sometimes useful to set all of the bits in a word to a particular value, whatever their previous value.

A word contains its maximum unsigned value when all the bits are set to 1's.

For convenience, we define a function to generate a word of particular size and value:

Hrd :  $\aleph_1 \rightarrow \aleph \rightarrow Hord$ V size :  $\aleph_1$ ; value :  $\aleph$ ;  $\mu$  : Hord + Hrd size value =  $\mu \Leftrightarrow$ # $\mu$  = size A vel  $\mu$  = value <u>mod</u> succ(maxvel  $\mu$ )

Sometimes it is useful to concatenate words together since processors can often handle multiples of some base size of word. These two words may be of differing sizes for complete generality.

$$\begin{array}{c} - & - \\ \hline \hline & - \\ \hline \hline & - \\ \hline \hline & - \\ \hline \hline \\ \hline & - \\ \hline \hline & - \\ \hline \hline \\ \hline \hline \\ \hline \hline & - \\ \hline \hline \hline \\ \hline \\$$

The number of bits in the resulting word is the sum of the number of bits in each of the words being concatenated:

$$H \forall H_1, H_2 : Hord \cdot \#(H_1 \cap H_2) = \#H_1 + \#H_2$$

The high and low halves of a word may be projected using two functions. These projections can be concatenated to form the original word.

```

lo, hi : Word → Word

∀ H : Word +

lo(H) = (0..(#H <u>div</u> 2)-1) ↓ A

hi(H) = succ<sup>(#H</sup> <u>div</u> 2) IH

F ♥ H : Word + H = lo(H) hi(H)

```

## 2.2 Bitwise functions

Bitwise logical functions involve individual bits. A bit may be complemented:

$$\sim : Bit \rightarrow Bit$$

$$\sim = \{0 \mapsto 1, 1 \mapsto 0\}$$

We can also AND, (inclusive) OR and (exclusive) XOR pairs of bits by providing the relevant truth table in each case:

$\begin{array}{c} -\bullet -, \\ -+-, \\ -\bullet -: (Bit \times Bit) \rightarrow Bit \\ \bullet = \{(0,0) \mapsto 0, (0,1) \mapsto 0, (1,0) \mapsto 0, (1,1) \mapsto 1\} \\ + = \{(0,0) \mapsto 0, (0,1) \mapsto 1, (1,0) \mapsto 1, (1,1) \mapsto 1\} \\ \bullet = \{(0,0) \mapsto 0, (0,1) \mapsto 1, (1,0) \mapsto 1, (1,1) \mapsto 0\} \end{array}$

Most microprocessors allow bitwise logical operations on words. For instance, a word may be (1's) complemented i.e. all 0 bits are changed to 1's and all 1's are changed to 0's. This is sometimes referred to as a bitwise logical NOT operation. We can upgrade the definition for a bit to a function which applies to a word:

Many bitwise operations take pairs of bits as input (e.g. those described above).

The corresponding pairs of bits in a pair of words may now be ANDed, ORed, and XORed, again by upgrading the equivalent bit functions:

```

\begin{array}{c} -\bullet - \bullet \\ -\bullet - \bullet \\ -\bullet - \bullet \\ -\bullet - \bullet \end{array} : (Word \times Word) \rightarrow Word \\ \hline \\ \forall \ H_1, \ H_2 : Word \ \bullet \\ H_1 \bullet H_2 = (H_1 \ \underline{pair} \ H_2) (-\bullet ) \land \\ H_1 \bullet H_2 = (H_1 \ \underline{pair} \ H_2) (-\bullet ) \land \\ H_1 \bullet H_2 = (H_1 \ \underline{pair} \ H_2) (-\bullet ) \land \\ \end{array}

```

# 2.3 Shift functions

A word may be shifted left or right. In this case, the bottom (LSB) or top (MSB) bit of the word can attain a certain value, depending on the type of shift (e.g. arithmetic, logical or rotation).

$\begin{array}{c} -\ll \_: (\mathsf{Word} \times \mathsf{Bit}) \to \mathsf{Word} \\ \_\gg \_: (\mathsf{Bit} \times \mathsf{Word}) \to \mathsf{Word} \\ \hline & \forall \ \mathsf{H} : \mathsf{Word}; \ \mathsf{b} : \mathsf{Bit} & \bullet \\ & \mathsf{H} \ll \mathsf{b} = (\{\sharp\mathsf{H}\} \notin \mathsf{pred} \sharp\mathsf{H}) \cup \{\mathsf{0} \mapsto \mathsf{b}\} \land \\ & \mathsf{b} \gg \mathsf{H} = \{\sharp\mathsf{H} \mathsf{-1} \mapsto \mathsf{b}\} \cup (\mathsf{succ} \sharp\mathsf{H}) \end{array}$

# 2.4 Arithmetic functions

Microprocessors normally allow arithmetic operations. For example, a word may be incremented or decremented. The result wraps around if there is overflow or underflow in each case.

inc, dec : Word ≫ Word ∀н : Word • incн = нrd #н (succ⊕{maxvelн → 0})(valн) ^ decн = нrd #н ({0 ↦ maxvalн} ∪ pred)(valн)

Incrementing and then decrementing a word (or vice versa) leaves it unchanged. Additionally one is the inverse of the other.

F inc # dec = dec # inc = id[Word]

F dec = inc<sup>-1</sup>

This may be generalised for addition and subtraction by repeatedly incrementing or decrementing a word:

$\begin{array}{c} -+-, \\ ---: (Word \times N) \rightarrow Word \\ \hline \forall \ w : Word; \ i : N \\ w+i = inc' \\ w-i = dec^{i} \end{array}$

Similarly, a second word, possibly of a different size, may be added to or subtracted from a word. The size of the resulting word is determined by the first word.

$\begin{array}{c} -+-,\\ ---: (Word \times Word) \rightarrow Word\\ \hline\\ \forall \ H_1, \ H_2: \ Word \\ H_1+H_2 = H_1 + (val \ H_2) \\ H_1-H_2 = H_1 - (val \ H_2) \end{array}$

Some operations can return the 2's complement (negation) of a word:

Note that the 1's complement (bitwise logical NOT) and 2's complement (negation) of a word are related as follows:

$$F \forall \mu : Word \cdot -\mu = inc(\neg \mu)$$

Sometimes it is useful to "sign-extend" a word into another (normally longer) word. This involves setting any extra bits to the value of the most significant bit (the "sign" bit) in the first word. The rest of the bits in the resulting word are set to the values of the equivalent bits in the first word.

A word can be used as a signed relative offset. The value of the top bit determines the direction of the offset.

$$\begin{array}{c} \underline{\phantom{a}} \pm \underline{\phantom{a}} : (\operatorname{Hord} \times \operatorname{Hord}) \to \operatorname{Hord} \\ \\ \forall \ \mathbf{H}_1, \ \mathbf{H}_2 : \operatorname{Hord} \cdot \\ \\ & \mathbf{H}_1 \pm \mathbf{H}_2 \cong \mathbf{H}_1 + (\mathbf{H}_2 \underline{\operatorname{signext}} \mathbf{H}_1) \end{array}$$

This is particularly useful for branch instructions which usually allow a relative branch forwards and backwards.

# 2.5 Test conditions

Most microprocessors contain a status word which contains bits related to the results of previous operations. Different operations may affect different bits. Sometimes different operations affect the same bit in (possibly subtly) different ways.

Often we wish to test whether a word has a zero value, returning a '1' if it has and a '0' if not:

```

zero : Word → Bit

\forall H : Word •

ran H = {0} ⇒ zero H = 1 ∧

ran H ₹ {0} ⇒ zero H = 0

```

Conversely, we may wish to test whether a word contains all 1's, returning a '1' if it does and a '0' if not. This test can not usually be performed by microprocessors explicitly (unlike the test for zero above). However it can still be useful for the specification of other test conditions (see later).

```

ones : Word → Bit

V N : Word •

ones N = zero(~N)

```

Testing for a negative value can be performed by most microprocessors, returning a '1' if it is negative and a '0' if not. Negative words have the top "sign" bit set. Hence this function can be performed by the previously defined MSB function.

12

# 2.6 Hexadecimal notation

Most microprocessor documentation uses hexadecimal values for op-codes, addresses and so forth, since this notation may easily be converted to the corresponding bit pattern. Each digit is the equivalent of four bits. Hexadecimal digits are drawn from the set of characters (CHAR) and consist of the decimal digits '0' to '9' and the letters 'A' to 'F'. Each of these hexadecimal digits uniquely maps to a numerical value:

[CHAR]

$\begin{array}{c} \text{hex} : \text{CHAR} & \leftrightarrow \text{N} \\ \\ \hline \text{hex} = \{ {}^{\circ}0^{\circ} \mapsto 0, \ {}^{\circ}1^{\circ} \mapsto 1, \ {}^{\circ}2^{\circ} \mapsto 2, \ {}^{\circ}3^{\circ} \mapsto 3, \\ {}^{\circ}4^{\prime} \mapsto 4, \ {}^{\circ}5^{\circ} \mapsto 5, \ {}^{\circ}6^{\circ} \mapsto 6, \ {}^{\circ}7^{\prime} \mapsto 7, \\ {}^{\circ}8^{\circ} \mapsto 8, \ {}^{\circ}9^{\circ} \mapsto 9, \ {}^{\circ}A^{\circ} \mapsto 10, \ {}^{\circ}B^{\circ} \mapsto 11, \\ {}^{\circ}C^{\circ} \mapsto 12, \ {}^{\circ}D^{\circ} \mapsto 13, \ {}^{\circ}E^{\circ} \mapsto 14, \ {}^{\circ}F^{\circ} \mapsto 15 \} \end{array}$

We can define a function to handle a sequence of hexadecimal digits (i.e. a hexadecimal number). We shall employ the widely used notation of prefixing 0x to the hexadecimal string.

$0x : (seq CHAR) \rightarrow N$   $0x \langle \rangle = 0$   $\forall s : seq_1 CHAR | ran s \leq dom hex \cdot$  0x s = 16 \* 0x(front s) + hex(last s)

An alternative posibility would be to postfix the letter H (i.e. to define a similar postfix function, \_K).

#### 3. State

We shall consider the state of a 6800 based system in three parts, covering static conditions and then changes in state in each case:

- 1. Memory

- 2. Registers

- 3. System clock

We shall then combine these and consider changes in state of the entire system (as defined above) when an instruction is executed or an interrupt occurs. Finally, the state of the system when it powers up is detailed.

The 6800 operates on 8-bit bytes of data and 16-bit addresses:

Byte  $\cong$  {  $\bowtie$  : Word | # = 8 } Address  $\cong$  {  $\bowtie$  : Word | # = 16 }

The following functions convert values to data bytes and addresses respectively:

data ≙ (µrd 8) addr ≙ (µrd 16)

Some numerical values have known ranges. In particular, some numbers will fit into a *nibble* (4 bits), a data byte (8 bits) and a word address (16 bits). It is useful to define these ranges.

```

\begin{array}{rcl} & \forall \texttt{alue}_4 & \triangleq & 0..2^4 \text{--}1 \\ & \forall \texttt{alue}_8 & \triangleq & 0..2^8 \text{--}1 \\ & \forall \texttt{alue}_{16} & \triangleq & 0..2^{16} \text{--}1 \end{array}

```

## 3.1 Memory

The address space of the 6800 (and many other microprocessors) may be considered as a total function from Addresses to Bytes. We shall assume that ROM (Read Only Memory) and RAM (Random Access Memory) make up the available real memory. These two areas do not overlap.

> . Hemory \_\_\_\_\_ Hem : Address → Byte ROM, RAM : F Address RAM ∩ ROM = Ø

The memory may be updated by operations such as instructions and interrupts. In this case, the ROM and RAM areas (i.e. their domains) do not change. The RAM contents may be partially updated by an instruction or interrupt. Areas outside valid ROM and RAM may vary unpredictably and are thus not defined by this specification. The values in ROM do not vary. Only values in RAM may be updated reliably. Additionally, some operations do not affect the RAM contents.

\_ ΔMemory \_\_\_\_\_ Memory Memory' δMem : Address → Byte ROM' = ROM RAM' = RAM ROM ⊈ Mem' = ROM ⊈ Mem RAM ⊈ Mem' = RAM ⊈ (Mem ⊕ δMem)

EMemory 🛳 ΔMemory | δMem = Ø

Note that the assumptions above are not strictly true in all cases. For example, it is possible to have software switchable banked memory. However they hold for the majority of simple systems. In practice areas outside ROM and RAM may be used for memory mapped I/O. This is not covered here since it is very system dependent. It could be considered separately.

# 3.2 Registers

The 6800 has a number of registers:

Most of these are 8-bit registers:

$Regs_{B} \cong \{A, B, CCR, PC_{H}, PC_{L}, SP_{H}, SP_{L}, X_{H}, X_{L}\}$

Two of the 8-bit registers are general purpose accumulators:

Some of the registers are normally used in pairs, so that they may be used to hold 16bit memory addresses:

$$Regs_{16} \triangleq \{PC, SP, X\}$$

The 8-bit registers always contain byte values and the 16-bit registers always contain address values. The low and high bytes of the PC, SP and X registers concatenate to form 16-bit registers. The top two bits of the CCR are unused and are always set to 1.

```

Registers

Reg : Regs → Word

Reg[Regs<sub>B</sub>] S Byte

Reg[Regs<sub>16</sub>] S Address

Reg(PC) = Reg(PC<sub>L</sub>) \widehat{Reg(PC_H)}

Reg(SP) = Reg(SP<sub>L</sub>) \widehat{Reg(SP_H)}

Reg(X) = Reg(X<sub>L</sub>) \widehat{Reg(X_H)}

Reg CCR [6..7] = {1}

```

16

Any of the registers may be updated by an instruction (or interrupt). Every instruction consists of one or more bytes. (External interrupts have no bytes.) Normally the next instruction to be executed is the instruction following the current instruction. This may be overridden, for example by a branch instruction (see later). Individual bits in the Condition Code Register may be updated by the instruction depending on the result of the operation. However the top two bits of the CCR remain set to 1's even if the instruction attempts to overwrite them.

Sometimes an operation does not affect the 6800 registers (apart from the Program Counter which is automatically updated):

```

ERegisters ≙ ∆Registers | δReg = Ø ∧ δCCR = Ø

```

# Condition codes

The Condition Code Register holds various single bit codes at different bit positions. These are the carry, overflow, zero, negative, interrupt mask and half-carry bits:

> C ≙ 0 V ≙ 1 Z ≏ 2 N ≙ 3 I ≙ 4 H ≙ 5

The contents of the individual condition code bits are often of interest. We make the following definitions for syntactic brevity:

$\begin{array}{rcl} C_{cc} & \cong & (\operatorname{Reg}\ \operatorname{CCR})\ \operatorname{C} \\ V_{cc} & \cong & (\operatorname{Reg}\ \operatorname{CCR})\ \operatorname{V} \\ Z_{cc} & \cong & (\operatorname{Reg}\ \operatorname{CCR})\ \operatorname{Z} \\ N_{cc} & \cong & (\operatorname{Reg}\ \operatorname{CCR})\ \operatorname{N} \\ I_{cc} & \cong & (\operatorname{Reg}\ \operatorname{CCR})\ \operatorname{I} \\ H_{cc} & \cong & (\operatorname{Reg}\ \operatorname{CCR})\ \operatorname{H} \end{array}$

Condition code bits often depend on the values of bits in results of operations. For the convenience of these specifications, we use the following short forms for  $i \in 0...7$ ,  $j \in 0...15$  and  $x \in Accumulator:$

| ×,  | ≙ | (Reg x) | ij |

|-----|---|---------|----|

| H,  | ≙ | (Mem M) | i  |

| R   | ≙ | Ri      |    |

| X   | € | (Reg X) | j  |

| RŘ, | ≙ | RR j    |    |

#### 3.3 System clock

The system contains a clock which controls the timing of the system. This consists of a sequence of pulses. This may be modelled as the number of clock pulses which have occurred since the system was powered-up:

When an instruction is executed or an interrupt occurs, it takes a certain number of clock cycles to execute:

AClock Clock Clock' Cycles : N Clk' = Clk + Cycles

## 3.4 M6800 system

The system state consists of memory, registers and a clock:

M6800 ≙ Memory A Registers A Clock

There are various types of 6800 addressing modes. Additionally, the 6800 may respond to an external Interrupt or execute an Illegal instruction.

Modes ::= Immediate | Direct | Indexed | Extended | Inherent | Relative | Interrupt | Illegal

Each of these modes is detailed later.

When an instruction is executed, the op-code is read from the memory location indicated by the current value of the Program Counter. The instruction will have a particular addressing mode. The state of the system will change when the instruction has executed:

```

ΔM6800

ΔMemory

ΔRegisters

ΔClock

Op : Value<sub>B</sub>

Mode : Modes

Op = val Mem(PC)

```

Some operations do not affect the memory or registers (apart from the Program Counter which is automatically incremented depending on NBytes):

ΞM5800 ≙ ΔM6800 A Effemory A ERegisters

20

## 3.5 Power-up

The clock starts from zero for convenience in this model, when the system is initialised (i.e. powered up). It is assumed that the ROM already holds the program to be executed.

Interrupts are disabled and the Program Counter is loaded from the top two locations in memory. Note that hexadecimal numbers are used, rather than decimal, for memory addresses and op-code values since this is more normal (and convenient) in microprocessor documentation as discussed earlier.

$\begin{array}{c} \text{M5800}_{\text{INIT}} \\ \text{M5800'} \\ \hline \\ \text{Clk' = 0} \\ \text{I}_{cc} \text{' = 1} \\ \text{Reg'(PC_{H}) = Mem'(addr 0xFFFE)} \\ \text{Reg'(PC_{L}) = Mem'(addr 0xFFFF)} \\ \end{array}$

#### 4. Interrupts

When an interrupt occurs, or if the SWI or WAI instructions are executed (see later), all the 6800 registers are saved on the stack. program control is transferred to a new address specified by the contents of memory at a particular vector address. The interrupt mask bit is set in the Condition Code Register. This is defined by a framing schema (denoted by  $\Phi$ ) which may be used in the subsequent definitions of these cases:

```

\begin{aligned} & \phi \text{Interrupt} \\ & \Delta M6800 \\ & \text{Vector} : \text{Value}_{15} \\ & \delta \text{Mem} = \{ \text{Mem}(\text{Reg}(\text{SP})-6) \mapsto \text{Reg}(\text{CCR}), \\ & \text{Mem}(\text{Reg}(\text{SP})-5) \mapsto \text{Reg}(\text{B}), \\ & \text{Mem}(\text{Reg}(\text{SP})-4) \mapsto \text{Reg}(\text{A}), \\ & \text{Mem}(\text{Reg}(\text{SP})-3) \mapsto \text{Reg}(\text{X}_{H}), \\ & \text{Mem}(\text{Reg}(\text{SP})-2) \mapsto \text{Reg}(\text{X}_{L}), \\ & \text{Mem}(\text{Reg}(\text{SP})-2) \mapsto \text{Reg}(\text{X}_{L}), \\ & \text{Mem}(\text{Reg}(\text{SP})-1) \mapsto \text{hi}(\text{Next}), \\ & \text{Mem}(\text{Reg}(\text{SP})) \mapsto \text{lo}(\text{Next}) \} \\ & \delta \text{Reg} = \{ \text{PC}_{\text{H}} \mapsto \text{Mem}(\text{eddr}(\text{Vector})), \\ & \text{PC}_{L} \mapsto \text{Mem}(\text{eddr}(\text{Vector}+1)), \\ & \text{SP} \mapsto \text{Reg}(\text{SP})-7 \} \\ & \delta \text{CCR} = \{ \text{I} \mapsto 1 \} \end{aligned}

```

There are three interrupts which may be activated externally to the 6800 microprocessor. An external interrupt is not an instruction read from memory so it may be considered to have a length of zero bytes. This will result in program control returning to the current instruction when au RTI instruction (see later) is subsequently executed at the end of the interrupt service routine, provided the stack is not corrupted.

It takes a number of clock cycles to service the interrupt and stack the registers. The exact number of cycles could not be found in the documentation used to formulate this specification [8,9], so it is not given here. It is likely to be of the order of the minimum number of cycles taken by the HA1 instruction. If known, it could easily be inserted in the following schemas.

The hardware interrupt (IRQ) can only be activated if the interrupt mask bit in the CCR is clear:

The non-maskable interrupt (NMI) may be activated at any time:

```

NMI

$$\philling$ Interrupt

NMI? : Bit

NMI? = 0

Yector = 0xFFFC

NBytes = 0

```

When a reset occurs, the registers are not stacked and the memory is left unaffected, but the "reset" vector is used to restart the program in the same way as occurs at power-up:

> Reset \_\_\_\_\_\_  $\Delta M6800$   $\Xi Memory$   $\delta Reg = \{ PC_H \mapsto Mem(eddr 0xFFFE), PC_L \mapsto Mem(eddr 0xFFFF) \}$  $\delta CCR = \{ I \mapsto 1 \}$

In conclusion, the system has three possible sources of external interrupt. Note that the 6800 interrupt vectors are all located at the top of memory. Hence it is normal for this area to be contained in ROM.

# 5. Instructions

All microprocessors have a set of instructions which they can execute. These instructions can affect the registers and/or the memory using a variety of addressing modes, depending on the microprocessor involved.

## 5.1 Addressing modes

Many of the 6800 instructions use a selection of memory addressing modes. Each has a memory address (M) of an operand calculated in a manner depending on the addressing mode. The op-code for a given type of addressing mode is always and constant offset from the op-code for a particular base addressing mode. The 6800 Extended addressing mode may conveniently be selected for this base addressing mode. The corresponding op-code for a particular instruction will be known as the base op-code (OpBase). The value of OpBase is specified in subsequent schemas defining specific instructions.

The number of clock cycles which an instruction takes to execute also depends on the addressing mode. Again this is easily calculated from a base number of cycles for a particular addressing mode (CyclesBase). The number of execution cycles may be defined in terms of an offset from the base number of cycles in subsequent schemas.

The information above may be combined together in a framing schema for use when defining each of the addressing modes covered in the rest of the section:

ΦAddrMode ΔM6800 M : Address OpBase : Value<sub>8</sub> CyclesBase : N

We shall now define the major addressing modes of the 6800 as framing schemas for use by subsequent schemas describing individual 6800 instructions.

Immediate mode addressing gives the address of the byte immediately following the instruction op-code byte:

Direct mode addresses are in the first 256 bytes of memory. The byte following the op-code specifies this address, the upper byte of the address being zero:

Indexed mode address are calculated by adding the contents of the byte following the op-code (0-255) to the index register:

Extended mode addresses are specified fully using the two bytes following the op-code, high byte first, low byte second:

Several or all of these addressing modes may be used by a specific instruction. Hence we shall combine them together into one schema.

There are two other addressing modes used by many instructions so these are also defined separately here.

Some instructions use inherent addressing. In this case there is no memory address to be calculated. The instruction consists of a single byte op-code.

\_ ØInherent \_\_\_\_\_\_ ØAddrNode Mode = Inherent NBytes = 1 CyclesBase = 2

Note that the memory address (1) is left undefined in the above framing schema since it will never be used in later specifications making use of this schema.

Some "branch" instructions use relative addressing to calculate a new value for the Program Counter if a branch occurs. The byte following the op-code is sign-extended and added to the address of the next instruction. Hence a branch instruction may transfer program control up to 127 bytes forwards or 128 bytes backwards relative to the start of the instruction following the branch instruction.

The complete instruction set of the 6800 is covered in subsequent sections consisting of families of related instructions as designated by Motorola [8].

# 5.2 Accumulator and Memory instructions

This family of instructions use one or both of the 8-bit accumulators and/or a byte in memory. These can be further sub-divided into different types of instruction, depending on the allowed addressing modes.

# Inherent addressing

Some instructions use inherent addressing and operate on accumulator A or B only. The memory contents are unaffected. The instruction operation produces a byte result, R, which is used to update the accumulator.

φSingleAcc φInherent ≡Memory × : Accumulator R : Byte Cycles = CyclesBase δReg = { × ↦ R }

# Accumulator addressing

Either of the accumulators may be pushed onto or popped off the stack. These operations take four cycles to execute.

$\Phi StackAcc ... \\ \Phi Inherent \\ x : Accumulator \\ OpBase : Value_B \\ (x = A \land Op = OpBase) \lor \\ (x = B \land Op = OpBase + 1) \\ Cycles = CyclesBase + 2 \\ \end{tabular}$

#### 28

## Single operand addressing

Some instructions have a single operand. They can update a memory byte by performing an operation on it, but only using a limited set of the available addressing modes:

¢MemUpdate \_\_\_\_\_ ¢Modes Operand, R : Byte Mode € { Indexed, Extended } Cycles = CyclesBase + 2 Operand = Mem(N) δMem = { M ↦ R } δReg = Ø

These can also perform the same operation on one of the accumulators. These replace the op-codes which would have been used by the immediate and direct addressing modes not used because of the limited number of addressing modes above.

The last two schemas may be combined to produce a framing schema which describes single operand instructions with multiple addressing modes:

φSingle ≙ φMemUpdate V φAccUpdate

Double operand addressing

Some instructions have two operands. One is in one of the two accumulators and the other is extracted from memory using a selection of addressing modes. The op-code base offsets are calculated from the op-code base of the instruction which uses accumulator A (OpBaseA). The value of OpBaseA is defined in subsequent schema definitions for specific instructions.

These double operand instructions leave memory unaffected and take the basic number of clock cycles to execute. The instruction operation produces a byte result (R).

ΦDouble ΦAccumulator ΞMemory R : Byte Cycles = CyclesBase δReg = { x ↦ R }

30

# Test instruction framing schema

Some instructions simply perform tests on a byte value, T. In this case, the memory and registers (apart from the CCR) are left unaffected (or effectively updated with existing contents). The top "sign" bit of the byte may be of particular interest.

The accumulator and memory family of instructions can now be defined using the framing schemas above. All the instructions operate on 8-bit values in memory and the two accumulators.

# Transfer instructions

Some instructions simply transfer bytes between registers and/or memory without modifying their contents. For example, an accumulator may be loaded from a memory byte. The Condition Code Register bits are updated appropriately.

LDA  $\Phi$ Double 0pBaseA = 0xB6 R = Mem(M) $\delta CCR = \{ N \mapsto R_7, Z \mapsto zero(R), V \mapsto 0 \}$

Conversely, there is an instruction to store the contents of an accumulator into a byte in memory. This cannot use the immediate addressing mode. It takes an extra clock cycle to execute compared to most other similar instructions (e.g. LDA). The addressed memory byte is updated with the result and the CCR bits are set appropriately.

```

STA _____

\PhiAccumulator

OpBaseA = 0xB7

Mode \neq Immediate

Cycles = CyclesBase + 1

SMem = { M \mapsto Reg(x) }

SReg = Ø

SCCR = { N \mapsto MSB(Reg x),

Z \mapsto zero(Reg x),

V \mapsto 0 }

```

The accumulators may be transferred back and forth:

TAB  $\oint SingleAcc$  Op = 0x16  $\delta Reg = \{A \mapsto Reg(B)\}$  $\delta CCR = \{N \mapsto B_7, Z \mapsto Zero(B), V \mapsto 0\}$

TBA

$$\Phi$$

SingleAcc

$0p = 0x17$

$\delta$ Reg = { B  $\mapsto$  Reg(A) }

$\delta$ CCR = { N  $\mapsto$  A<sub>2</sub>,

Z  $\mapsto$  zero(A),

V  $\mapsto$  0 }

The accumulators may be pushed on to the stack. In this case, the condition codes are not affected.

PSH \_\_\_\_\_  $\phi$ StackAcc OpBase = 0x36 SMem = {Reg(SP)  $\mapsto$  Reg(x) } SReg = {SP  $\mapsto$  Reg(SP)-1 } SCCR = Ø The accumulators may also be restored from the stack. Again, the CCR is unaffected. In this case the memory contents are also unaffected.

> PULA \$\$tackAcc EMemory OpBase = 0x32 \$Reg = { x ↦ Mem(Reg(SP)+1), SP ↦ Reg(SP)+1 } \$CCR = Ø

# Logical instructions

Some instructions perform bitwise logical operations on the accumulators and memory bytes. For example, a byte operand may be 1's complemented:

```

COM

\oint Single

OpBase = 0x73

R = \sim Operand

SCCR = \{ N \mapsto R_7, Z \mapsto zero(R), V \mapsto 0, C \mapsto 1 \}

```

There is a bitwise logical AND instruction:

```

AND

\phiDouble

0pBaseA = 0xB4

R = Reg(x) \bullet Mem(M)

\delta CCR = \{N \mapsto R_7, 2 \mapsto zero(R), V \mapsto 0\}

```

a bitwise logical inclusive OR instruction:

and a bitwise logical exclusive OR instruction:

```

EOR _____

\PhiDouble

OpBaseA = 0xB8

R = Reg(x) \oplus Mem(M)

SCCR = { N \mapsto R<sub>7</sub>,

Z \mapsto zero(R),

V \mapsto 0 }

```

# Arithmetic instructions

Some instructions perform simple arithmetic operations on bytes.

An operand may be incremented. The overflow bit in the CCR is set if the original contents of the operand had the top bit clear and the rest of the operand bits were set to 1's.

INC  $\product{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale}{\scale$

Conversely, an operand may be decremented. The overflow bit in the CCR is set if the original contents of the operand had the top bit set and the rest of the operand bits were zero.

There are three "add" instructions. They all update the half-carry bit in the CCR with the carry from hit 3. The overflow bit is set if there was a 2's complement overflow. The carry bit is set if there was a carry from the most significant bit of the result. The standard "add" instruction simply adds a byte from memory to an accumulator.

36

Accumulator B can be added to accumulator A (but not vice versa):

$\begin{array}{l} ABA \\ \hline \phi SingleAcc \\ \hline 0p = 0x1B \\ R = Reg(A) + Reg(B) \\ & & \\ \$Reg = \{ A \mapsto R \} \\ & & \\ \$CCR = \{ H \mapsto A_3 \circ B_3 + B_3 \circ \sim R_3 + \sim R_3 \circ A_3, \\ & & \\ N \mapsto R_7, \\ & & \\ Z \mapsto zero(R), \\ & & \\ V \mapsto A_7 \circ B_7 \circ \sim R_7 + \sim A_7 \circ \sim B_7 \circ R_7, \\ & & \\ C \mapsto A_7 \circ B_7 + B_7 \circ \sim R_7 + \sim R_7 \circ A_7 \} \end{array}$

The current value of the carry bit in the CCR may be added to the result as well:

```

ADC

\phiDouble

\phiDouble

R = Reg(x) + Mem(M) + C_{cc}

\delta CCR = \{ H \mapsto x_3 \circ M_3 + M_3 \circ R_3 \circ R_3

```

There is a "Decimal Adjust Accumulator" instruction for use when binary coded decimal (BCD) operands are involved. The adjustment to be added to the accumulator is calculated from the carry bit, upper half-byte value of the accumulator, half-carry bit and lower half-byte value of the accumulator as follows:

daa : Bit × Value<sub>4</sub> × Bit × Value<sub>4</sub> → Value<sub>8</sub> ∀ i : Bit × Value<sub>4</sub> × Bit × Value<sub>4</sub> • i ∈ {0}×(0x0..0x9)×{0}×(0x0..0x9) ⇒ daa i = 0x00 i ∈ {0}×(0x0..0x8)×{0}×(0xA..0xF) ⇒ dea i = 0x06 i ∈ {0}×(0x0..0x9)×{1}×(0x0..0x3) ⇒ daa i = 0x06 i ∈ {0}×(0xA..0xF)×{0}×(0x0..0x9) ⇒ daa i = 0x60 i ∈ {0}×(0xA..0xF)×{0}×(0xA..0xF) ⇒ daa i = 0x66 i ∈ {0}×(0xA..0xF)×{1}×(0x0..0x3) ⇒ daa i = 0x66 i ∈ {0}×(0x0..0x2)×{0}×(0x0..0x9) ⇒ daa i = 0x66 i ∈ {0}×(0x0..0x2)×{0}×(0x0..0x7) ⇒ daa i = 0x66 i ∈ {0}×(0x0..0x2)×{0}×(0xA..0xF) ⇒ daa i = 0x66 i ∈ {0}×(0x0..0x3)×{1}×(0x0..0x3) ⇒ daa i = 0x66 i ∈ {0}×(0x0..0x3)×{1}×(0x0..0x3) ⇒ daa i = 0x66

Entries not included in the table are undefined. The overflow bit in the CCR is always undefined after this instruction has been executed. It is intended that this instruction should be used immediately after an "add" instruction.

There are matching "subtract" instructions for each "add" instruction. Note however that the half-carry bit in the CCR is left unaffected by these instructions.

> SUB  $\phi$ Double pBaseA = 0xB0 R = Reg(x) - Mem(M)SCCR = {  $N \mapsto R_7$ ,  $Z \mapsto zero(R)$ ,  $V \mapsto x_7 e^{M} T_7 e^{R_7} e^{R_7}$ ,  $C \mapsto x_7 e^{M} T_7 e^{R_7} e^{R_7}$

SBA fSingleAcc  $Op = 0 \times 10$  R = Reg(A) - Reg(B)  $SReg = \{ A \mapsto R \}$   $SCCR = \{ N \mapsto R_7,$   $Z \mapsto zero(R),$   $V \mapsto A_7 \circ B_7 \circ R_7 \circ R_$

```

SBC

pDouble

pBaseA = 0xB2

R = Reg(x) - Hem(M) - C_{cc}

&CCR = \{ N \mapsto R_7, Z \mapsto zero(R), V \mapsto x_7 e^{-M}7 e^{-R_7} e^{-R_7}, C \mapsto x_7 e^{-M}7 e^{-R_7} e^{-R_7

```

An operand may be negated (2's complemented). The overflow bit in the CCR is set if the result has the top bit set and the rest of the result bits are zero. The carry bit is set to the opposite of the zero bit.

> NEG  $\oint Single$ OpBase = 0x70 R = -Operand SCCR = { N  $\mapsto$  R<sub>7</sub>, Z  $\mapsto$  zero(R), V  $\mapsto$  R<sub>7</sub>\*zero(74R), C  $\mapsto$  \*zero(R) }

A memory byte or an accumulator may be cleared to all 0's.

```

CLR

\oint Single

OpBase = 0x7F

R = data(0)

SCCR = { N \mapsto 0,

Z \mapsto 1,

V \mapsto 0,

C \mapsto 0 }

```

Note that there is no equivalent instruction to set a byte to all 1's.

# Shift instructions

Some 6800 instructions shift hytes by one bit position left or right. Note that the overflow bit in the CCR is always set as the XOR of the resulting negative and carry CCR bits for all 6800 shift instructions.

There are shift instructions which rotate a byte left or right by one bit through the carry bit in the CCR:

```

ROL

\phiSingle

0pBase = 0x79

R = Operand \ll C_{cc}

\delta CCR = \{ N \mapsto R_7 \},

Z \mapsto zero(R),

V \mapsto N_{cc}' \oplus C_{cc}',

C \mapsto Operand(7) \}

```

```

ROR

\oint Single

OpBase = 0x76

R = C<sub>cc</sub> \gg Operand

SCCR = { N \mapsto R<sub>7</sub>,

Z \mapsto zero(R),

V \mapsto N<sub>cc</sub>' \oplus C<sub>cc</sub>',

C \mapsto Operand(0) }

```

There are arithmetic shift instructions which shift a byte left or right by one bit. These are equivalent to multiplying and dividing a signed byte value by 2.

```

ASL

\phiSingle

0pBase = 0x78

R = 0perend \ll 0

\deltaCCR = { N \mapsto R<sub>7</sub>,

Z \mapsto zero(R),

V \mapsto N<sub>cc</sub>' \oplus C<sub>cc</sub>',

C \mapsto 0perand(7) }

```

```

ASR

\phiSingle

0pBase = 0x77

R = 0perand(7) \gg 0perand

\delta CCR = { N \mapsto R_7,

Z \mapsto zero(R),

V \mapsto N_{cc} \in C_{cc},

C \mapsto 0perand(0) }

```

There is a logical shift right instruction, filling the result with a zero in its top bit:

```

LSR

\phiSingle

0pBase = 0x74

R = 0 \gg Operand

\deltaCCR = { N \mapsto 0,

Z \mapsto zero(R),

V \mapsto N<sub>cc</sub>' \oplus C<sub>cc</sub>',

C \mapsto Operand(0) }

```

Note that there is no matching LSL (logical shift left) instruction since this is equivalent to an ASL instruction (see above).

# Test instructions

Some instructions only affect the condition codes by performing tests on byte values.

There is a bitwise logical AND test instruction which simply sets the condition code bits as if an AND instruction had been performed, but does not update the result:

BIT  $\phi$ Double  $\phi$ Test  $0\rho$ BaseA = 0xB5  $T = \text{Reg}(x) \circ \text{Mem}(M)$ SCCR = {  $N \mapsto T_7$ ,  $Z \mapsto \text{zero}(T)$ ,  $V \mapsto 0$  }

A byte operand may be tested. The condition codes are set as if zero had been subtracted from the operand.

```

TST _____

\PhiSingle

\PhiTest

0pBase = 0x7D

T = Operand - 0

SCCR = \{ N \mapsto T_7, Z \mapsto zero(T), V \mapsto 0, C \mapsto 0 \}

```

There is a "compare" instruction which simply sets the condition code bits as if a SUB instruction had been performed, but does not update the result:

CMP  $\Phi$ Double  $\Phi$ Test OpBaseA = 0xB5 T = Reg(x) - Mem(M) SCCR = { N  $\mapsto$  T<sub>7</sub>, Z  $\mapsto$  zero(T), V  $\mapsto$  x<sub>7</sub>e~M<sub>7</sub>e~T<sub>7</sub>e~x<sub>7</sub>eM<sub>7</sub>eT<sub>7</sub>, C  $\mapsto$  ~x<sub>7</sub>eM<sub>7</sub>eM<sub>7</sub>eT<sub>7</sub>e~x<sub>7</sub> }

The two accumulators may be compared in a similar way without changing the contents of either:

```

CBA

\oint SingleAcc

\oint Test

Op = 0 \times 11

T = Reg(A) - Reg(B)

\& CCR = \{ N \mapsto T_7, Z \mapsto zero(T), V \mapsto A_7 \circ B_7 \circ T_7 \circ A_7 \circ B_7 \circ T_7, C \mapsto A_7 \circ B_7 \circ T_7 \circ A_7 \}

```

# Instruction types

The 6800 includes the following transfer/logical/arithmetic/shift/test type accumulator and memory instructions:

| DoubleOp                | â | LDA V STA V<br>AND V ORA V EOR V<br>ADD V ADC V SUB V SBC V<br>B17 V CMP |

|-------------------------|---|--------------------------------------------------------------------------|

| SingleOp                | 4 | COM V<br>DEC V INC V NEG V CLR V<br>ROL V ROR V ASL V ASR V LSR V<br>TST |

| Inherent <sup>0</sup> p | Q | TAB V TBA V<br>ABA V DAA V SBA V<br>CBA                                  |

| St <b>ack</b> 0p        | ≙ | PSH ¥ PUL                                                                |

We can combine all these sub-types of instruction together:

# 5.3 Index Register and Stack instructions

These instructions manipulate the 16-bit index register and stack pointer. Some have several addressing modes. These can be further sub-divided into "load" and "store" type operations, each of which produces a 16-bit result, RR. Load operations do not affect memory:

> ΦXLoad ΦModes ΞMemory RR : Address Cycles = CyclesBase + 1

Store operations cannot be used in immediate mode:

φXStore φModes RR : Address Mode ≠ Immediate Cycles = CyclesBase + 2

Some of the instructions use inherent addressing. None of these affect the memory contents.

This family of instructions can now be defined using the framing schemas above.

46

The index register and stack pointer can be loaded from memory:

```

LDX

\phiXLoad

opBase = 0xCE

RR = Reg(X)

SReg = { X<sub>H</sub> \mapsto Mem(M),

X_L \mapsto Mem(M+1) }

SCCR = { N \mapsto RR<sub>15</sub>,

Z \mapsto zero(RR),

V \mapsto 0 }

```

```

LDS

\phiXLoad

OpBase = 0x8E

RR = Reg(SP)

SReg = { SP<sub>H</sub> \mapsto Mem(M),

SP<sub>L</sub> \mapsto Mem(M+1) }

SCCR = { N \mapsto RR<sub>15</sub>,

Z \mapsto zero(RR),

V \mapsto 0 }

```

and stored into memory:

```

STX = \\ \phi XStore

OpBase = 0xCF

RR = Reg(X)

SReg = 0

SCCR = \{ N \mapsto RR_{15}, \\ Z \mapsto zero(RR), \\ V \mapsto 0 \}

SMem = \{ M \mapsto Reg(X_H), M+1 \mapsto Reg(X_L) \}

```

```

STS

\phi X Store

0pBase = 0x8F

RR = Reg(SP)

SReg = 0

SCCR = \{ N \mapsto RR_{15}, Z \mapsto zero(RR), V \mapsto 0 \}

SMem = \{ M \mapsto Reg(SP_H), M+1 \mapsto Reg(SP_L) \}

```

They can also be transferred back and forth:

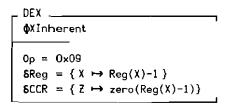

TXS  $\phi$ XInherent 0p = 0x35  $\delta$ Reg = { SP  $\mapsto$  Reg(X)-1 }  $\delta$ CCR = Ø

Note that the SP is loaded with one less than the contents of the index register and the index register is loaded with one more than the SP in each case. This is for programming convenience so that the index register can be pointed to the first entry on the stack, not the next empty entry.

The index register and stack pointer can both be incremented and decremented. In the case of the index register, the zero flag bit in the CCR is set appropriately. In the case of the stack pointer, the CCR is not affected.

INX  $\phi$ XInherent Op = 0x08  $\delta$ Reg = { X  $\mapsto$  Reg(X)+1 }  $\delta$ CCR = { Z  $\mapsto$  zero(Reg(X)-1) }

INS \_\_\_\_\_  $\phi$ XInherent  $O_p = 0 \times 31$   $\delta$ Reg = { SP  $\mapsto$  Reg(SP)+1 }  $\delta$ CCR = Ø

DES \_\_\_\_\_\_  $\phi$ XInherent \_\_\_\_\_  $O_P = O_x34$   $\delta$ Reg = { SP  $\mapsto$  Reg(SP)-1 }  $\delta$ CCR = Ø The index register can be compared with memory:

CPX  $\Phi XLoad$ OpBase = 0x8C RR = Reg(X) - Mem(M+1)  $\cap$  Mem(M) SReg = Ø SCCR = { N  $\mapsto$  RR<sub>15</sub>, Z  $\mapsto$  zero(RR), V  $\mapsto$  X<sub>15</sub>  $\bullet \sim \forall 7_{7} \bullet \sim \forall R_{15} \bullet \forall 7_{7} \bullet RR_{15} }$

The 6800 includes the following instructions involving the index register and/or stack pointer:

IndexOp ♠ LDX V LDS V STX V STS V TXS V TSX V INX V INS V DEX V DES V CPX

#### 5.4 Branch and Jump instructions

All "branch" instructions use the relative addressing mode. They leave the memory unchanged and take four cycles to execute. The CCR is not affected. If a branch condition occurs, then the PC is updated with the relative offset. Otherwise the program proceeds to the next instruction as normal.

The 6800 has the following branch instructions:

| BRA | ≘ | <b>@Branch  </b> 0p = 0x20 ^ Cond = 1                                                 |

|-----|---|---------------------------------------------------------------------------------------|

| BCC | ≘ | $\Phi B$ ranch   Op = 0x24 $\wedge$ Cond = $\sim C_{cc}$                              |

| BCS | ≙ | $\Phi$ Branch   Op = 0x25 $\wedge$ Cond = C <sub>cc</sub>                             |

| BEQ | ≙ | $\Phi$ Branch   Op = 0x27 $\wedge$ Cond = Z <sub>cc</sub>                             |

| BGE | â | $\Phi$ Branch   0p = 0x2C $\wedge$ Cond = $\sim (N_{cc} \oplus V_{cc})$               |

| BGT | ≙ | $\phi$ Branch   Op = 0x2E $\land$ Cond = $\sim$ ( $Z_{cc} + (N_{cc} \oplus V_{cc})$ ) |

| BHI | ≙ | $\phi$ Branch   Op = 0x22 $\wedge$ Cond = $\sim$ (C <sub>cc</sub> +Z <sub>cc</sub> )  |

| BLE | ≙ | $\phi$ Branch   Op = 0x2F ∧ Cond = $Z_{cc} + (N_{cc} \oplus V_{cc})$                  |

| BLS | ≙ | <b>¢Branch  </b> Op = 0x23 ^ Cond = C <sub>ec</sub> +Z <sub>ec</sub>                  |

| BLT | ≙ | <b>¢8</b> ranch   Op = 0x2D ∧ Cond ≂ N <sub>cc</sub> ⊕V <sub>cc</sub>                 |

| BMI | ≙ | <b>∲B</b> ranch   Op = 0x2B ∧ Cond = N <sub>ee</sub>                                  |

| BNE | ₽ | <b><math>\phi</math>Branch   Op = 0x26 ^ Cond = <math>\mathbf{z}_{cc}</math></b>      |

| BVC | ≙ | <b>∲B</b> ranch   Op = 0x28 ∧ Cond = ~V <sub>cc</sub>                                 |

| 8VS | ≙ | <b><math>\phi</math>Branch</b>   Op = 0x29 $\land$ Cond = $V_{cc}$                    |

| BPL | ê | <b>¢Branch  </b> Op = 0xZA ∧ Cond = ~N <sub>cc</sub>                                  |

|     |   |                                                                                       |

There is also a "Branch to Subroutine" instruction, which saves the return address on the stack and calculates a new value for the PC:

There is a "Jump" instruction. Indexed and extended addressing modes may be used. The memory and CCR contents are unaffected.

There is a "Jump to Subroutine" instruction, similar to the JMP instruction, which saves the return address on the stack. The number of cycles taken to execute this instruction does not obey the normal rules which apply to all other instructions with multiple addressing modes.

> JSR  $\oint Mode =$   $Mode \in \{ Indexed, Extended \}$  OpBase = 0xBD  $Mode = Indexed \Rightarrow Cycles = 8$   $Mode = Extended \Rightarrow Cycles = 9$   $\& Mem = \{ Mem(Reg(SP)-1) \mapsto hi(Next), Mem(Reg(SP)) \mapsto lo(Next) \}$   $\& Reg = \{ PC \mapsto H \}$   $SP \mapsto Reg(SP)-2 \}$  $\& CCR = \emptyset$

The 6800 includes the following branch and jump instructions:

BranchOp ≙ BRA V BCC V BCS V BEQ V BCE V BCT V BHI V BLE V BLS V BLT V BMI V BNE V BYC V BYS V BPL V JMP V JSR

#### 5.5 Condition Code Register instructions

This set of instructions use inherent addressing and do not affect the memory contents. Most of the instructions update CCR flag bits, but not the rest of the registers.

> ¢CCR ¢Inherent ΞMemory Cycles = CyclesBase δReg = Ø

The following instructions may be performed to clear and set individual Condition Code Register bits:

$\begin{array}{rcl} \mathsf{CLC} & \cong & \varphi\mathsf{CCR} & \mid & \mathsf{Op} = & \mathsf{0} \times \mathsf{0C} & \land & \mathsf{SCCR} = \{\mathsf{C} \mapsto \mathsf{0}\}\\ \mathsf{CLI} & \cong & \varphi\mathsf{CCR} & \mid & \mathsf{Op} = & \mathsf{0} \times \mathsf{0E} & \land & \mathsf{SCCR} = \{\mathsf{I} \mapsto \mathsf{0}\}\\ \mathsf{CLV} & \cong & \varphi\mathsf{CCR} & \mid & \mathsf{Op} = & \mathsf{0} \times \mathsf{0A} & \land & \mathsf{SCCR} = \{\mathsf{V} \mapsto \mathsf{0}\}\\ \mathsf{SEC} & \cong & \varphi\mathsf{CCR} & \mid & \mathsf{Op} = & \mathsf{0} \times \mathsf{0D} & \land & \mathsf{SCCR} = \{\mathsf{C} \mapsto \mathsf{1}\}\\ \mathsf{SEI} & \cong & \varphi\mathsf{CCR} & \mid & \mathsf{Op} = & \mathsf{0} \times \mathsf{0F} & \land & \mathsf{SCCR} = \{\mathsf{I} \mapsto \mathsf{1}\}\\ \mathsf{SEV} & \cong & \varphi\mathsf{CCR} & \mid & \mathsf{Op} = & \mathsf{0} \times \mathsf{0B} & \land & \mathsf{SCCR} = \{\mathsf{V} \mapsto \mathsf{1}\}\\ \end{array}$

The setable bits of the CCR may be loaded from accumulator A:

TAP  $\triangleq \Phi CCR \mid O_P = 0 \times 06 \land \delta CCR = Reg(A)$

Conversely, accumulator A may be loaded with the contents of the CCR:

These operations may be collected together as a family of instructions:

CCROp ⊆ CLC V CLI V CLV V SEC V SEI V SEV V TAP V TPA

# 5.6 Miscellaneous instructions

There is a "No Operation" instruction which does nothing but pass program control to the next instruction:

NOP \$\phi Inherent \$\frac{1}{2}M6800 \$\phi = 0x01 Cycles = CyclesBase

There is a "Return from Subroutine" instruction. The PC is restored from the stack. The memory contents and the CCR are left unaffected.

| _ RTS                                                    |

|----------------------------------------------------------|

| <b>¢</b> Inherent                                        |

| Ellemory                                                 |

|                                                          |

| $0p = 0 \times 39$                                       |

| Cycles = 5                                               |

| $\mathbf{\delta}Reg = \{PC_{H} \mapsto Mem(Reg(SP)+1),\$ |

| $PC_{L} \mapsto Mem(Reg(SP)+2),$                         |

| SP → Reg(SP)+2 }                                         |

| SCCR = Ø                                                 |

There is a "Software Interrupt" instruction. This simulates an interrupt using its own vector.

There is a "Wait for Interrupt" instruction. This stacks the registers and then waits for an IRQ (if the interrupt mask bit in the CCR is not set) or an NMI interrupt to occur, or for the system to be reset. Unless an external interrupt is received, the program will be suspended forever.

| _ HAI                                                              |         | _ |

|--------------------------------------------------------------------|---------|---|

| <b></b>                                                            |         | ' |

| •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• |         |   |

| 0p = 0×3E                                                          |         |   |

| Cycles ≥ 9                                                         |         |   |

| Vector € {0xFFF8, 0xFFFC,                                          | 0×FFFE} |   |

| $I_{cc} = 0 \implies Vector \neq 0 \times FFF8$                    |         |   |

There is a "Return from Interrupt" instruction. The registers are all restored from the stack. The memory contents are left unaffected. The CCR is loaded from a memory byte on the stack but the individual bits are not subsequently affected by the instruction.

| _ RTI                            |

|----------------------------------|

| <b><math>\phi</math>Inherent</b> |

| Ellemory                         |

|                                  |

| 0p = 0x3B                        |

| Cycles = 10                      |

| δReg = { CCR ↦ Mem(Reg(SP)+1),   |

| B ↦ Mem(Reg(SP)+2),              |

| A ↦ Mem(Reg(SP)+3),              |

| $X_{H} \mapsto Mem(Reg(SP)+4),$  |

| $X_{L} \mapsto Mem(Reg(SP)+5),$  |

| $PC_{H} \mapsto Mem(Reg(SP)+6),$ |

| $PC_{L} \mapsto Mem(Reg(SP)+7),$ |

| SP $\mapsto$ Reg(SP)+7 }         |

| SCCR = 0                         |

The 6800 includes the following miscellaneous instructions:

# 6. Overall operation

Op-codes which have not so far been specified are considered illegal. The state of the system after the execution of such an op-code is undefined.

Illegal0p ≙ ∆M6800 | Mode = Illegal

This specification could be tightened if more were known about an illegal instruction. For example, at present this specification allows the contents of the registers and RAM to be entirely changed after an illegal instruction. If more information were available, predicates could be added to this schema.

The following groups of legal instructions discussed in previous sections may be executed by the 6800. We project the (change of) state of the 6800 since we are not interested in any of the temporary components defined in each of the individual instruction schemas for the convenience of the specification.

LegalOp ≑ (AccMemOp V IndexOp V BranchOp V CCROp V MiscOp) 1 446800

The system has three possible sources of external interrupt:

ExtInterrupt ♀ (IRQ V NMI V Reset) | Mode = Interrupt

The priority of external interrupts has not been defined above (i.e. if two interrupts occur simultaneously either could be serviced first) since the documentation used [8,9] did not make any ordering clear. Such details could easily be included in the formal definition of the 6800 by including the status of the external interrupts as part of the state.

Each operation execution of the 6800 consists of the execution of an instruction (legal or otherwise) or an external interrupt:

```

Instruction ≙ I)legalOp ⊕ LegalOp

Exec ≙ Instruction V ExtInterrupt

```

When the 6800 is started, a sequence of such operations is executed depending on the contents of memory and (non-deterministically in this specification) on the occurence of external interrupts.

Given the specification of each of the instructions, it is possible to consider sequences of instructions and prove (in the absence of any external interrupts) properties of such sequences. For example, often a decrement instruction is followed by a conditional branch instruction at the end of a loop. We could prove the following properties of such a construct:

```

DEXBNE \Rightarrow DEXTAM6800 ; BNETAM6800

DEXBNE \vdash Reg(X)\neq1 \Rightarrow Reg'(PC) = (Reg(PC)+3)±Mem(Reg(PC)+2)

DEXBNE \vdash Reg(X)=1 \Rightarrow Reg'(PC) = Reg(PC)+3

```

#### 7. Conclusion

The instruction set of the Motorola 6800 microprocessor has been formally specified. Enough experience has been gained so that more complicated and modern microprocessors such as the 68000 family could be specified in a similar manner. However such processors would require a larger document and more work in order to cover them fully.

The specification of the instructions have been factored out using framing schemas to reduce the overall length of the specification given here. If Z where to be used to present an instruction set in the form of a manual, then it is anticipated that each instruction would be allocated at least a page with an expanded schema allowing easy reference for the instruction on that page alone. A possible example layout is shown in Appendix A.

Z has proved an excellent tool for specifying a microprocessor instruction set. The length of the specification is very favourable with the more informal methods currently used for instruction set documentation in industry and elsewhere. Not only that, but we also gain a means of formally reasoning about the properties of the instruction set. This could prove to be invaluable, especially at the design stage. In the future, computer-based tools should be available to check consistency and give assistance with proofs. It is to be hoped that manufacturers will adopt such methods in duecourse.

### 8. Acknowledgements

Thank you to the developers of the Z specification language at the PRG and the inventors of the 6800 microprocessor at Motorola. Carroll Morgan, Tim Gleeson and Brian Monahan at the PRG provided helpful comments on early drafts. Ruaridh Macdonald at RSRE, Malvern and Stephen Murrell at the University of Miami also gave some useful suggestions. Steve Heath of Motorola, UK and Rajit Chandra of Intel, California commented on the paper from a manufacturer's point of view. Roger Gimson, Karen Paliwoda, Stig Topp-Jorgensen and Bernard Sufrin at the PRG kindly checked later drafts.

#### 9. References

- 1. Hunt, W. A. "FM8501: A Verified Microprocessor", Technical Report 47. Institute for Computing Science, The University of Texas at Austin, (1986).

- Sufrin, B. A. (Editor) "Z Handbook", Draft 1.1, Programming Research Group, Oxford University, (1986).

- Spivey, J. M. "Understanding Z: A Specification Language and its Formal Semantics", DPhil Thesis, Programming Research Group, Oxford University, (1985).

- Spivey, J. M. "The Z Library A Reference Manual", Programming Research Group, Oxford University, (1986).

- 5. Woodcock, J. "Structuring Specifications Notes on the Schema Notation", Programming Research Group, Oxford University, (1986).

- King, S., Sørensen, I., Woodcock, J. "Z: Concrete and Abstract Syntaxes", Version 1.0, Programming Research Group, Oxford University, (1987).

- Hayes, I. J. (Editor) "Specification Case Studies", Prentice-Hall International Series in Computer Science, (1987).

- 8. "M6800 Microprocessor Programming Manual", Motorola Semiconductor Products Inc., (1975).

- 9. "M6800 Microprocessor Instruction Set Summary", Motorola Microcomputer Applications Engineering.

# Appendix A

# Example manual pages

An example layout for two instructions in a 6800 microprocessor instruction set manual are given overleaf. It is suggested that each instruction should be given a page like this in such a manual to allow quick reference for a particular instruction without the necessity for cross reference, once the framework of the specification has been assimilated by the reader.

### Branch if Greater Than sero

# Operation

BGT  $\Delta M5800$ Cond : Bit  $O_{p} = 0x2E$ Mode = Relative NBytes = 2 Cycles = 4 Cond = Z<sub>cc</sub>+(N<sub>cc</sub>•V<sub>cc</sub>) Cond = 0  $\Rightarrow$  SReg = Ø Cond = 1  $\Rightarrow$  SReg = {PC  $\mapsto$  Next±Mem(Reg(PC)+1)} SCCR = Ø SMem = Ø

# Description

Causes a branch if Z is set or one of N and V (but not both) is set.

If the BGI instruction is executed immediately after execution of any of the instructions CBA, CMP, SBA, or SUB, the branch will occur if and only if the two's complement number represented by the minuend (i.e. accumulator A or B contents) was greater than the two's complement number represented by the subtrahend (i.e. memory contents).

Only the PC is affected. If a branch occurs, then the PC is updated with the relative offset, otherwise the program proceeds to the next instruction as normal.

#### Jump to Subroutine

### Operation

```

JSR

AN6800

(0p

\approx 0xAD

No de

= Indexed

NBytes = 2

Cycles = 8

\delta Reg = \{ PC \mapsto Reg(X) + Mem(Reg(PC) + 1) \},

SP \mapsto Reg(SP)-2

(0p = 0 \times BD)

Mode = Extended

NBytes = 3

Cycles = 9

\delta Reg = \{ PC_{H} \mapsto Mem(Reg(PC)+1), \}

\begin{array}{rcl} & \operatorname{PC}_{L} & \mapsto & \operatorname{Mem}(\operatorname{Reg}(\operatorname{PC})+2), \\ & \operatorname{SP} & \mapsto & \operatorname{Reg}(\operatorname{SP})-2 \end{array} \right)

8CCR = Ø

\delta Mem = \{ Mem(Reg(SP)-1) \mapsto hi(Next), \}

Mem(Reg(SP)) \rightarrow lo(Next)

```

# Description

The program counter is incremented by 2 or by 3, depending on the addressing mode, and is then pushed onto the stack, eight bits at a time. The stack pointer points to the next empty location on the stack. A jump occurs to the instruction stored at the numerical address, obtained according to the addressing mode.

# Appendix B

# Mathematical and Schema notation

A glossary of the Z mathematical and schema notation used in this monograph is included here for easy reference. Readers should note that the definitive concrete and abstract syntax for Z is available elsewhere [5].

# Z Reference Glossary

Mathematical Notation

# 1. Definitions and declarations.

Let  $x, x_i$  be identifiers and let  $T, T_i$  sets.

[T<sub>1</sub>, T<sub>2</sub>] Introduction of generic sets. LHS a RHS Definition of LHS as syntactically equivalent to RHS. T ::= x<sub>1</sub> | x<sub>2</sub> | ... | x<sub>n</sub> Data type definition. x : T Declaration of x as type T. x<sub>1</sub>: T<sub>1</sub>; x<sub>2</sub>: T<sub>2</sub>; ... ; x<sub>n</sub>: T<sub>n</sub> List of declarations. x<sub>1</sub>, x<sub>2</sub>, ..., x<sub>n</sub>: T a x<sub>1</sub>: T; x<sub>2</sub>: T; ... ; x<sub>n</sub>:T.

#### 2. Logic.

Let P. Q be predicates and D declarations.

| - P      | Negation: "not P".                                  |

|----------|-----------------------------------------------------|

| PAQ      | Conjunction: "P and Q".                             |

| ΡνΩ      | Disjunction: P or Q":                               |

|          | <b>≙</b> ¬(¬P∧ ¬Q).                                 |

| Р 🗕 🛛 👘  | Implication: "P implies Q" or                       |

|          | "if P then Q": ≙ ¬P v Q.                            |

| P ↔ Q    | Equivalence: "P is logically                        |

|          | equivalent to Q":                                   |

|          | $\cong (P \to Q) \land (Q \to P).$                  |

| true     | Logical constant.                                   |

| false    | ≙ -true                                             |

| ∀×∶T     | • P Universal quantification:                       |

|          | "for all $\times$ of type T <sub>1</sub> P holds".  |

| ∃ × : T  | • P Existential quantification:                     |

|          | "there exists an x of type T such                   |

|          | that P".                                            |

| 3, × : T | <ul> <li>P<sub>x</sub> Unique existence:</li> </ul> |

| 1        | "there exists a unique × of type                    |

|          | T such that P".                                     |

|          | ≙ (∃ x : T • P, ^                                   |

|          | n                                                   |

$$\neg (\exists y: I \mid y \neq x \cdot P_y)).$$

$$\forall x_1: T_1; x_2: T_2; \dots; x_n: T_n \cdot P$$

"For all  $x_1$  of type  $T_1$ ,

$x_2$  of type  $T_2, \dots, and$

$x_n$  of type  $T_n, P$  holds."

$$\exists x_1: T_1; x_2: T_2; \dots; x_n: T_n \cdot P$$

Similar to  $\forall$ .

$$\forall D \mid P \cdot Q \triangleq (\forall D \cdot P \Longrightarrow Q).$$

$$\exists D \mid P \cdot Q \triangleq (\exists D \cdot P \land Q).$$

$$D \vdash P$$

Theorem:  $a \vdash \forall D \cdot P.$

#### 3. Sets.

Let S, T and X be sets; t,  $t_k$  terms; P a predicate and D declarations.

| $t_1 = t_2$                        | Equality between terms.                                                 |

|------------------------------------|-------------------------------------------------------------------------|

| t <sub>i</sub> ≠t <sub>z</sub>     | Inequality: $rightarrow \neg (t_1 = t_2)$ .                             |

| t e S                              | Set membership: "t is an element                                        |

|                                    | of S".                                                                  |

| t⊈S                                | Non-membership: °¬(t ∈ S).                                              |

| ø                                  | Emptyset: ≘{x:Xifelse}.                                                 |

| S⊆T                                | Set inclusion:                                                          |

|                                    | <pre></pre>                                                             |

| ScT                                | Strict set inclusion:                                                   |

|                                    | ≙ S⊆T≜S≠T.                                                              |

| {t <sub>1</sub> , t <sub>2</sub> , | , t <sub>n</sub> } The set                                              |

|                                    | containing $t_1, t_2, \dots$ and $t_n$ .                                |

| {x:T]                              | P }                                                                     |

|                                    | The set containing exactly those                                        |

|                                    | x of type T for which P holds.                                          |

| (t <sub>1</sub> , t <sub>2</sub> , | , t <sub>n</sub> ) Ordered n-tuple                                      |

|                                    | of $t_1, t_2, \ldots$ and $t_n$ .                                       |

| T <sub>1</sub> × T <sub>2</sub> ×  | $\ldots \times T_n$ Cartesian product:                                  |

|                                    | the set of all n-tuples such that                                       |

|                                    | the kth component is of type T <sub>k</sub> .                           |

| ${x_1:T_1;}$                       | x <sub>2</sub> :T <sub>2</sub> ; ; x <sub>n</sub> :T <sub>n</sub>   P } |

|                                    | The set of n-tuples                                                     |

|                                    | $(x_1, x_2, \ldots, x_n)$ with each                                     |

|                                    | $x_k$ of type $T_k$ such that P holds.                                  |

|                                    |                                                                         |

| {D   P •                | t }                                                                              |

|-------------------------|----------------------------------------------------------------------------------|

|                         | The set of t's such that given                                                   |

|                         | the declarations D, P holds.                                                     |

| $\{D \cdot t\}$         | <pre></pre>                                                                      |

| PS                      | Powerset: the set of all subsets                                                 |

|                         | of S.                                                                            |

| <b>P</b> <sub>1</sub> S | Non-empty powerset:                                                              |

| -                       | P₁S ≈ PS \ {∅}.                                                                  |

| FS                      | Set of finite subsets of S:                                                      |

|                         | ≘ {T: PS   T is finite}.                                                         |

| <b>F</b> <sub>1</sub> S | Non-empty finite set:                                                            |

|                         | $\mathbf{F}_1 \mathbf{S} \cong \mathbf{F} \mathbf{S} \setminus \{ \emptyset \}.$ |

| SNT                     | Set intersection: given S, T: PX,                                                |

|                         | <b>≙ {x:X   x € S ∧ x € T}</b> .                                                 |

| SUT                     | Set union: given S, T: PX,                                                       |

|                         | $\triangleq \{ x : X \mid x \in S \lor x \in T \}.$                              |

| SΛT                     | Set difference: given S, T: PX,                                                  |

|                         | ≙ {x:X ] x € S ∧ x ∉ T}.                                                         |

| n ss                    | Distributed set intersection:                                                    |

|                         | given SS: P (P X),                                                               |

|                         | <b>⊇</b> {x:X   (∀S:SS • x € S)}.                                                |

| USS                     | Distributed set union:                                                           |

|                         | given SS: P (P X),                                                               |

|                         | $ \{ x: X \mid (\exists S: SS + x \in S) \}. $                                   |

| <b>#</b> S              | Size (number of distinct                                                         |

|                         | elements) of a finite set.                                                       |

| μS                      | Arbitrary choice from a set.                                                     |

# 4. Relations.

A relation is modelled by a set of ordered pairs hence operators defined for sets can be used on relations.

Let X, Y, and Z be sets; x: X; y: Y; and R:  $X \leftrightarrow Y$ .

| X ↔ Y | The set of relations from X to Y: |

|-------|-----------------------------------|

|       | ≏ ₽ (X × Y).                      |

x R y x is related by R to y: A (x, y) € R. (R is often underlined for clarity.)

| x ⊷ y                              | ≙ (x,y).                                                                                          |

|------------------------------------|---------------------------------------------------------------------------------------------------|

| { × <sub>1</sub> ⇔y <sub>1</sub> , | $x_2 \mapsto y_2, \ldots, x_n \mapsto y_n \}$                                                     |

|                                    | The relation                                                                                      |

|                                    | $\{(x_1, y_1), \ldots, (x_n, y_n)\}$                                                              |

|                                    | relating $\times_1$ to $y_1, \ldots$ , and                                                        |

|                                    | ×, koy,                                                                                           |

| dom R                              | The domain of a relation:                                                                         |

|                                    | ● { x:X   ∃y:Y • x R y }.                                                                         |

| ren R                              | The range of a relation:                                                                          |

|                                    | ≜ { y:Y   ∃x:X • x R y }.                                                                         |

| $R_1 \parallel R_2$                | Forward relational composition:                                                                   |

| 1 2                                | given $R_1: X \leftrightarrow Y; R_2: Y \leftrightarrow Z$ ,                                      |

|                                    | <b>a</b> {x:X; z:Z   ∃y:Y •                                                                       |

|                                    | $\times R_1 y \wedge y R_2 z$ }.                                                                  |

| R <sub>1</sub> o R <sub>2</sub>    | Relational composition:                                                                           |

| N1 - N2                            | $\mathbf{R}_2 \neq \mathbf{R}_1$ .                                                                |

| R <sup>-1</sup>                    | Inverse of relation R:                                                                            |

| n                                  |                                                                                                   |

| id X                               | <pre></pre>                                                                                       |

|                                    | -                                                                                                 |

| -k                                 | $\triangleq \{ \mathbf{x} : \mathbf{X} + \mathbf{x} \mapsto \mathbf{x} \}.$                       |

| R <sup>k</sup>                     | The relation R composed with                                                                      |

|                                    | itself k times: given $R : X \leftrightarrow X$ ,                                                 |

|                                    | $\mathbb{R}^0 \cong \operatorname{id} X, \ \mathbb{R}^{k+1} \cong \mathbb{R}^k \circ \mathbb{R}.$ |

| R*                                 | Reflexive transitive closure:                                                                     |

|                                    | $\Delta U \{n: \mathbb{N} \in \mathbb{R}^n\}.$                                                    |

| R⁺                                 | Non-reflexive transitive closure:                                                                 |

|                                    | ● U {n: N <sub>1</sub> • R <sup>n</sup> }.                                                        |

| R(S)                               | Relational image: given S : P X,                                                                  |

|                                    | $ \{ y: Y \mid \exists x : S \cdot x R y \}. $                                                    |

| 5 () R                             | Domain restriction to S:                                                                          |

|                                    | given S: 🗗 X,                                                                                     |

|                                    | ● {x:X;y:Y   x∈S ^ xRy}.                                                                          |

| SAR                                | Domain subtraction:                                                                               |

|                                    | given S: 🗗 X,                                                                                     |

|                                    | ● (X \ S) ∮ R.                                                                                    |

| R⊅T                                | Range restriction to T:                                                                           |