Abbey Bookbinding Co.

(Student Thesis Specialists)

38 Cosmeston Street, Cathays, Cardiff Tel: 395882

D4518483

#### THE APPLICATION OF MICROPROCESSORS

#### TO PULSE-WIDTH-MODULATED

#### INVERTERS

By

#### A.B.WILLIAMS, M.Sc.(WALES)

A dissertation submitted to the C.N.A.A. for the degree of Doctor of Philosophy.

and the second second

SEPTEMBER, 1982.

Department of Electrical and Electronic Engineering, Polytechnic of Wales.

In collaboration with Black Clawson International Limited.

| INTRODUCTION |             |                                                      |          |

|--------------|-------------|------------------------------------------------------|----------|

|              | Com         | mnication Principles                                 | 1        |

|              | Dow         | er Conversion                                        | 3        |

|              |             |                                                      |          |

|              |             | se-Width-Modulation (PWM) Techniques                 | 4.       |

|              | The         | Application Of Large Scale Integrated (LSI) Circuits | 6        |

|              |             |                                                      |          |

| 1.           | PULS        | SE MODULATED POWER CONVERTERS - PRACTICE AND THEORY  | 8        |

|              | 1.1         | Background To The Application Of The Thyristor In    |          |

|              |             | Variable Speed Drives                                | 8        |

|              | 1.2         | Classification Of Present Day Variable Speed         |          |

|              |             | Drives                                               | 9        |

|              |             | 1.2.1 Variable Transformer Types                     | 10       |

|              |             |                                                      | 10       |

|              |             | 1.2.2 The Unrestricted Frequency Converter           |          |

|              |             | 1.2.3 The High Frequency Link Inverter               | 13       |

|              |             | 1.2.4 The Solid State Phase Shift Inverter           | 13       |

|              | 1.3         | Practical Static Inverter Drives For A.C. Motors     | 14       |

|              |             | 1.3.1 The Six Step Voltage Fed Inverter              | 14       |

|              |             | 1.3.2 The Cycloconverter                             | 17       |

|              |             | 1.3.3 Pulse Width Modulation (PWM)                   | 19       |

|              | 1.4         |                                                      | 20       |

| •            | 1.4         |                                                      | 20       |

|              |             | 1.4.1 Types Of Modulation                            |          |

|              |             | 1.4.2 The Unmodulated Pulse Carrier Wave             | 24       |

|              |             | 1.4.3 Pulse Amplitude Modulation                     | 24       |

|              |             | 1.4.4 Pulse Position Modulation                      | 25       |

|              |             | 1.4.5 Pulse Width Modulation                         | 28       |

|              |             | 1.4.6 Trailing-edge Pulse Width Modulation           | 29       |

|              |             | 1.4.7 Leading-edge Pulse Width Modulation            | 33       |

|              |             | 1.4.8 Double-edge Pulse Width Modulation             | 35       |

|              | 1 5         |                                                      | 38       |

|              | 1.5         | <b>▲</b>                                             | 39       |

|              |             | 1.5.1 Specialist PWM Schemes                         | 33<br>42 |

|              |             | 1.5.2 Pulse-Width-Modulation (PWM) Generation        | 44       |

|              |             | 1.5.3 Regular Sampled Asymmetrical Double-edge       |          |

|              |             | Modulation                                           | 44       |

|              |             | 1.5.4 Limitations Of The Regular Sampling Process    |          |

|              |             | In PWM Systems                                       | 46       |

|              | 1.6         |                                                      | 48       |

|              |             |                                                      |          |

| 2.           |             | FORM ANALYSIS OF PWM SIGNALS                         | 50       |

|              | 2.1         | Waveform Analysis                                    | 50       |

|              | 2.2         | Frequency Domain Analysis Of A Two Level PWM         |          |

|              | _           | Waveform                                             | 52       |

|              | 2.3         | Analysis Of The Asymmetrical Regular Sampled PWM     |          |

|              | 2.0         | •                                                    | 61       |

|              | ~ .         | Waveform                                             | 64       |

|              | 2.4         | The Discrete Fourier Transform                       | 69       |

|              | 2.5         | The Discrete Fourier Transform (approximations)      |          |

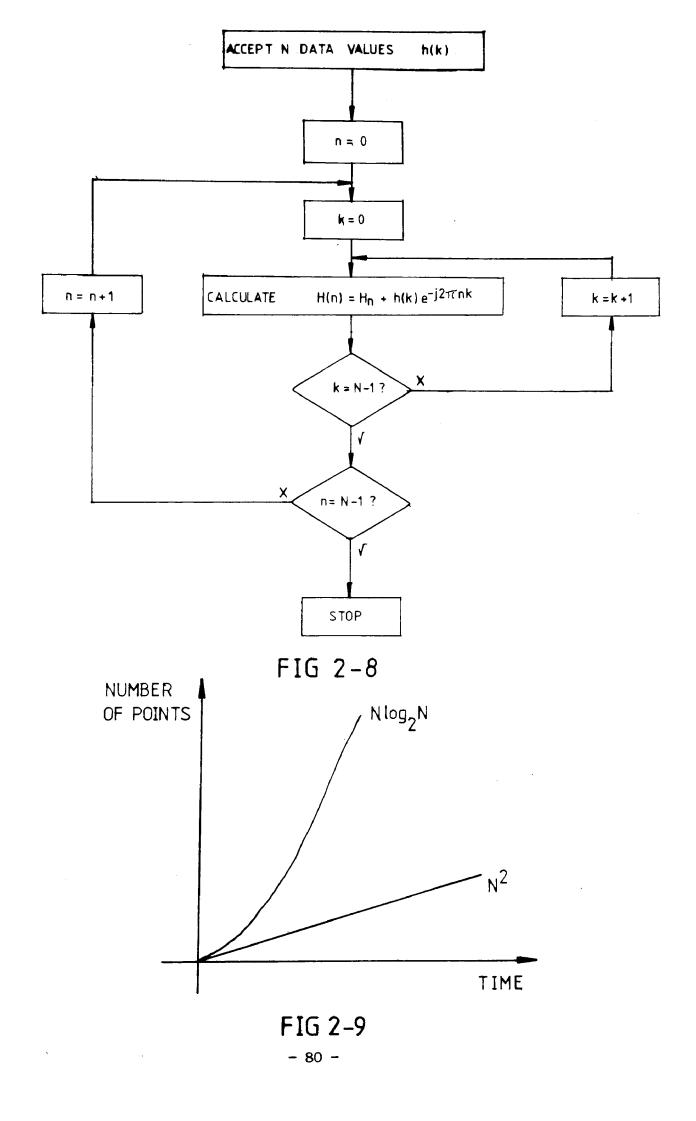

|              | 2.6         | Program Implementation Of The DFT                    | 79       |

|              | 2.7         | 0 1                                                  | 81       |

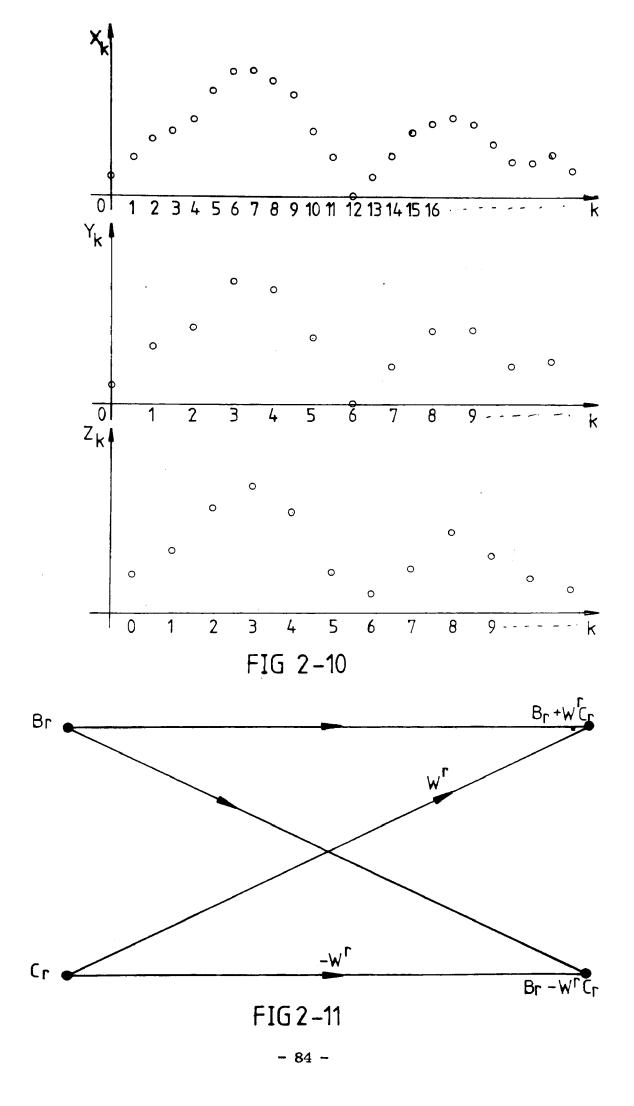

|              | 2.8         |                                                      | 82       |

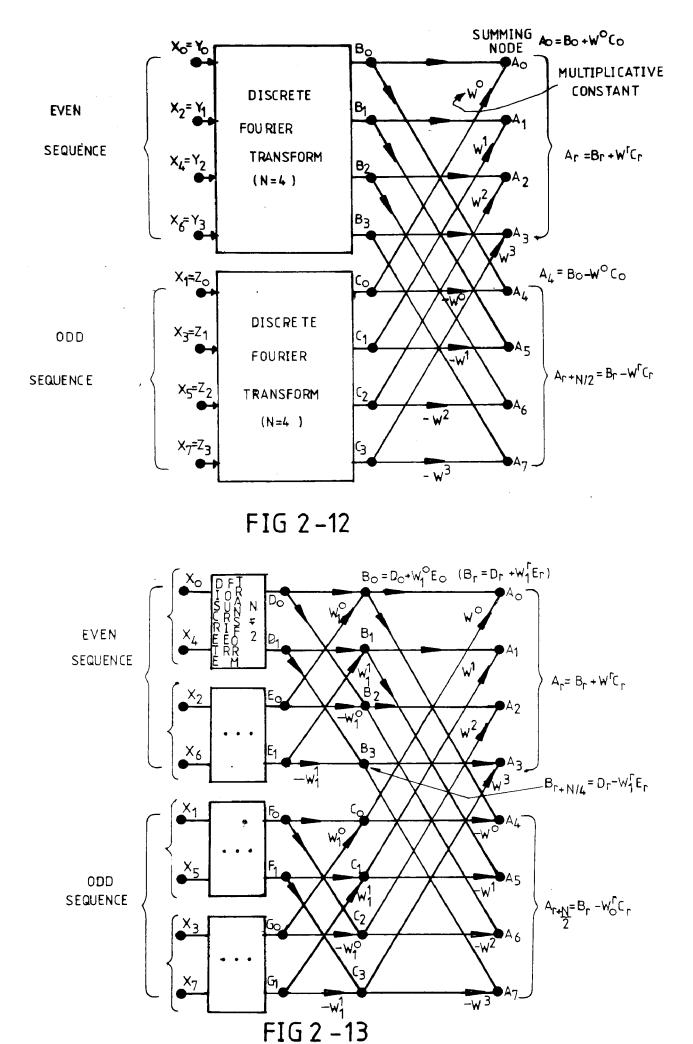

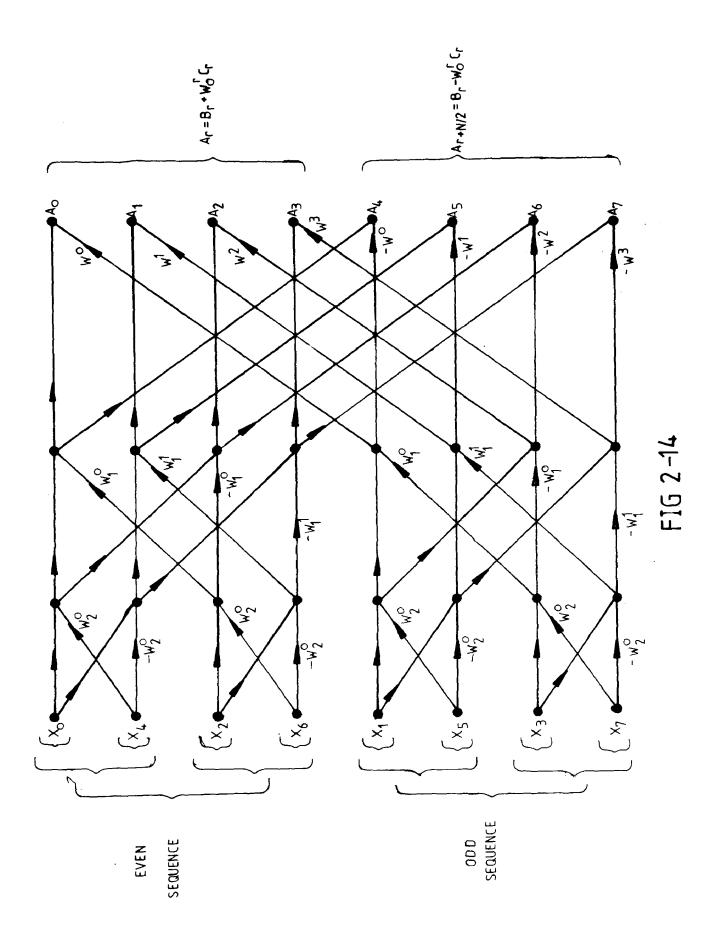

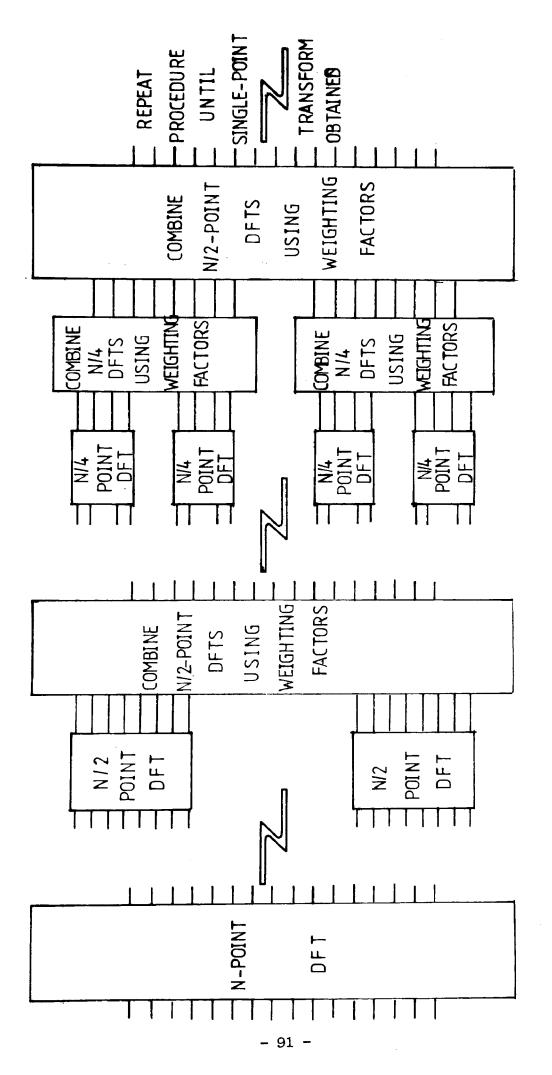

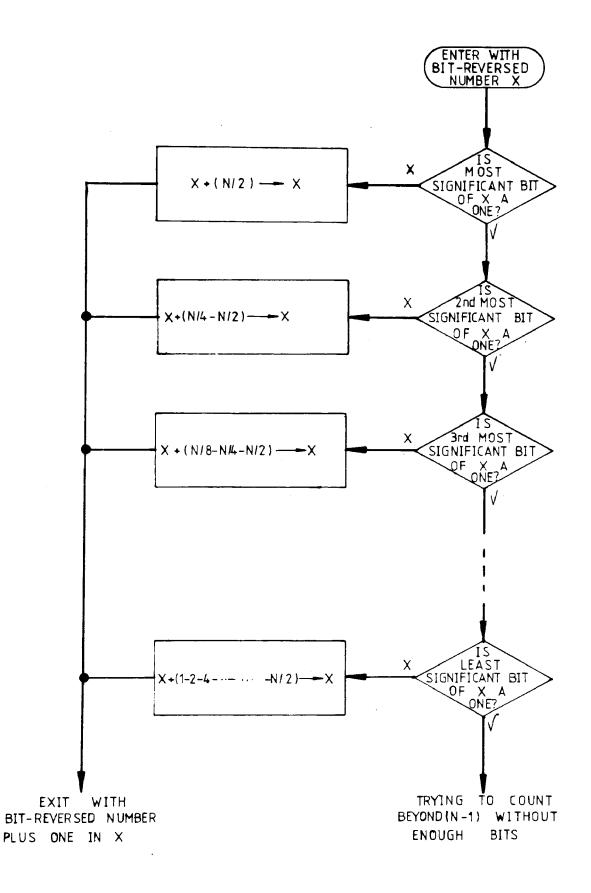

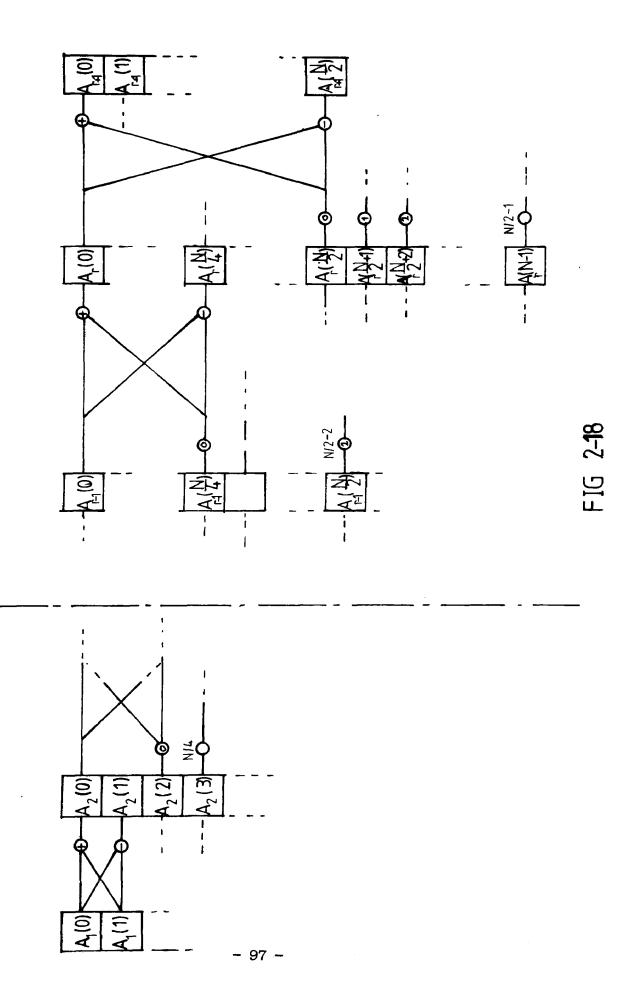

|              | <b>2</b> .0 | 2.8.1 The Decimation In Time Algorithm               | 83       |

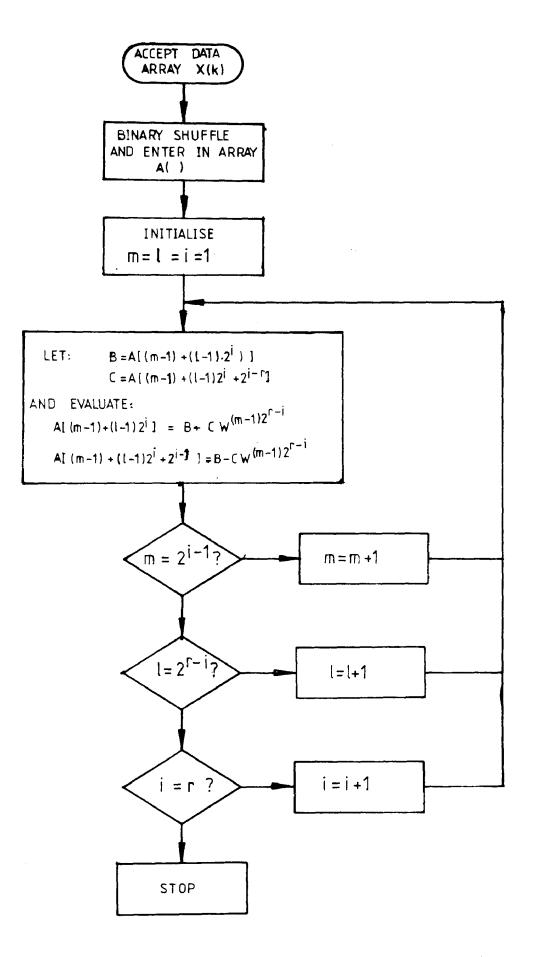

|              | 0 0         | Programming The Algorithm                            | 92       |

|              | 2.9         |                                                      | 92       |

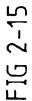

|              |             | 2.9.1 The Binary Reversal Routine                    | 94       |

|              |             | 2.9.2 Programming The Recurring FFT Equation         | 01       |

|              |             |                                                      |          |

| з. |       | PWM CONTROL SYSTEM - THE ANALOGUE APPROACH   | 101 |

|----|-------|----------------------------------------------|-----|

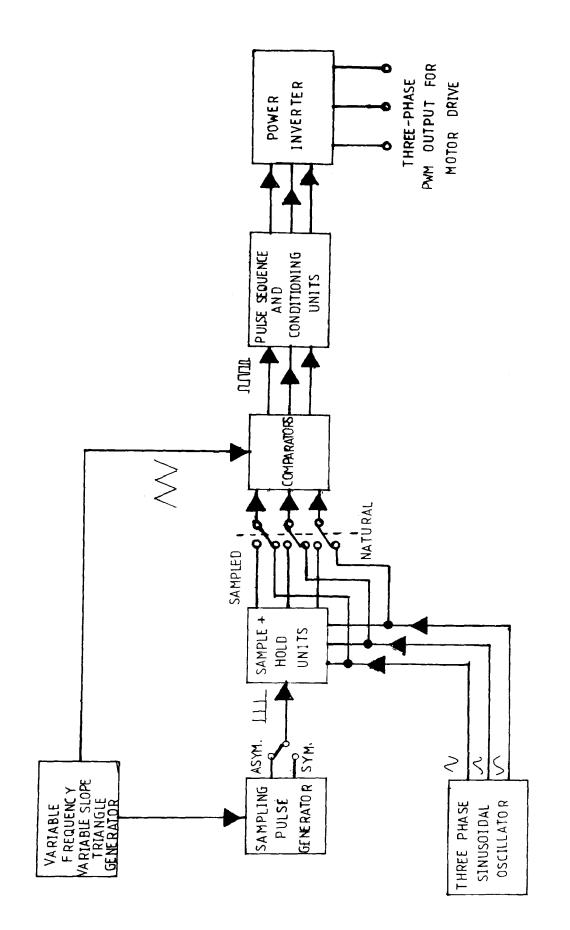

|    | 3.1   | System Realisation Of PWM Techniques         | 101 |

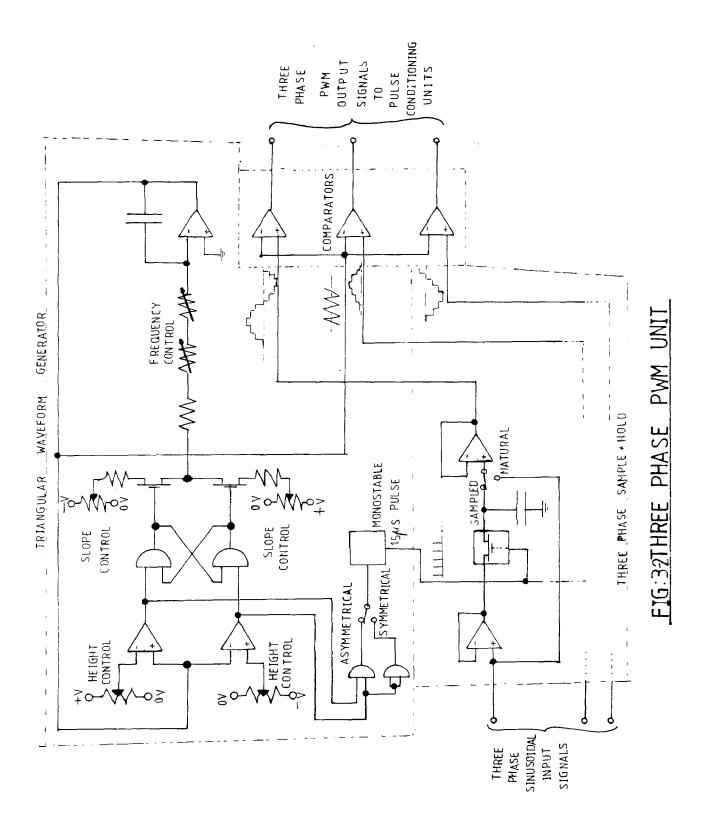

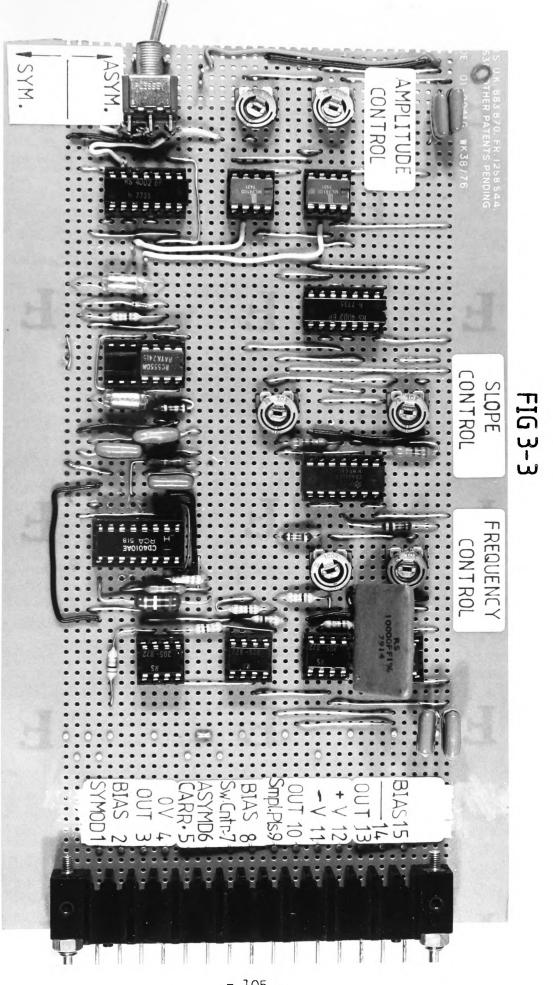

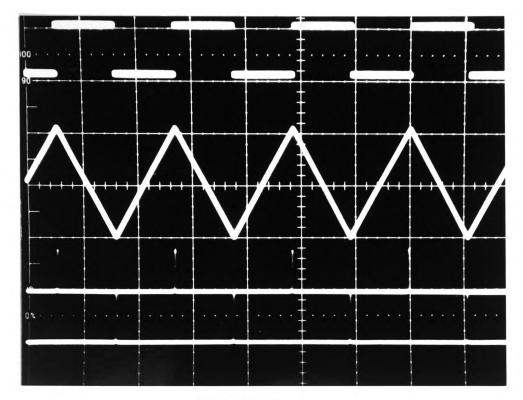

|    |       | 3.1.1 The Carrier Waveform Generation Board  | 103 |

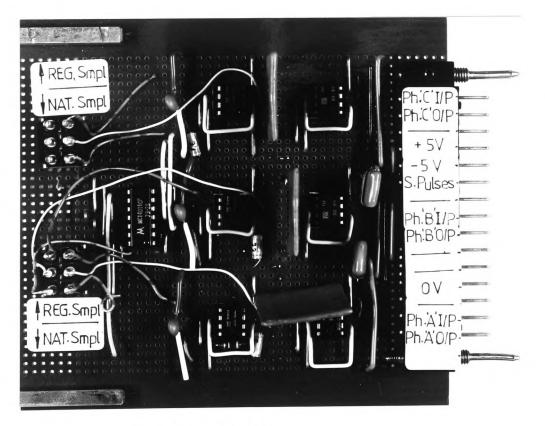

|    |       | 3.1.2 The Three Phase Sample And Hold Unit   | 107 |

|    |       | 3.1.3 The Three Phase Modulating Waveform    |     |

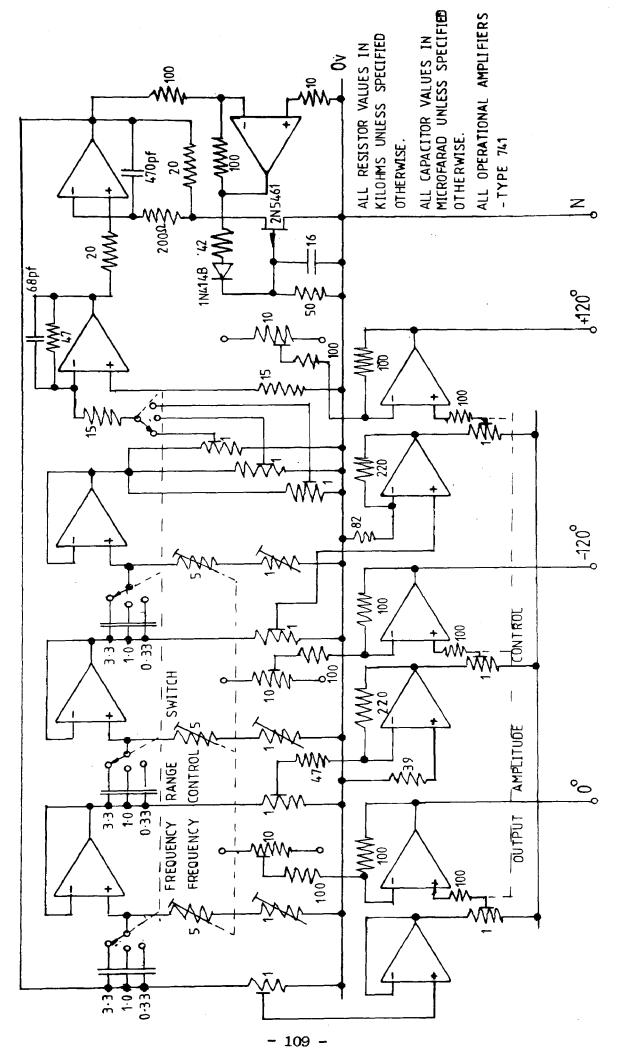

|    |       | Generator                                    | 108 |

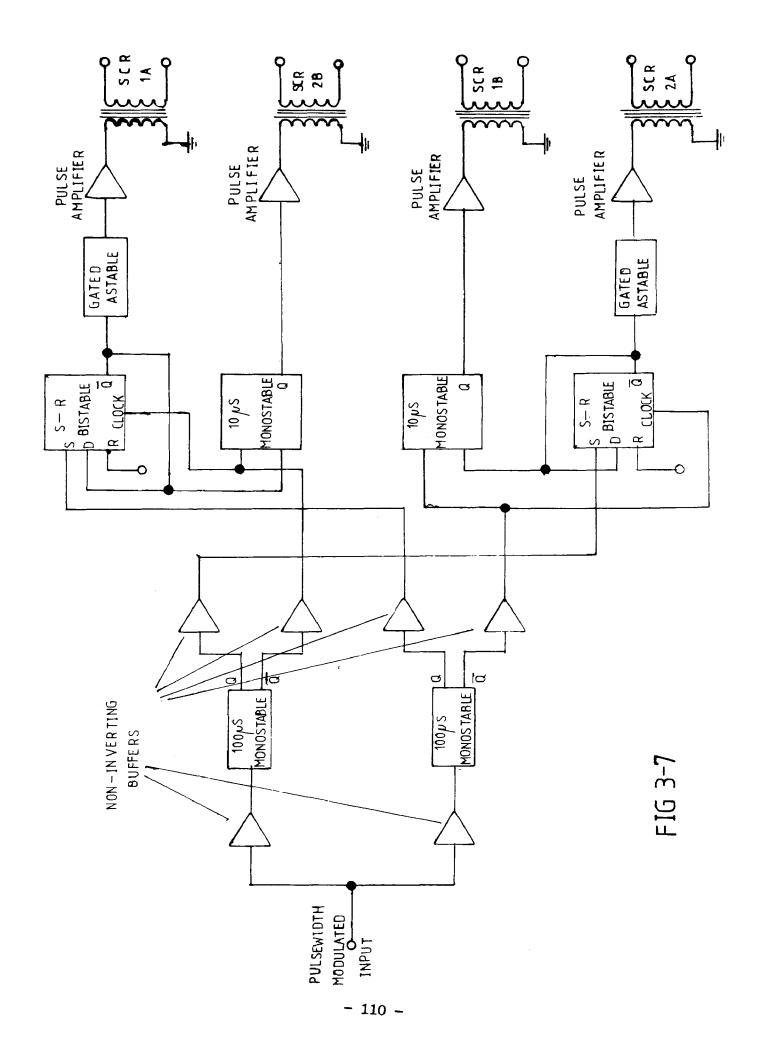

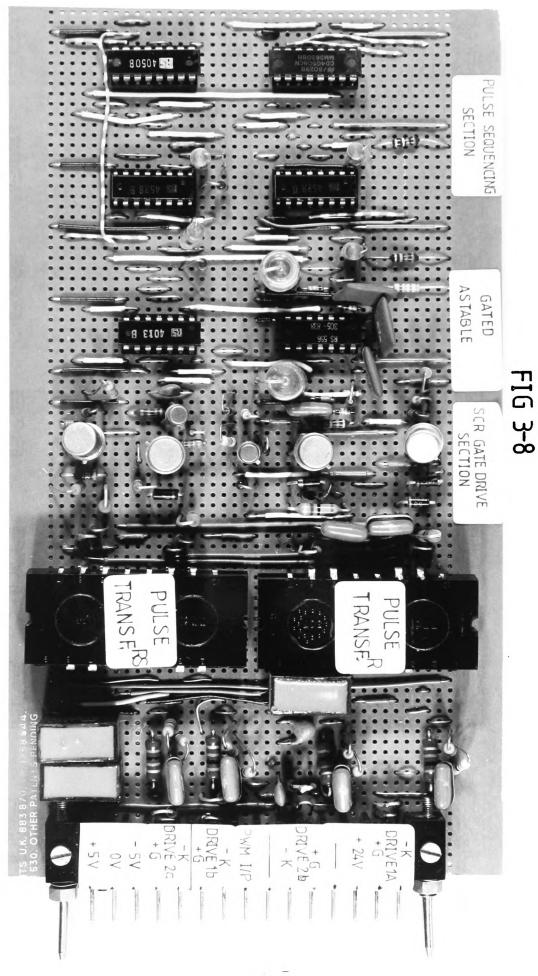

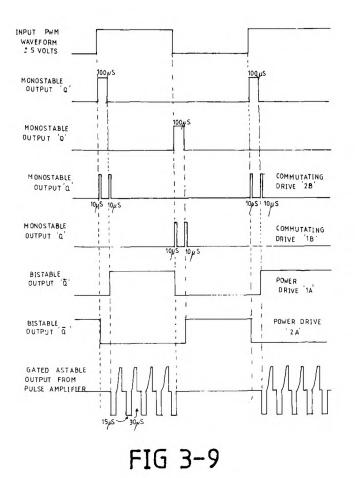

|    |       | 3.1.4 Pulse Sequence And Conditioning Unit   | 108 |

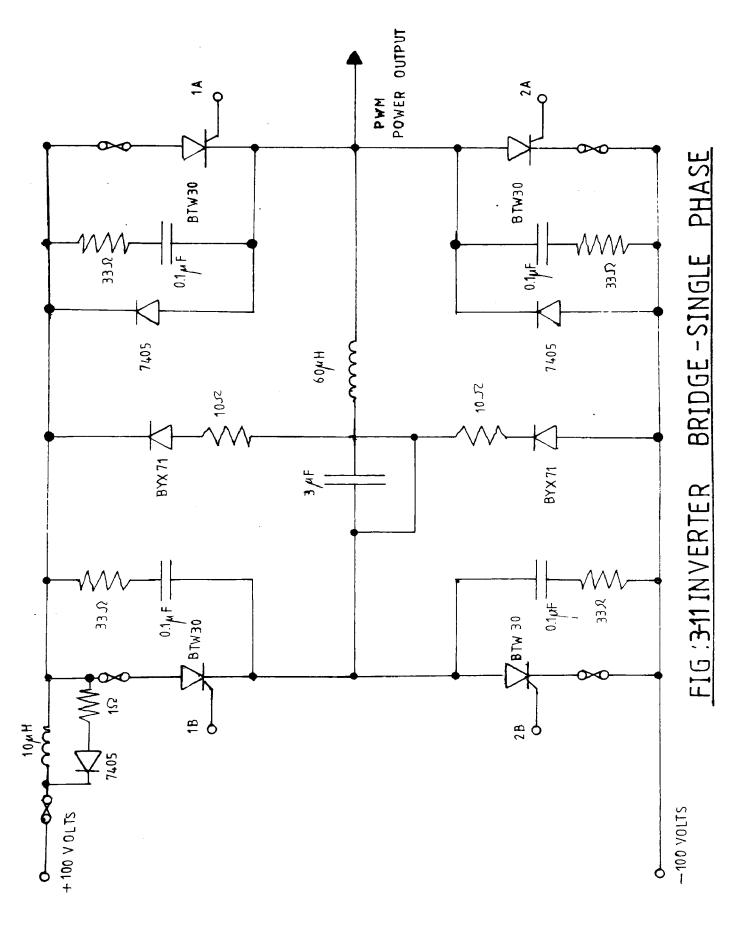

|    |       | 3.1.5 The Mcmurray Bridge Power Inverter     | 114 |

|    | 3.2   | Advanced Semiconductor Technology-discrete   |     |

|    | ÷     | Switching Devices                            | 117 |

|    |       | 3.2.1 The Gate Turn Off Switch               | 117 |

|    |       | 3.2.2 The Bipolar Transistor                 | 119 |

|    |       | 3.2.3 The HEXFET                             | 110 |

|    |       | 3.2.4 VFETS                                  | 120 |

|    | 33    | Integrated Circuits (SSI-LSI)                | 121 |

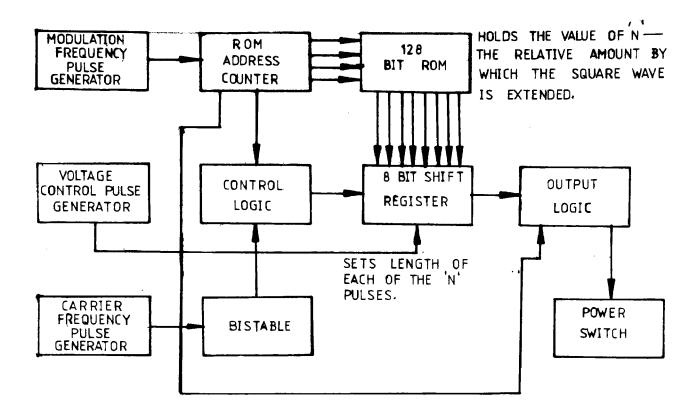

|    | 0.0   | 3.3.1 ROM Pulse Width Modulation             | 125 |

|    |       |                                              | 125 |

|    |       | 3.3.2 The Microprocessor                     | 127 |

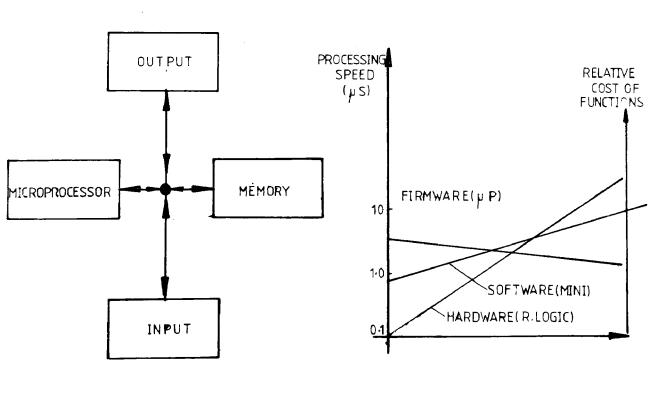

| 4. | PHILO | SOPHY OF MICROPROCESSOR SYSTEM DESIGN        | 132 |

|    | 4.1   | The Criteria For The Adoption Of The         |     |

|    |       | Microprocessor In Place Of Random Logic      | 132 |

|    | 4.2   | Real Time Systems                            | 133 |

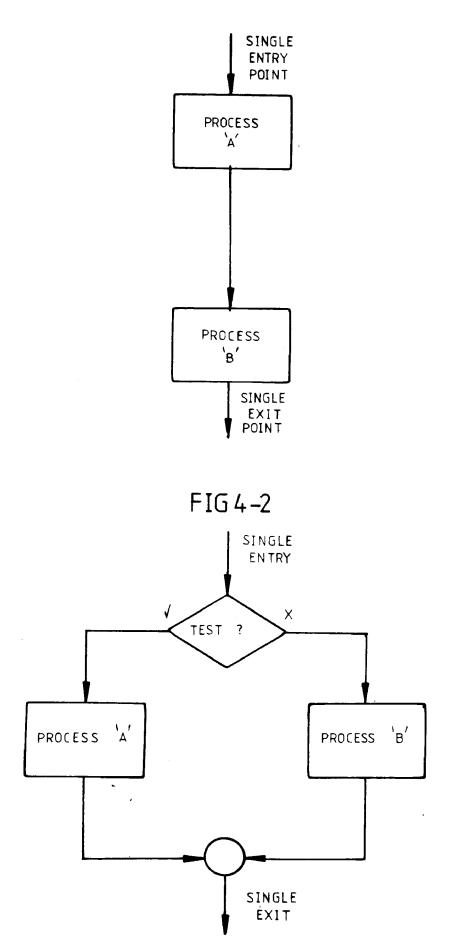

|    | 4.3   | Structured Programming In Assembly Language  | 136 |

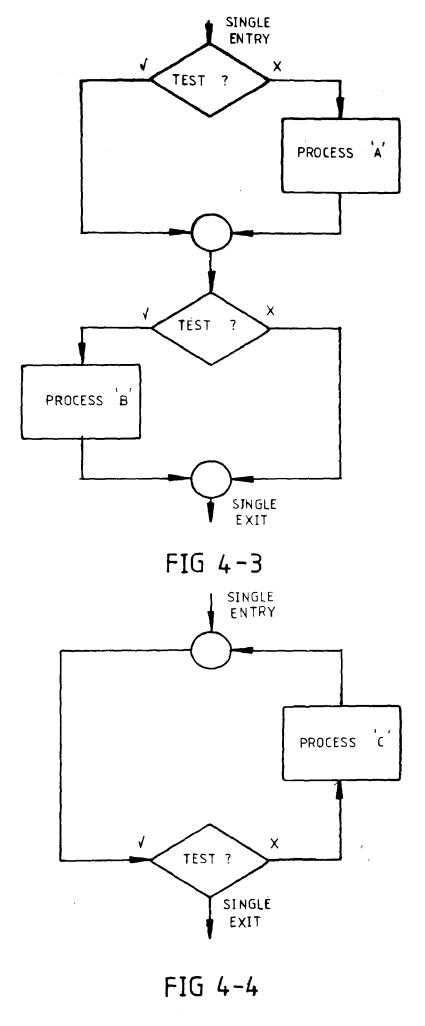

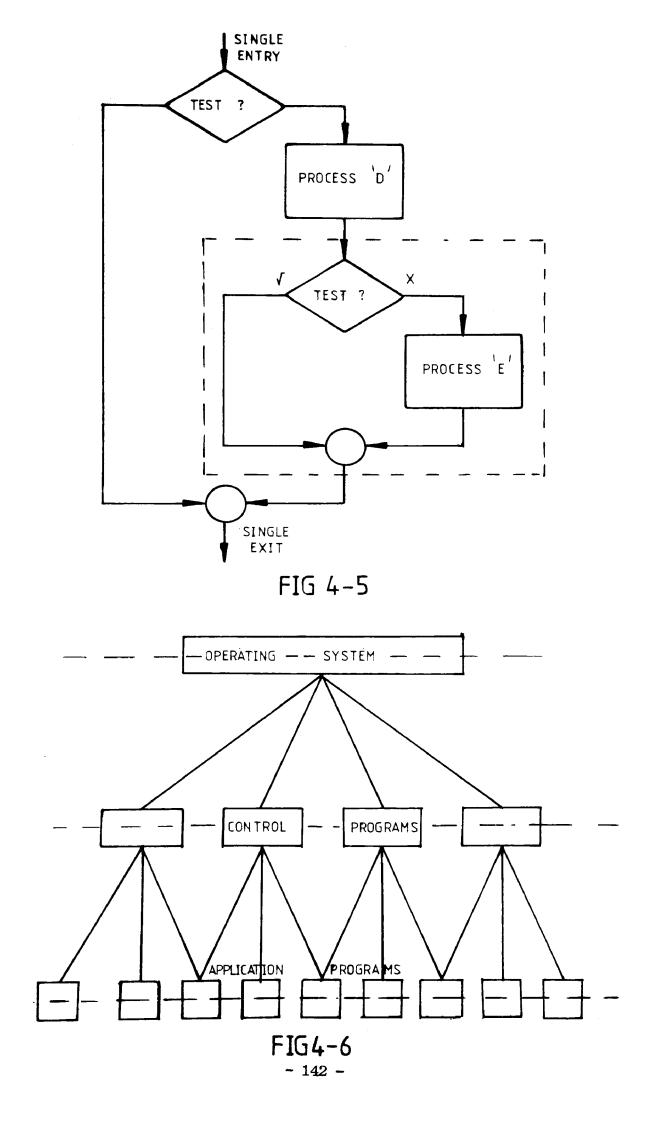

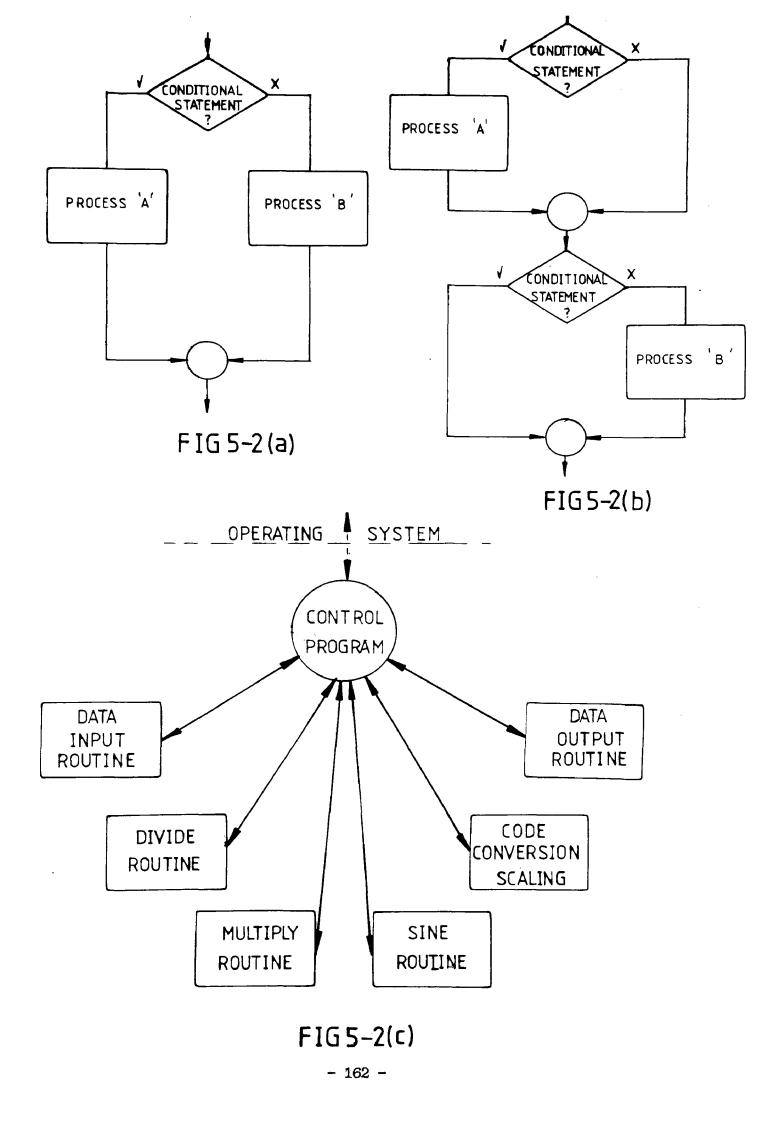

| ·  |       | 4.3.1 A Module                               | 137 |

|    |       | 4.3.2 The Sequence Statement                 | 138 |

|    |       | 4.3.3 The 'IF THEN ELSE' Statement           | 138 |

|    |       | 4.3.4 The 'DO-WHILE' Statement               | 138 |

|    | 4.4   | Writing Programs                             | 141 |

|    |       | 4.4.1 Register Transfer Instructions         | 143 |

|    |       | 4.4.2 Arithmetic And Logic Instructions      | 143 |

|    |       | 4.4.3 Skip, Jump Or Branch Instructions      | 143 |

|    |       | 4.4.4 Machine Operational Instructions       | 144 |

|    |       | 4.4.5 Machine Status Instructions            | 144 |

|    | 4.5   | The Choice Of Microprocessor                 | 145 |

|    |       | 4.5.1 Architecture                           | 146 |

|    |       | 4.5.2 Speed Of Operation                     | 146 |

|    |       | 4.5.3 The Instruction Set                    | 146 |

|    |       | 4.5.4 Total Cost                             | 147 |

|    |       | 4.5.5 Software Support And Second Source     | 147 |

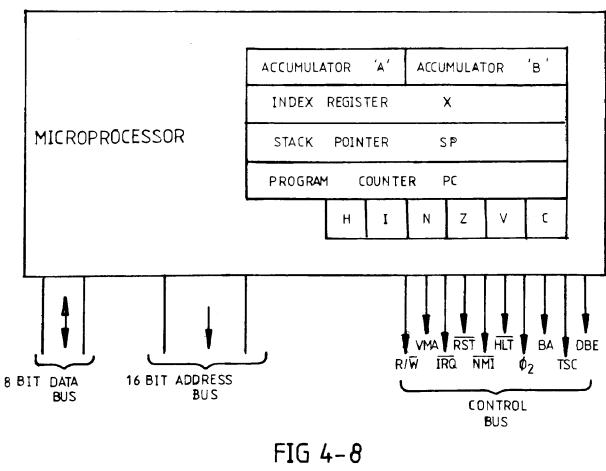

|    | 16    | The 6800 System                              | 150 |

|    |       | The Bus System                               | 152 |

|    | 4.1   | 4.7.1 The Data Bus                           | 153 |

|    |       | 4.7.1 The Data bus<br>4.7.2 The Control Bus  | 153 |

|    |       |                                              | 153 |

|    | 4 0   | 4.7.3 The Address Bus                        | 100 |

|    | 4.8   |                                              | 154 |

|    |       | Hardware Choice                              | 154 |

|    | 4.9   | System Design - Hardware/Software Trade Offs | 100 |

| ь. | THE MICROPROCESSOR CIRCUIT/SYSTEM DESIGN            | 158         |

|----|-----------------------------------------------------|-------------|

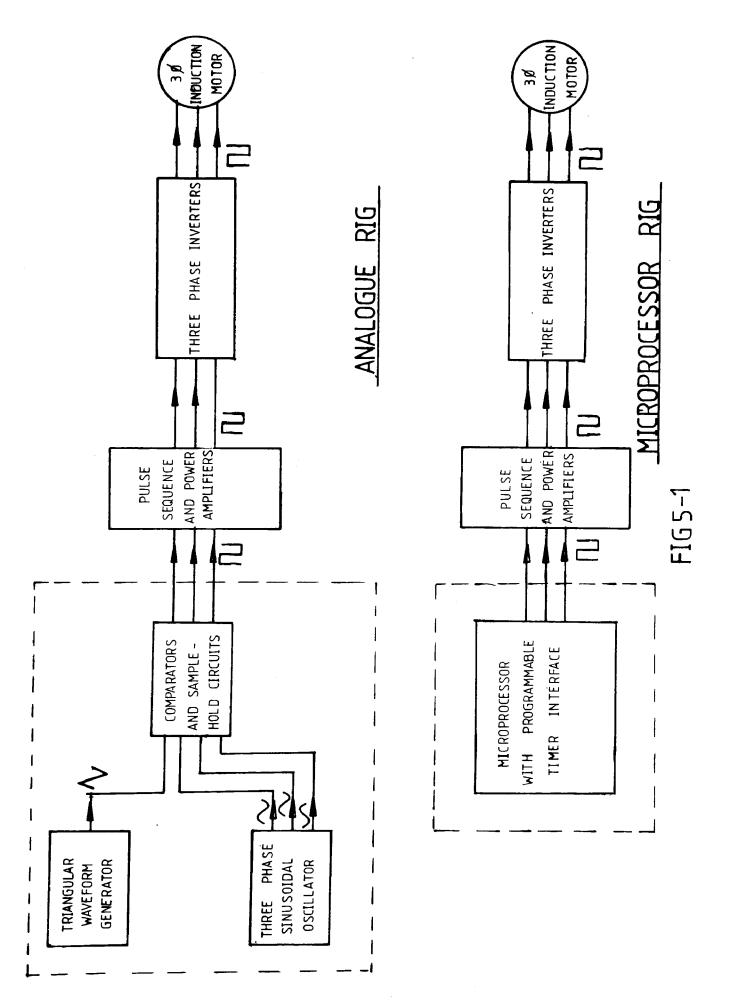

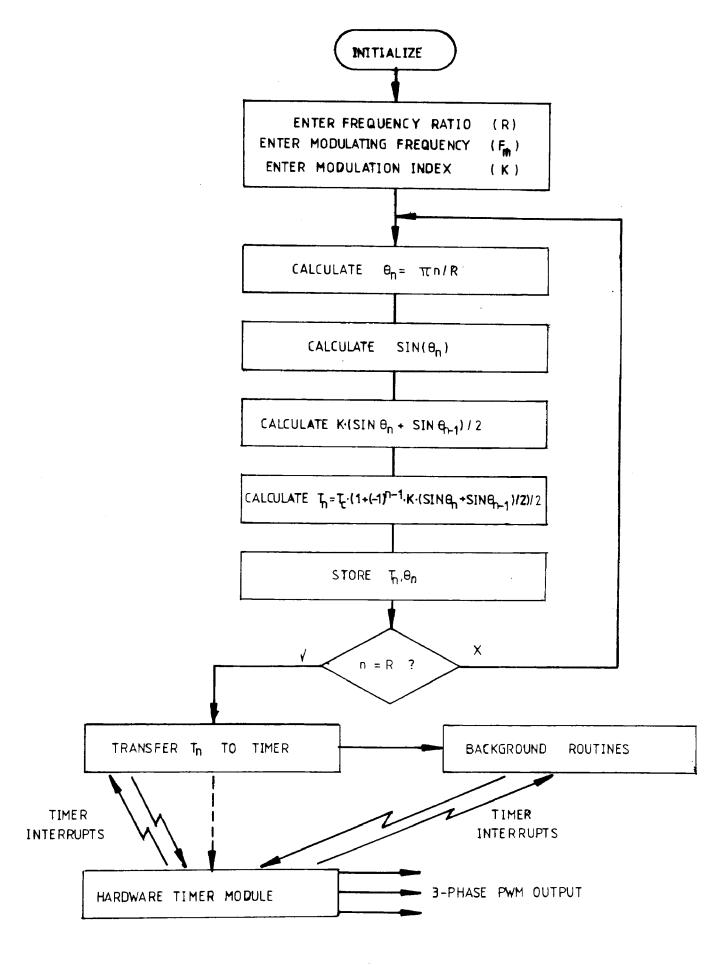

|    | 5.1 Digital Implementation Of P.W.M.                | 158         |

|    | 5.2 Microprocessor Control                          | 158         |

|    | 5.3 A Microprocessor Solution                       | 160         |

|    | 5.4 The Hardware/Software System Interface          | 161         |

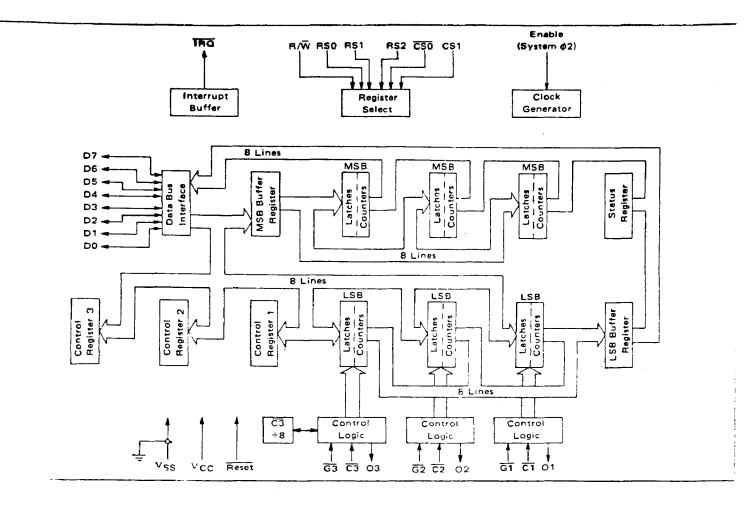

|    | 5.4.1 Operation Of Timer                            | 164         |

|    | 5.4.2 Timer Mode Selection                          | 167         |

|    | 5.4.3 The Continuous Operating Mode                 | 167         |

|    | 5.4.4 Operation Of Counters                         | 168         |

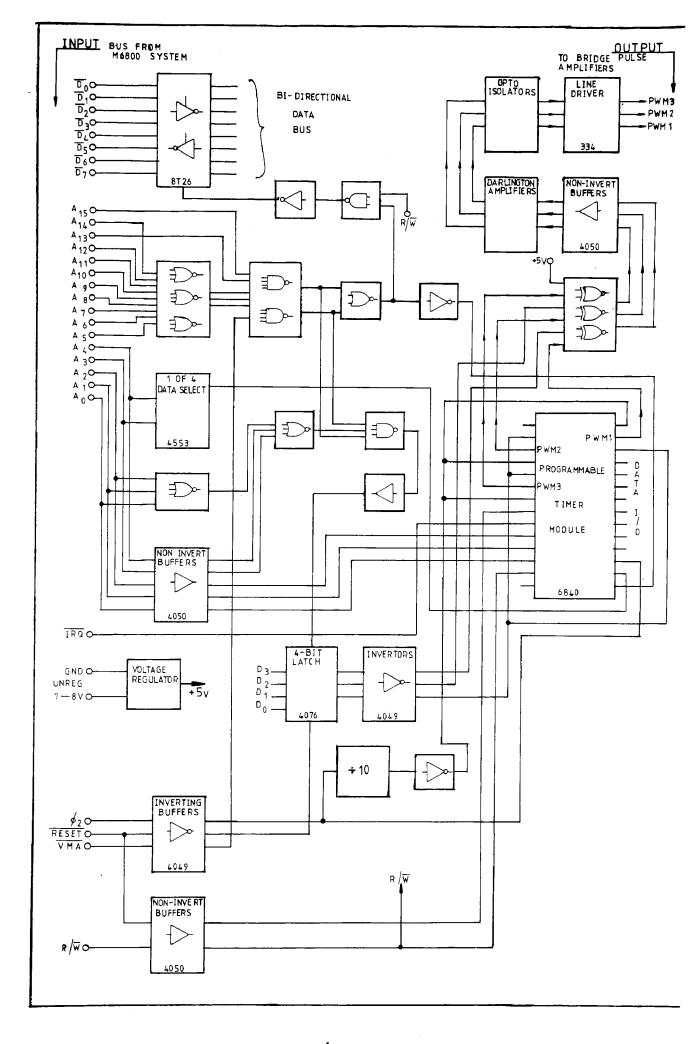

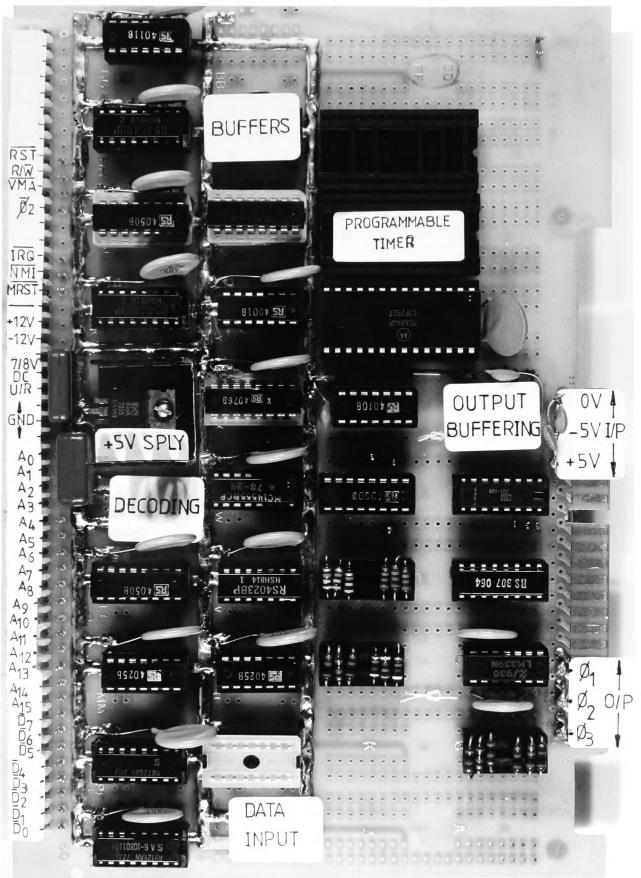

|    | 5.5 The PTM Interface Unit Hardware                 | 169         |

|    | 5.6 The Microprocessor Software                     | 172         |

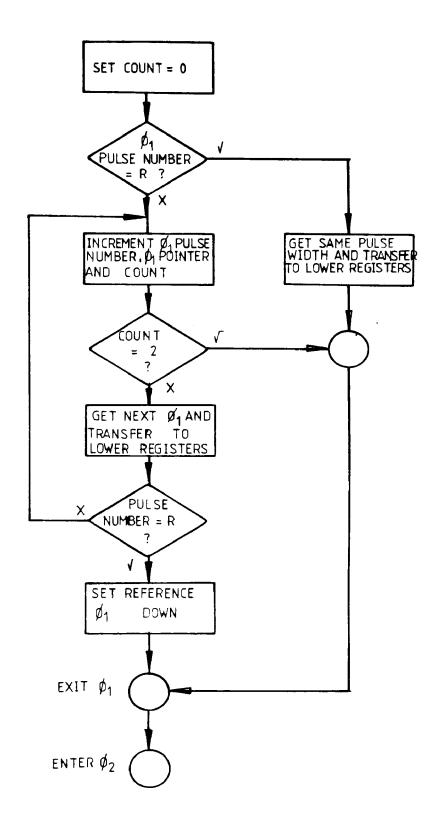

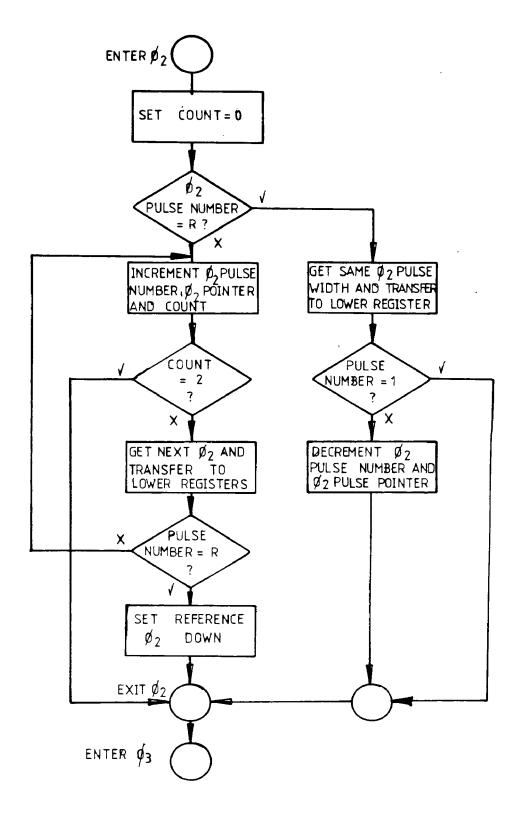

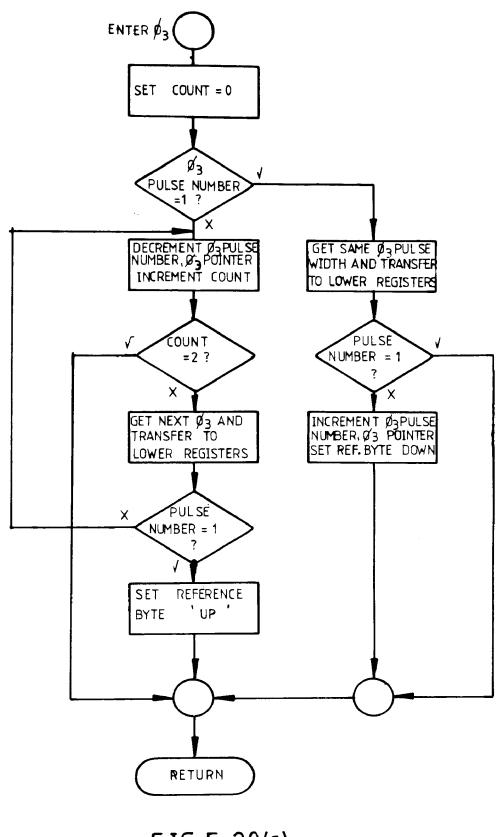

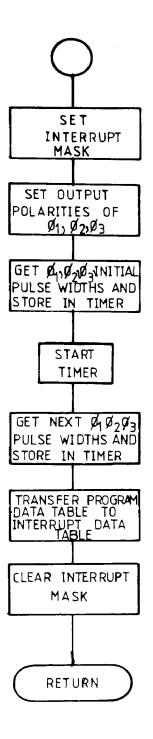

|    | 5.6. 1 The Timer Initialisation Routine             | 173         |

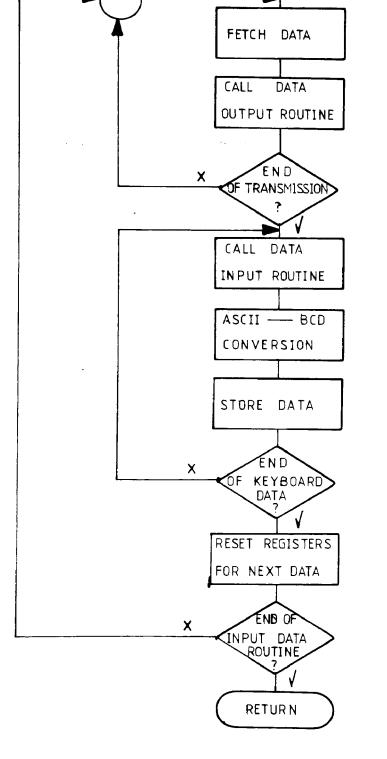

|    | 5.6. 2 Input Data For 'Input' Routine               | 174         |

|    | 5.6. 3 Input Routine                                | 174         |

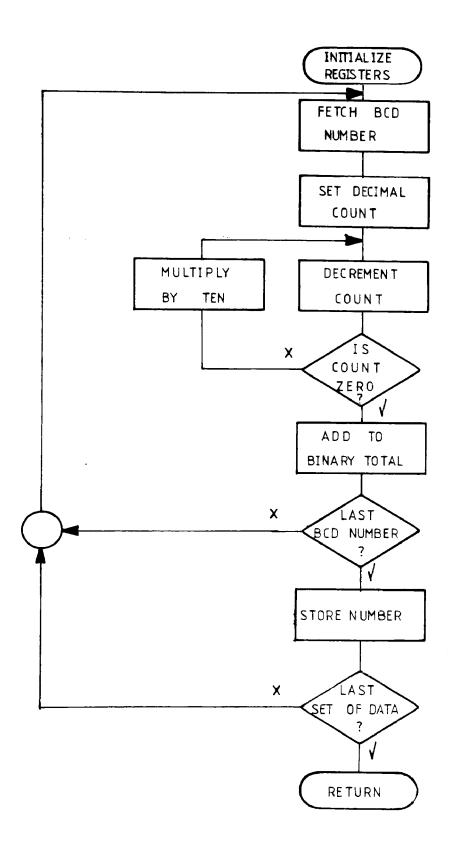

|    | 5.6. 4 BCD To Binary Conversion                     | 174         |

|    | 5.6. 5 The Multiply Routine                         | 178         |

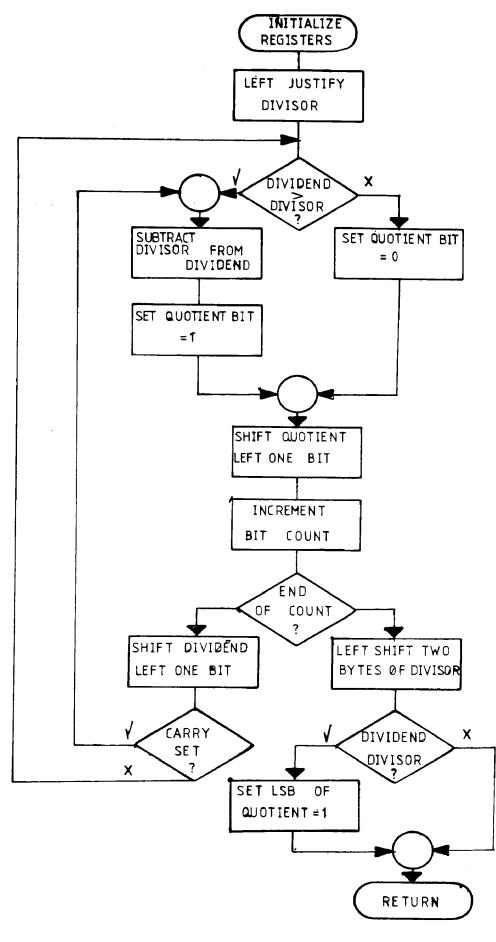

|    | 5.6. 6 The Divide Routine                           | 180         |

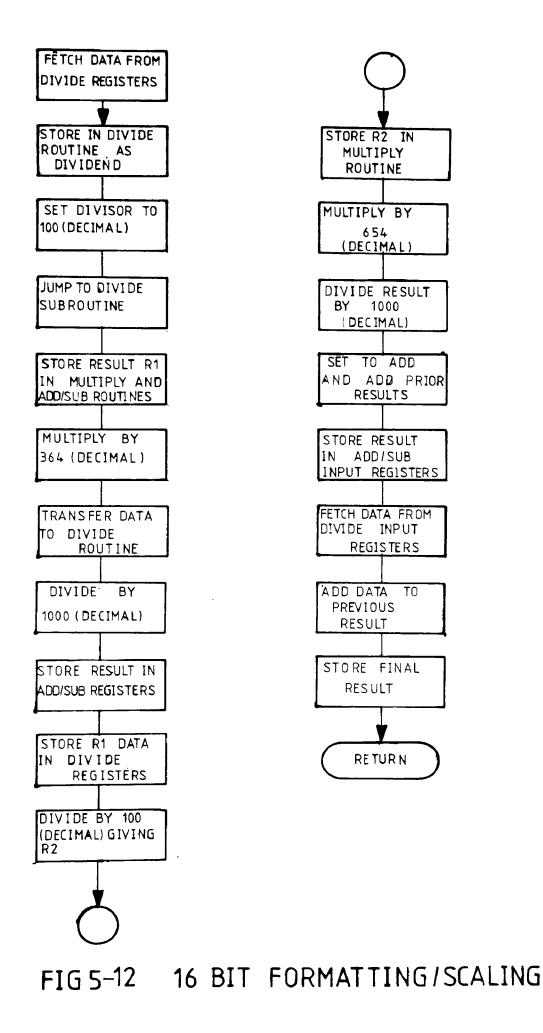

|    | 5.6. 7 16 Bit Formatting Routine                    | 182         |

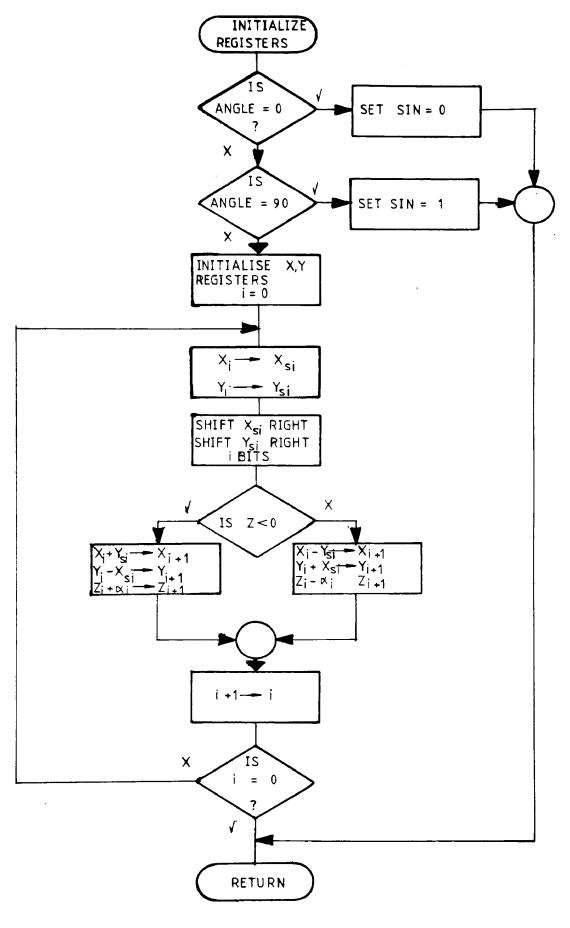

|    | 5.6. 8 The Co-ordic Algorithm                       | 182         |

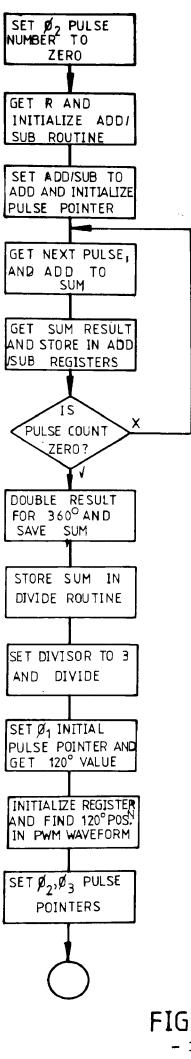

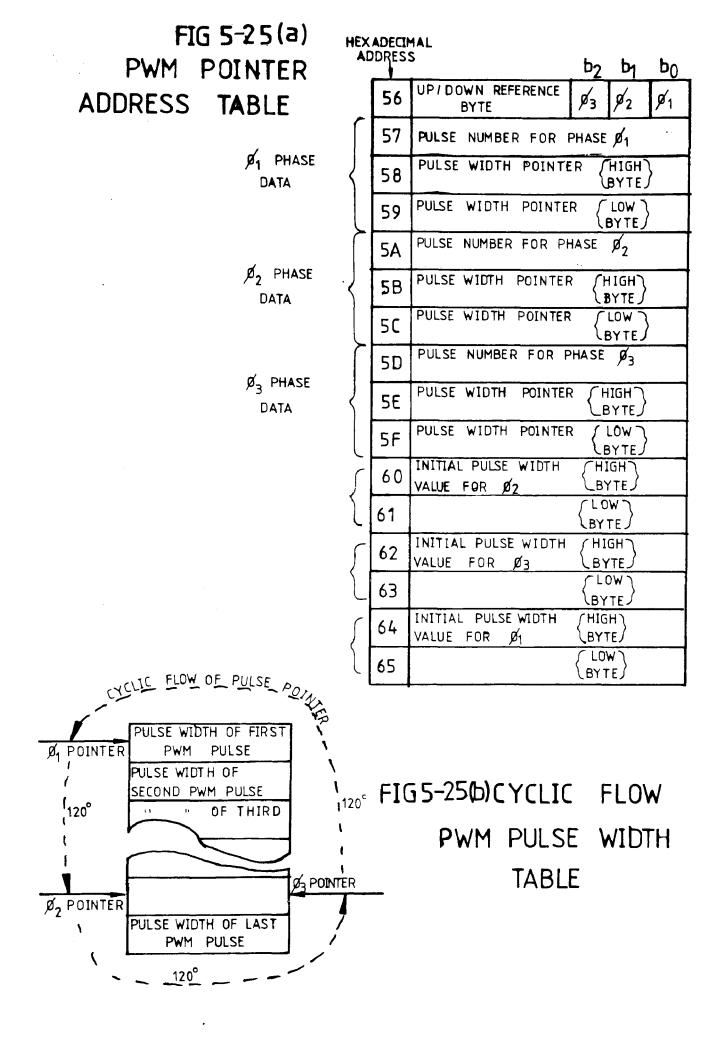

|    | 5.6. 9 Primary Three Phase Sort                     | 191         |

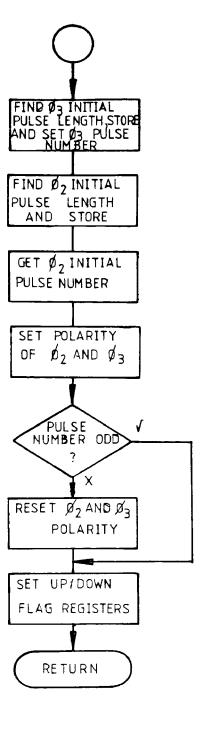

|    | 5.6.10 Secondary Three Phase Sort                   | 193         |

|    | 5.6.11 Data Output To Timer Routine                 | <b>19</b> 3 |

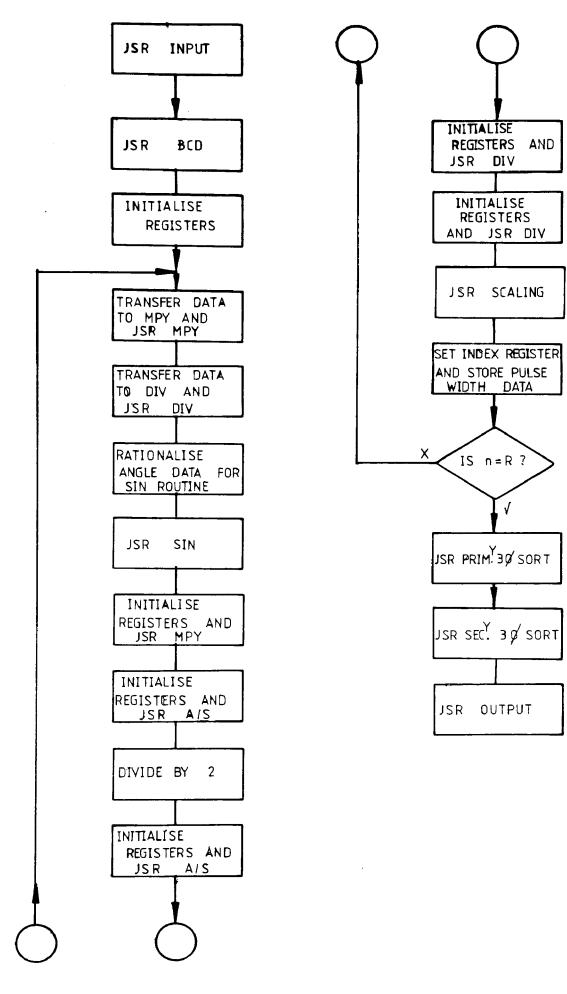

|    | 5.6.12 The Control Program                          | 198         |

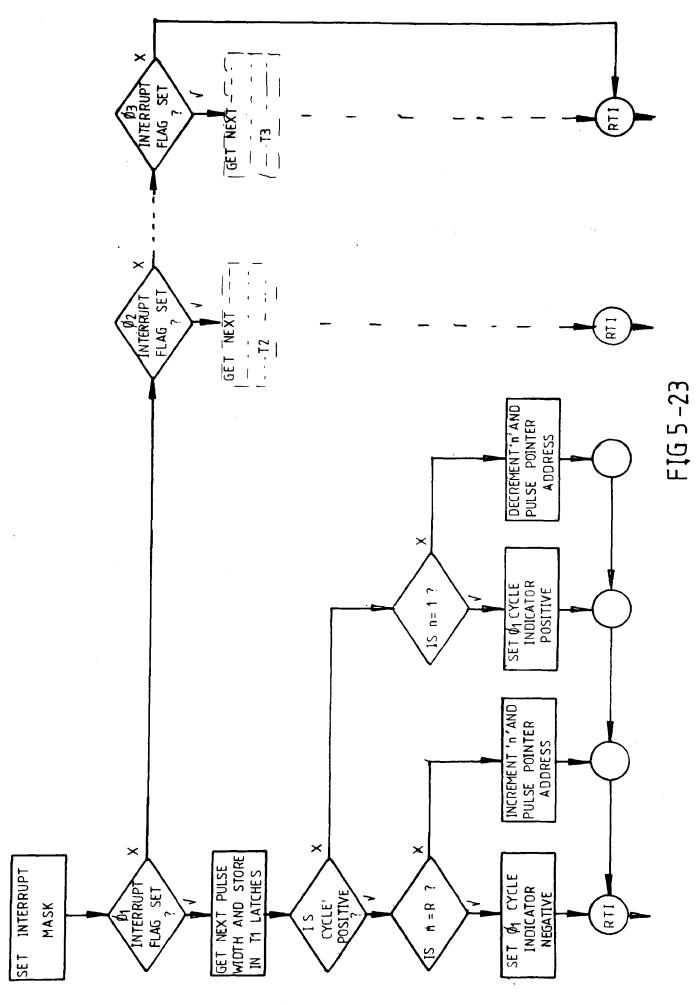

|    | 5.6.13 The Interrupt Routine                        | 198         |

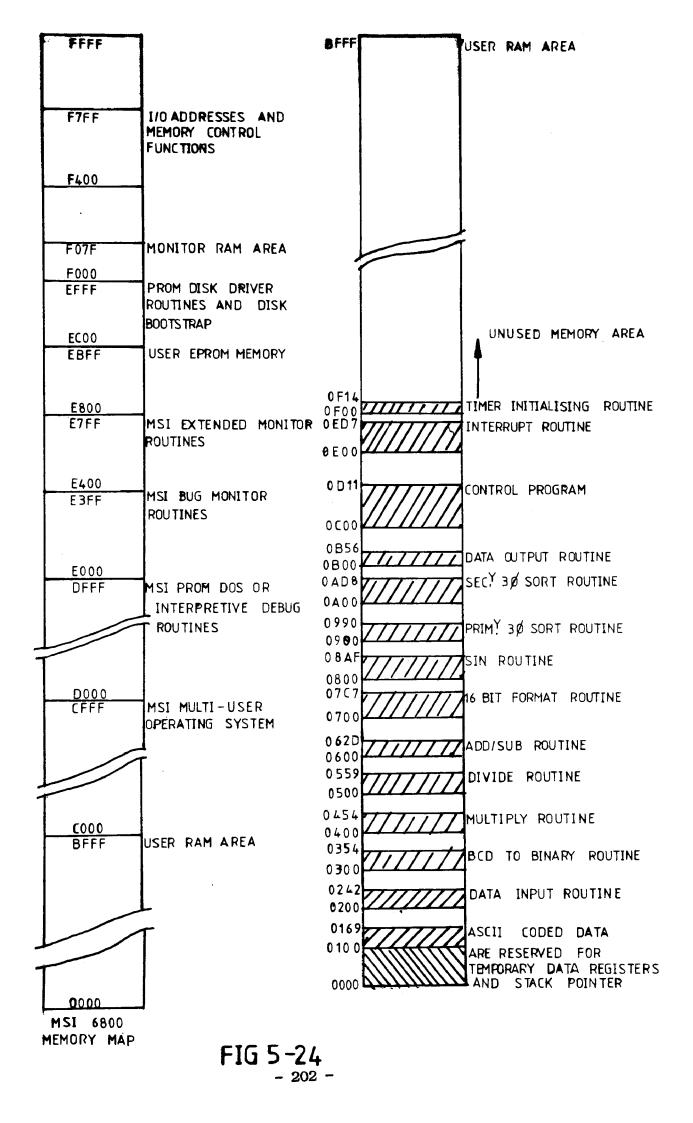

|    | 5.7 The Memory Map                                  | 201         |

|    | 5.8 Operating Method For Running The Microprocessor | 201         |

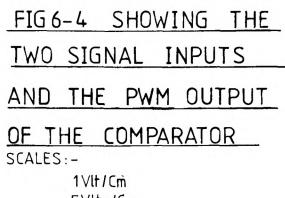

| 6. | ANALYSIS OF RESULTS                                 | 207         |

|    | 6.1 Introduction                                    | 207         |

|    | 6.2 Circuit Operation Of Carrier/Modulating Signal  |             |

|    | Generator                                           | 207         |

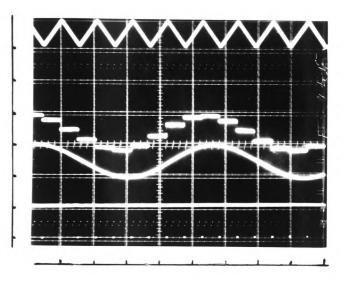

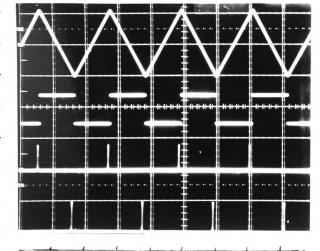

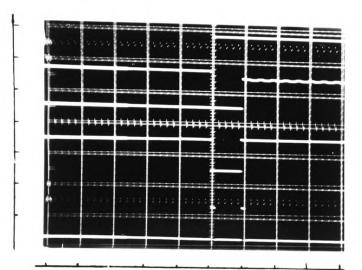

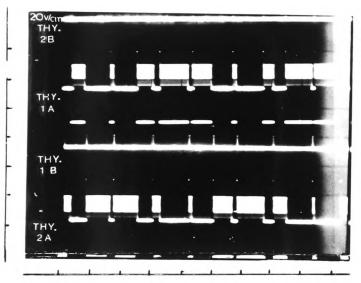

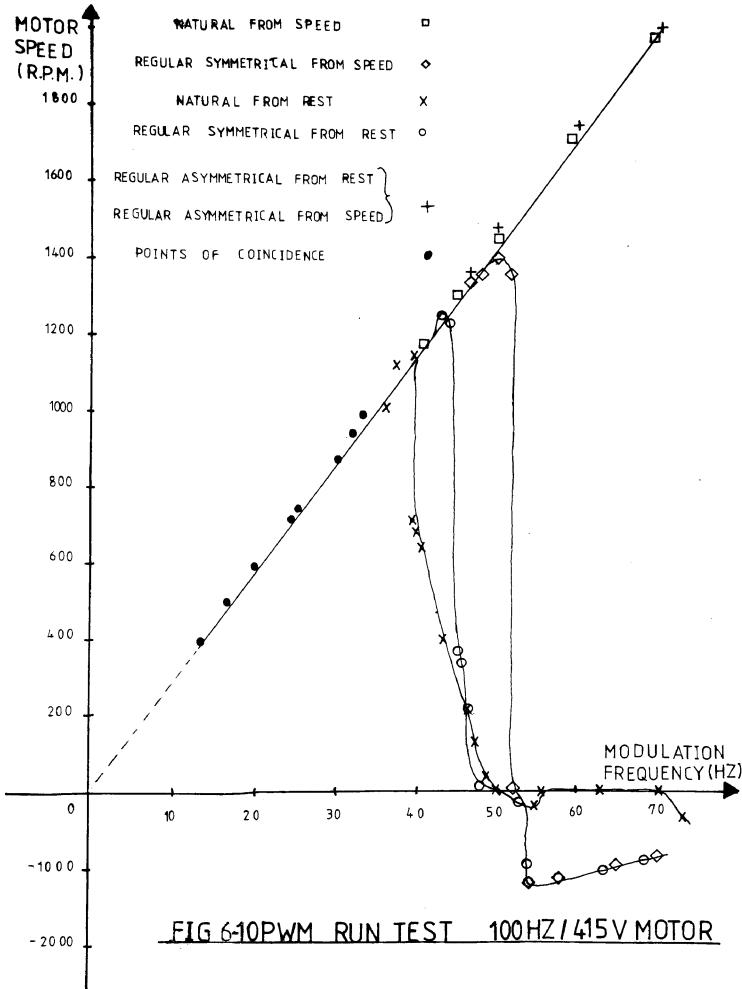

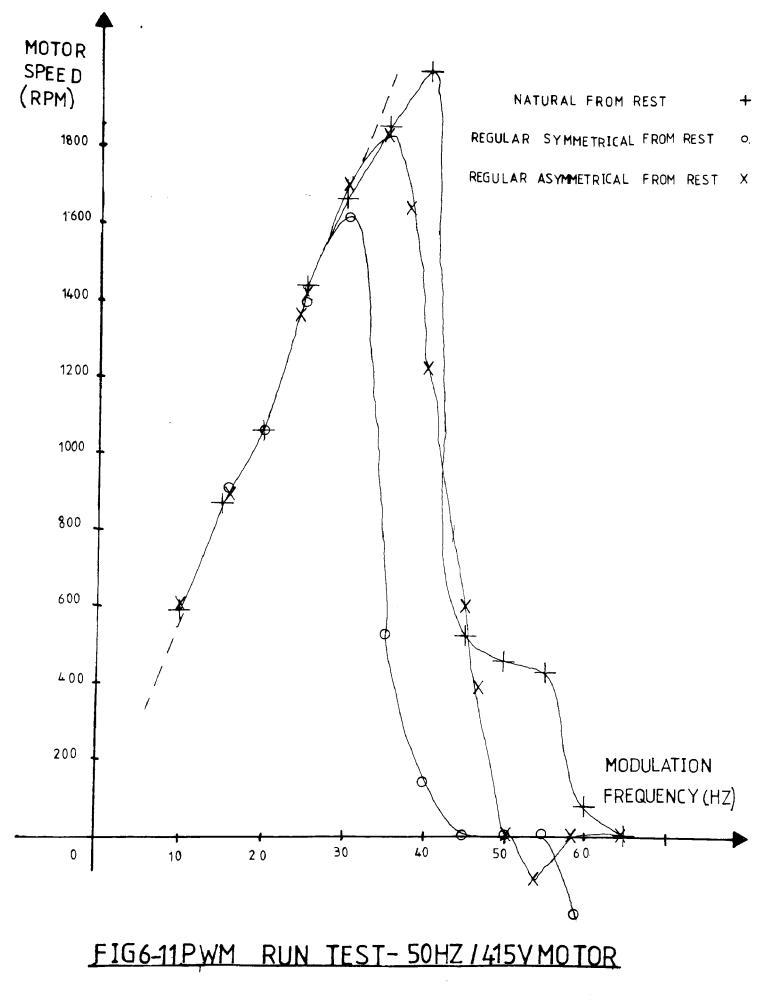

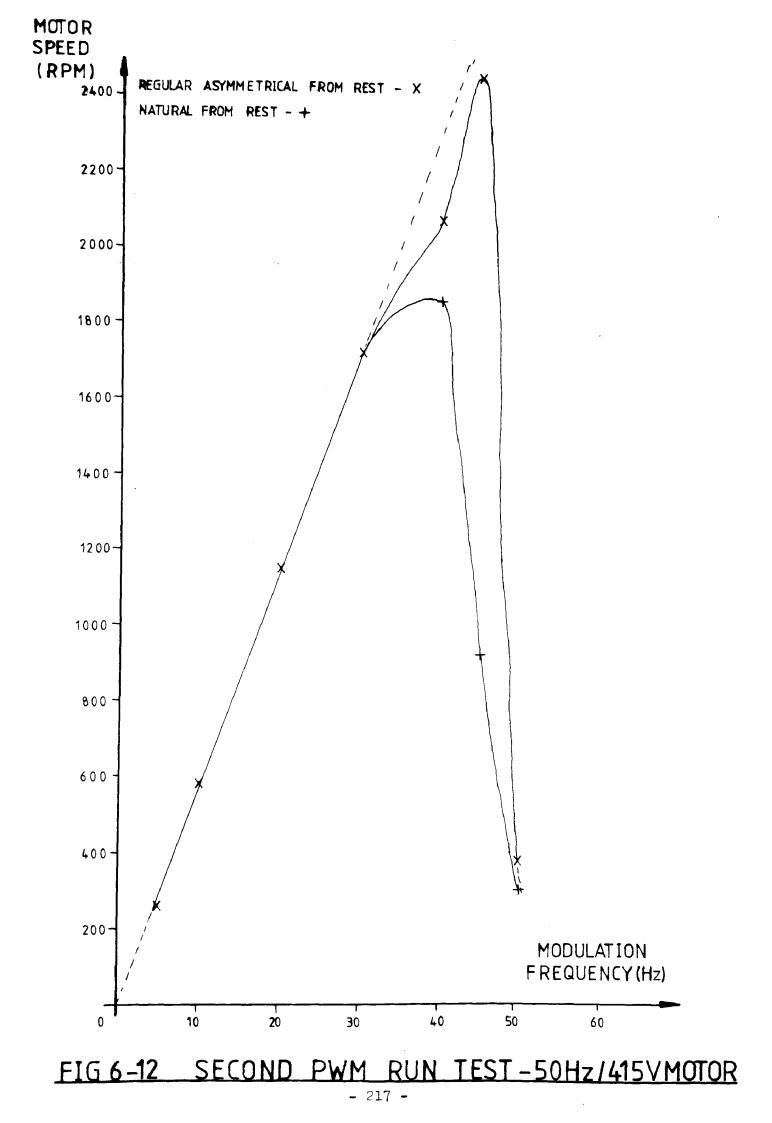

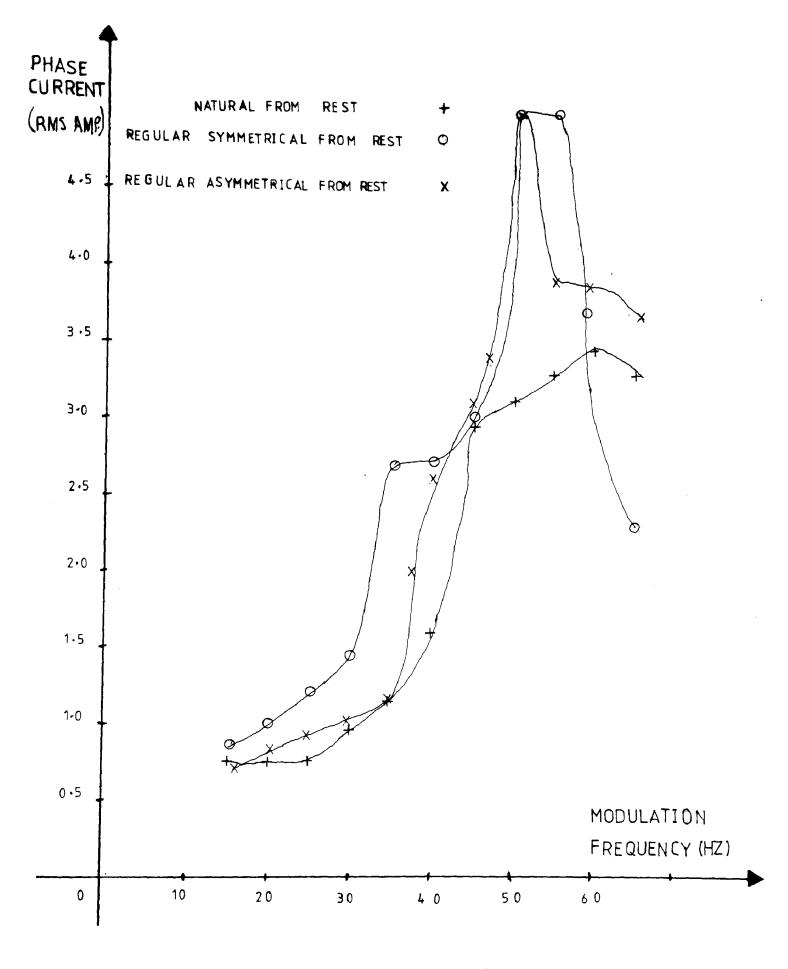

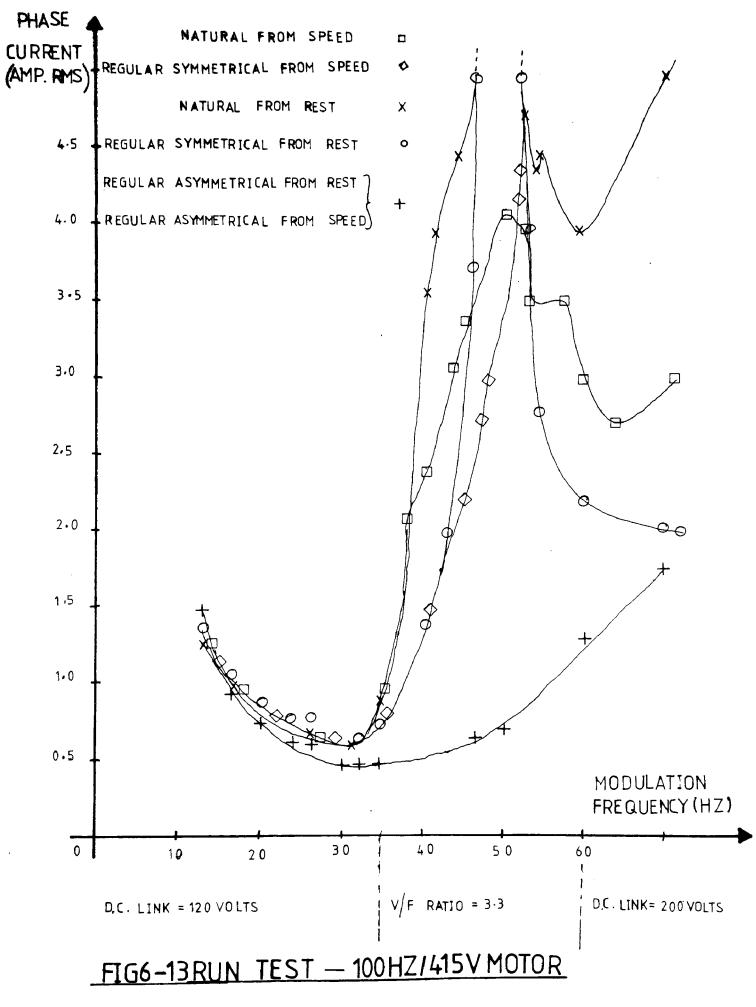

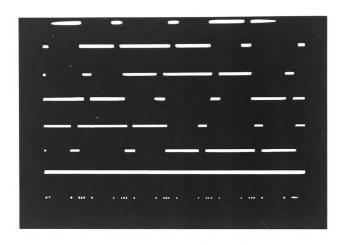

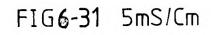

|    | 6.3 PWM Run Test - The Analogue System              | 213         |

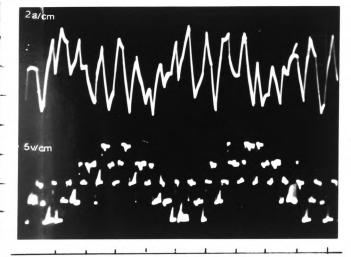

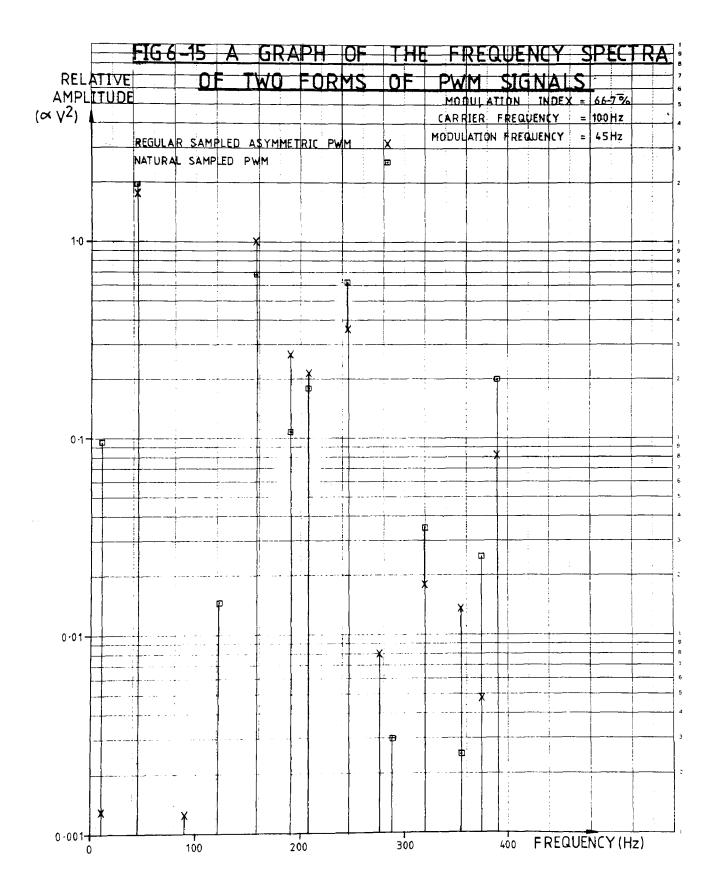

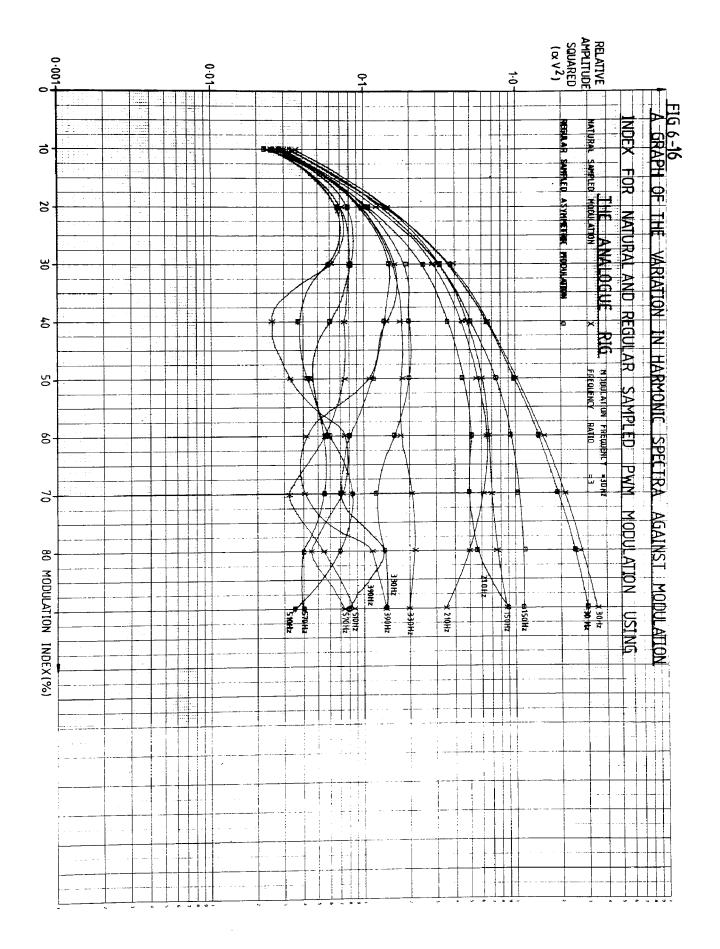

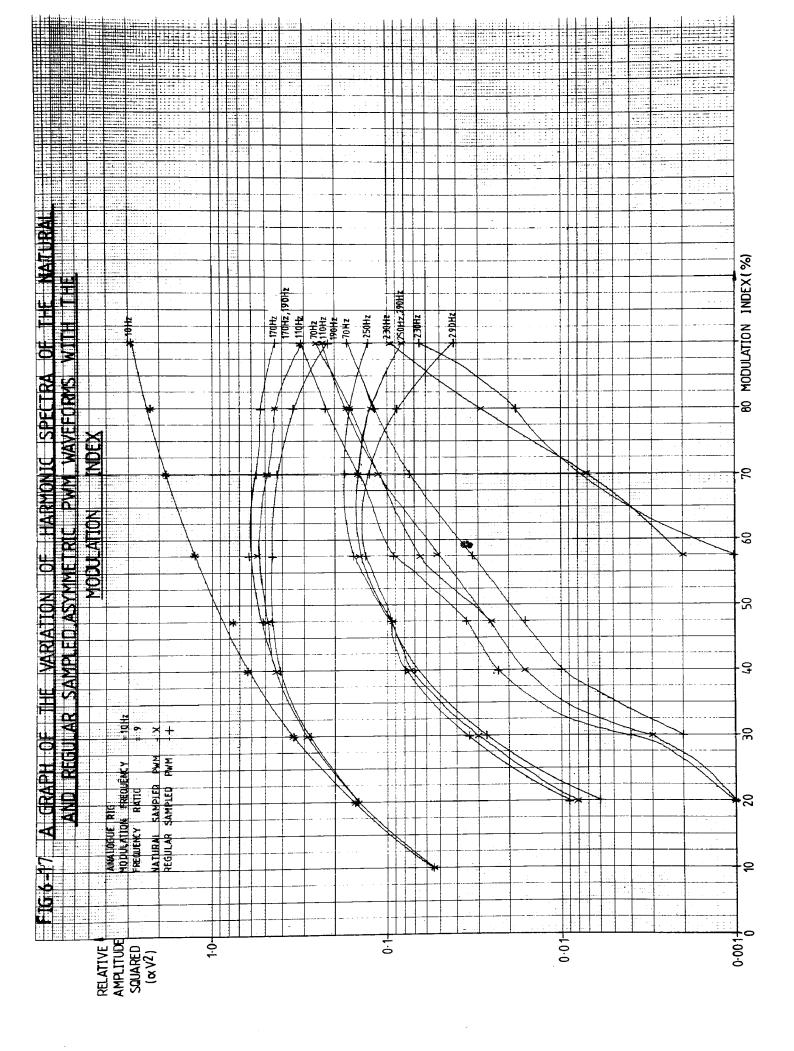

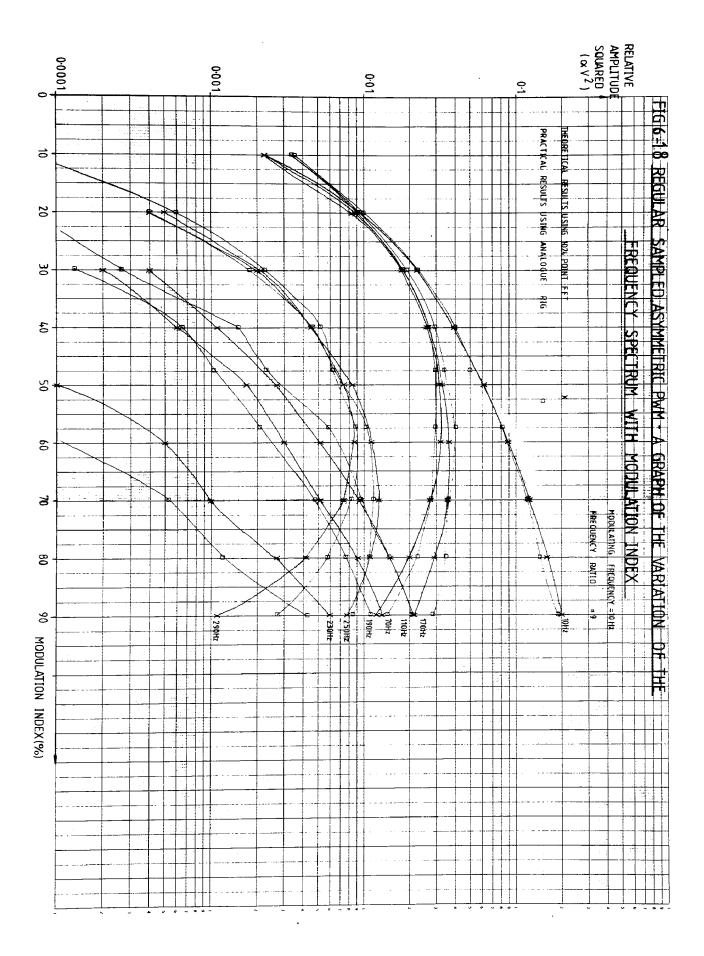

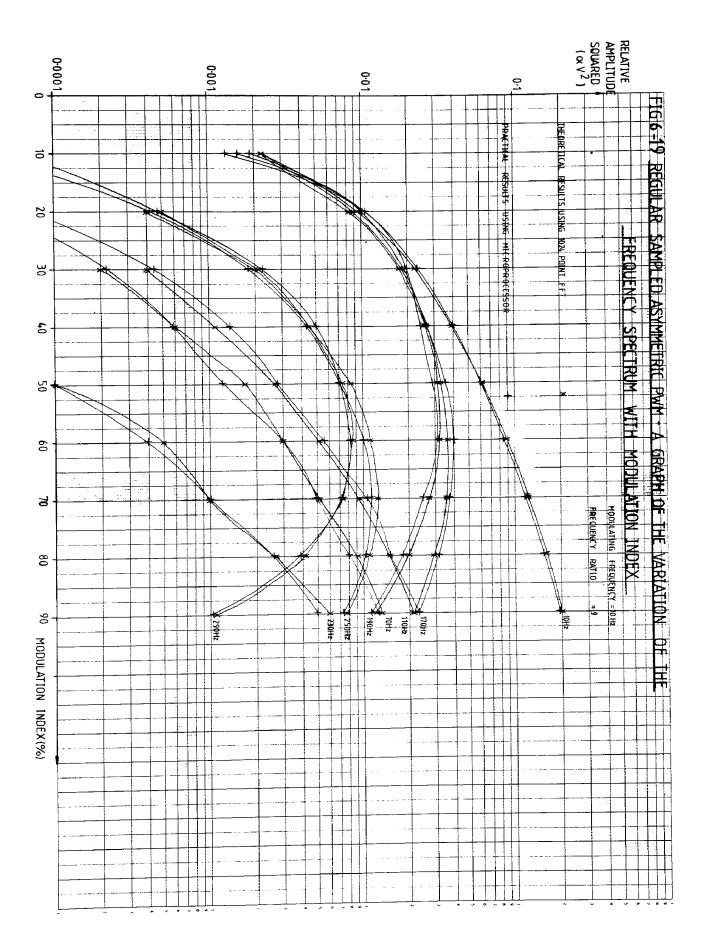

|    | 6.4 Spectral Comparison                             | 220         |

|    | 6.5 Microprocessor Regular Sampled, Asymmetric PWM  |             |

|    | Emulation                                           | 225         |

| 7. | CONCLUSIONS                                         | 241         |

| •• | 7.1 The Analogue Equipment                          | 241         |

|    | 7.2 The Bridge Inverter                             | 243         |

|    | 7.3 The Microprocessor Implementation               | 245         |

|    | 7.3.1 The Hardware                                  | 245         |

|    | 7.3.2 The Microprocessor                            | 246         |

|    | 7.3.3 The Programmable Timer                        | 238         |

|    | 7.3.4 Hardware Software Tradeoffs                   | 248         |

|    | 7.4 System Performance                              | 250         |

|    | 7.5 Future Trends                                   | 253         |

|    |                                                     |             |

| 8. | ACKNOWLEDGEMENTS                                    | 255         |

| 9. | REFERENCES                                          | 256         |

#### MEMORANDUM

#### MICROPROCESSOR CONTROL OF POWER INVERTERS

This thesis incorporates the results of a three year investigation into variable speed drives for induction motors with particular reference to the use of a microprocessor. The work was carried out in the laboratories of the Polytechnic of Wales from April 1979 to April 1982, under the supervision of Dr. M.G.Jayne and with the industrial collaboration of Black Clawson International of Newport, Gwent.

All work and ideas are original unless otherwise acknowledged in the text or by reference. This work has not been submitted for another degree of the C.N.A.A., nor for the award of a degree or diploma at any other institution. The main contribution that the author claims to have made to the subject of variable speed AC drives include :

- 1. The application of communication principles as the background philosophy to the modulation strategy for the generation of pulse width modulation (PWM) waveforms utilized in the realisation of variable speed a.c. drives.

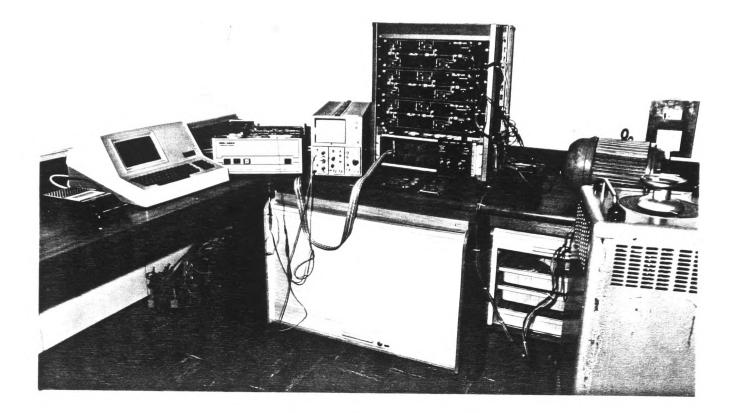

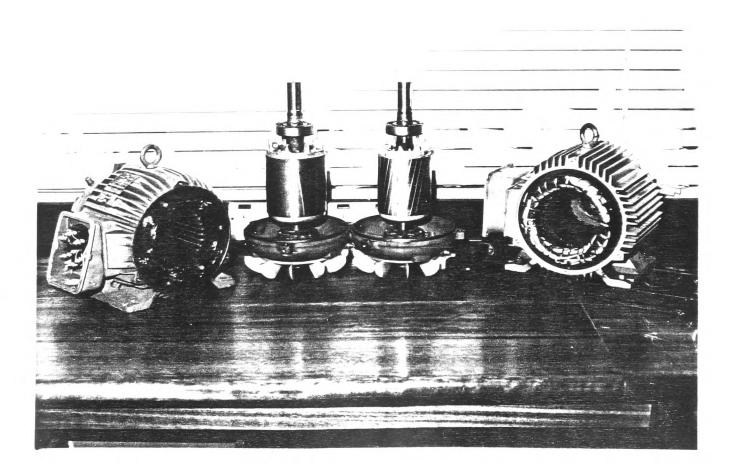

- 2. The design and development of a mark II analogue rig suitable for generating several types of PWM waveforms which were then evaluated in terms of their practical performance in the speed control of a three phase induction motor.

- 3. The development of computer programs, written in Basic on the PET microcomputer for the purpose of :

- (i) Analyzing the frequency spectrum of the natural Sampled form of PWM generation using Bessel Functions;

- (ii) Analysing the frequency spectrum of the Regular Sampled Asymmetric form of PWM generation using a Fast Fourier Transform technique.

- 4. The design and development of a novel microprocessor system for the variable speed control of AC drives. Prior art techniques had not investigated this approach which offers several advantages :

- (i) A reduction in the amount of hardware required over other techniques;

- (ii) the use of an interrupt system and a specialised programmable peripheral chip so that :

- (a) Only a single microprocessor is required;

- (b) A control program routine can be added to the system without the need for a second processor;

- (c) No external computation of pulse widths, on a mainframe

computer, is required;

- (d) Only 2 kilobytes of memory are required for the software;

- (e) A far greater degree of flexibility is achieved in the control of the pulse number of the PWM waveform whereby its value can be freely selected and is not fixed by the setting of carrier and modulation frequencies as in the prior art analogue rig;

- (f) New data, for controlling pulse number, speed and torque, can be entered into the system whilst the motor is being run, at speed, by the microprocessor so that smooth, incremental changes in motor speed can be achieved.

- 5. As a consequence of (4) a novel programmable interface unit has been designed which incorporates a software control technique for the starting and stopping of the programmable timer whilst the hardware configuration allows the reversal of motor rotation to be simply achieved.

- 6. Also, as a consequence of (4) a novel technique the implementation of the formula describing the Regular Sampled Asymmetric form of PWM using numerical software was utilised for generating three phase PWM waveforms. This necessitated the design of several software programs to provide 16 bit by 16 bit multiplication, 24 bit by 8 bit division, code conversion, scaling, a 16 bit sine routine using the co-ordic algorithm was particularly useful in that a complete range of sine values could be obtained allowing enough accuracy to distinguish 1° differences in the input data. This approach allowed a significant saving in memory size-180 bytes of data, with the added memory requirement of a program to access the table of data would have been necessary in a table look-up approach.

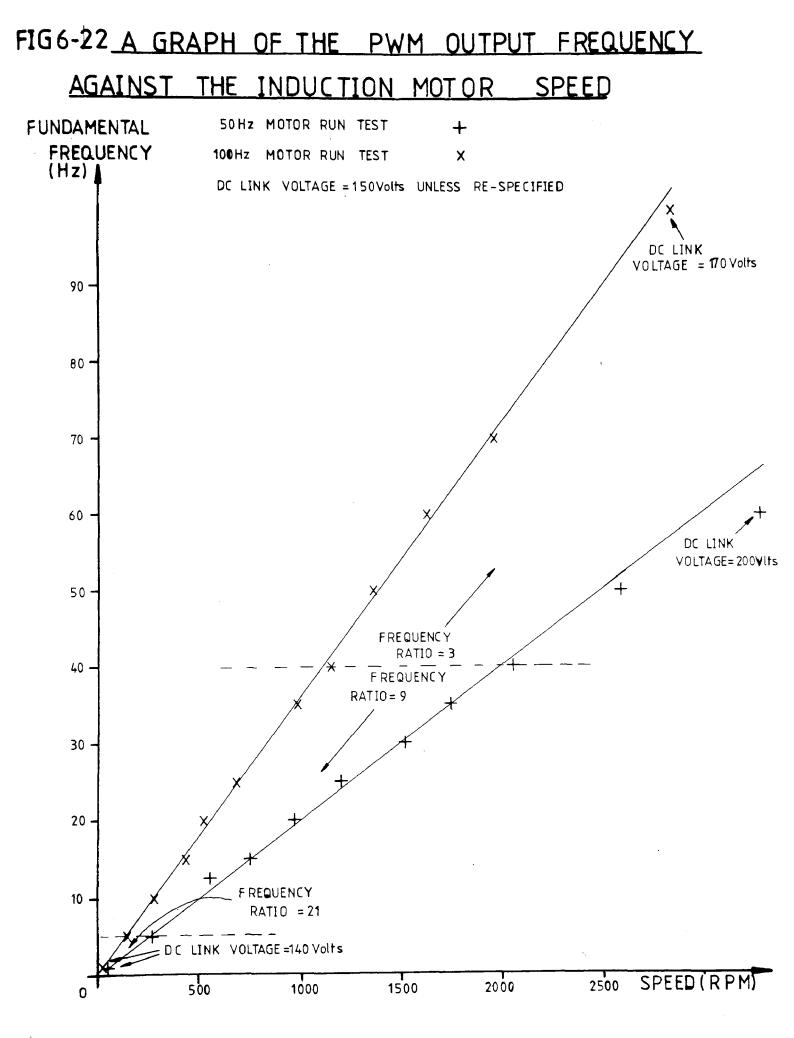

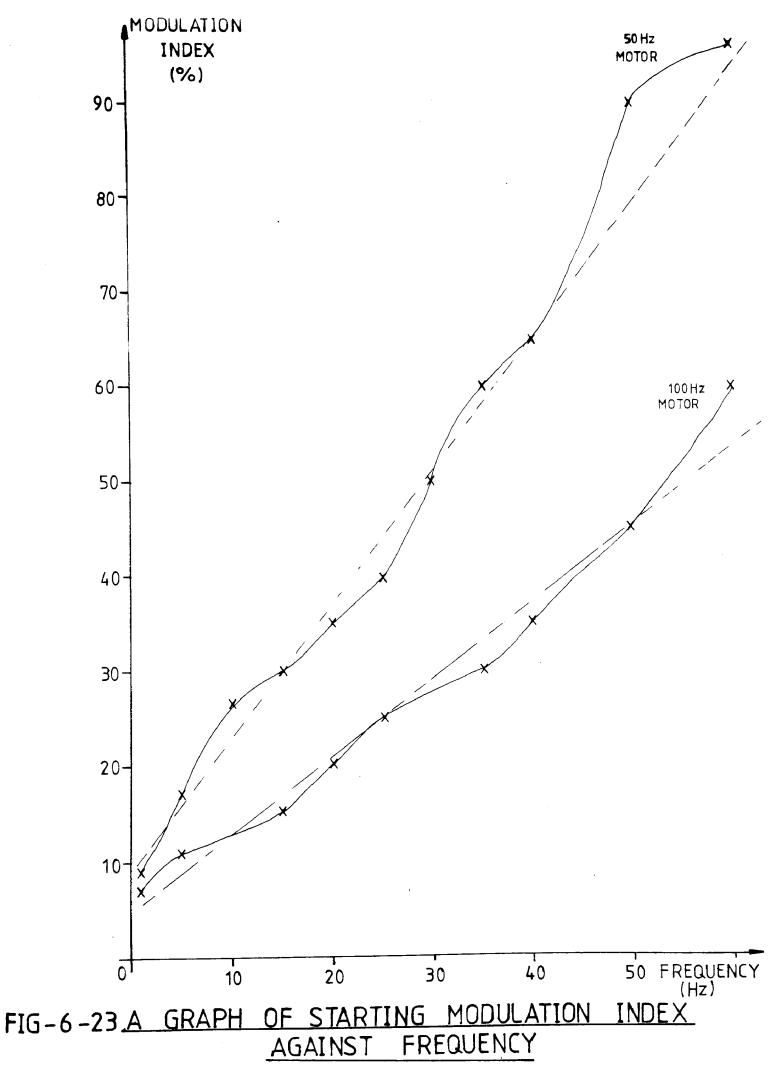

- 7. The graphs comparing the measured frequency spectra of the analogue and digital techniques of PWM generation with the theoretical spectra as predicted by the FFT analysis show conclusively that :

- (i) The microprocessor is, in fact, emulating the regular sampled asymmetric form of PWM modulation;

- (ii) the microprocessor implementation is far more accurate than the analogue rig and was able to control a 5h.p. induction motor over a 100:1 speed range, the frequency varying from 1Hz to 100Hz whilst the frequency ratio varied from 21 to 3. The modulation index was selected to maintain a constant V/F ratio, although, at its extremities, a change in D.C. link voltage was necessary in order to generate the appropriate torque so that the proper operating speed could be achieved.

The investigation has supported the publication of several articles :

Jayne, M.G.; Williams, A.B.; 'An Investigation Into the Operation of a Thyristor with Law Harmonic Control' pp464-467 Int.Conf. on Electronics and Microelectronics (EUROCON 80) Stuttgart, Germany, march 1980.

Jayne, M.G.; Williams, A.B.; "An Investigation Into the Application of Microprocessors: to Pulse-Width-Modulated Inverters" pp.11-51 to 11-63 Int.Conf. on Numerical Control of Electrical machines (CONUMEL 80) Ecole Control de Lyon, Lyon, France, April 1980.

Williams, A.B.; Jayne, M.G.; "A Software Approach to the generation of P.W.M. Waveforms for Variable Speed Induction Motor Drives" 17th Universities Power Engineering Conference U.M.I.S.T., April 1982.

| v         | = amplitude of pulse                             |

|-----------|--------------------------------------------------|

| Т         | = (1) periodic time                              |

|           | (2) pulse width value                            |

| N,K,n,m,r | = integers                                       |

| Α         | = (1) amplitude of wave                          |

|           | (2) variable                                     |

| В         | = (1) variable                                   |

|           | (2) arbitrary constant                           |

| С         | = (1) capacitance                                |

|           | (2) variable                                     |

| Е         | = (1) direct supply voltage                      |

|           | (2) variable                                     |

| F         | = (1) frequency                                  |

|           | (2) variable                                     |

| G,G       | = variables                                      |

| K         | = modulation index                               |

| L         | = inductance                                     |

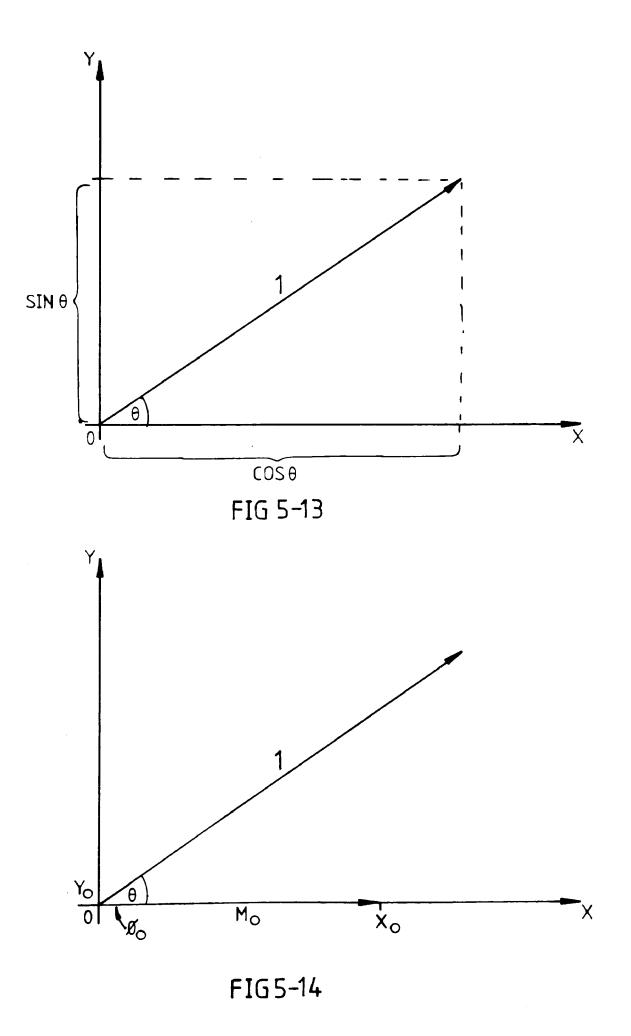

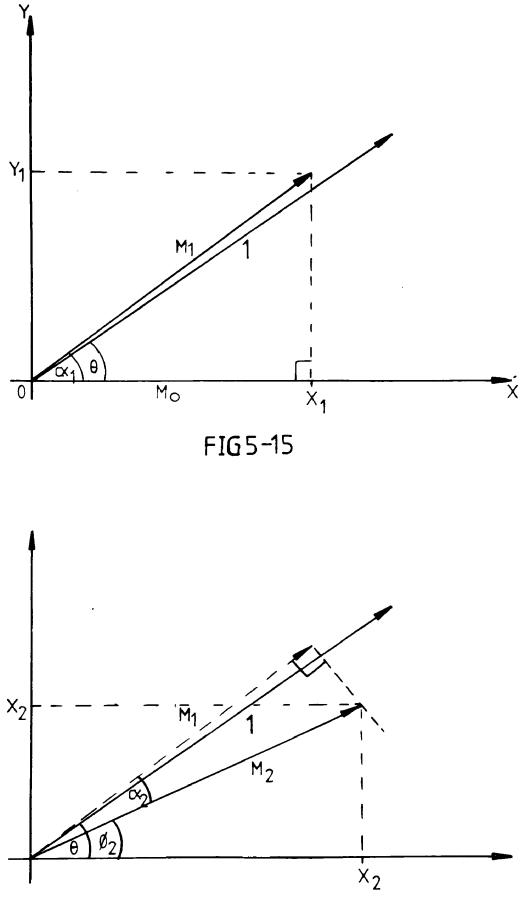

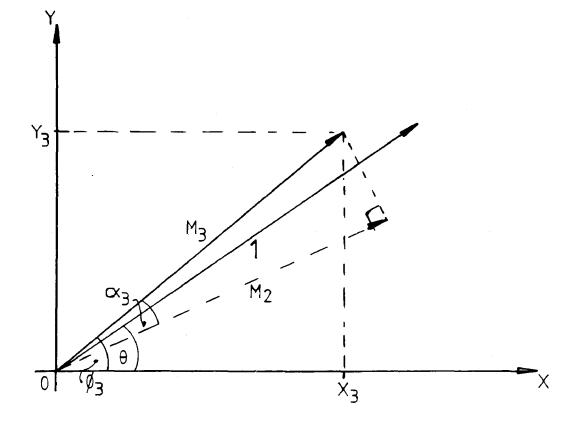

| Μ         | = magnitude of vector                            |

| Mi        | = modulation index                               |

| R         | = (1) frequency ratio                            |

|           | (2) resistance                                   |

| W         | = exponential constant ( $W = \exp(-2\pi j/n)$ ) |

| I         | = current                                        |

| X         | = (1) X co-ordinate                              |

|           | (2) variable                                     |

| Y         | = Y co-ordinate                                  |

| $\mathbf{J}_{\mathbf{n}}$ | = Bessel function of order n                          |

|---------------------------|-------------------------------------------------------|

| е                         | = (1) exponential                                     |

|                           | (2) instantaneous values of time function             |

| f                         | = frequency                                           |

| t                         | = time                                                |

| k                         | = integer ratio                                       |

| h                         | = height                                              |

| b                         | = bit                                                 |

| v                         | = instantaneous voltage                               |

| to                        | = pulse width                                         |

| w                         | = angular frequency                                   |

| φ                         | = (1) phase designation                               |

|                           | (2) phase angle                                       |

|                           | (3) vector angle                                      |

| θ                         | = phase angle                                         |

| α                         | = (1) gradient                                        |

|                           | (2) vector angles                                     |

| $\Delta_{o}(t$            | ) = function of time incorporating an infinite series |

|                           | of unity amplitude impulses, period T                 |

| $\Delta_{i}(t)$           | ) = function of time incorporating infinite series    |

|                           | of unity amplitude impulses, period To                |

| V(t)                      | U(t), f(t), x(t), h(t) = functions of time            |

| • •                       | = sampled function of continuous function h(t)        |

| $\hat{\hat{h}}(t)$        | = time domain product of two sampled data functions   |

| 8(t)                      | = impulse function                                    |

| X(n)                      | ,A(n),Xk,Yk,Zk,h(k) = sampled data time series        |

| Ĥ (n                      | ) = fourier transform                                 |

| f(x)                      | = arbitary function of x                              |

|                           |                                                       |

(v)

| *          | = convolution                                       |

|------------|-----------------------------------------------------|

| $\bigcirc$ | = transformation between time and frequency domain, |

|            | or vice versa                                       |

| DFT        | = discrete fourier transform                        |

| FFT        | = fast fourier transform                            |

| PWM        | = pulse width modulation                            |

| NS PWM     | = natural sampled pulse width modulation            |

| RSA PWM    | = regular sampled asymmetric pulse width modulation |

| ROM        | = read only memory                                  |

| RAM        | = random access memory                              |

| EPROM      | = electrically programmable read only memory        |

| TTL        | = transistor transistor logic                       |

| CMOS       | = complementary metal oxide silicon semiconductor   |

| PTM        | = programmable timer module                         |

| IRQ        | = interrupt request control line of microprocessor  |

| R/W        | = read/write control line of microprocessor         |

| DMA        | = direct memory access line of microprocessor       |

$\bigcirc$

Decision

Process

$\bigcirc$

#### Connector

$\bigcirc$

Terminal

# Suffices

- c pertaining to carrier wave

- m pertaining to modulating wave

- s pertaining to sampling

- r pertaining to repetition wave

- a pertaining to phase of 3-phase system

- b pertaining to phase of 3-phase system

- c pertaining to phase of 3-phase system

#### SUMMARY

The introduction gives consideration to the aspects of communication principles, power converters, PWM modulation techniques and the application of LSI intergrated circuits as regards their effect on the design of variable speed AC drives.

Chapter 1 includes background material where several types of variable A.C. drives are compared. The theoretical speed possibilities of various PWM schemes show that certain techniques improved harmonic spectrum properties, more suited to the wide offer range speed control of induction motors. Chapter 2 introduces alternative approaches to the analysis of sinuisoidal or natural PWM The latter waveform is and the regular sampled PWM waveforms. analysed by expressing the function in terms of the time domain; conversion from the time to the frequency domain is then obtained using a Fast Fourier Transform (FFT) technique implemented on the 32K PET microcomputer. Chapter 3 describes a successful analogue rig designed to generate several, alternative PWM waveforms which were used to drive an induction motor via the McMurray bridge inverter. Practical performances of the differing PWM waveforms were evaluated, using this equipment and the regular sampled, asymmetric PWM waveform was shown to have some operational advantages - it was this technique which was then given further consideration for microprocessor implementation.

Chapter 4 outlines the top-down, structured design philosophy necessary for the efficient successful realisation of the hardware and software of a microprocessor system. The detail of the complete unit

(viii)

is given in Chapter 5 which describes the hardware and software of a microprocessor design used to provide the switching drive to the induction motor via the inverter. Several sotware algorithms are described which, when run by the control program in the appropriate sequence, produce the three phase PWM output waveform. An analysis of results is provided in Chapter 6 which shows that both the analogue and microprocessor rigs can operate an induction motor over wide speed ranges. The micropocessor realisation was far more accurate in its emulation of the Regular Sampled Asymmetric PWM waveform and controlled the motor over a 100:1 speed range.

The concluding chapter summarises the problems, state-of-art and further applications of the microprocessor implementation whose unique properties are hardly obtainable with other, more conventional forms of practical realisation.

#### INTRODUCTION

# Communication Principles

One of the main requirements of a variable speed cage rotor induction motor drive system is that the magnitude and frequency of the voltage applied to the motor be independently variable over a wide range. However, such a requirement is not easily met in practice. Generally mains power supplies are constant frequency constant voltage sources so that power transmission can be cost effective. Therefore, some method of achieving an efficient variable frequency, variable voltage supply from the static mains supply is required.

There are many techniques of power conversion where the aim is to provide a three-phase variable frequency, variable voltage source [1],[2]. For high power converters, where efficiency is at a premium the use of pulse modulated systems has found favour because the system can operate with efficiencies in excess of 90%. Further the technology of thyristors has advanced such that fast turn-off, high power devices are available at a low enough cost to ensure the economic viability of power inverters.

The availability of high power thyristors has accentuated the development of pulse modulated power transfer, a technique which has been used extensively in the communications field for the transmission of information signals.

- 1 -

The process of static frequency change is known as modulation. For example, amplitude modulation is a process which changes both the amplitude and frequency of a fixed frequency source. Information transmission and coding techniques cover frequency modulation (FM), amplitude modulation (AM), phase modulation (PM), double sideband modulation (DSM), pulse position modulation (PPM), pulse code modulation (PCM) and pulse amplitude modulation (PAM). All of these approaches can be applied to the problem of variable frequency power transmission from the A.C. supply to the induction motor; not all will be efficient and those techniques most suited to information transmissions will not, of necessity, be most efficient in application to power transfer.

The application of communication principles to variablefrequency, solid-state power converters has resulted in significant improvements in efficiency of power inversion through the implementation of pulse width modulation (PWM) as a means of frequency and voltage control [3]. PWM is a well-known principle of information communication [4] and the concept of a.c. power converters as modulators (since frequency changing can only be obtained by modulation) has influenced research activities in employing the premise that communication principles can be applied to modern power converters with some benefit [5].

Other practical examples of the application of communication principles to power converters are the use of amplitude modulation to achieve a 2:1 speed change [6], the stepped sine wave modulation principle [7], which achieves the elimination of sub harmonic problems (at non-integer frequency ratios) and the implementation of

- 2 -

mathematical analyses which allow a fundamental appreciation of the modulation principle involved [8]. Alternative analyses can also provide a clear insight into the frequency spectra of the modulation process when integer frequency ratios are adopted [9].

Waveform analysis is an important aspect of any investigation into PWM motor drives. The harmonics present in a PWM waveform can produce major problems - large eddycurrent losses, torque pulsations and sub-harmonic rotational torques [10]. A knowledge of the amplitude, phase and frequency of the harmonics is essential for effecting assessments of motor operation and system performance.

# Power Conversion

The recent Bart experience [19] has cast great doubt on the suitability of the DC motor for industrial and transport use. Experience has shown that the DC machine is the weakest link of the drive system and that the brushes and commutators are responsible for maximum failure rates, which result in expensive equipment outages.

For many years the inherent simplicity, ruggedness, low cost and high torque/inertia ratio of the induction motor has been a crucial factor in determining its use for constant speed drives - about 80% of motor production is taken up by induction motors. For a similar period these same qualities have spurred research into variable speed induction motor drives. However, in many cases, the significant advantage of the isolated rotor, with no electrical connection, has been sacrificed in order to achieve the range of speed control. Of the remaining techniques, such as the cycloconverter, speed limitations still exist [11] in the design of the unit (even though there have been some improvements) and a high cost penalty is incurred in operation in that 36 thyristors are required in order that low frequency 'cogging' effects can be avoided - different approaches [12],[13] incur other limitations in response time, complexity and economic viability whilst variable D.C. link, 6 step inverters [14] introduce cogging at low frequencies (below 5Hz) and require two power modulation stages. With PWM inverters, both voltage and frequency conversion are achieved in a single set of power modulators. Using McMurray bridge inverters only twelve thyristors are required, whilst six of these are needed for commutation only and do not operate at the high power levels of the load circuitry - in addition, the design of the McMurray bridge inverter is well documented.

Even with these limitations, there are still many areas which require investigation. Several different types of PWM could be generated and it is shown in the earlier chapters that regular sampled asymmetric PWM has definite practical advantages over the natural sampled form of PWM.

# PWM Modulation Techniques

Using a mixer/multiplier in communications circuits has some similarity to the use of a comparator in power circuits. By changing the character of the two input signals to the mixer, differing processes of modulation can be obtained (that is AM and DSM). In the same way, very different forms of PWM can be obtained simply by changing the two modulating signals to the comparator.

- 4 -

A large number of PWM generation techniques have been proposed in the literature [15], [16] in an effort to produce an improved A.C. variable speed induction motor drive with lower losses, fewer pulsating torques and greater frequency stability. The PWM waveforms can appear to be similar, when studied in the time domain, but a frequency domain analysis immediately indicates major differences in their spectra.

Under normal operating conditions the induction motor has a sine-wave drive. If it is assumed that this is an optimum drive condition then the harmonic content of the PWM waveform can be seen to be an important parameter in determing operational performance. Further, the amplitude, frequency (or frequency ratio) and phase of the harmonics will set the resultant pulsating torques, their level, direction and stability.

In an effort to reduce the harmonic content multi-voltage-level PWM waveforms [17] have been proposed for use in motor drives. However, practical constraints generally limit engineered systems to the use of two-level waveforms, although, three-level waveforms are When using two level PWM drives it is occasionally utilized. important to have a three-wire connection to the three-phase motor since a four-wire system, which would include a neutral return, would radically alter the characteristics of the drive. Carrier harmonics, present in the PWM signal, would be provided with a return path, hence current flow is obtained at all frequencies. In the three-wire system, in the absence of a neutral connection, harmonic current flow only occurs when there is an amplitude and/or phase difference between the harmonics in the three phase PWM waveforms. It is to be noted

- 5 -

that triple harmonics can actually be cancelled in this technique [18], when using triple integer frequency ratios. It is the two-level PWM waveform which is considered for further research.

# Application of LSI Integrated circuits

Because of the recent availability of large scale integrated circuits, considerable effort has been devoted to the development of a digital PWM control system for power inverters, in order to eliminate the problems of drift and setting up procedure associated with analogue control techniques. However, it was also thought that these advantages should not be realised at the cost of deterioration in the harmonic spectra of the output PWM voltage waveform, or loss of adaptability and flexibility of the power inverter. Therefore, it was decided to implement the preferred regular sampled asymmetric PWM process by means of a microprocessor, where the switching points of the three-phase width-modulated pulses were determined by the stored program in conjunction with the input data.

After some initial re-design and testing of the analogue rig experimental results confirmed the suitability of the regular sampled form of PWM. Subsequently, a software based, microprocessor design was completed using the trignometric equation describing the individual pulse widths of the regular sampled, three phase, PWM waveform. The interface hardware containing the programmable timer module was re-designed several times since it was found that on some occasions the timer did not appear to operate to specification. Eventually the fault was found to be hardware based and caused by the inherent delays of the CMOS chips used for address decoding. Once

- 6 -

these delays were equalised the interface unit operated as required. The main hardware components retained from the analogue design, were the McMurray inverter and the pulse amplifier/sequence circuits.

The microprocessor rig was tested and used to control a 5h.p. induction motor over a range from 1Hz to 100Hz, although it was found necessary to modify the D.C. link voltage at both extremities. In addition, a spectrum analysis of the ouput waveform, from the microprocessor, proved that the system was accurately emulating the preferred regular sampled asymmetric technique of PWM generation far more accurately than the analogue rig.

# 1.1 Backround to the Application of the Thyristor in Variable Speed Drives

In early attempts, the generation of a variable frequency output, for induction motor power supplies, was both costly, complicated and only justified in special circumstances. One practical application was as the propellor drive on battleships [20,21] where the generator speed was adjusted over a wide range by diesel or steam turbines. In 1947 [22] Heumann reviewed the larger power (M.W.) techniques of induction producing variable frequency scources for motors. Alternators and frequency converters, driven by adjustable speed electric motors, were the two fundamental types of conversion apparatus in use. Control of frequency was accomplished by the control of the speed of the driving motor of the conversion set, and the systems were used to spin large propellors, on test, for adjustable speed testing of compressor and gas turbines, and for the high power drive of large wind tunnels [23] (1958). Another scheme [24] generated the variable frequency by using a gas turbine alternator which powered six gas circulators which were driven by six 7,000H.P. squirrel cage induction motors. This was used for the  $\Omega_2$  blower drives for the Hinkley Point and Bradwell Atomic Power Stations.

In 1956 Russian authors [25] considered the use of switching relays, in series with the 3 phase A.C. supply. Large inrush currents and slow switching speed limited the applications. This approach was further considered by Erlicki, [26] using thyratrons and

- 8 -

Bird [27] and Munoz [28] using thyristors. It appears that the approach could only produce a few discrete frequencies (such as 40Hz) at which proper operation of the induction motor was achieved. In 1958 Straughen [29] used a D.C. magnetic circuit as a frequency doubler which allowed the motor to operate at two discrete speeds, one being twice that of the other - even as late as 1961 [30] mercury arc rectifiers were still being considered for frequency changing.

The invention of the thyristor, in 1957, was to substantially improve the economics of power frequency - changing supplies for induction motors. By the early 1960's the thyristor had become well established as a power switching device. [31,32]

# 1.2 Classification of Present Day Variable Speed Drives

In the late 50's/early 60's, industrial manufacturers readily accepted the thyristor which compared so favourably with the fragile thyratron and bulky magnetic amplifiers as well as the motor generator sets, required for the generation of variable frequency sources, for motor speed control. The advent of the opto-coupler has also helped overcome the severe noise problems dictated by the heavy industry environment. This device has enabled the isolation of units, in order to avoid the problems of ground loops and parasitic capacitive coupling. Further, the continued increase in complexity and reduction in size of integrated circuits, has allowed the design of separate, modular units, which can be connected in various ways. These systems realise the functions of a wide range of variable speed A.C. drives such that costs are reduced and reliability improved.

- 9 -

Variable frequency inverters, for A.C. motors, have widely differing design approaches. Each design has its merits, although some techniques have distinct advantages which others do not possess. A brief description of the available types, is given together with an outline of their individual characteristics.

# 1.2.1 Variable Transformer Types

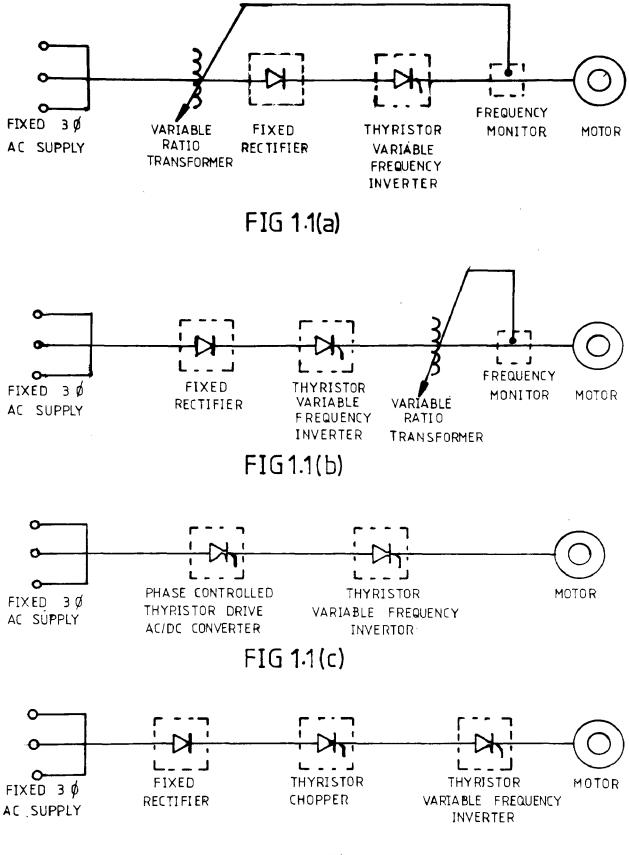

#### 1.2.1.1 Type (a) Variable Input Transformer

The variable input transformer (VIT) inverter technique, Figure 1.1(a), transforms the input A.C. power line voltage, by a controllable turns ratio, which is determined by the ouput frequency of the inverter. The transformer output voltage is subsequently rectified and then modulated, by the inverter, to provide a three phase, quasi square-wave drive (i.e. the resulting phase voltage will have six steps) with adjustable voltage and frequency. Note that two controlled power conversion stages are required (the transformer and the inverter), that the transformer is expensive and would require mechanical maintenance. Further, the response time of the unit would be further limited by that of the variable ratio transformer whilst the inverter would have to be designed to operate over a wide voltage range.

FIG 1.1(d)

.

# 1.2.1.2 Type (b) the Variable Output Transformer

The fixed A.C. supply is rectified and smoothed to provide a constant D.C. link voltage to the inverter Figure 1.1(b), whilst the inverter output is connected through a variable transformer whose turns ratio controls the voltage of the three phase supply to the motor Figure 1.1(b). The output transformer adjusts the amplitude of the motor supply, with output frequency, in order to maintain the proper voltage to frequency ratio.

The principle disadvantages are the slower response time, two power conversion stages are required whilst the output transformer must be a wide-band device, whose specifications must include its operation at the minimum output frequency and maximum rated load.

#### 1.2.2 The Unrestricted Frequency Converter

This unit is very similar to the cycloconverter principle described later. The main difference is that the upper frequency limitations are removed through the introduction of forced commutation. Improvements in power factor are achieved, however, the extra costs and complexity of the device appears to have ensured that it still remains a project of research interest only, Miyairi and Takahashi [33] first proposed the system in 1968 and Westinghouse investigated a similar system although it is not, as yet, produced commercially.

# 1.2.3 The High Frequency Link Inverter

This technique uses a tuned circuit in the output which is excited from a pulse source - the output being transformer coupled to the motor. This approach is best adopted for constant speed drives as the tuned circuit components would require to be variable, necessitating some mechanical drive system. This system has proved useful in space applications for fixed frequency supplies and D.C. power conversion.

# 1.2.4 The Solid State Phase Shift Inverter

The input A.C. supply is rectified to a constant D.C. voltage which supplies two or more separate inverters, all in parallel. The output of the inverters are phase-shifted with respect to each other and added, algebraically by the use of output transformers. The phase shift can be modified in such a way as to control the output voltage amplitude.

This technique requires extra inverters and a wide-band output transformer increases complexity and cost although the method has again found use in space application for fixed frequency power supplies.

#### 1.3 Practical Static Inverter Drives for A.C. Motors

#### 1.3.1 The Six Step Voltage Fed Inverter

The most common waveform employed for static inverter drives is the six step or quasi-square wave drive Figure 1.1(c). Twelve, eighteen and twenty four step versions are possible, but their cost is seldom justified by the reduced harmonic content present in the output waveform. The six step waveform is specifically designed so that the third harmonic, and all its multiples, are identically zero. All the systems are capable of regeneration to a certain extent - resistors can be included to dissipate the regenerated energy. However, for true regeneration the diode bridge or thyristor bridge needs to be replaced by a bi-lateral thyristor bridge which would allow power flow in both directions. No further modifications are normally required to the inverter sections.

Commercially available stepped waveform inverters use many schemes to attain frequency and voltage control and all units are restricted to operation above 5Hz due to the crawling and cogging torques produced in the motor at lower frequency operation. The speed range is limited to about 10:1 and the predominant conversion methods are as follows.

#### 1.3.1.2 Variable Voltage-Phase Controlled

Two power conversion stages are utilised Figure 1.1(c). The first stage converts the constant A.C. input voltage to a variable D.C. voltage by employing a phase controlled thyristor bridge, circuit. The second power conversion generates the quasi-square waveforms which determine the operating frequency of the supply to the motor. In this way a variable voltage, variable frequency, six-step, three-phase waveform is generated. In addition, by varying the D.C. voltage and the inverter frequency, simultaneously, a constant voltage/frequency ratio can be maintained, for a wide range of speeds.

It is usually necessary to provide a separate, constant voltage D.C. supply for the commutating circuit to ensure correct operation over the full speed range. This system tends to be the least expensive and although it cannot be operated from a standby battery, nor is it satisfactory for low frequency operation, it is the most common industrial power conversion technique. The system has a good response time, the limitations being determined by motor characteristics rather than those of the solid-state units.

# 1.3.1.3 Variable Voltage-Chopper-Controlled

The system requires three power conversion sections all in series Figure 1.1(d) a diode bridge for converting the A.C. input to a constant D.C. potential, a chopper and filter, for producing a variable D.C. supply and an inverter to set the frequency of the final A.C. drive to the motor. The system has several advantages. It can be operated from a standby battery system, it has a fast response time, can operate a number of inverters at different frequency/voltage settings for multi-motor drives and the use of the high frequency chopper enables the design of sophisticated protection circuitry. Inverter fuse failures, due to load faults, are reduced by this safety system.

# 1.3.1.4 Six Step Current Fed Inverters

The basic systems are as previously outlined, the main differences being confined to the inverters. Large inductors are placed in series with the supply to the inverters. This has the effect of forcing the current to be constant, rather than the voltage. That is, it is the polarity of the voltage which reverses as the power flows to and from the load, during the cycle. In this case, it is necessary to provide voltage limiting circuits, instead of the current limiting circuits of the previous units.

The main advantage provided by this approach is the rugged reliability achieved in application. Momentary shorts, caused by load faults or interference, can be easily tolerated, without fusing, since the current remains constant (as determined by the D.C. link inductance). The inverter can be designed with low speed rectifier grade thyristors whilst the regeneration process is simple and no additional components are required - further only six thyristors are required. The current inverters do have several limitations however they cannot operate on no load and are unstable on light load, high speed applications. Further the frequency range is somewhat lower and the large series inductor and commutating capacitor components

- 16 -

increase both size and costs of the inverter, whilst, at present, a single current inverter cannot be utilised with multi-motor drives.

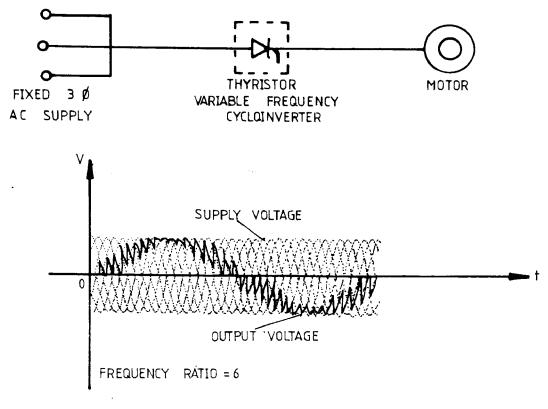

# 1.3.2 The Cycloconverter

In theory, the cycloconverter Figure 1.2(a) requires only a single power conversion unit to convert the incoming constant voltage, constant frequency supply, to a variable voltage variable frequency supply. It is a direct A.C. to A.C. converter, since no intermediate D.C. link is required.

In practice, a three phase to six phase transformer is required, in order that the ripple amplitude on the output waveforms is reduced to a reasonable level. This entails the use of thirty- six thyristors (as compared to twelve in other bridge units) in the power conversion circuit, although commutation is effected naturally, by the polarity reversal of the input A.C. waveform.

The three phase sinusoidal output waveform is approximated by the phased addition of selected segments of the A.C. input waveforms as shown in Figure 1.2(b), so that its average value approaches a sine wave.

The cycloconverter is limited to producing low frequency drives from below 1Hz to approximately one third of the supply frequency. If the modulator is operated beyond this limit, low frequency components are produced which interfere with the normal operation of the motor. Due to its high initial cost and low frequency limitations, its main application is found in controlling large motors (in excess of 500kW) or in controlling multi-motor stations as required in steel works

- 17 -

FIG 1.2(a)

FIG 1.2(b)

roller tables. The drive can also suffer from poor power factor performance although it is fully regenerative in operation.

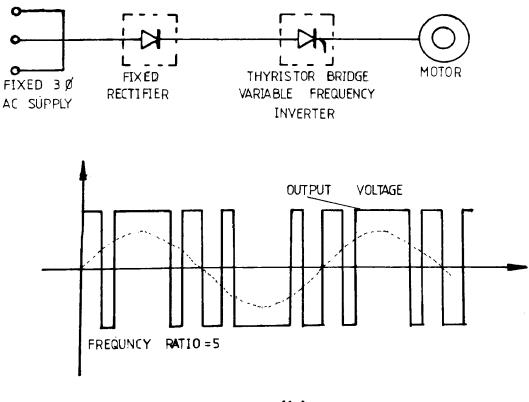

# 1.3.3 Pulse Width Modulation (PWM)

The input A.C. supply is rectified to provide a constant D.C. link voltage to a set of twelve thyristors connected in a bridge configuration Figure 1.2(b). The D.C. voltage is then converted into a set of pulses (the number may vary from one to over twenty- four) whose widths are varied, with respect to each other, and in such a way that their average value approximates to a sine wave as shown in Figure 1.2(b).

Two power conversion sections are required although both voltage and frequency control, of the output waveform, is achieved in a single set of thyristor bridge inverters. Voltage control is realised by varying the relative pulse widths whilst frequency control is achieved by varying the distances between the pulses (using some form of central reference point). As with the cycloconverter the number of pulses per cycle has a significant effect on the harmonic content of the waveform and the inductive reactance of the motor serves so as to smooth the input current waveform.

Good power factors (approximately 0.96 at all frequencies) and unrestricted frequency ranges are obtained. Low frequency operation below 5Hz, is also easily achieved through the use of larger pulse numbers (hence fewer low frequency harmonics). However, regeneration is not possible with a rectified three phase supply and the power handling capability is limited to approximately 100kW by the fact that

- 19 -

the fast-turn off inverter grade thyristors have a limited power specification.

All the schemes, presented in the brief review, are open loop control systems. That is there is no feedback control included in their circuitry. Although the dynamic performance of every unit could be improved using frequency, voltage, current or flux feedback information the basic limitations of each approach still remain.

# 1.4 Pulse Modulation - Theoretical Possiblities

Variable speed/torque induction motor drives require variable frequency/voltage sources. Generally, mains power supplies are constant frequency, constant voltage sources so that power transmission can be cost effective. Thus, some method of achieving a variable frequency, variable voltage supply from a static frequency, static voltage supply needs to be implemented.

There are many techniques of power conversion where the aim is to provide a three-phase variable frequency, variable voltage source [1,2]. For high power converters, where efficiency is at a premium the use of pulse modulated systems has found favour because the system can operate with efficiencies in excess of 90%. Further the technology of thyristors has advanced such that fast turn-off, high power devices are available at a low enough cost to ensure the economic viability of power inverters.

The availability of high power thyristors has accentuated the development of pulse-modulated power transfer [34] and pulse modulation techniques have also been used extensively in the

- 20 -

communications field for the transmission of information signals [8]. The process of static frequency change is known as modulation. For example, amplitude modulation is a process which changes both the amplitude and frequency of a fixed frequency source. Information transmission and coding techniques cover frequency modulation (FM), amplitude modulation (AM), phase modulation (PM), double sideband modulation (DSM) and pulse - position modulation (PPM), pulse code modulation (PCM) and pulse amplitude modulation (PAM). All of these approaches can be applied to the problem of variable frequency power transmission from the A.C. supply to the induction motor; not all will be efficient and those techniques most suited to information transmissions will not, of necessity, be most efficient in application to power transfer.

However, the application of communication principles to variable-frequency, solid-state power converters has resulted in significant improvements, in efficiency, of power inversion through the implementation of pulse width modulation (PWM) as a means of frequency and voltage control.[35]

PWM is a well known principle of information communication [4] and the concept of A.C. power converters as modulators (since frequency changing can only be obtained by modulation) has influenced research activities in employing the premise that communication principles can be applied to modern power converters with some benefit.[36]

Other practical examples of the applications of communication principles to power converters are the use of amplitude modulation to achieve a 2:1 speed change [28], the stepped sine wave modulation

- 21 -

principle [7], which achieves the elimination of subharmonic problems (at non-integer frequency ratios) and the implementation of mathematical analyses which allow a fundamental appreciation of the modulation principle involved.[38] Alternative analyses can also provide a clear insight into the frequency spectra of the modulation process when integer frequency ratios are adopted. [9]

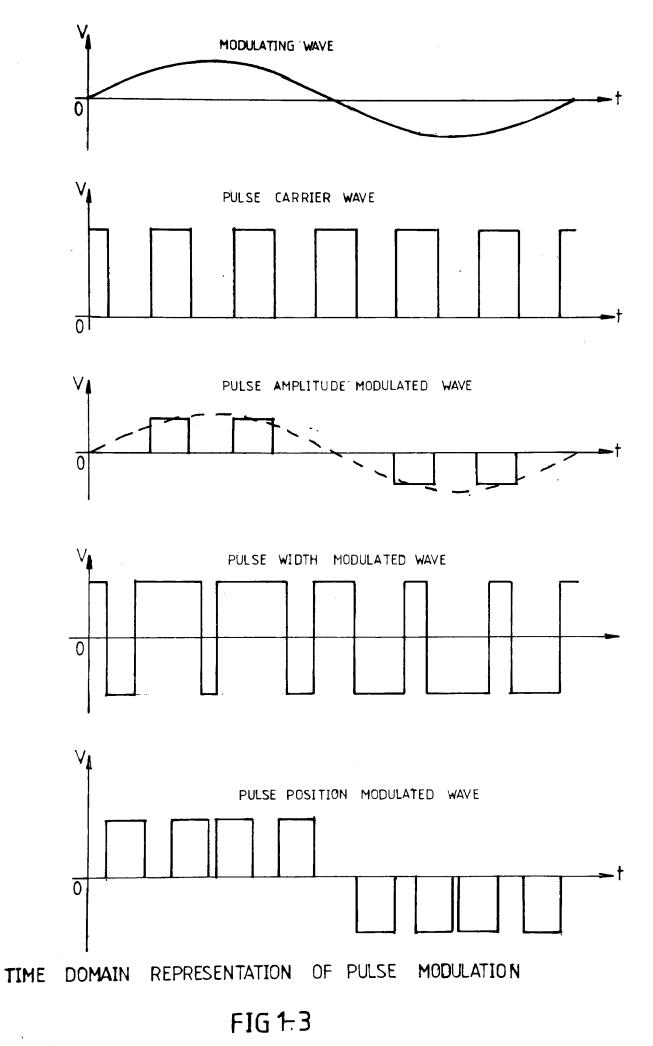

#### 1.4.1 Types of Pulse Modulation

The unmodulated carrier-wave of a pulse-modulated system, is generally considered to consist of a series of regularly recurring pulses. Such a waveform can be completely defined by three parameters. The three parameters are :

1. The amplitude of the pulses, Vp.

2. The duration between pulses, T.

3. The duration of the pulses, to.

Normally the three parameters are constant. Modulation is the process of varying one or more of the three parameters, while the remaining parameters are held constant. Variation of the amplitude of the pulses while the duration between pulses and the duration of the pulses are held constant is termed - 'amplitude-modulation'. When the amplitude and duration of the pulses are held constant, and the pulses is made to vary, the between duration The variation of the 'pulse-position-modulation' achieved. is duration or width of the pulses, while the amplitude of the pulses and

- 22 -

- 23 -

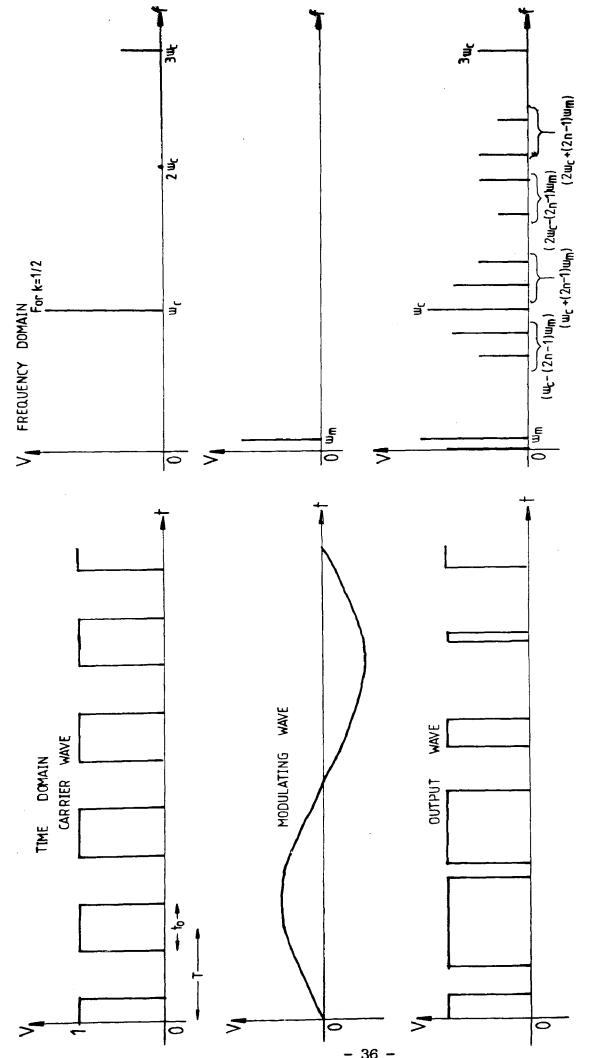

duration between the pulses are held constant, is known as 'pulse-width-modulation'. The above modulation processes are illustrated in the time domain in Figure (1.3). Although pulse-modulation normally infers the variation of one parameter while the remaining two parameters are held constant, the possibility of simultaneously varying two of the three parameters or all three parameters cannot be ruled out.

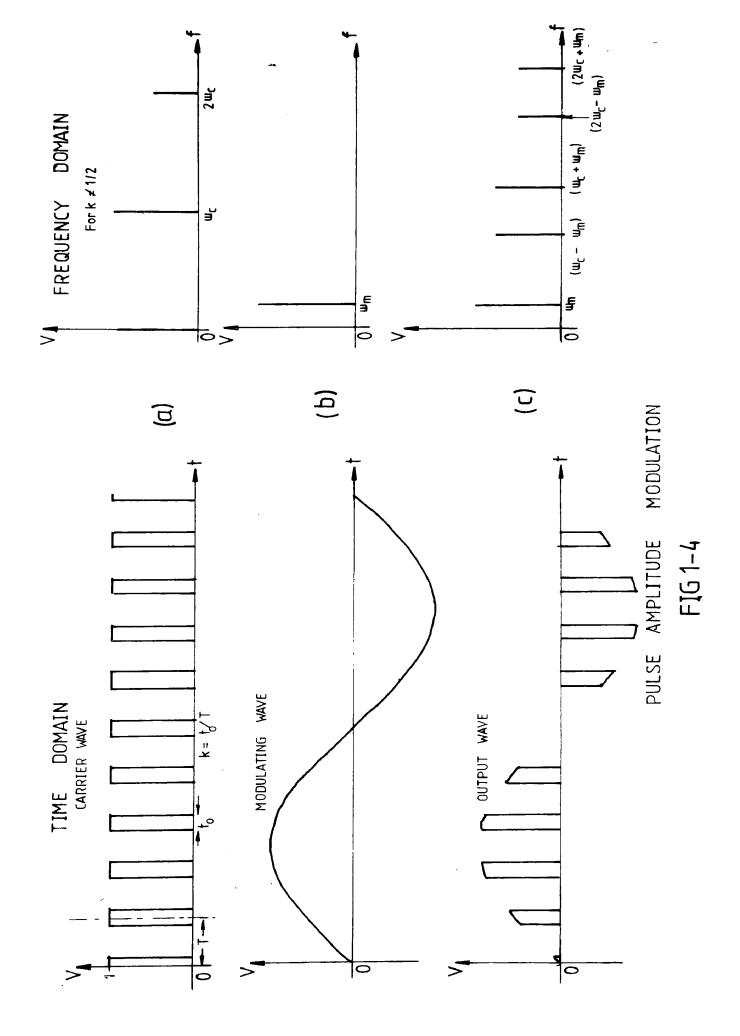

## 1.4.2 The Unmodulated Pulse Carrier Wave

The zero on the time-axis of the unmodulated pulse-carrier wave may be positioned as shown in Figure 1.4(a). The carrier-wave can then be expressed by the following time function :

$$U(t) = k + k \sum_{m=1}^{\infty} \frac{\sin m k \pi}{m k \pi} \cdot \cos m \omega_{c} t \qquad ---- (1.1)$$

where  $k = \frac{t_{O}}{T}$ .

#### 1.4.3 Pulse Amplitude Modulation (P.A.M.)

This method of modulation basically entails the variation of the amplitude of the pulses according to the modulating signal, so that instead of the pulses having unit height, they have a height varying as V(t), where V(t) is the modulating function. Therefore, if the modulating function is defined by :

$$V(t) = A_{m} \cos(\omega_{m}t + \phi_{m}) ---- (1.2)$$

then the process of amplitude modulation is given by :

$$M(t) \cdot U(t) = [A_{m} \cos(\omega_{m}t + \phi_{m})] [k + k \sum_{m=1}^{\infty} \frac{\sin m k \pi}{m k \pi} \cdot \cos m \omega_{c}t]$$

$$= k A_{m} \cos(\omega_{m}t + \phi_{m}) + KA_{m} \sum_{m=1}^{\infty} \frac{\sin m k \pi}{2 m k \pi} \cdot \cos[(m \omega_{c} \pm \omega_{m})t \pm \phi_{m}] ---- (1.3)$$

This process is illustrated in both the time and frequency domains in Figure 1.4. It will be seen from equation (1.3) that the products of modulation are upper and lower side bands of frequencies :  $(m\omega_c + \omega_m)$  and  $(m\omega_c - \omega_m)$  around the carrier of frequency,  $\omega_c$ , and its harmonics, plus a remanent of the modulating wave of frequency,  $\omega_m$ . The amount of modulating wave remaining, will depend on the magnitude of  $A_m$  and the value of k.

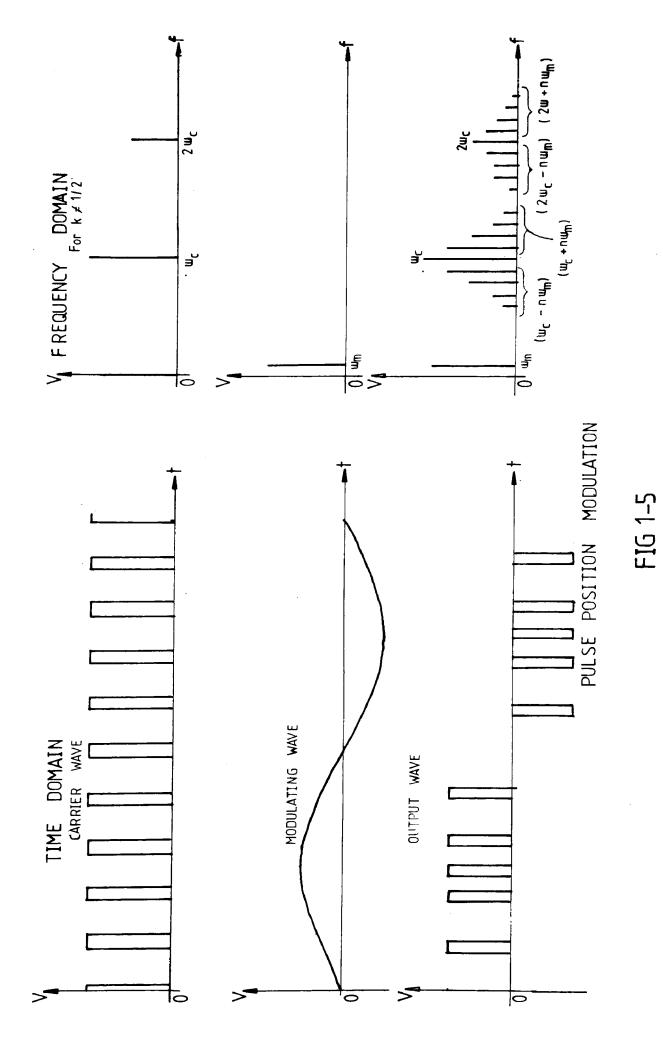

#### 1.4.4 Pulse Position Modulation (P.P.M.)

P.P.M. causes the pulses illustrated in Figure 1.5 to be displaced in time according to instantaneous values of the modulating wave, the height and duration of the pulses being maintained constant. The unmodulated pulses which have a repetition period, T, and mid-time values at 0,T,2T,3T-----, are described by the time function :

$$U(t) = k + k \sum_{m=1}^{\infty} \frac{\sin m k \pi}{m k \pi} \cdot \cos m \omega_{c} t \qquad ----(1.1)$$

If the pulse centre lines are varied in time according to the function :

$$T.A_m \cos (\omega_m t + \phi_m)$$

and to  $\langle \langle T, then the pulse position modulated pulses are described by the time-function [37]:$

$$f(t) = k + 2k \sum_{m=1}^{m=\omega} \frac{\sin m k \pi}{m k \pi} \cos m \omega_{c} [t - T A_{m} \cos(\omega_{m} t + \phi_{m})] -----(1.4)$$

- 25 -

- 26 -

\_ 27 \_

Equation (1.4) can be further expanded in terms of Bessel functions as follows :

where  $x = 2\pi A_m m$ .

Figure (1.5) illustrates the P.P.M. process in both the time and frequency domains. Equation (1.5) illustrates that the products of modulation are the carrier signal and its harmonics which have amplitudes of  $2 \frac{\sin m k \pi J_0}{m \pi} (x)$ , and side-bands around the carrier and its harmonics of frequencies :  $m(\omega_c - \omega_m)$  and  $m(\omega_c + \omega_m)$  and amplitudes of  $2 \frac{\sin m k \pi J_0}{m \pi} (x)$ .

It is important to note that equation (1.5) does not contain a harmonic component of modulating frequency whose amplitude is proportional to the amplitude of the modulating wave. This suggests that no linear means of voltage control of the wanted harmonic component is provided.

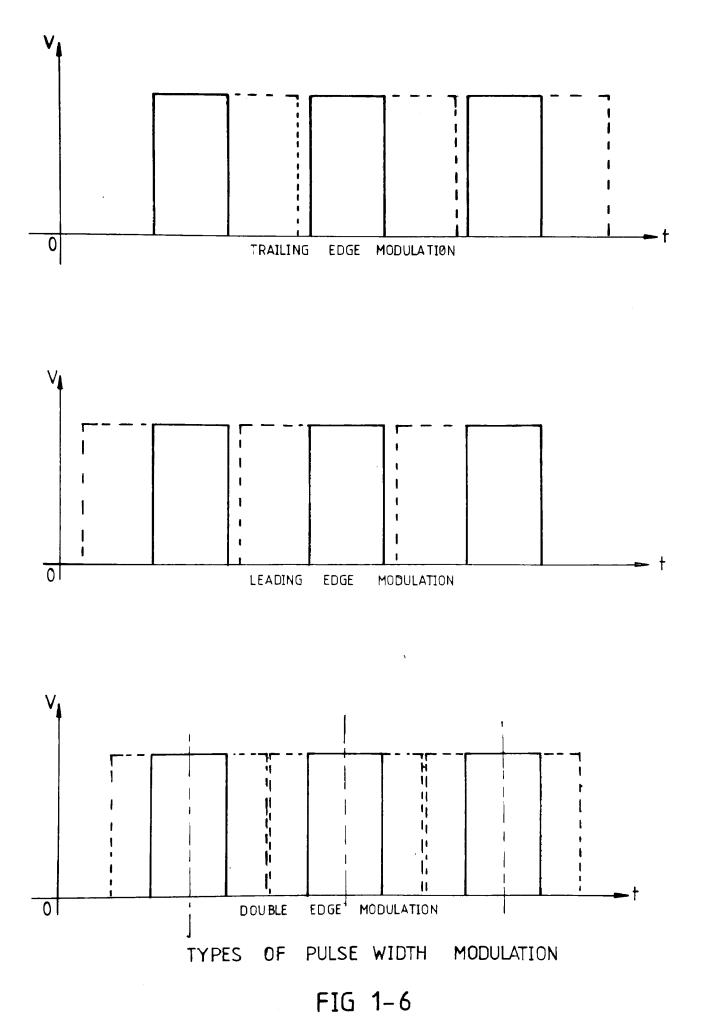

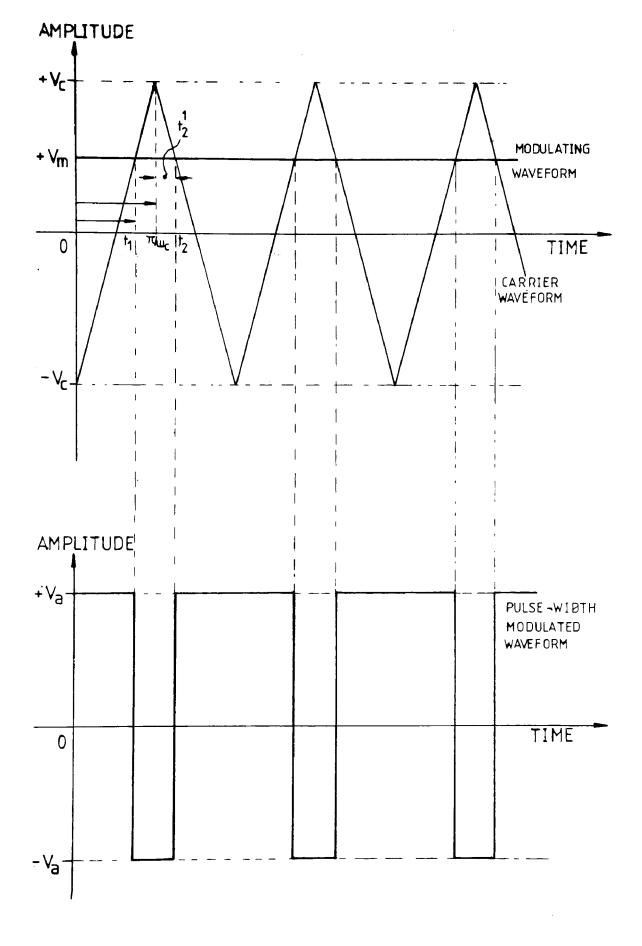

## 1.4.5 Pulse-Width-Modulation (PWM)

This method of modulation causes the widths of the pulses illustrated in Figure 1.4(a) to vary. The degree of variation in the width of each pulse, is dependent upon instantaneous values of the modulating wave. The three possible ways by which the duration of the pulses can be varied are :

1. leading-edge fixed, trailing-edge varied,

2. trailing-edge fixed, leading-edge varied,

3. centre line of pulses fixed, both edges varied.

These three methods of varying the widths of the pulses are used to define the type of pulse-width-modulation, and are illustrated in Figure (1.6).

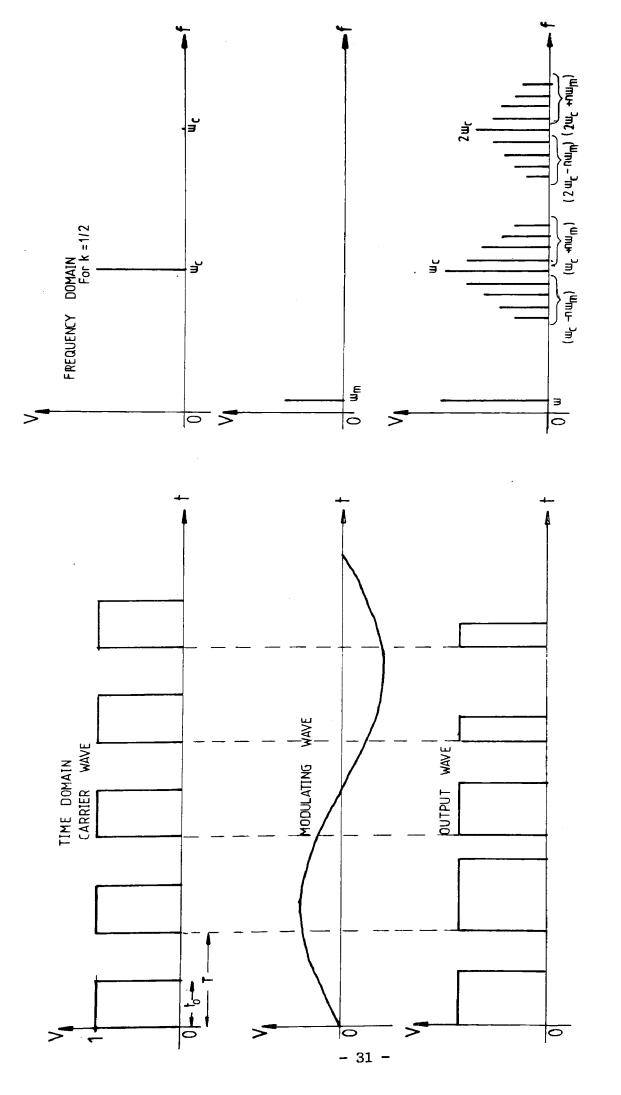

## 1.4.6 Trailing-Edge Pulse-Width-Modulation

This particular form of P.W.M. causes the leading-edges of the pulses to be fixed, whilst the trailing-edges are modulated, the degree of modulation being dependent upon instantaneous values of the modulating wave. This process is illustrated in Figure (1.7). The unmodulated pulses of duration, to, and repetition period, T, are described by the time function  $[^{38}]$ :

$$f(t) = k + k \sum_{\substack{m=0\\m \neq n}}^{m=\infty} \frac{\sin 2m k \pi}{m k \pi} \cos m\omega_{c} t$$

$$m=1$$

$$+ k \sum_{\substack{m=0\\m \neq n}}^{m=\infty} \frac{(1-\cos 2m k \pi)}{m k \pi} \sin m\omega_{c} t \qquad ----(1.6)$$

For this case one of the leading edges of the pulses, is chosen to coincide with zero time as illustrated in Figure (1.7). If the duration of the pulses are varied according to the function :

$$T_{o}(1 + A_{m}\cos(\omega_{m}t + \phi_{m})) ----(1.7)$$

- 30 -

FIG 1-7

TRAILING EDGE MODULATION

then the width modulated pulses are described by the function :

$$f(t) = k(1 + A_{m}Cos(\omega_{m}t + \phi_{m}))$$

$$+ \frac{1}{\pi} \sum_{m=1}^{m=\infty} \frac{1}{m} [Sin 2 m \pi k(1 + A_{m}Cos(\omega_{m}t + \phi_{m}))]Cos m\omega_{c}t$$

$$+ \frac{1}{\pi} \sum_{m=1}^{m=\infty} \frac{1}{m} [1 - Cos 2 \pi m k(1 + A_{m}Cos(\omega_{m}t + \phi_{m}))]Sin m\omega_{c}t$$

$$----(1.8)$$

This function can also be described in terms of Bessel functions as follows :

$$f(t) = k(1 + A_{m}^{COS}(\omega_{m}t + \phi_{m})) + \frac{1}{\pi}\sum_{m=1}^{m=\infty} \frac{1}{m} (Sin \ m\omega_{c}t)$$

$$+ \frac{1}{\pi}\sum_{m=1}^{m=\infty} \sum_{m=1}^{n=\infty} \frac{1}{m} \mu_{n}(2 \ m \ \pi k \ A_{m})Sin(2 \ m \ \pi k \ + \frac{n \ \pi}{2}) ]Cos((m\omega_{c} \ \pm n \ \omega_{m})t \ \pm \ n\phi_{m}$$

-----

From equation (1.9), several interesting facts are apparent : the amplitude of the harmonic component of modulating frequency, is directly proportional to the amplitude of the modulating wave. No harmonics of the modulating wave are present. The amplitude of a harmonic of the carrier wave is inversely proportional to its order. It is of particular interest to note that if the mark/space ratio of the unmodulated pulse carrier-wave is made equal to 1:1, that is to say k = 1/2; then only one of the two side-band terms exists for integer values of m and n. Therefore, for odd values of m and n the side-band components Sin( $(m\omega_c \pm n\omega_m)t \pm \phi_m$ ) will exist with amplitudes of  $\frac{1}{m\pi}J_n(2 \ m\pi k \ A_m)$ , whereas, for even values of m and n the side- band terms of Cos( $(m\omega_c \pm n\omega_m)t \pm \phi_m$ ) will exist, their amplitudes being given by :  $\frac{1}{m\pi}J_n(2 \ m\pi \ k \ A_m)$ .

This means that for all integer values of m and n, side-band frequency components of frequencies :  $(m\omega_c + n\omega_m)$  and  $(m\omega_c - n\omega_m)$  will always occur for this particular form of P.W.M.

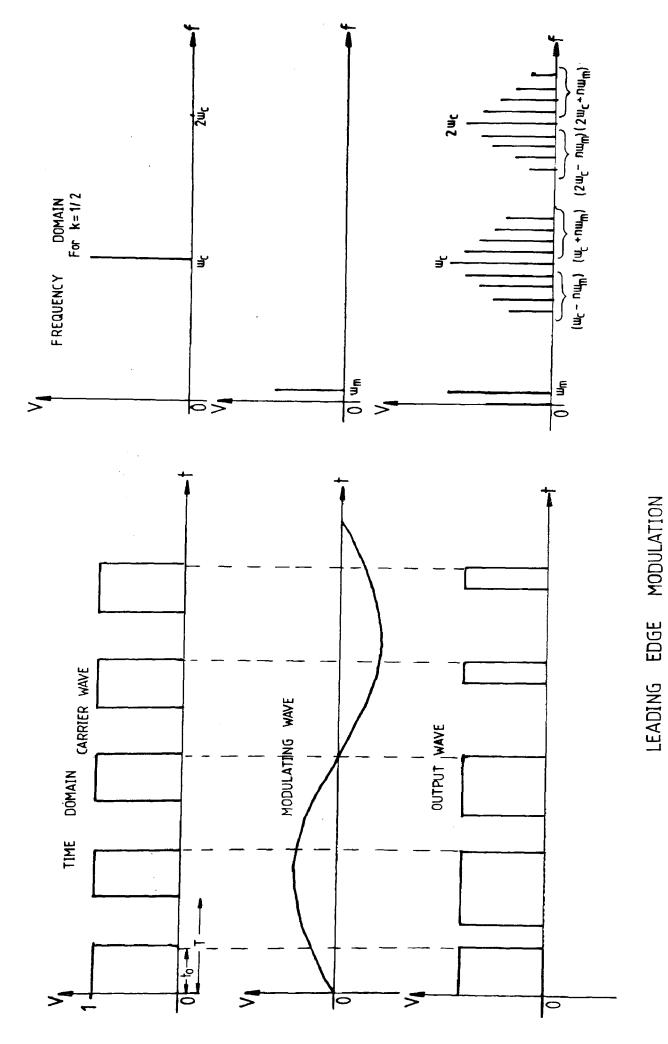

#### 1.4.7 Leading-Edge Pulse-Width-Modulation

For this P.W.M. process the trailing-edges of the pulses are fixed while the leading-edges are modulated. Figure (1.8) illustrates this process in both the time and frequency domains. The time function which describes the modulation of the pulses can be determined from equation (1.9) by reversing the time scale; that is to say : substituting -t for t. This results in the following function :-

$$f(t) = k(1 + A_m \cos(\omega_m t + \phi_m)) - \frac{1}{\pi} \sum_{m=1}^{m=\infty} \frac{1}{m} \sin m\omega_c t$$

$$+\frac{1}{\pi}\sum_{m=1}^{m=\infty}\sum_{m=1}^{m=\infty}\frac{1}{m}\left[\mathcal{V}_{n}(2 \ m\pi kA_{m})\sin(2 \ m\pi k + \frac{n \pi}{2})\right]\cos((m\omega_{m})$$

$$+ n \omega_{\rm m})t + n \phi_{\rm m}$$

$$+\frac{1}{\pi}\sum_{m=1}^{m=\infty}\sum_{m=1}^{m=\infty}\frac{1}{m}[J_{n}(2 m\pi kA_{m})\cos(2 m\pi k + \frac{n}{2}))]Sin((m\omega_{c})$$

$$+ n\omega_{\rm m})t - n\phi_{\rm m}) --(1.10)$$

FIG 1-8

The amplitudes of the various components are the same as for trailing-edge modulation but the phase relationships are different.

# 1.4.8 Double-Edge Pulse-Width-Modulation

This form of modulation causes both edges of the pulses to be modulated. The instants in time at which the leading and trailing edges of each pulse occur, are dependent upon the respective instantaneous values of the modulating wave. This process is illustrated in Figure (1.9). The unmodulated pulses of duration, t, with one pulse centred at t= o, can be described by the time function :-

$$f(t) = k + \frac{2}{\pi} \sum_{m=1}^{m=\infty} \left[ \frac{1}{m} \sin m \pi k \right] \cos m\omega_c t \qquad ----(1.11)$$

If the duration of the pulses are varied according to the function :

$$t_{o}(1 + A_{m} \cos(\omega_{m} t + \phi_{m}))$$

-----(1.12)

then the width - modulated pulses are described by the function :

$$f(t) = k(1 + A_{m}^{COS}(\omega_{m}^{t} + \phi_{m}^{t}))$$

$$+ \frac{2}{\pi} \sum_{m=1}^{m=\infty} \frac{1}{m} \{ \text{Sin m } \pi \text{ k Cos} [m \pi \text{ k } A_{m}^{COS}(\omega_{m}^{t} + \phi_{m}^{t}) \} \}$$

$$+ \cos m \pi \text{ k Sin } [m \pi \text{ k } A_{m}^{COS}(\omega_{m}^{t} + \phi_{m}^{t}) ] \} \quad \cos m\omega_{c}^{t} t$$

----(1.13)

- 35 -

EDGE PULSE WIDTH MODULATION FIG 1-9 DOUBLE

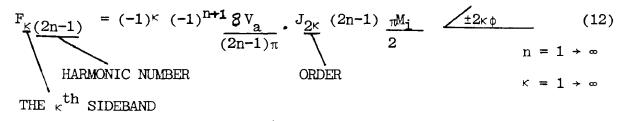

This function can also be described in its Bessel function form as follows :

$$f(t) = k(1 + A_{m}Cos(\omega_{m}t + \phi_{m}))$$

$$+ \frac{2}{\pi} \sum_{m=1}^{m=\infty} \frac{1}{m} [J_{o}(m \pi k A_{m})Sin m \pi k]Cos m\omega_{c}t$$

$$+ \sum_{n=1}^{n=\infty} J_{n}(m \pi k A_{m})Sin(m \pi k + \frac{n \pi}{2}) [Cos((m\omega_{c}) + n\omega_{m})t + n\phi_{m}])$$

+

$$\cos((m\omega_{c} - n\omega_{m})t - n\phi_{m})]$$

----(1.14)

This function shows that, for this case also, the amplitude of the harmonic component of modulating frequency is proportional to the amplitude of the modulating wave.

The second term gives the carrier component and its harmonics of frequency  $m\omega_c$ . The amplitude of the harmonics of the carrier wave are dependent upon the value of k. If k = 1/2, (that is to say : the mark/space ratio of the unmodulated pulses is 1:1) then only odd harmonics of the carrier will be present.

The third term gives the side-band about the carrier whose frequencies are given by  $(m\omega_c + n\omega_m)$  and  $(m\omega_c - n\omega_m)$ . The amplitude of the side-bands are once again dependent upon the value of k. If k = 1/2 as before then for odd harmonics of the carrier only even order side-bands exist, and for even harmonics of the carrier only odd order side-bands exist.

- 37 -

## 1.5 Techniques of P.W.M. Generation

It should be noted that when P.W.M. is used as a means of information communication that part of the signal power which carries no information to the receiver is wasted. The amount of power wasted depends upon the maximum extent to which a pulse can be modulated. When the redundant part is subtracted from the P.W.M. wave, we have P.P.M. and the power saved represents the fundamental advantages of P.P.M. over P.W.M.[39] for information transmission.

In the field of variable speed A.C. drives it is the transmission of power, not information, which is of fundamental importance. This fact produces a difference in the philosophical approach to the design of Power Systems. Optimum techniques of information transmission are not necessarily optimum techniques of power transmission. The redundant power frequency term in P.W.M. actually cancels in the three phase drive, which improves its qualities as a means of power transmisson. Further, P.P.M. will always have a greater pulse number than P.W.M. for any given power transfer and minimum pulse width requirement. These facts alone significantly reduce the efficiency of P.P.M. inverters due to the associated increase in power losses. Thus, for power systems, P.W.M. is superior to P.P.M. as a method of power conversion and transmission. Thus, when applying communications principles to power systems the philosophical differences should be given careful consideration.

The use of a pulse amplitude modulation scheme immediately introduces the practical requirement of a fast response time, variable voltage supply. This technique can provide a reduced harmonic content, in the output power signal, with respect to that of the P.W.M. signal. However, the extra cost and complexity involved would not appear to be justified by the gain in reduction of harmonic content. Further, the double-sided form of P.W.M. modulation has significant advantages over the single-sided forms of P.W.M. modulation. In addition, this does not involve any extra cost or complexity-simply a change in the modulation waveforms used to obtain the P.W.M. waveform. It is also of practical significance that both frequency and voltage control can be achieved in the P.W.M. signal with a single set of power modulators. Whilst problems of cogging, torque pulsations and poor low frequency operation [40,41,42] have been reported in the literature, as already demonstrated, the harmonic content of the P.W.M. waveform can be considerably changed by the choice of modulating waveforms, used to achieve the P.W.M. signal. This fact is of importance as it affects the harmonic content of the waveform at frequencies near the fundamental - this has a direct practical effect on the appearance of cogging and locking torques.

### 1.5.1 Specialist P.W.M.Schemes

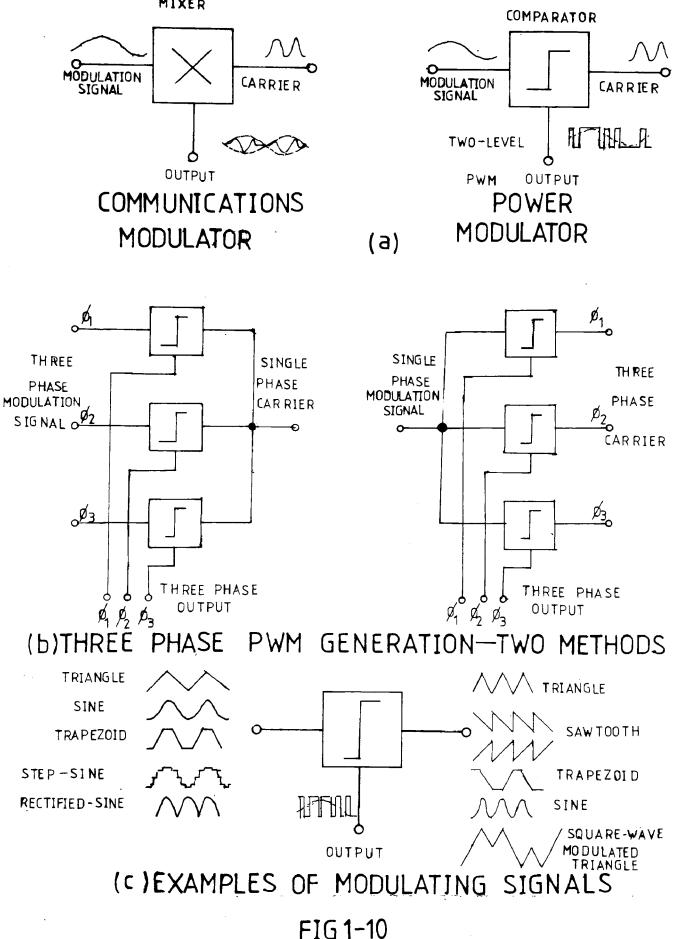

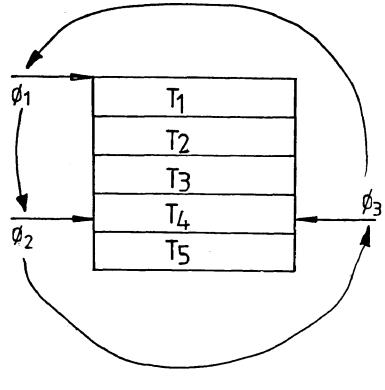

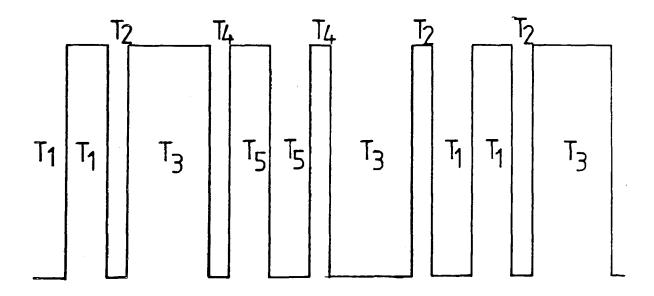

Using a mixer/multiplier in communication circuits has some similarity to the use of a comparator in power circuits. By changing the character of the two input signals to the mixer, differing processes of modulation can be obtained (that is A.M., D.S.M.). In the same way, very different forms of P.W.M. can be obtained simply by changing the two modulating signals to the comparator Figure 1.10(a).

A large number of P.W.M. generation techniques have been proposed in the literature [16,43] in an effort to produce an improved A.C. variable speed induction motor drive with lower losses, fewer pulsating torques and greater frequency stability. The P.W.M. waveforms can appear to be similar, when studied in the time domain, but a frequency domain analysis immediately indicates major differences in their spectra.

Under normal operating conditions the induction motor has a sine-wave drive. If it is assumed that this is an optimum drive condition then the harmonic content of the P.W.M. waveform can be seen to be an important parameter in determining operational performance. Further, the amplitude, frequency (or frequency ratio) and phase of the harmonics will set the resultant pulsating torques, their level, direction and stability.

In an effort to reduce the harmonic content multi-voltage-level P.W.M. waveforms [44] have been proposed for use in motor drives. However, practical constraints generally limit engineered systems to the use of two-level waveforms, although, three-level waveforms are occasionally utilized. When using two-level P.W.M. drives it is important to have a three-wire connection to the three-phase motor since a four-wire system, which would include a neutral return would radically alter the characteristics of the drive. All harmonics present in the P.W.M. signal would be provided with a return path, hence current flow is obtained at all frequencies. In the three-wire system, in the absence of a neutral connection, harmonic current flow,

- 40 -

only occurs when there is an amplitude and/or phase difference between the harmonics in the three-phase P.W.M. waveforms. It is to be noted that triple harmonics can actually be cancelled in this technique [45], when triple integer frequency ratios are utilized. It is the two-level P.W.M. waveform which is considered for further research.

## 1.5.2 PWM Generation Systems

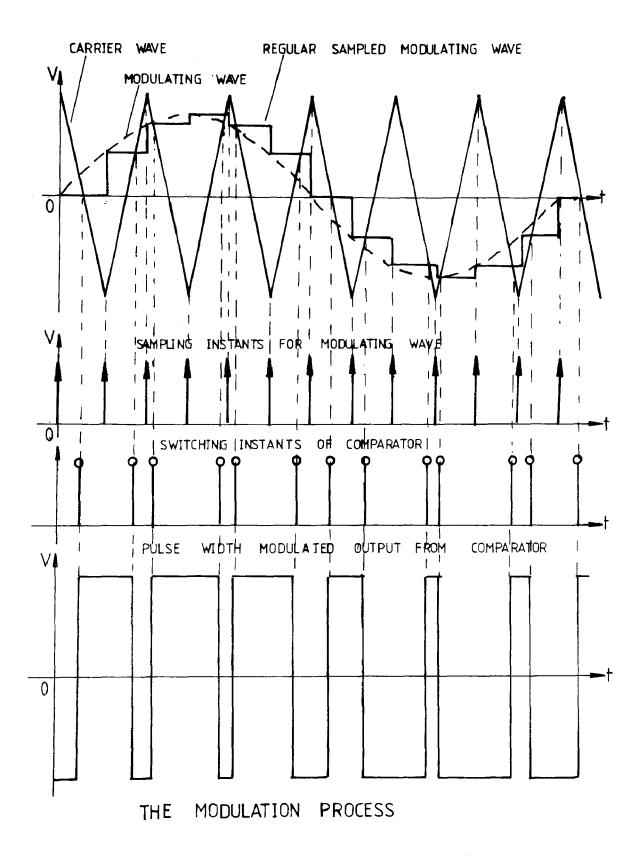

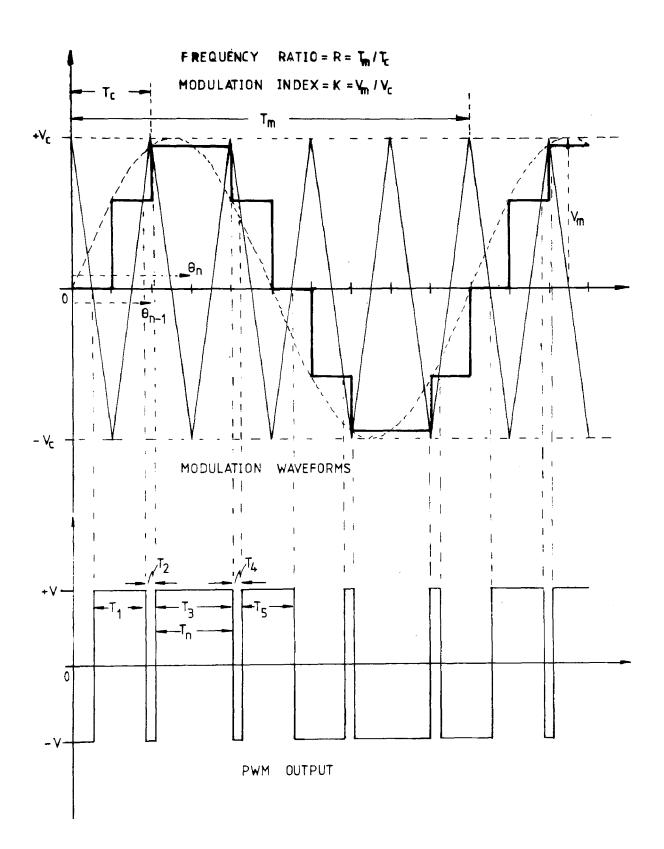

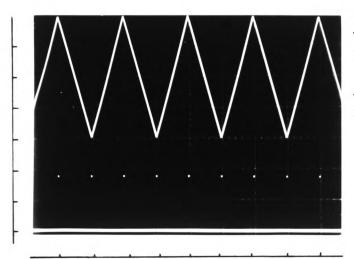

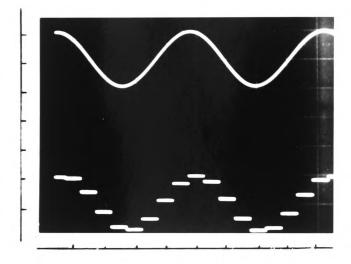

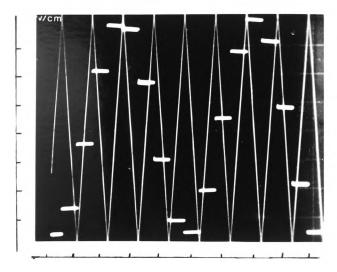

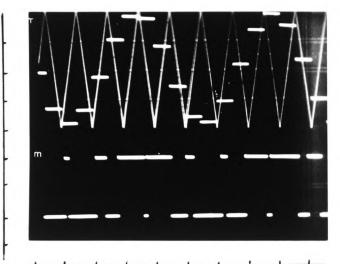

The analogue system of P.W.M. generation employs a carrier signal and modulating signal applied as the two inputs to a comparator, the resultant P.W.M. output being used as the power drive reference signal. Figure 1.10(b).

For three-phase systems, many techniques utilise a three-phase modulating signal as the reference and this is the approach adopted in the practical implementation to be described. Even with these limitations there are still a great many alternative techniques of P.W.M. generation, made possible by the variations of the waveshape of the carrier and modulating signals. Each system will produce unique frequency spectra complicated by the fact that the spectrum will change when the amplitude of the modulating wave (i.e. the modulation index) is changed.

As indicated in Figure 1.10(c), various signals can be used as the modulation signal, these include the use of a symmetrical triangular waveform, a full-wave rectified A.C. waveform, a trapezoidal waveform or a stepped sine waveform. The carrier signal can be a sawtooth waveform with a vertical trailing or leading edge, a sinusoidal waveform, a symmetrical triangular waveform or a

- 42 -

square-wave modulated triangular waveform synchronised to the modulation signal. Many other types of waveform can also be included.

When comparing modulation techniques using a triangular carrier with sinusoid modulation, a sawtooth carrier with sinusoid modulation, a triangular carrier with triangular modulation and a sinusoid carrier with sinusoid modulation, Takahashi [16] concluded that the harmonic content of the P.W.M. waveform is minimised when the carrier wave is triangular and the signal wave is purely sinusoidal.

Further, when a sinusoidal carrier and signal wave is employed, a non-linear relationship is induced between the amplitude of the signal wave (or modulation index) and the amplitude of the fundamental frequency in the P.W.M. output [46]. Also the symmetric triangular carrier wave is the most effective in suppressing low order harmonic amplitudes, whereas, the sawtooth reference introduces particular harmonic components which never appear in other schemes. Stepped sinewaves have also been employed as modulating signals, although the distortion introduced has been shown to be greater than the sine/triangle scheme [47]. However, this particular type of sampling has been widely used in communication systems. The reasons for its wide acceptance in communications are not clearly defined, theliterature available suggest that its acceptance might have been influenced by two factors :-

1. it satisfies the basic sampling theorem and

2. it is argued that it provides an improved signal to noise ratio when compared with natural sampling.

- 43 -

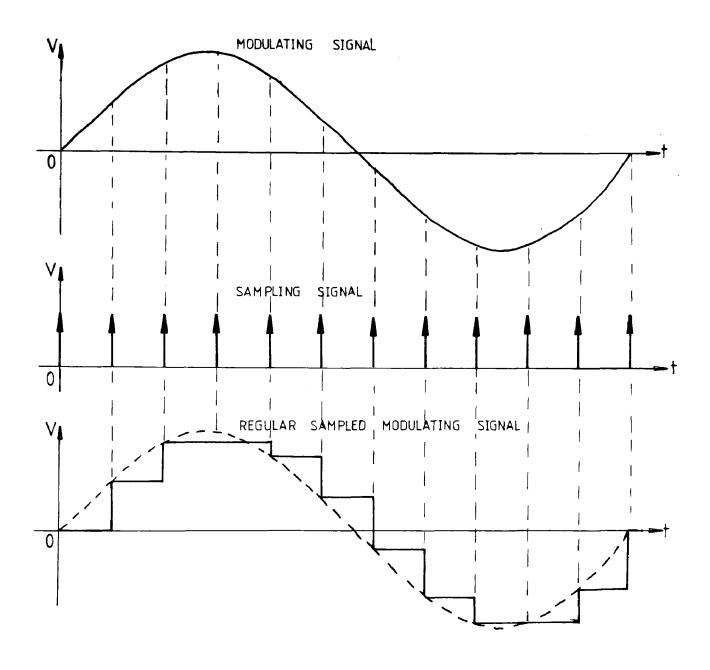

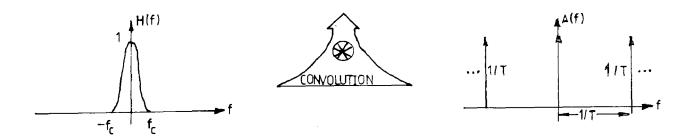

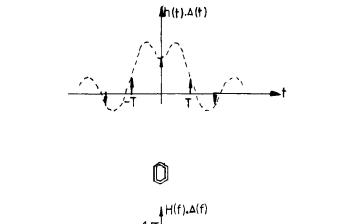

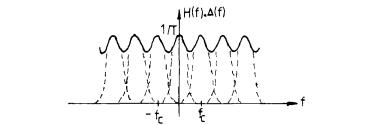

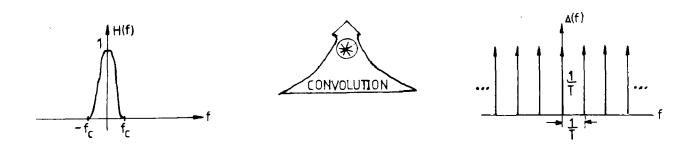

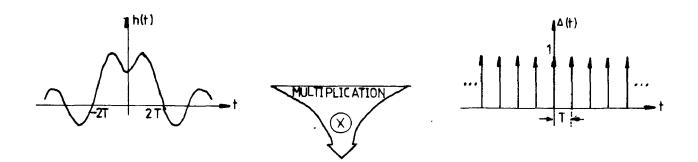

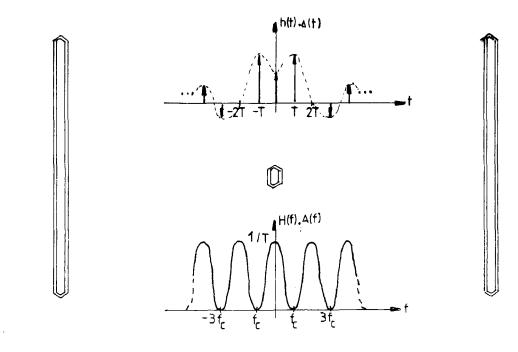

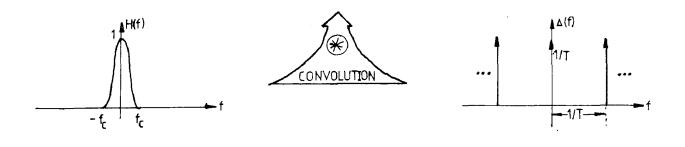

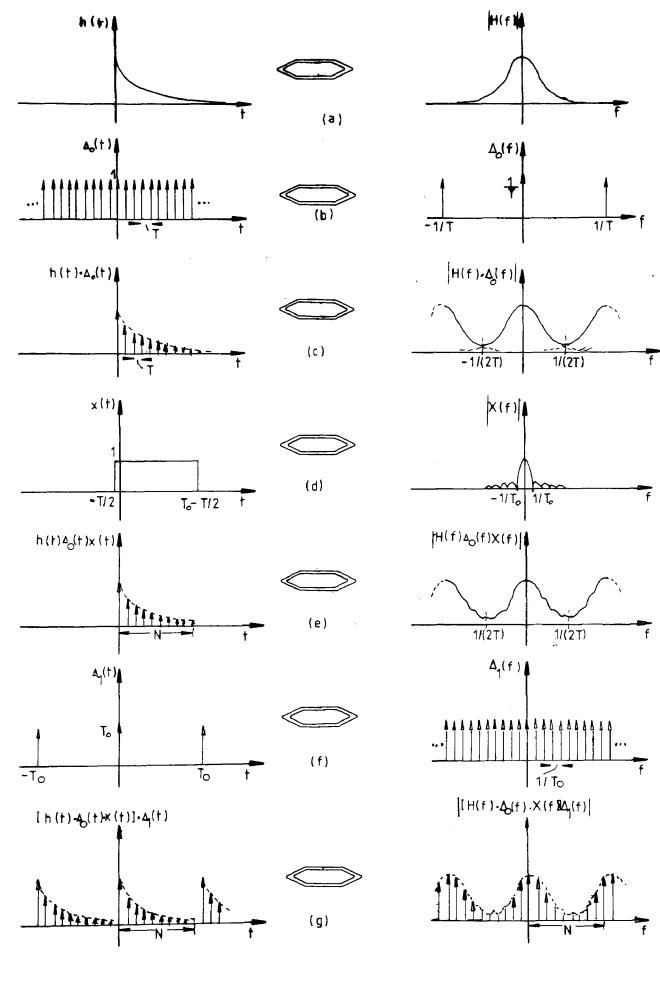

The previously mentioned techniques of regular sampling did not include the synchronisation of the samples of the modulating wave to the apices of the triangular carrier wave. It may be possible that this was the fundamental cause of the distortion rather than the introduction of regular sampling itself. Therefore, it was thought that the application of regular sampling techniques to P.W.M. power convertors might provide a means of improving the harmonic spectra. The application of the regular sampling process to the generation of P.W.M. waveforms, basically entails the sampling of the modulating wave prior to comparison with the carrier wave (Figure 1.11). Samples of the modulating wave are taken at regular intervals by means of the sampling switch, and are then held constant over the sampling period by storing the samples on a capacitor. This converts the modulating wave to its regular sampled version which is then compared with the carrier wave to produce the switching instants of the width modulated pulses. It can be shown that the generation of the regular sampled modulating wave is achieved at a cost of only four extra components. This point is of considerable significance since the capital cost of the P.W.M. convertor must be kept to a minimum if it is to compete with prior-art systems.

# 1.5.3 Regular Sampled Asymmetrical-Double-Edge Modulation

Although there are numerous forms of asymmetrical double-edge the form referred to throughout this thesis as modulation 'asymmetrical' is dependent upon regular sampling at twice the carrier frequency and the comparison of the regular sampled modulating wave triangular carrier wave. This type  $\mathbf{of}$ with an isosceles

- 44 -