# THE BUS STRUCTURE FOR A POLYMORPHIC

COMPUTER SYSTEM

By

Andrew Kennedy Roach B.Sc.(Hons)

This Thesis is submitted in partial fulfilment for the Degree of M.Phil under the regulations of the CNAA

Department of Mathematics and Computing The Polytechnic Of Wales

In collaboration with MITEL Corp.

February 1986

# Statement

I hereby declare that the work embodied in this Thesis are the results of my own independant investigations unless otherwise stated. This work has not been, nor is it currently being, submitted in consideration for any other degree.

Candidate -- A. K. Roach

Director of Studies -- G. E. Quick

### Acknowledgement

I wish to express my appreciation to the following, who provided me with guidance, help and support throughout my research.

Dr. Gerry Quick, Head of School of Computer Studies, West Glamorgan Institute of Higher Education, Swansea, whose initial work this Thesis is a continuation of.

All the members of the Department of Mathematics and Computing at the Polytechnic of Wales; especially Mr.D.J.Green, Dave Eyres, John Ellis, Colin and Chris Bowring; all of whom made my stay a pleasant and eventful one.

Finally my parents, Leslie and Valerie, for without their financial support this research would not have been possible.

#### ABSTRACT

#### The Bus Structure for a Polymorphic Computer System

# A.K.Roach B.Sc(Hons) M.Phil Thesis

The proposed advances in fifth Generation Computing Systems aim to provide an Intelligent Image to the system user. While such images are software based, written in languages such as Prolog and LISP, much of the proposed hardware architecture has lacked innovation and vision. This Thesis addresses these two important points by providing an insight into bus interaction for various scheduling schemes and system configurations, in order that these unique system architectures may evolve.

This Thesis discusses the issues relavent to the application of cellular computer systems and their projected performance characteristics. The cellular computer system under study is the Group Processor System, which is a TRANSPUTER like computer architecture.

The Group Processor System is simulated, and important results are illustrated in graphical form. These graphs are analysed, and the conclusions drawn are of use to computer architects who wish to design and construct Group Processor Systems. The results may also be of use to those architects wishing to develop TRANSPUTER based computer systems.

As a result of the simulation, a major design fault in the original Group Processor proposal resulted in a severe 'bottle-neck' in input-output processing. This has been greatly improved by the provision of the Terminal Environment Switching System; which is also detailed in this Thesis. The result of this research has yielded a more flexible Group Processor System which may be targetted for applications in Intelligent and Knowledge Based Systems.

The relevance of current architecture is discussed in the context of proposed fifth Generation computing needs.

| CONTENTS         | PAGE |

|------------------|------|

| Title            | i    |

| Statement        | ii   |

| Acknowledgement  | iii  |

| Abstract         | iv   |

| Table Of Figures | x    |

# CHAPTER

| 1 I | NTR | ODU | JCTI | ON |

|-----|-----|-----|------|----|

|-----|-----|-----|------|----|

| 1.0 Introduction 1.1 Computer Architecture 1.2 The Von-Neumann Architecture 1.3 Von-Neumann Architectural Implementations 1.4 Fifth Generation Computer Research | 1-1<br>1-1<br>1-2<br>1-3<br>1-7 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 1.4.1 Japanese Activity                                                                                                                                          | 1-7                             |

| 1.4.2 The Alvey Programme                                                                                                                                        | 1-8                             |

| 1.5 Thesis Plan                                                                                                                                                  | 1-10                            |

| 1.6 Scope of Thesis                                                                                                                                              | 1-12                            |

| 2 THE FOUNDATIONS OF COMPUTER ARCHITECTURE                                                                                                                       |                                 |

| 2.0 Introduction                                                                                                                                                 | 2-1                             |

| 2.1 Why a new Generation                                                                                                                                         | 2-2                             |

| 2.2 The Semantic Gap                                                                                                                                             | 2-3                             |

| 2.2.1 The Operating System Semantic Gap                                                                                                                          | 2-4                             |

| 2.2.2 The Programming Environment Gap                                                                                                                            | 2-4                             |

| 2.2.3 The Storage Semantic Gap                                                                                                                                   | 2-5                             |

| 2.2.4 Consequences of the Sematic Gap                                                                                                                            | 2-5                             |

| 2.3 The Von-Neumann Architecture                                                                                                                                 | 2-6                             |

| 2.4 Parallel Systems                                                                                                                                             | 2-7                             |

| 2.5 Multi-Processor Systems and Attributes                                                                                                                       | 2-7                             |

| 2.5.1 Multi-Processor Computer Systems                                                                                                                           | 2-7                             |

| 2.5.2 Tightly Coupled Computer Systems                                                                                                                           | 2-9                             |

| 2.5.3 Loosely Coupled Computer Systems                                                                                                                           | 2-9                             |

| 2.6 Multi Processor Classifications                                                                                                                              | 2-10                            |

| 2.7 Bounded Parallel Systems                                                                                                                                     | 2-14                            |

| 2.8 Unbounded Parallel Systems                                                                                                                                   | 2-14                            |

| 2.9 Engineered Bounded Systems                                                                                                                                   | 2-15                            |

| 2.9.1 DEC VAX-11/782                                                                                                                                             | 2-15                            |

| 2.9.2 B5000                                                                                                                                                      | 2-21                            |

| 2.9.3 iAPX-432                                                                                                                                                   | 2-22                            |

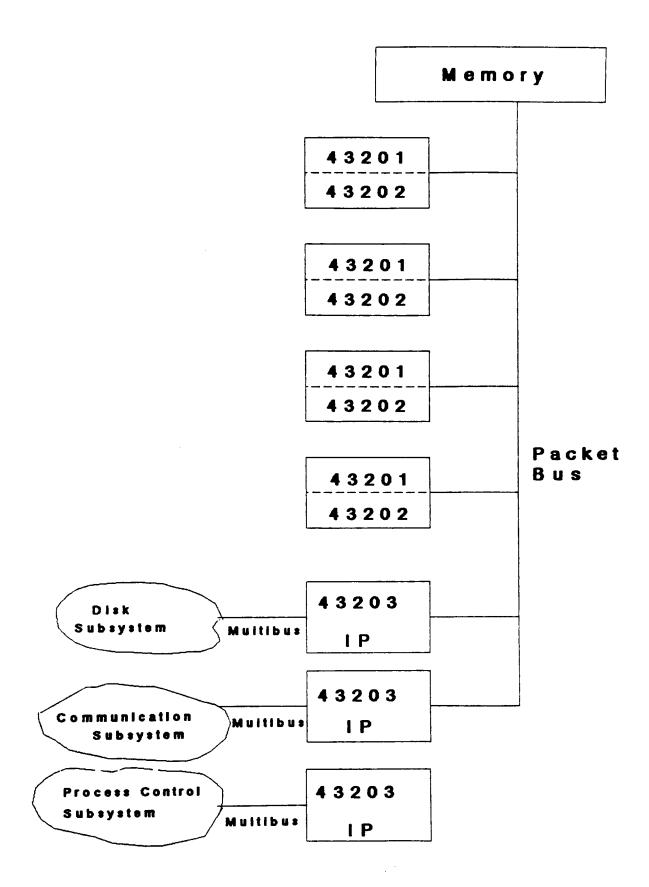

| 2.9.3.1 Overview of the iAPX432<br>2.9.3.2 Components - Configurations                            | 2-22<br>2-24                 |

|---------------------------------------------------------------------------------------------------|------------------------------|

| 2.9.4 Carnegie Mellon Machines                                                                    | 2-26                         |

| 2.9.4.1 C.mmp<br>2.9.4.1 The Hardware<br>2.9.4.3 The Software Base<br>2.9.4.4 Success and Failure | 2-26<br>2-27<br>2-29<br>2-29 |

| 2.10 Engineered Unbounded Systems                                                                 | 2-31                         |

| 2.10.1 Cm*<br>2.10.2 MPP<br>2.10.3 The Transputer                                                 | 2-31<br>2-35<br>2-37         |

| 2.11 Summary                                                                                      | 2-41                         |

| 3 FIFTH GENERATION NEEDS                                                                          |                              |

| <ul> <li>3.0 Introduction</li> <li>3.1 Background</li> <li>3.2 Fifth Generation Systems</li> <li>3.3 Application Areas</li> <li>3.4 Processor Architecture Exploiting VLSI</li> <li>3.5 Needs and Uses</li> </ul>                                                                                                                               | 3-1<br>3-1<br>3-2<br>3-3<br>3-3<br>3-4                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| <ul> <li>3.5.1 Industrial Automation</li> <li>3.5.2 Office Automation</li> <li>3.5.3 Science and Engineering</li> <li>3.5.4 Computer Hardware and Software</li> <li>3.5.5 Military</li> <li>3.5.6 Aerospace</li> <li>3.5.7 Retail and Service Industries</li> <li>3.5.8 Education</li> <li>3.5.9 Health Care</li> <li>3.5.10 Leisure</li> </ul> | 3-5<br>3-6<br>3-7<br>3-8<br>3-9<br>3-9<br>3-10<br>3-11<br>3-12<br>3-13 |

| 3.6 Involved Countries<br>3.7 Concerns and Goals                                                                                                                                                                                                                                                                                                | 3-13<br>3-14                                                           |

| 3.7.1 Japan and ICOT                                                                                                                                                                                                                                                                                                                            | 3-14                                                                   |

| 3.8 Designing the Next Generation                                                                                                                                                                                                                                                                                                               | 3-15                                                                   |

| 3.8.1 Exploiting Parallelism 3.8.2 VLSI: The Solution?                                                                                                                                                                                                                                                                                          | 3-16<br>3-16                                                           |

| 3.9 The Problems to be Encountered                                                                                                                                                                                                                                                                                                              | 3-16                                                                   |

| 3.9.1 Physical Limitations<br>3.9.2 Conceptual Limitations                                                                                                                                                                                                                                                                                      | 3-17<br>3-17                                                           |

| 3.10 Future Computer Architecture                                                                                                                                                                                                                                                                                                               | 3-18                                                                   |

# **4 BUS ARBITRATION CONCEPTS**

| 4.0 Background                         | 4-1  |

|----------------------------------------|------|

| 4.1 Introduction                       | 4-1  |

| 4.2 Current Computer Architecture      | 4-2  |

| 4.3 Bus Arbitration Objectives         | 4-4  |

| 4.4 Current Arbitration Techniques     | 4-5  |

| 4.5 Centralised Arbitration            | 4-6  |

| 4.5.1 Daisy Chain                      | 4-6  |

| 4.5.2 Polling                          | 4-8  |

| 4.5.3 Independant Requests             | 4-10 |

| 4.6 Distributed Arbitration            | 4-12 |

| 4.6.1 Distributed Daisy Chain          | 4-14 |

| 4.6.2 Distributed Polling              | 4-14 |

| 4.6.3 Distributed Independant Requests | 4-17 |

| 4.7 The Universal Arbiter              | 4-17 |

| 4.8 Summary                            | 4-24 |

# 5 THE GROUP PROCESSOR ARCHITECTURE

| 5.0  | Introduction                               | 5-1  |

|------|--------------------------------------------|------|

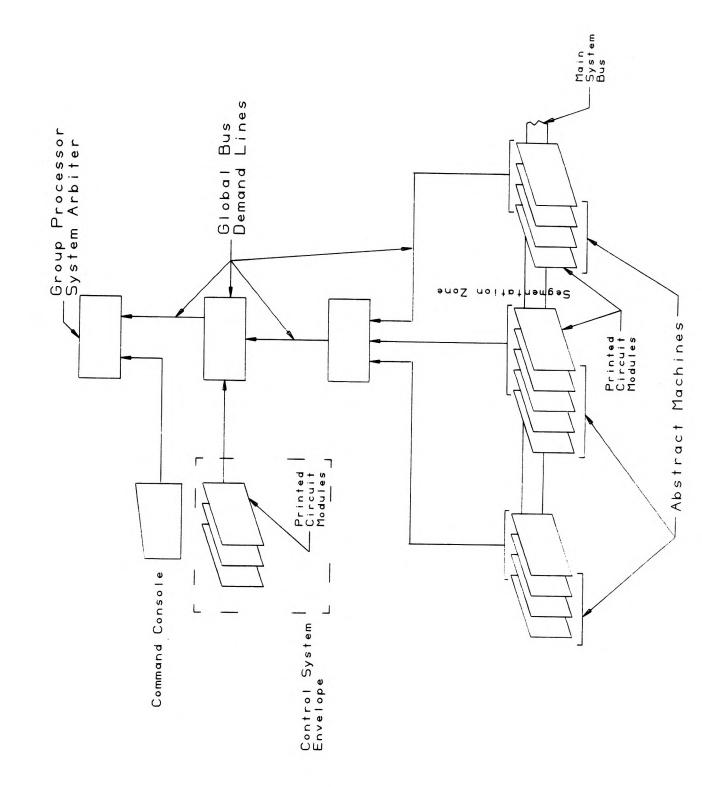

| 5.1  | High Level System Description              | 5-1  |

| 5.2  | Peripheral Interface Environment           | 5-3  |

| 5.3  | Group Processor Environment                | 5-6  |

| 5.4  | Module External Input Output               | 5-6  |

| 5.5  | Logical Bus Structure                      | 5-8  |

| 5.6  | Bus Structures                             | 5-12 |

| 5.7  | Inter-Module Bus Structure                 | 5-15 |

| 5.8  | Single Use Environment                     | 5~17 |

| 5.9  | Multi User Environment                     | 5-17 |

| 5.10 | The Group Processor Operating System       | 5-19 |

| 5.11 | Distributed Control                        | 5-20 |

| 5.12 | High Level Operating System Representation | 5-23 |

| 5.13 | Group Processor System Summary             | 5-23 |

|      |                                            |      |

# 6 THE SIMULATION ENVIRONMENT

| 6.0 Introduction                             | 6-1 |

|----------------------------------------------|-----|

| 6.1 The Modelling Approach                   | 6-1 |

| 6.1.1 Synthetic Benchmarks                   | 6-2 |

| 6.1.2 Live Benchmarks                        | 6-2 |

| 6.1.3 Simulation                             | 6-3 |

| 6.1.4 Mathematical Modelling                 | 6-3 |

| 6.2 The Case For Simulation                  | 6-3 |

| 6.3 Computer Structure, Resource Application | 6-4 |

| 6.3.1 What is a resource?                    | 6-5 |

| 6.3.2 Definitions                            | 6-5 |

|   | 6.4 \$         | Simulation Architecture                                                                                                                                                                                                                                                                                                                                                                                                             | 6-6                                                                  |

|---|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|   | e              | 5.4.1 System Architecture Components                                                                                                                                                                                                                                                                                                                                                                                                | 6-6                                                                  |

|   |                | 6.4.1.1 Buses<br>6.4.1.2 Bus Arbiters<br>6.4.1.3 Cells<br>6.4.1.4 Modules                                                                                                                                                                                                                                                                                                                                                           | 6-7<br>6-7<br>6-7<br>6-7                                             |

|   |                | 5.4.2 The Group Processor<br>5.4.3 Bus Interconnection Schemes                                                                                                                                                                                                                                                                                                                                                                      | 6-7<br>6-8                                                           |

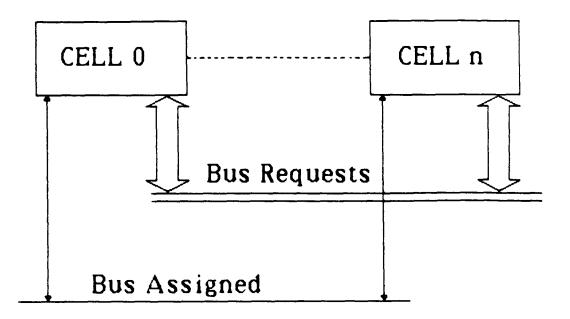

|   | 6.6 H<br>6.7 Z | Bus Arbitration<br>Bus Requests<br>Actioning Bus Requests<br>The Simulator Program                                                                                                                                                                                                                                                                                                                                                  | 6-8<br>6-9<br>6-9<br>6-9                                             |

|   | (              | 6.8.1 System Parameters<br>6.8.2 Major Parameters<br>6.8.3 Tuning Parameters                                                                                                                                                                                                                                                                                                                                                        | 6-10<br>6-10<br>6-10                                                 |

|   | 6.9            | The Simulation Environment                                                                                                                                                                                                                                                                                                                                                                                                          | 6-11                                                                 |

|   |                | 6.9.1 The Job Scheduler<br>6.9.2 The Job Server<br>6.9.3 System Loading                                                                                                                                                                                                                                                                                                                                                             | 6-11<br>6-13<br>6-14                                                 |

|   | 6.10           | Range of Results                                                                                                                                                                                                                                                                                                                                                                                                                    | 6-14                                                                 |

|   |                | <ul> <li>6.10.1 Variation of Physical Constants</li> <li>6.10.2 Variation of Cell Numbers</li> <li>6.10.3 Variation of Module Numbers</li> <li>6.10.4 Variation of Inter-module bus</li> <li>6.10.5 Variation of Intra-module bus</li> <li>6.10.6 Variation of Soft Constants</li> <li>6.10.7 Bus Request Rate</li> <li>6.10.8 Ratio of Jobs</li> <li>6.10.9 Time Required as Bus Master</li> <li>6.10.10 Message Length</li> </ul> | 6-14<br>6-15<br>6-15<br>6-15<br>6-16<br>6-16<br>6-16<br>6-16<br>6-17 |

|   | 6.12           | Simulation Goals<br>Limiting Factors<br>Conclusion                                                                                                                                                                                                                                                                                                                                                                                  | 6-17<br>6-17<br>6-18                                                 |

| 7 | RESULTS        | AND IMPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

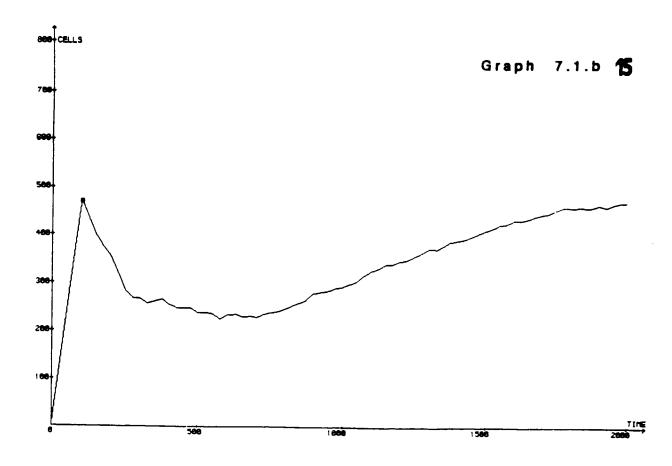

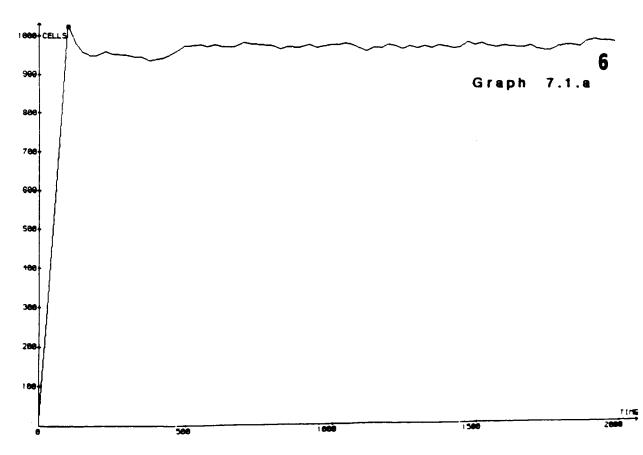

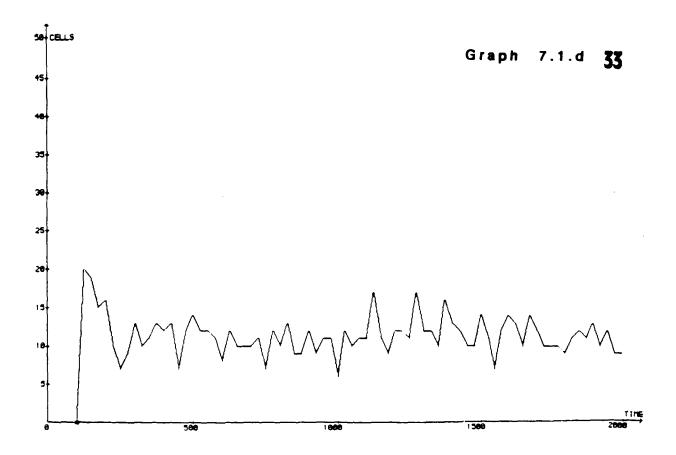

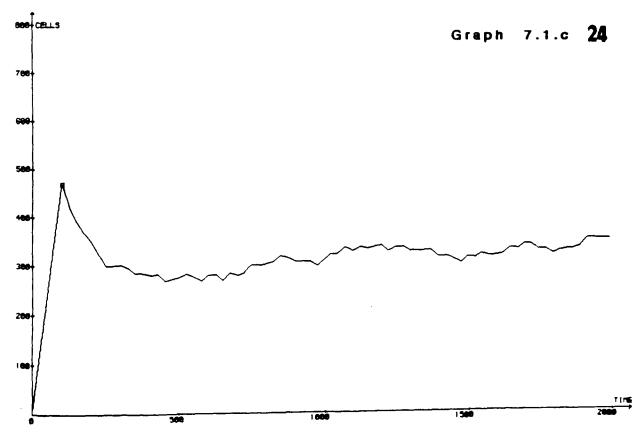

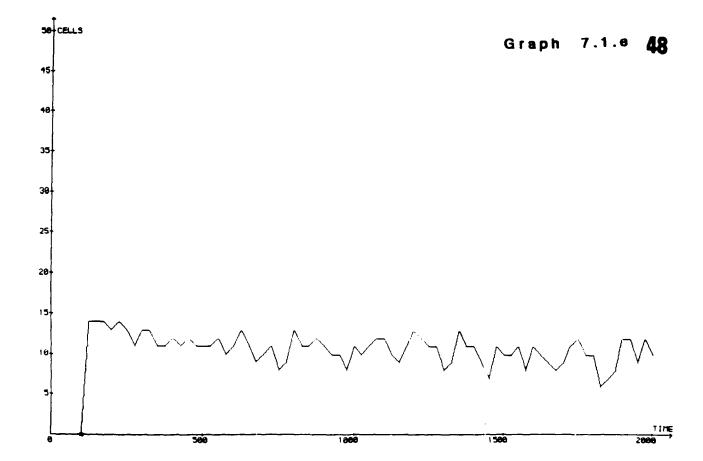

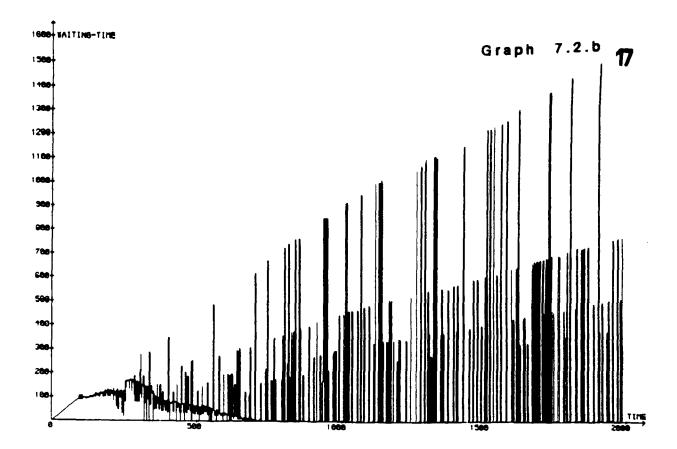

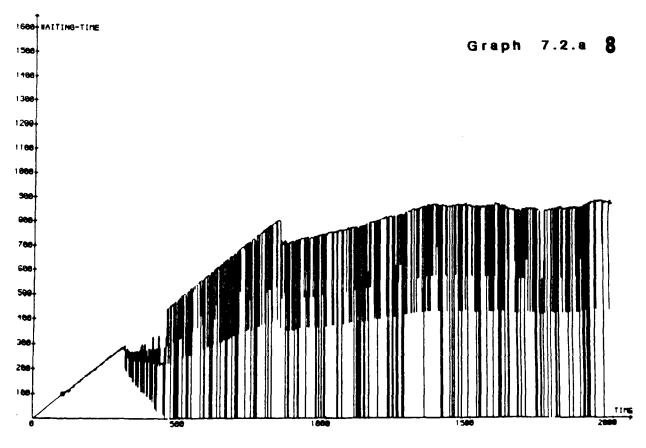

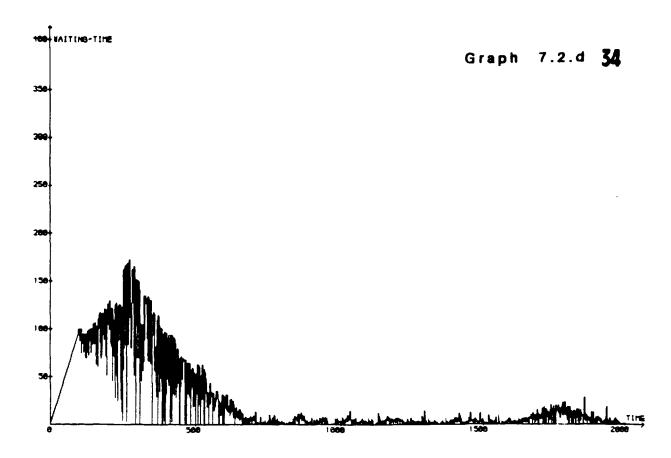

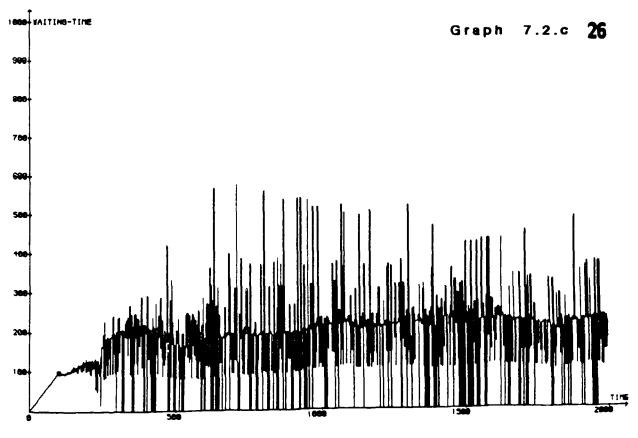

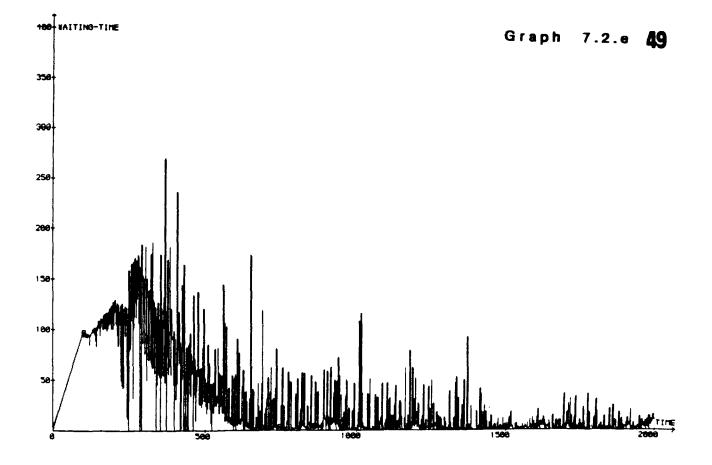

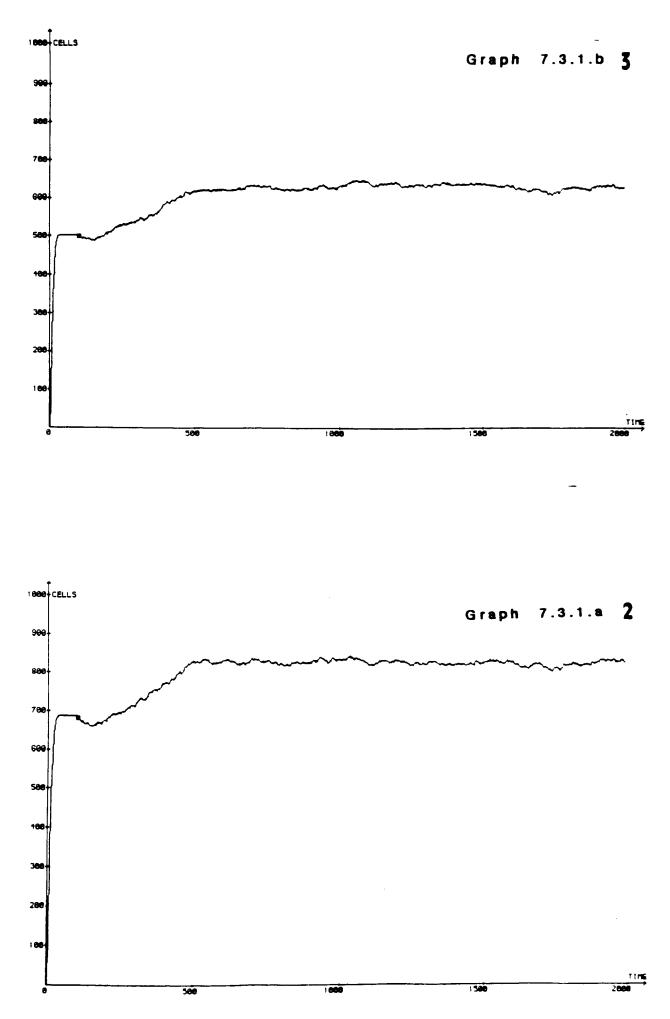

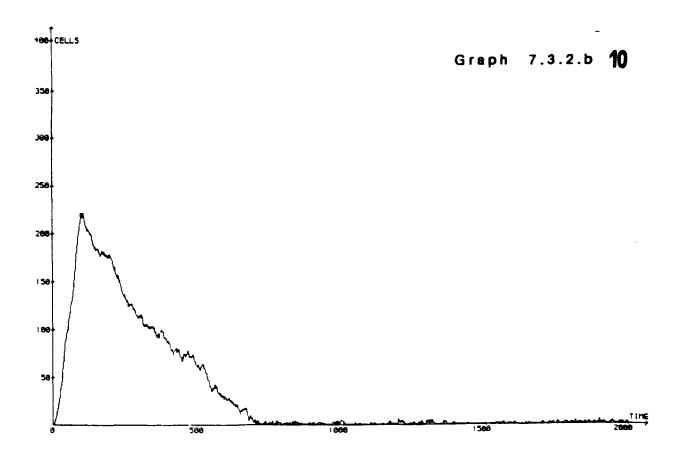

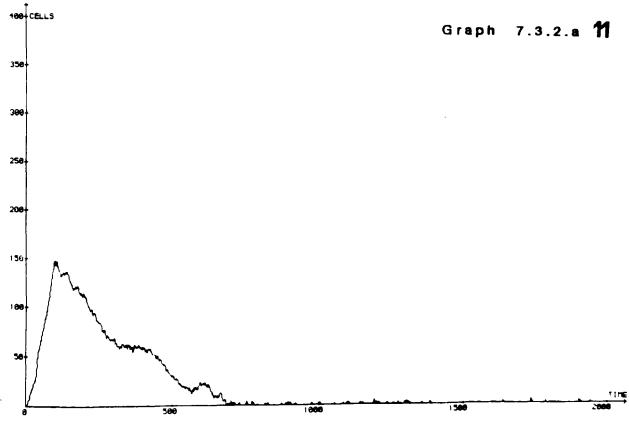

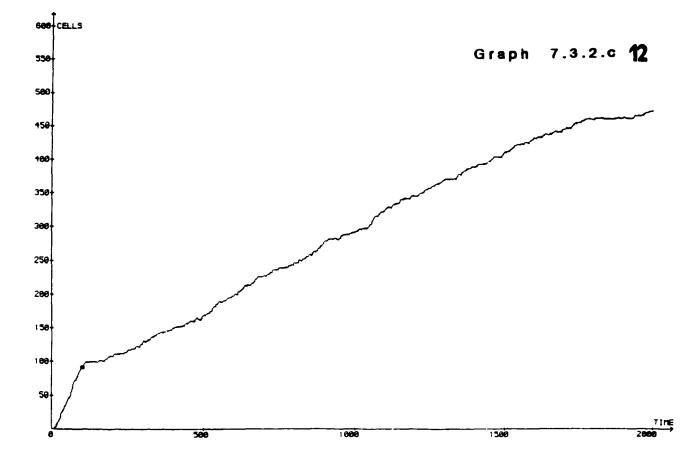

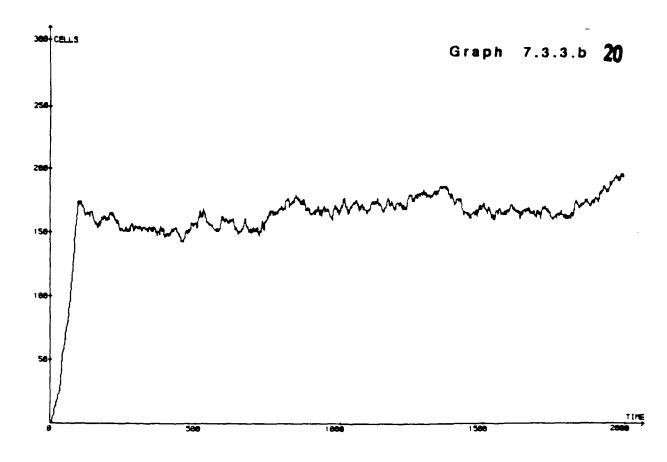

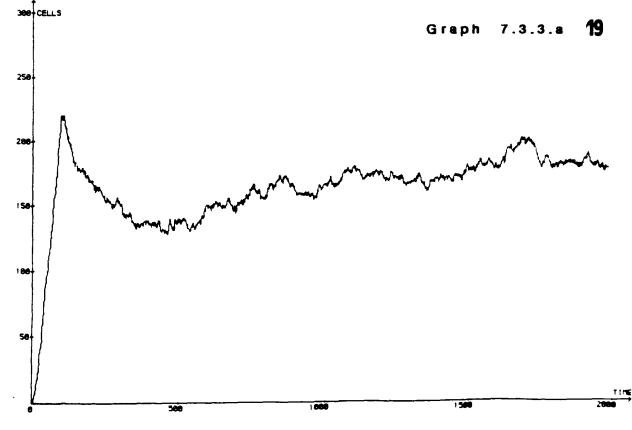

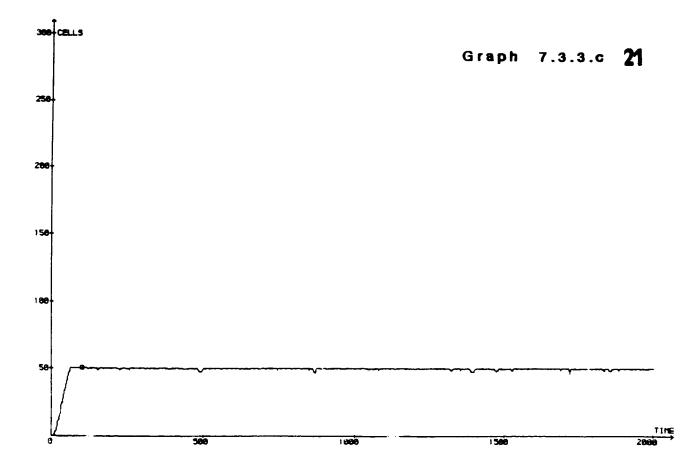

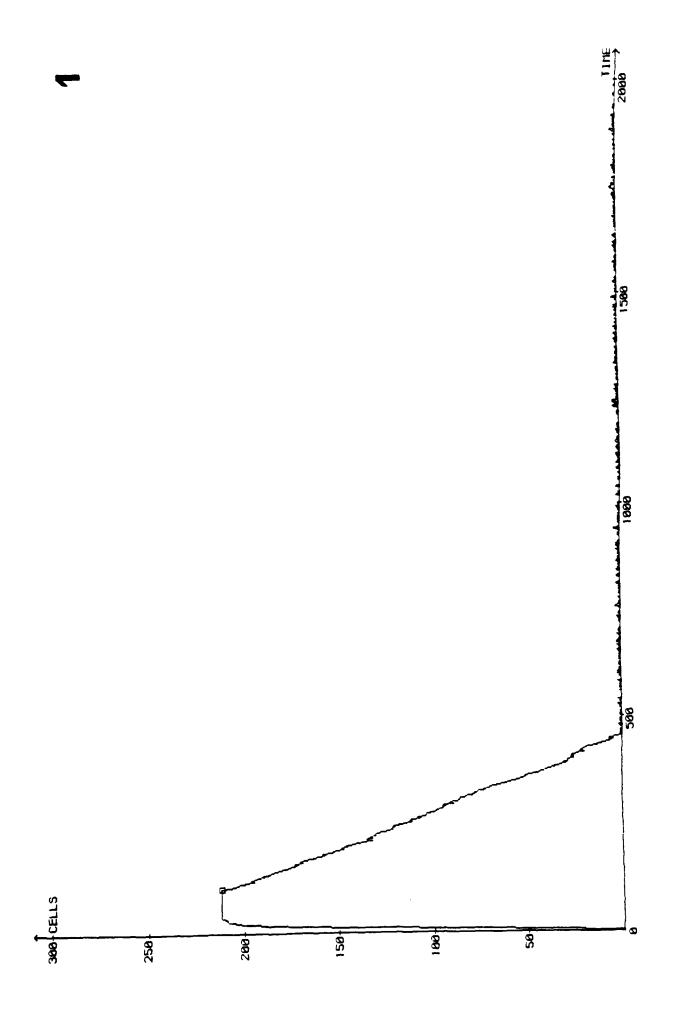

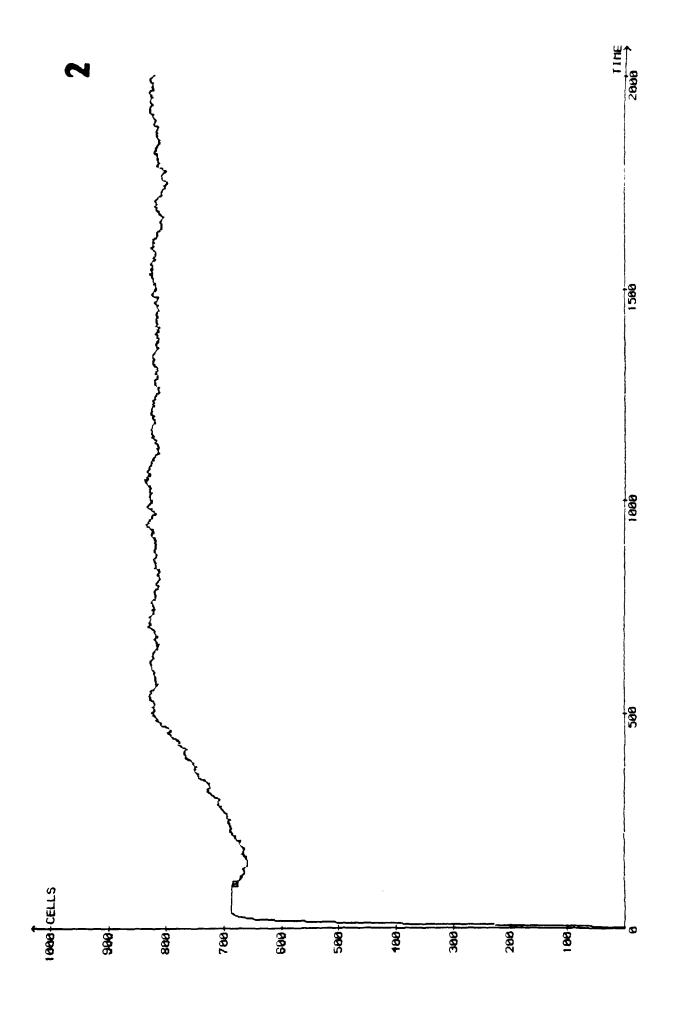

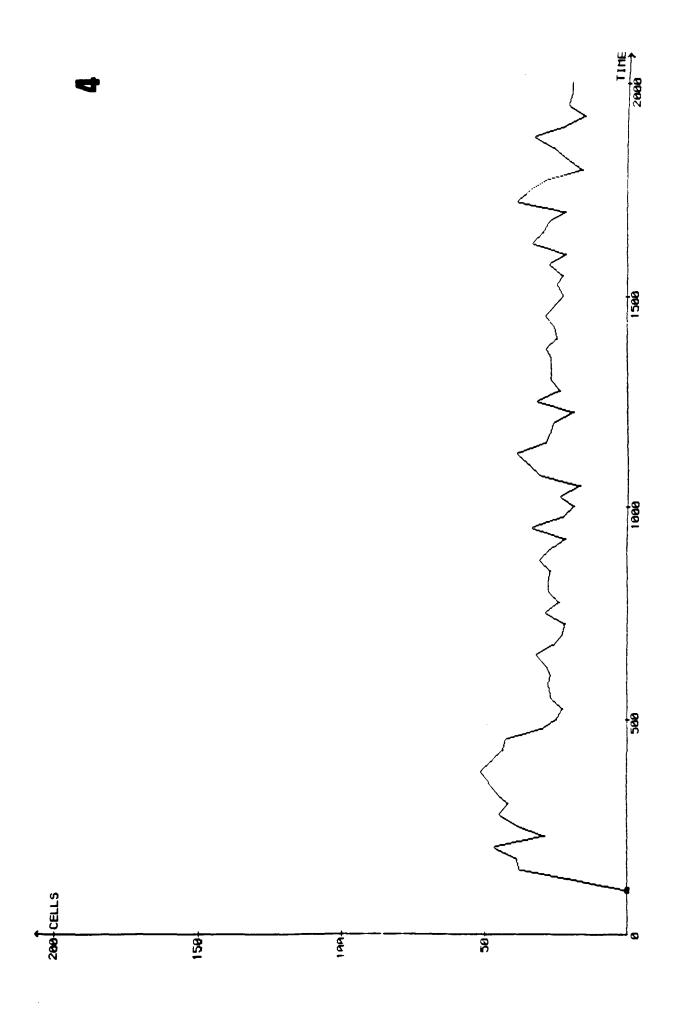

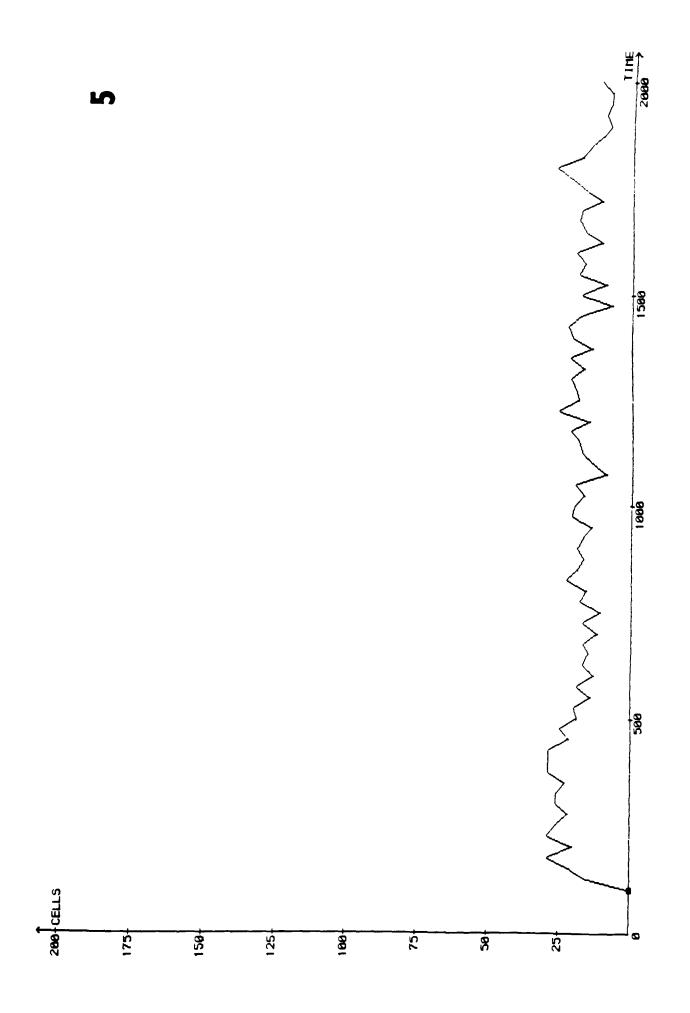

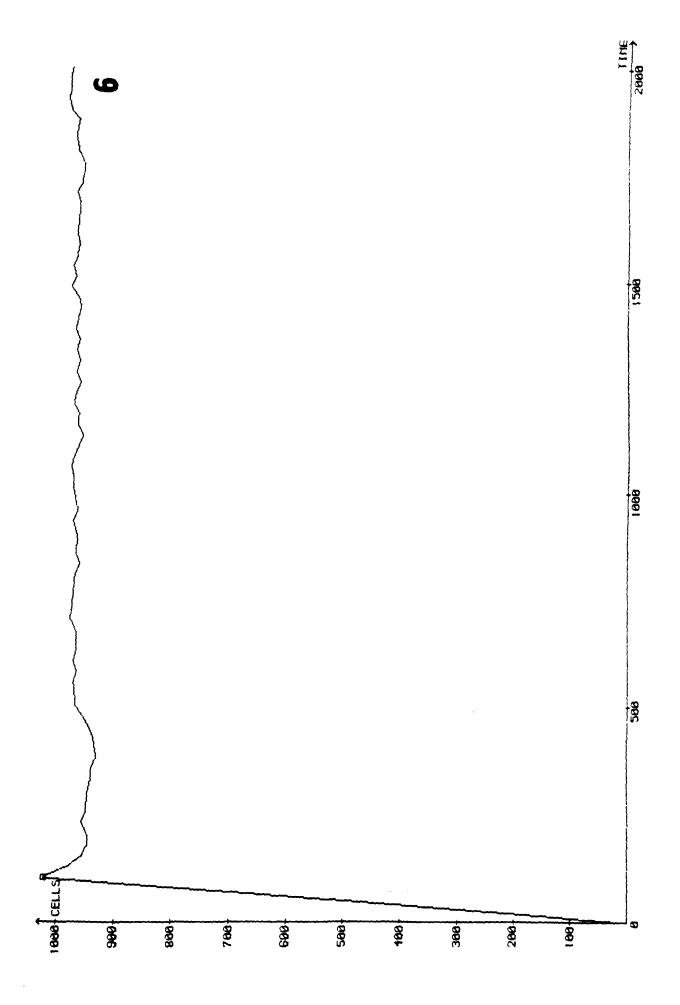

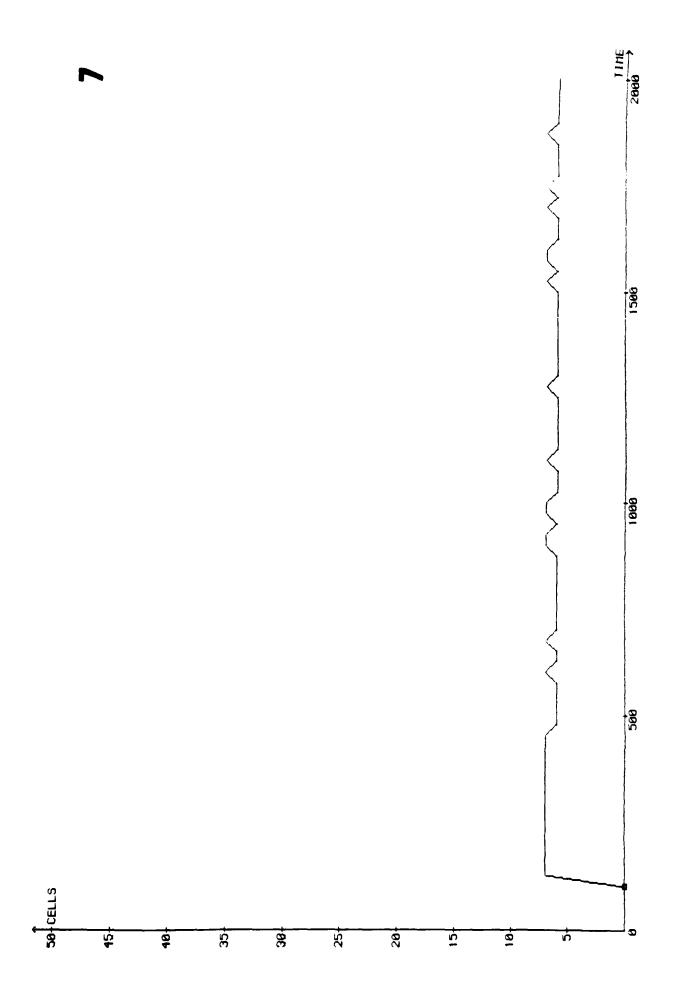

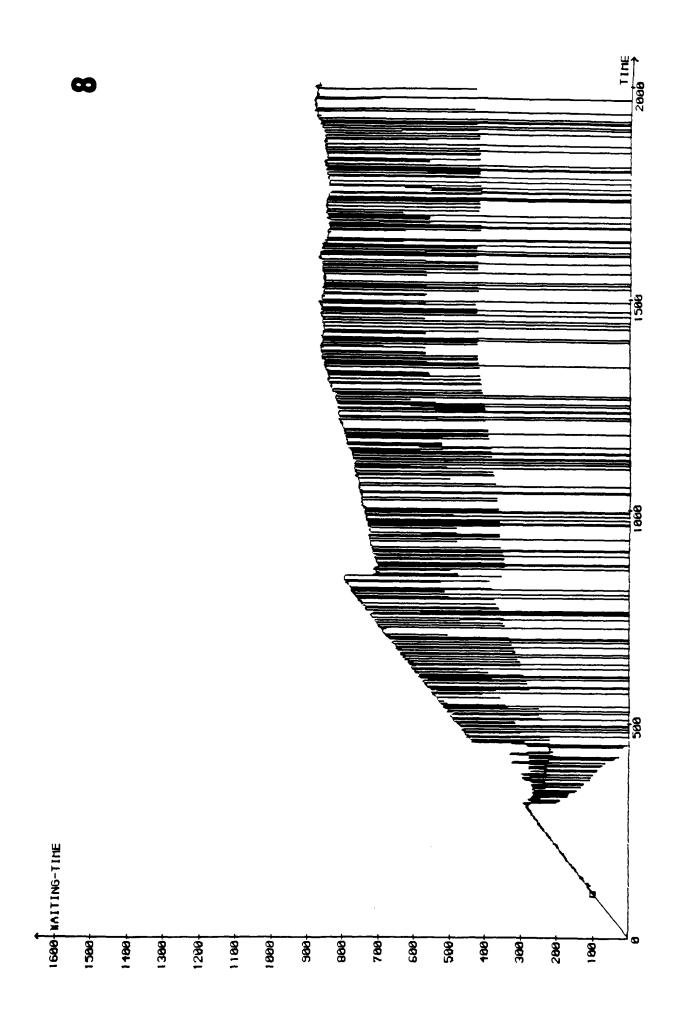

#### 7-1 7.0 Introduction 7.1 Table of Results 7-2 7.2 Basic Group Processor System 7-9 7.3 Extended Group Processor System 7-11 7.4 Operating System Constraints 7-12 7.5 Off-loading Factor 7.6 Segmemted Input/Output 7-15 7-16 7-17 7.7 Dedicated Systems 7-18 7.8 Closer Analysis

| 7.8.1 Effects of Bus Contention | 7-18 |

|---------------------------------|------|

| 7.8.2 Inter-Cell Communication  | 7-22 |

| 7.9 Software Considerations     | 7-28 |

| 7.10 Conclusions                | 7-35 |

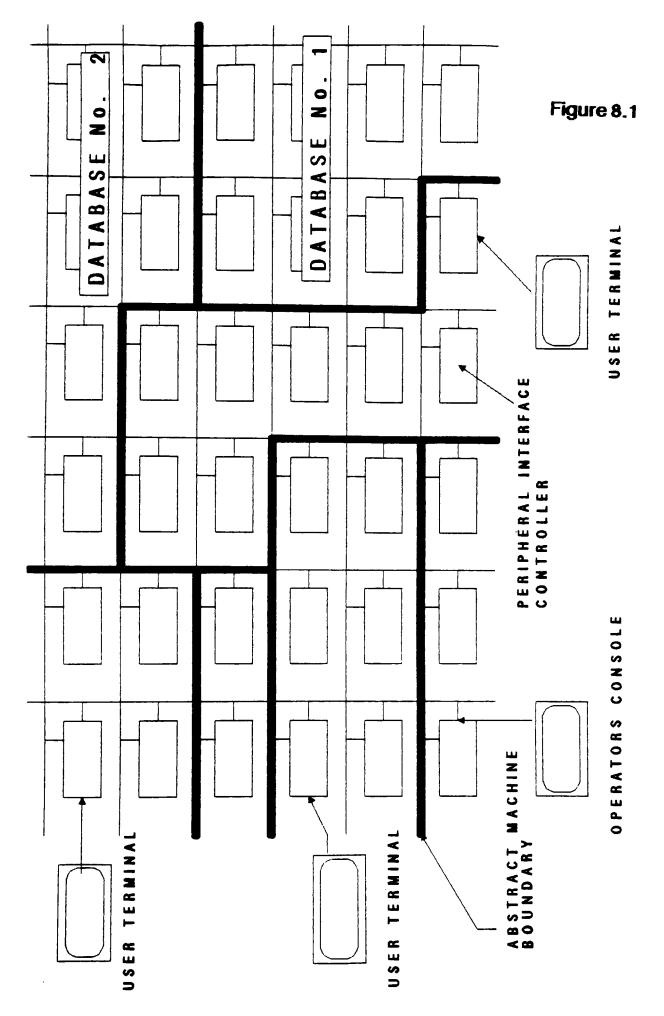

# 8 GROUP PROCESSOR ARCHITECTURAL ENHANCEMENTS

| 8.0 Introduction                    | 8-1  |

|-------------------------------------|------|

| 8.1 Group Processor System Problems | 8-1  |

| 8.2 T.E.S.S. Outline                | 8-2  |

| 8.3 T.E.S.S. Objectives             | 8-4  |

| 8.4 T.E.S.S. Operations             | 8-8  |

| 8.5 Module/Channel Interface        | 8-12 |

| 8.6 Crossbar Operation              | 8-14 |

| 8.7 Bus Arbitration                 | 8-15 |

| 8.8 Summary                         | 8-18 |

| _                                   |      |

# 9 CONCLUSION AND FURTHER RESEARCH

| 9.0 Introduction               | 9-1 |

|--------------------------------|-----|

| 9.1 Research Initatives        | 9-  |

| 9.2 Computer Architecture      | 9-  |

| 9.3 The Group Processor System | 9-  |

| 9.4 T.E.S.S.                   | 9-  |

| 9.5 Future Research            | 9-  |

| 9.6 Summary                    | 9-  |

| APPENDIX | ONE: | Simulator | Graphica | 1 Output | A1-1 |

|----------|------|-----------|----------|----------|------|

| APPENDIX | TWO: | Simulator | Program  | Listing  | A2-1 |

| Figure No.                                                                  | Figure Title                                                                                                                                                                                                                                                                                                       | Page No.                                                                                              |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 2.1a                                                                        | Single User Global Memory                                                                                                                                                                                                                                                                                          | 2-8                                                                                                   |

| 2.1b                                                                        | Single user Global + Local Memory                                                                                                                                                                                                                                                                                  | 2-8                                                                                                   |

| 2.2                                                                         | Single user Loosely Coupled                                                                                                                                                                                                                                                                                        | 2-11                                                                                                  |

| 2.3                                                                         | Multi-user Multi-processor                                                                                                                                                                                                                                                                                         | 2-12                                                                                                  |

| 2.4                                                                         | VAX-11/782 Connections                                                                                                                                                                                                                                                                                             | 2-16                                                                                                  |

| 2.5                                                                         | VAX Architectures                                                                                                                                                                                                                                                                                                  | 2-18                                                                                                  |

| 2.6                                                                         | Dual VAX Configuration                                                                                                                                                                                                                                                                                             | 2-20                                                                                                  |

| 2.7                                                                         | 4 Processor iAPX-432 Configuration                                                                                                                                                                                                                                                                                 | 2-25                                                                                                  |

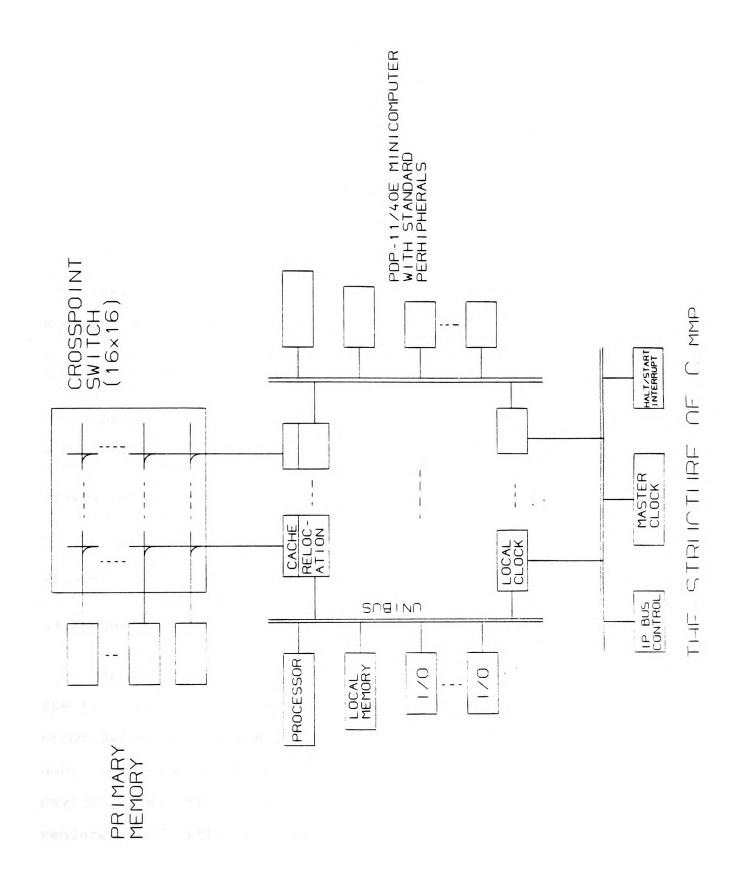

| 2.8                                                                         | C.mmp                                                                                                                                                                                                                                                                                                              | 2-28                                                                                                  |

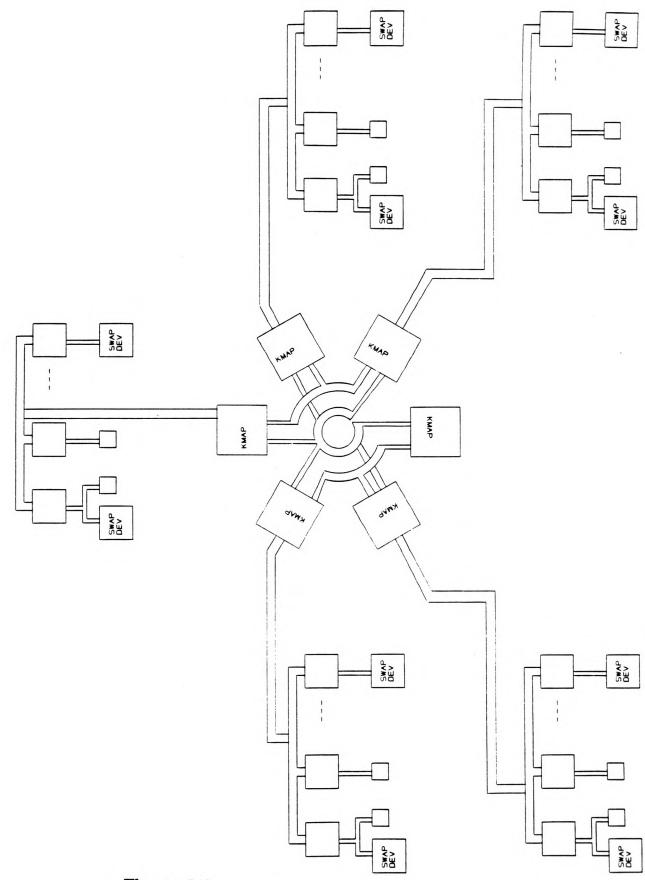

| 2.9                                                                         | 5 Cluster Cm*                                                                                                                                                                                                                                                                                                      | 2-32                                                                                                  |

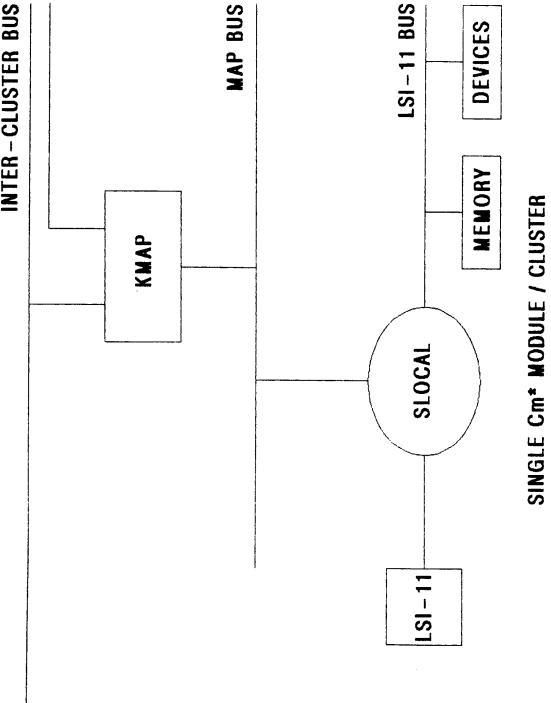

| 2.10                                                                        | Cm* individual cluster                                                                                                                                                                                                                                                                                             | 2-33                                                                                                  |

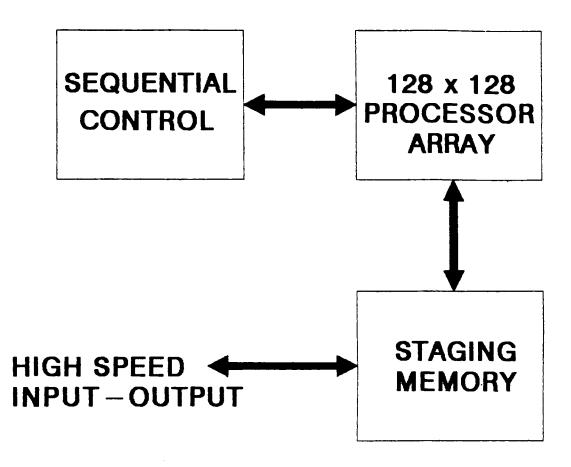

| 2.11                                                                        | MPP                                                                                                                                                                                                                                                                                                                | 2-36                                                                                                  |

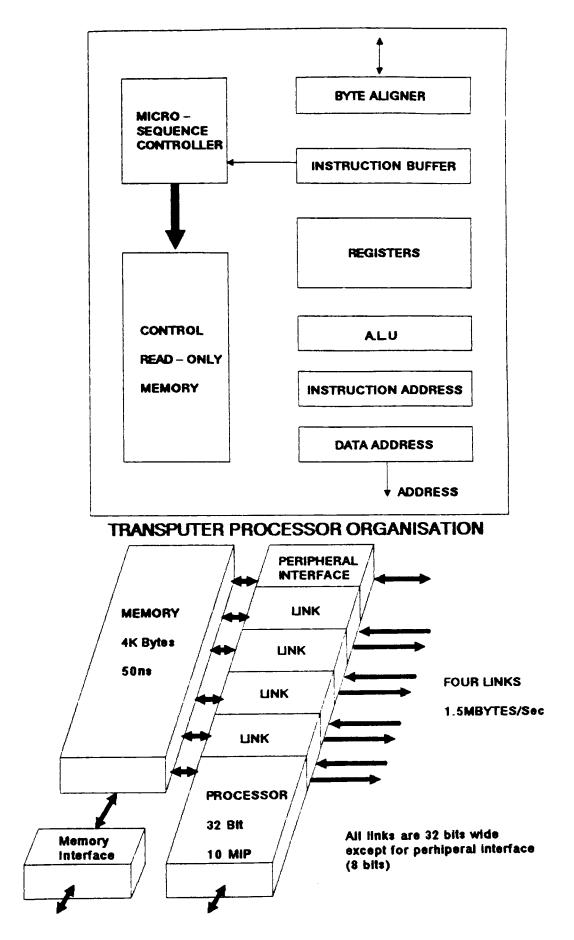

| 2.12                                                                        | The Transputer                                                                                                                                                                                                                                                                                                     | 2-39                                                                                                  |

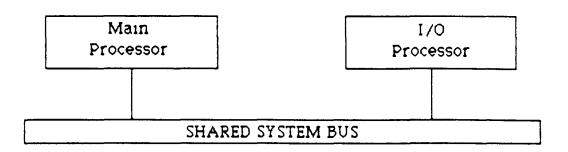

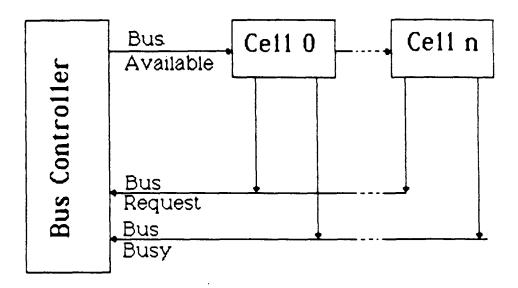

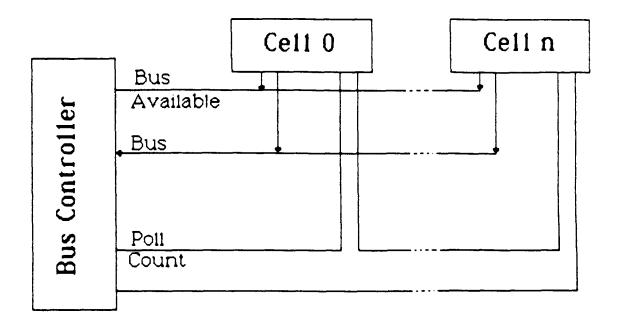

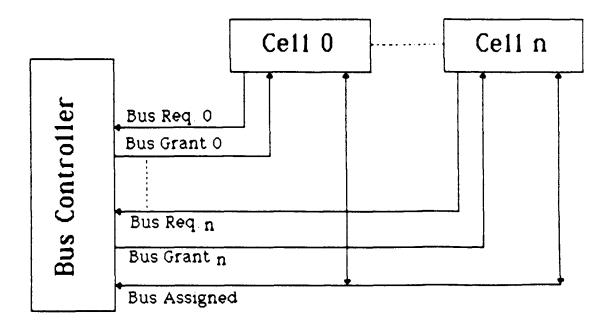

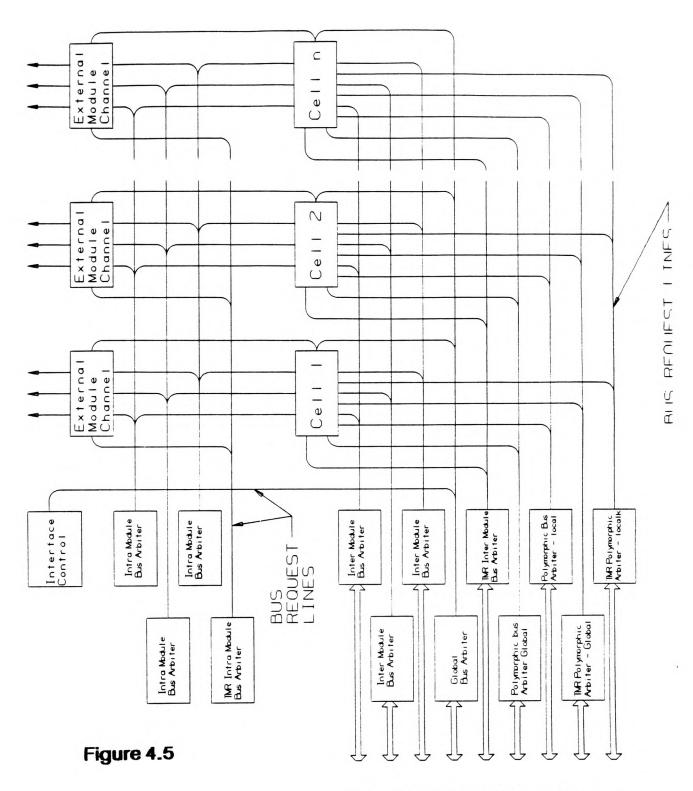

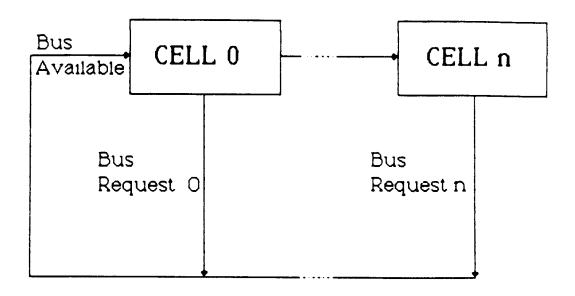

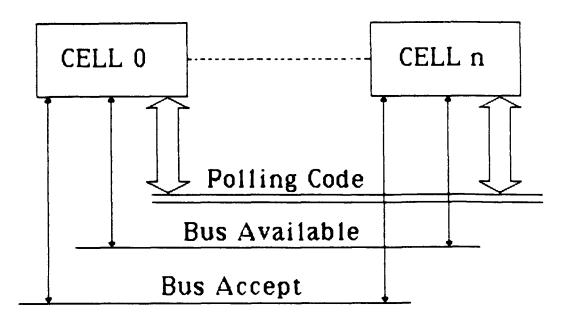

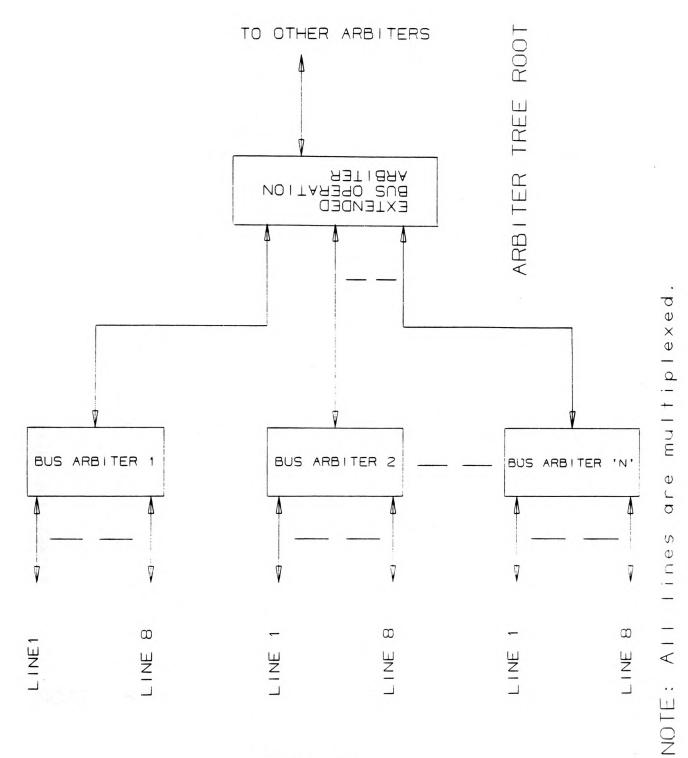

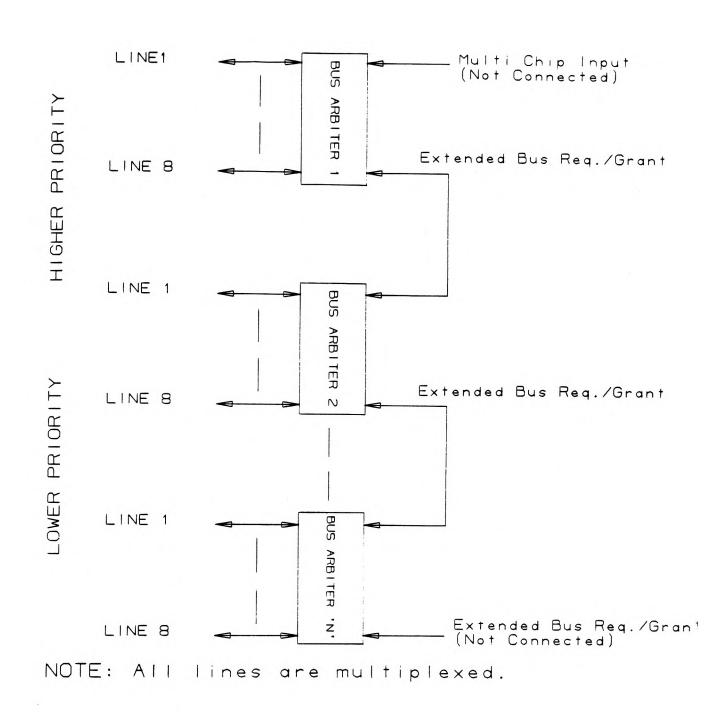

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11 | Simple Parallel System<br>Centralised Daisy Chain<br>Centralised Polling<br>Centralised Independant Requests<br>Bus Arbiter Types<br>Distributed Daisy Chain<br>Distributed Polling<br>Distributed Independant Requests<br>Hierarchical Arbitration<br>Linear Priority Arbitration<br>Fifth Generation Arbitration | $\begin{array}{r} 4-3\\ 4-7\\ 4-9\\ 4-11\\ 4-13\\ 4-15\\ 4-16\\ 4-18\\ 4-20\\ 4-21\\ 4-23\end{array}$ |

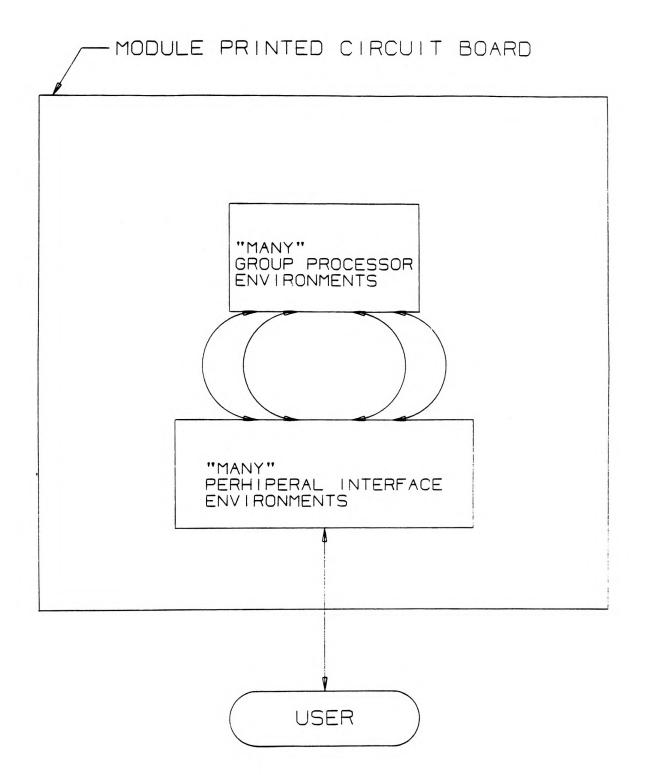

| 5.1                                                                         | Functional Composition of G.P.S                                                                                                                                                                                                                                                                                    | 5-2                                                                                                   |

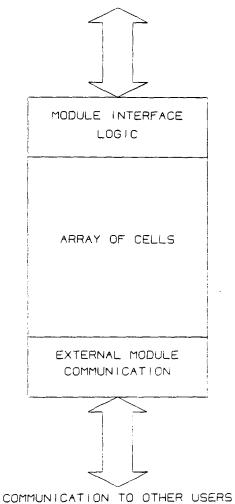

| 5.2                                                                         | Group Processor Module                                                                                                                                                                                                                                                                                             | 5-4                                                                                                   |

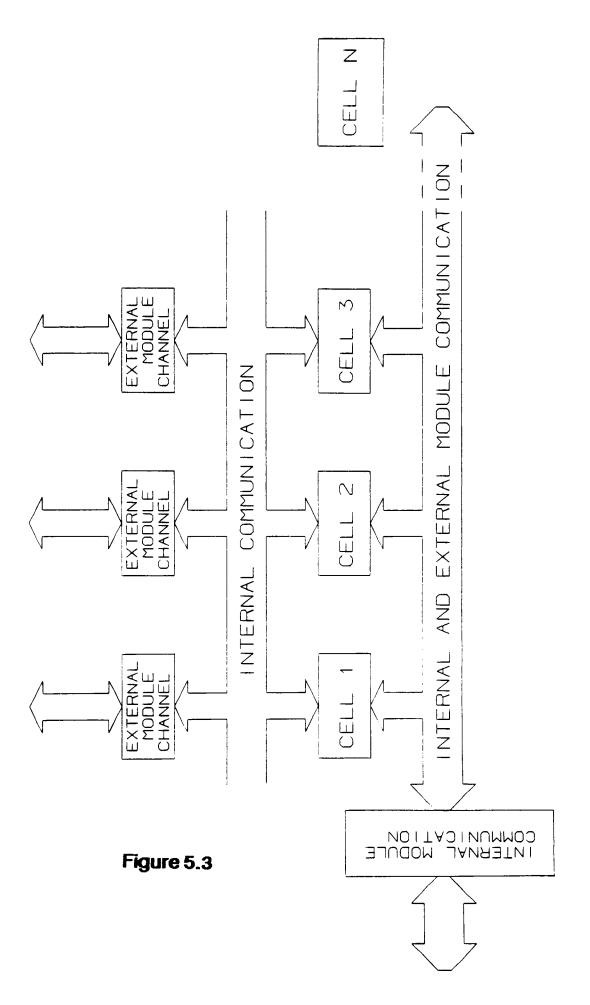

| 5.3                                                                         | Module Component Architecture                                                                                                                                                                                                                                                                                      | 5-5                                                                                                   |

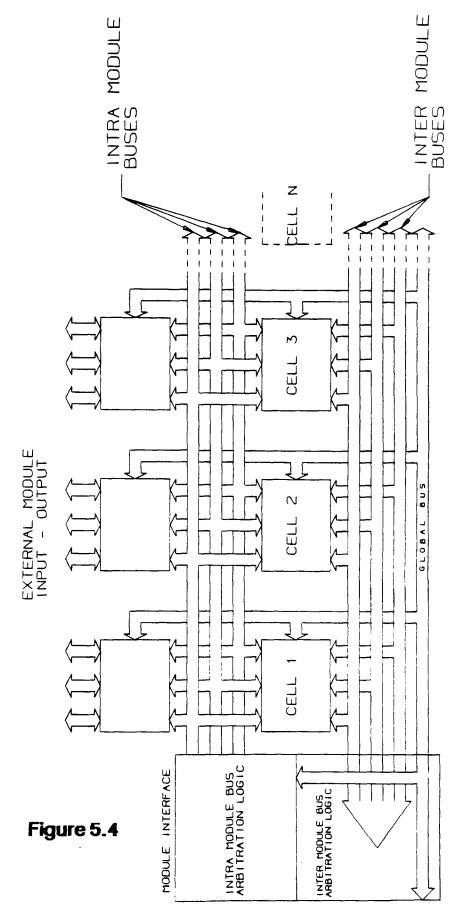

| 5.4                                                                         | Inter-module Bus Structure                                                                                                                                                                                                                                                                                         | 5-7                                                                                                   |

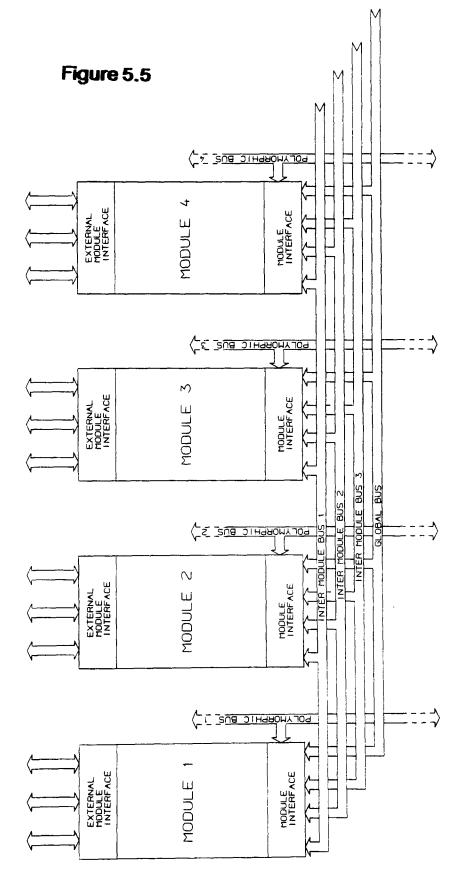

| 5.5                                                                         | Data Bus Architecture                                                                                                                                                                                                                                                                                              | 5-9                                                                                                   |

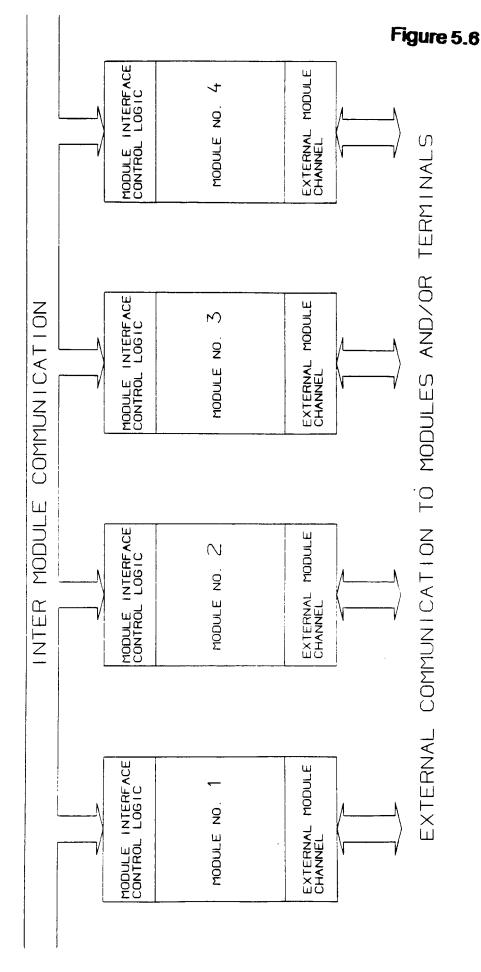

| 5.6                                                                         | Module Coupling Architecture                                                                                                                                                                                                                                                                                       | 5-11                                                                                                  |

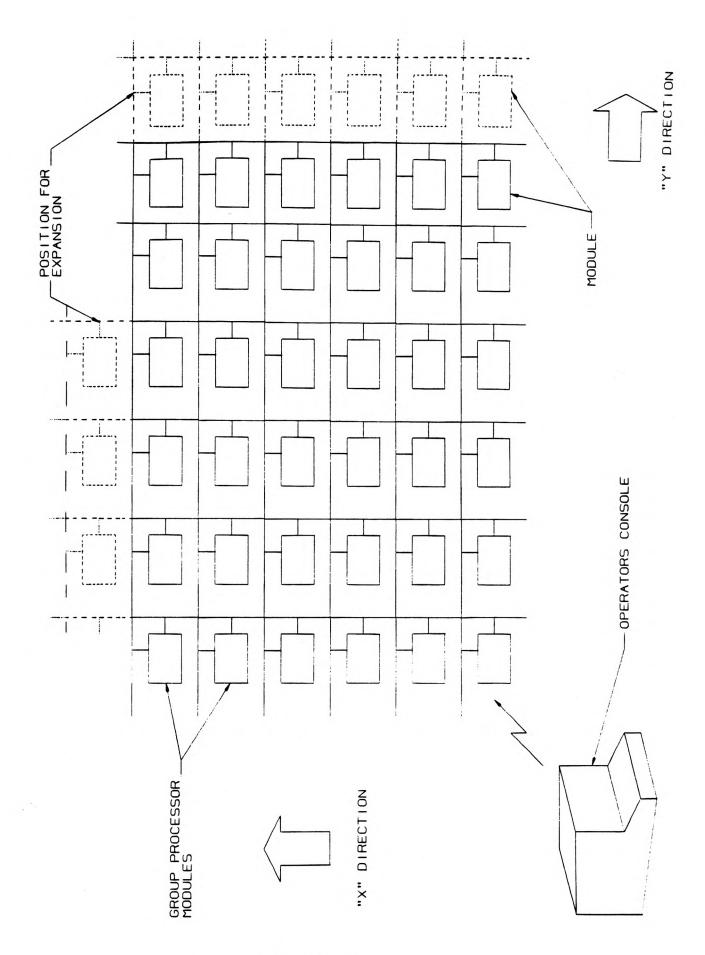

| 5.7                                                                         | Single User System                                                                                                                                                                                                                                                                                                 | 5-13                                                                                                  |

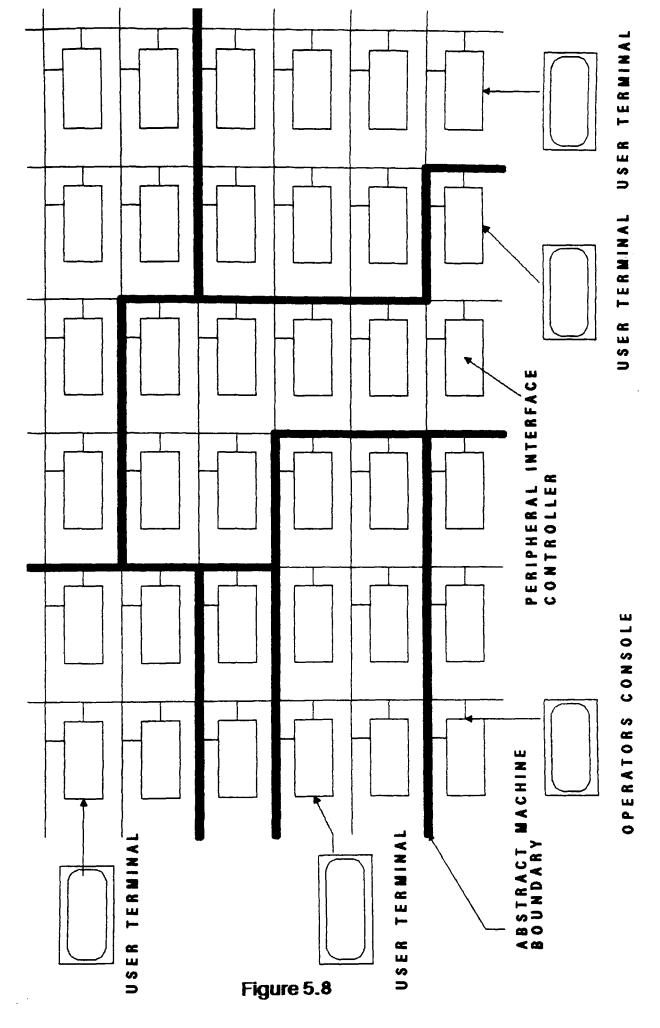

| 5.8                                                                         | Multi User System                                                                                                                                                                                                                                                                                                  | 5-14                                                                                                  |

| 5.9                                                                         | Multi User Environment                                                                                                                                                                                                                                                                                             | 5-18                                                                                                  |

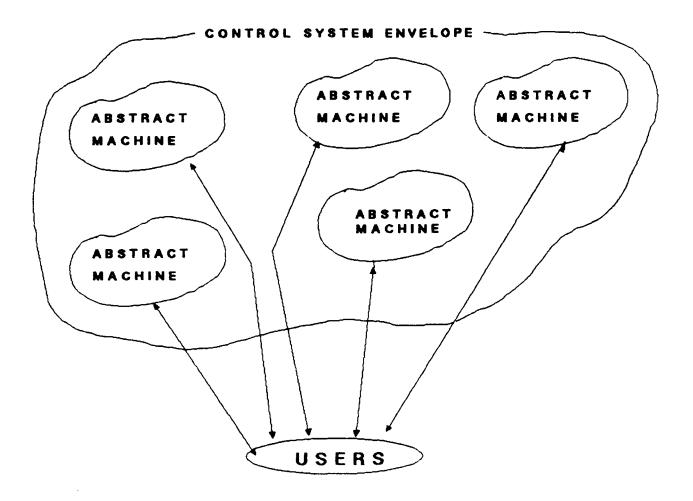

| 5.10                                                                        | Distributed Operating System                                                                                                                                                                                                                                                                                       | 5-22                                                                                                  |

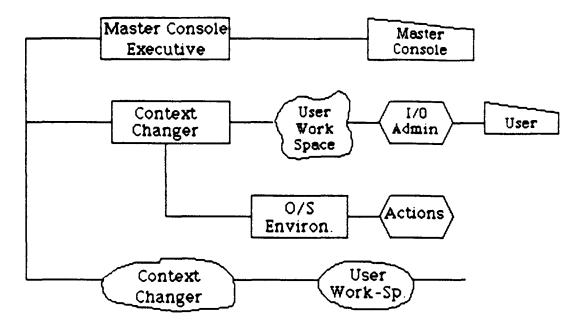

| 6.1                                                                         | Simulator Schematic                                                                                                                                                                                                                                                                                                | 6-12                                                                                                  |

| 7.1                                                                         | Table of Results 1                                                                                                                                                                                                                                                                                                 | 7-4                                                                                                   |

| 7.2                                                                         | Table of Results 2                                                                                                                                                                                                                                                                                                 | 7-5                                                                                                   |

| 7.3                                                                         | Table of Results 3                                                                                                                                                                                                                                                                                                 | 7-6                                                                                                   |

| 7.4                                                                         | Table of Results 4                                                                                                                                                                                                                                                                                                 | 7-7                                                                                                   |

| 7.5                                                                         | Table of Results 5                                                                                                                                                                                                                                                                                                 | 7-8                                                                                                   |

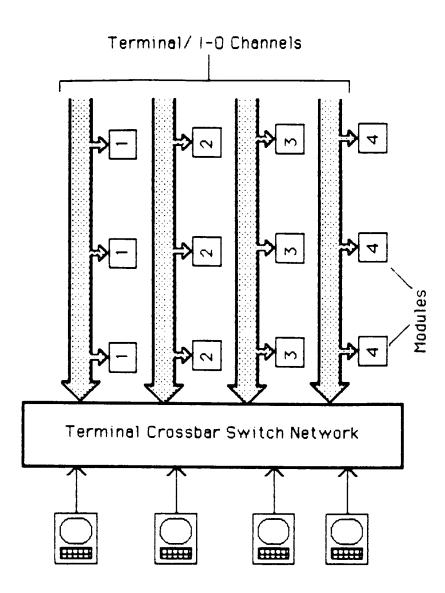

| 8.1                                                                         | Multi User System                                                                                                                                                                                                                                                                                                  | 8-3                                                                                                   |

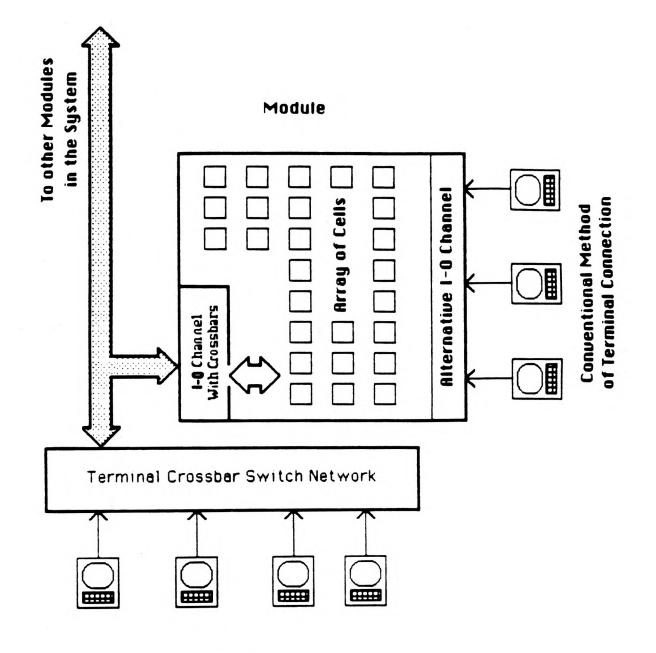

| 8.2                                                                         | T.E.S.S Architecture Outline                                                                                                                                                                                                                                                                                       | 8-5                                                                                                   |

| 8.3                                                                         | Terminal Alternatives                                                                                                                                                                                                                                                                                              | 8-7                                                                                                   |

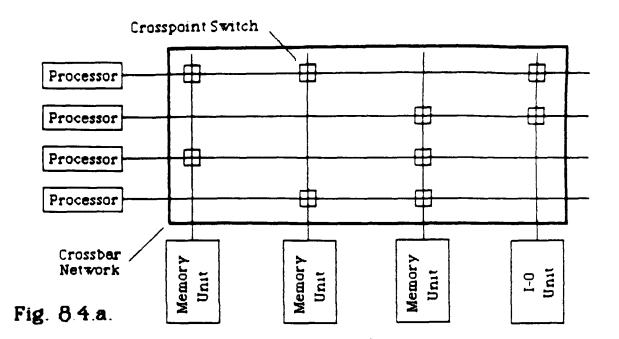

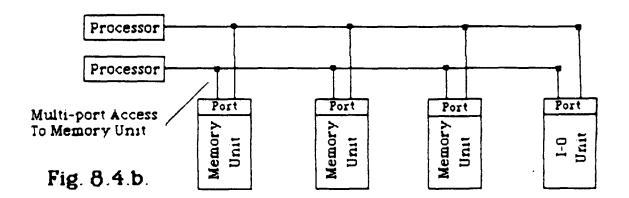

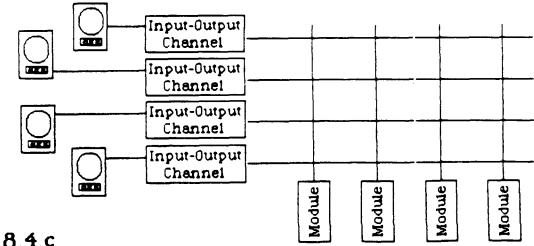

| 8.4                                                                         | Ported Memory Concepts                                                                                                                                                                                                                                                                                             | 8-9                                                                                                   |

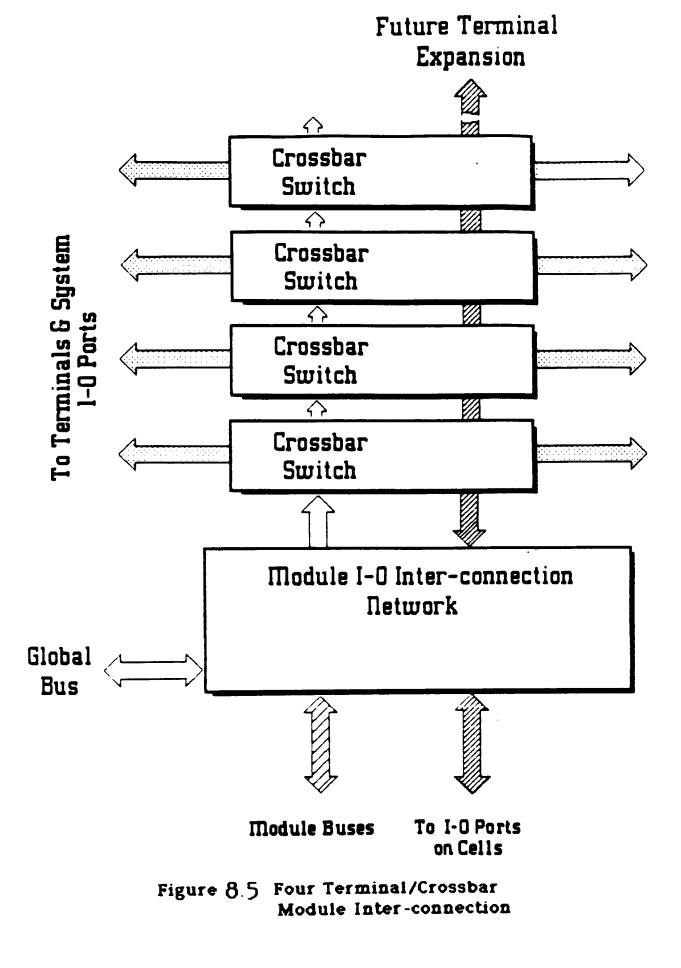

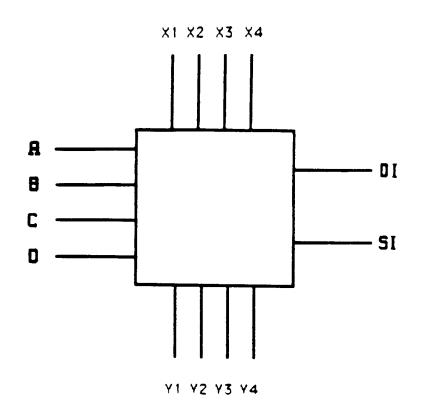

| 8.5                                                                         | Four Terminal/Crossbar Module                                                                                                                                                                                                                                                                                      | 8-11                                                                                                  |

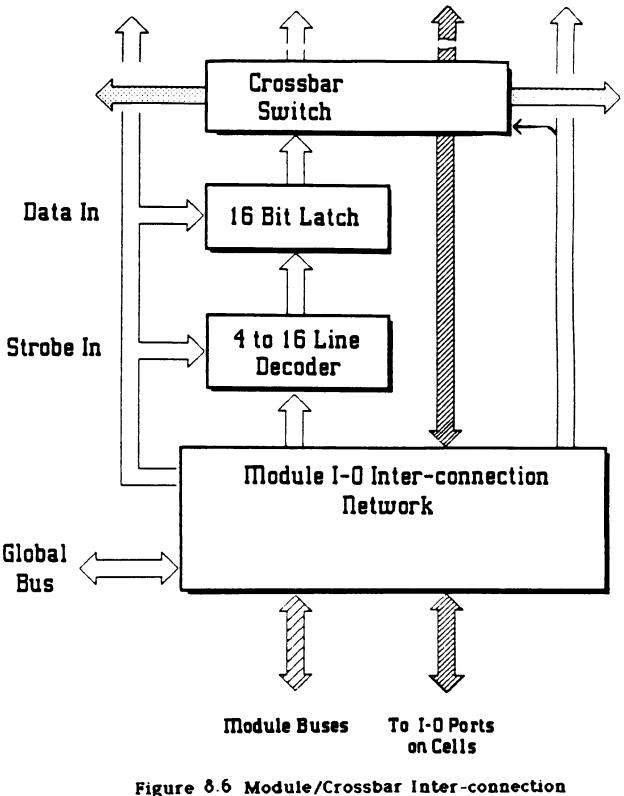

| 8.6                                                                         | Interconnection<br>Module/Crossbar Interconnection<br>Network                                                                                                                                                                                                                                                      | 8-13                                                                                                  |

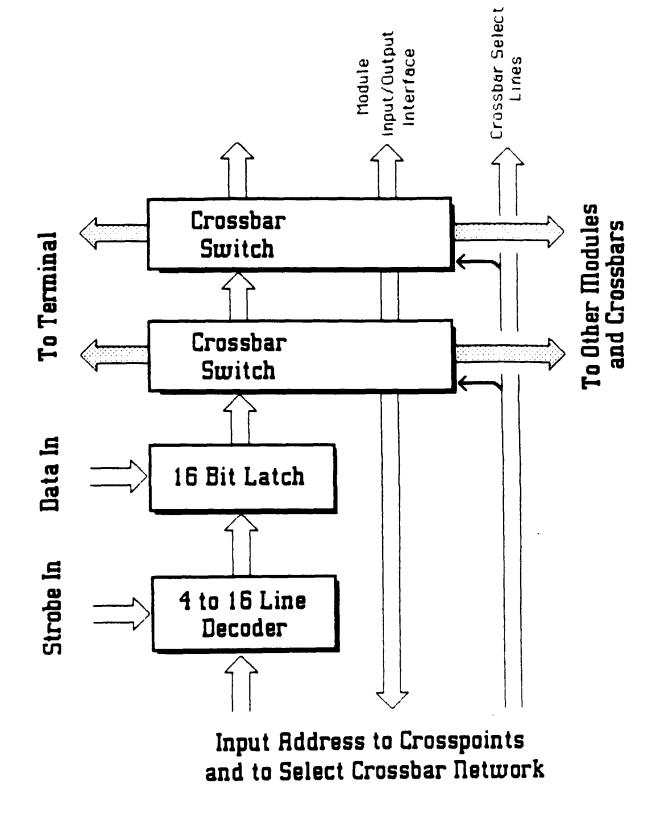

| 8.7                                                                         | Crossbar Addressing Mechanism                                                                                                                                                                                                                                                                                      | 8-16                                                                                                  |

| 8.8                                                                         | Crossbar Functional Diagram                                                                                                                                                                                                                                                                                        | 8-12                                                                                                  |

# CHAPTER ONE

#### CHAPTER ONE

#### INTRODUCTION

#### 1.0 Introduction

There is a general consensus among the computer science fraternity that the 1990's will see the end of the traditional Von-Neumann architecture machine, and that a new generation of general purpose computing machines will evolve.

Most computer architects also see a need for a new generation of system design. Unfortunately, few truly new inititives are forthcoming, as most 'new' designs are based limited extension of the classical Von-Neumann on a computing machine. The research set out in this Thesis has set as its aim a divergence from classical views on computer architecture, to views which may seem radical. This research sees as its starting point the abandonment of classical bounded multi processor computing systems, consisting of say 64 processors. Only with seemingly unbounded systems can we say that computer architecture has developed a new Fifth Generation of computing machinery.

# 1.1 Computer Architecture

Defining what is meant by Computer Architecture is not a simple task. Computer Architecture is not restricted to the sole aspects of hardware. Building black-boxes from registers, memory devices etc., is certainly part of the process, so is the interconnection of these boxes via buses, switches and controllers. A blend of hardware and software features which make the machine operate must also be included. Computer architecture may be defined as the design of the integrated system which provides a useful tool to the programmer. Computer architecture may be defined to mean:-

The internal workings of the black-boxes which are the main components of the system and the means of interconnecting these boxes, their parallel activites and cooperation.

#### 1.2 The Von-Neumann Architecture

The first major architecture was proposed by John Von-Neumann et al. in their 1946 paper, 'Preliminary Discussions of the Logic Design of an Electronic Computing Instrument' [5]. Even with the advent of modern machines [4] most computer architectures bear the mark of this design. Therefore before embarking on any description of the generations of computer architecture, a brief description of the Von-Neumann architectural model is essential.

The Von-Neumann architectural model was conceived for a specific purpose, that of providing a simple stored program execution mechanism to carry out the computations for the solutions of differential equations. The architecture can be said to have the following properties:- 1) A single, sequentially addressed memory. The program and its associated data are stored in a single memory, the memory being referenced with sequential (0, 1, 2, 3,...) addresses.

A linear memory. The memory is one dimensional, that is, it has the appearance of a vector of words.

3) No explicit distinction between instructions and data. Instructions and data are distinguished implicitly by the operations directed toward them.

4) Meaning is not part of the data. There is nothing that explicitly distinguishes a set of bits representing a floating-point number from those representing a character string. The meaning of the data is assigned by the program logic.

# 1.3 Von-Neumann Architectural Implementations

Computer architecture has developed much in the last 30 years, from the Manchester Mark-1 to Seymour Cray's Cray X-MP/2 [13].

The Mark 1 is of historical importance as it was the world's first stored-program computer. The machine marked the beginning of a new technological era. In todays terms the machine posessed the following hardware features:

- 1) A 32-bit word length.

- 2) Serial binary arithmetic (2's complement).

- 3) A main store of 32 words (expandable to 8192).

The main emphasis of the project was to prove the practicability of the Williams Tube for realising the stored program concept and as a result the logic was kept as simple as possible. The subtractor was the only arithmetic element included, as it can perform complements and additions without modification.

The next major step was the prototype construction of the Atlas machines at Manchester University in the 1950's [2]. Atlas-1 and Atlas-2 were eventually produced by the Ferranti Corp. Atlas featured multiple index registers, interrupt processing of I/O devices. Two original features of Atlas, namely a one-level storage and extracode have been copied in many other machines. The one level store is common to most time-shared or multi programmed computers.

Significant features of the Atlas system were:-

1) Provision of a virtual address space greater than the physical address space.

2) Implementation of a one level store using a mixture of core and drum memories.

3) Interrupt system and method of peripheral control.

4) Realisation at the design stage that there would be a complex operating system and provision in the hardware of specific features needed to assist such an operating system.

Computer systems have usually been designed via the 'hardware' route. Subsequent to design, these systems have been handed over to a systems programming team for the development of a package to facilitate the use of the hardware. However the Burroughs B5000 [3] was designed from top to bottom as a total hardware/software system.

The B5000 achieves a unique physical and operational modularity through the use of switches which logically function as crossbar switches. The B5000 was designed as an integrated hardware/software system which offered multiprocessing and parallel processing.

The Digital Equipment Corporation's PDP-8 is of importance as it was the first true minicomputer. The PDP-8 was a single address 8 bit computer. It was the first of a family called the 'OMNIBUS' machines. Like its predecesor, the PDP-5, the PDP-8 was a single address 12-bit [10] computer designed for 'task' environments with a minimum of arithmetic computing and and small memory requirements, i.e process control.

The early constraints placed on computer architects, created computers with what we now regard as faults or weaknesses, namely:-

- 1) Limited addressing capability

- 2) Few registers

- 3) No hardware stack facilities

- 4) Limited priority interrupt structures

- 5) No byte string handling

Page 1-5

- 6) No ROM facilities

- 7) Little I/O processing

- 8) No simple hardware upgrade

- 9) High programming costs (All users use machine code)

The DEC PDP-11 was designed with the above in mind, and successfully [9] overcame these limitations. This was due mainly to the fact that semiconductor technology became available to solve the problems at low cost.

The VAX-11/780 computer system is the first implementation of the [11] VAX-11 architecture, a Virtual Address eXtension to the PDP-11 architecture. The most distinctive feature of the VAX is the extension of the virtual address from 16 bits, as on the PDP-11, to 32 bits; giving an address space of some 4.3 gigabytes. Since maximum PDP-11 compatibility was a design objective, the VAX includes a compatibility mode which provides the basic PDP-11 instruction set, without the privileged instructions.

#### The IBM System/360 and System/370

The System 360 was the first planned computer family to cover a range [1] of cost and performance. The 360 predecessor, the 7090, ran into problems later encounterd by the PDP-8, namely limited growth potential. Rather than 'fiddle' with the architecture IBM planned a family of processors with growth potential for the future. The initial family plan called for a wide range of cost and performance implementations, microcode being used to provide emulation support for prior systems. The motivation to extend the 360 architecture came from two main sources:-

1) The experience of the 360 achitecture has identified a number of bottlenecks and limitations in the efficiency of system use has pointed out areas where additional machines were needed.

2) The lowering of the cost of technology made it economically possible to include functions that did not appear justified in the original 360 architecture.

The most interesting aspect of the 360-370 design is achieving a performance range and a primary memory size range in excess of 100:1.Thus the user is given a very large range of configuration alternatives.

#### 1.4 Fifth Generation Computer Research

Japan's capability for producing high quality electronic products is well known. It therefore came as a shock when in 1981 the Japanese announced to the World a programme of research into Fifth Generation computing systems. This was the responsibility of The Japanese Ministry of International Trade and Industry, MITI [8].

#### 1.4.1 Japanese Activity

In 1982 Supercomputers were an American exclusive. Today, Japanese firms are offering machines that challenge, and in some ways exceed, the performance of those American machines. This has been due mainly to the fact that MITI has decided that Japan must learn to innovate, not just copy and improve on existing technology.

MITI's development plans for fifth Generation computers started in 1982. The budget for the years 1982-1984 being some 10 billion Yen. The Institute for New Generation Computer Technology (ICOT) has been created to spearhead Japanese efforts in the field, and has been succesful in designing and building an Inference Machine and a Database Machine.

However, NTT is the only Japanese company trying to develop a true [12] parallel processor. Two types of dataflow are under study; one is a highly parallel array processor for scientific calculations, the other is an architecture designed to apply data-flow techniques to list processing.

#### 1.4.2 The Alvey Programme

The Japanese initative produced a number of responses around the word. The most notable was The UK's Alvey Committee, which producd a number of goals for Britan's involvements in fifth Generation computing systems. The Alvey Programme was set up as a result of the Alvey Committee report, (A Programme for Advanced Information Technology), in 1982. The Programme aims to mobilise the United Kingdom's strengths in Information Technology, (IT), in order to improve the UK's competitive position in the World's IT market. The research programme is a collaborative effort between Government, industry, academic and commercial research units. The Programme combines projects in four main technology areas.

The four enabling areas are:-

1) VLSI

The requirement for massively parallel systems demands a VLSI approach to building systems. VLSI gives the capability of interconnecting the very large number of logic elements required for data and signal processing.

2) Software Engineering

Fifth generation computing systems will tend to be more complex than present day systems. This will result in a longer time delay in generating and maintaining proposed fifth generation programs. Therefore, Software Engineering is aimed at improving the efficiency of the specification, generation and maintenance of the program instructions for IT systems.

3) Intelligent Knowledge Based Systems

One major area of activity is the design of intelligent machine/software systems. These systems should be adaptive systems capable of learning. The object is to produce inference systems that can be incorporated in education, medicine, military, etc.

#### 4) The Man-Machine Interface

The proposals of 'Alvey' clearly imply that computing systems will be applied to new application areas, possibly with new methods for input and output. The wider aspects of the involvement include <u>psychological</u> aspects of using complex systems.

Specifically, this section covers visual, speech, touch input-output devices and the better understanding of the nature of communication between the user and the machine.

Following Japan's initative, the United States and Europe have started various research programmes into fifth Generation design. Most countries are in an early stage of development and are desperately trying to catch up on Japan's early lead. One question remains unanswered; are the claimed fifth Generation systems truly advances on the older technologies, or simply refinements of proven systems?

### 1.5 Thesis Plan

Following a brief introduction to Computer Architecture and the area of the proposed fifth Generation computing in chapter 1, chapter 2 presents a critique of architectures from the previous generations presenting a new possible classification scheme for the architectural generations, independant of technology. The chapter also examines the reasons why the Von-Neumann architecture is in need of replacement, and examines some of the machines which have tried to overcome its limitations. Chapter 3 looks at the new application requirements of a fifth Generation computer system, and criticises some of the so called fifth Generation machines.

Chapter 4 examines the problems of bus contention brought about by large numbers of processors and offers some solutions to this problem. This chapter presents bus interconnection patterns in the context of maximising bus traffic in fully distributed systems.

In chapter 5, an introduction to a Polymorphic, Space Sharing [6] Computer System, called the Group Processor System, is given. Details of the functions performed within the Group the components of Processor's homogenous architecture and the interaction within the organisational structure are presented. The design claims to overcome the two basic problems isolated by the Data Flow Group atU.C. Irvine [7] namely data localisation and concurrent bus access. This architecture is able to emulate a data driven machine.

Chapter 6 presents an introduction to the various methods of system performance measurement and gives a detailed simulation environment for hierarchical system interconnection. Moreover, the simulator is concerned with the dynamic environment generated by the execution Group Processor System environment.

Chapter 7 examines results from the simulator for various system configurations. The simulator provides a 'window' on the program environment within the Group Processor System, this yields important data used to optimise the Group Processor System architecture. This chapter highlights one major weakness of Quick's original design concept for the Group Processor System, that of real time input/output under heavy loading.

The proposed architecture presented by Quick [6] provided detail into the working architecture of the basic Group Processor System. However, many areas of the bus system were left for refinement, and these are studied in this Thesis. The results of the study have enabled the next chapter, chapter 8, to propose many important system tuning features to be employed in engineering the Group Processor System. The chapter proposes a new design for the input/output system of the Group Processor System.

The final chapter, chapter 9, contains conclusions drawn from this research. Specifically, the areas of computer architecture, fifth Generation Computer Architecture, system simulation and system performance are discussed.

Each chapter is complete with references at the end of the chapter. The references are presented in the UNIX format.

#### 1.6 Scope of the Thesis.

This research continues the abandonment of the Von-Neumann architecture, for an architecture more radical in concept. Polymorphic systems provide the necessary degree of reliability needed for real time control systems coupled with a high degree of resource utilisation. The major advantages of the Polymorphic 'Group Processor System' is its massive parallelism. While the Group Processor System seems to offer a solution to current problems in IKBS, some potential problems arise when 'engineering' the system. These areas are addressed in this Thesis by simulating the bus interaction for various bus scheduling schemes and system configurations. The results drawn from this Thesis provide the information needed to proceed with the next stage of the Group Processor System, namely circuit and software design.

# References - Chapter 1

1. IBM Corporation, "A Guide to the IBM System/370", 5th Edition 1976.

2. SUMNER, F., HALEY, G., AND CHEN, E., "The Central Control Unit of th ATLAS Computer", PROC IFIP 1962.

3. LONERGAN, W., AND KING, P., "Design of the B5000", Datamation V7 N5 1961.

4. SIEWIOREK, D., BELL, G., AND NEWELL, A., "Computer Structure: Principles and Examples", McGraw-Hill 1982

5. BURKS, A.W., GOLDSTINE, H.H., AND VON-NEUMANN,J., "Preliminary Discussion of the Logic Design of an Electronic Computing Instrument", Pt 1. No.1, Princeton N.J. 1946.

6. QUICK, G.E., "The Group Processor Approach Computer Architecture", Ph.D Thesis, UC Swansea 1982.

7. GOSTELOW, K.P. AND THOMAS, R.E., "Performance of a Dataflow Computer.," UC Irvine TR 127a.

8. MOTO-OKA, T., "Fifth Generation Systems," North Holland 1982.

9. DIGITAL, "PDP-11 Hardware Handbook", 1977.

10 BELL, G., MUDGE, J., AND MCNAMARA, J., "A DEC View of Hardware System Design", Digital Press 1978.

11. DIGITAL, "VAX-11/780 Hardware Handbook", 1982-3.

12. NATO Conference on Relational Database Architecture, Les Arcs, France 1985.

13. LUBEK, O., MOOR, J. AND MENDEX, R., "A Benchmark of Three Supercomputers: Fujitsu VP-200, Hitachi S810/20 and Cray X-MP/2", IEEE Computer 1984

# CHAPTER TWO

#### CHAPTER TWO

#### THE FOUNDATIONS OF COMPUTER ARCHITECTURE

# 2.0 Introduction

Many of the designs for computing systems have been centred on a typical system architecture comprising of a central processor (or some finite multiple up to say 16), random access memory, input-output processors, and some backup storage such as magnetic disk or tape. Highly reliable systems, such as the Tandem [17] have been an extension to these systems by incorporating some form of redundancy in one or more parts of the design.

The more "classical" designs are based on Von-Neumann's architecture, which have received criticism from some researchers [3,21,7]. A number of variations on the Von-Neumann architecture has resulted in many and multi-computer organisations multi-processor [1,4,24,14,19,30,32,33]. In developing an alternative design, researchers have proposed several alternative architectures [2,8,13,26,28]. These architectures can be best described as non sequential; they have tried to deviate from the classical Von-Neumann machine.

#### 2.1 Why a new generation of computers?

With few exceptions, there have been no advances in computer architecture of current systems since the 1950's.

An argument against this is the introduction of such concepts as microprogramming, VLSI, pipelining and cache memories. However, these do not represent architectural concepts, but merely advances in the implementation of particular current architectures.

In comparing the architectures of the most widely used machines;

e.g. IBM S/370 S/34, DEC PDP/11, VAX etc

to the EDSAC and EDVAC, the first electronic stored program computers, all the significant differences will be found to have originated in the 1960's. Which were:-

- 1) Index registers

- 2) General purpose registers

- 3) Floating point data representation

- 4) Indirect addressing

- 5) Interrupts

- 6) Asynchronous input-output

- 7) Virtual storage

- 8) Multi-tasking

Although current systems differ significantly from their predecessors in terms of cost, speed, reliability, internal organisation and circuit technology, the computer architecture of most current systems has not advanced beyond the concepts of the 1950's.

Given this state of affairs the following must be asked:-

1) Are the architectures of the 40's and 50's the optimal ones for today?

2) Is not todays world different, measured in cost of logic, speed, sophistication of computer application and magnitude of the software problem, and that changes in computer architecture are needed?

If the above points are valid, we must put forward some evidence why a new approach is necessary.

#### 2.2 The Semantic Gap

Most of the shortcomings in todays machines are due to the 'Semantic Gap'. The Semantic Gap was originally defined to be a measure of the difference between concepts in current high level languages and the underlying concepts in computer architecture [20].

Todays systems have an uncomfortable semantic gap in that objects and operations reflected in their architecture are rarely closely related to the objects and operations provided by the programming languages. In broadening the definition of the semantic gap, it may be said that there is a large gap in semantics between programming environments and their representation of the program concepts at the architectural level.

#### 2.2.1 The Operating System Semantic Gap

The operating system is an integral part of most computing systems. In general the operating system has four purposes:-

1) Providing utility services to other programs, such as storage allocation for the execution of large programs.

2) Shielding programs from such items as interrupts, machine interfaces etc. for software portability.

Providing, at varying levels of sophistication, a

'virtual machine' concept.

4) Creating and enforcing system managemant policies.

A case can be built for a gap between the operating system concepts and the underlying machine. For instance, many operating systems designers recognise that the working set model is crucial to managing a storage hierarchy in a close to optimal manner. Although instrumentation required to do this has been identified it exists in no commercial architectures.

# 2.2.2 The Programming Environment Semantic Gap

Evidence can be found of a large gap between fundamental notions of programming and most computer architectures. For instance, such concepts as modularity, abstract data types [22], information hiding, and monitors are important in the design of large software systems, but support for these concepts is missing from today's architectures.

### 2.2.3 The Storage Semantic Gap

This gap is more difficult to see as it represents a gap that does not exist. The operating system architects have obscured the gap by falling into it. The issue here is the lack of a uniform concept of storage. The programmer is faced with a visable hierarchy of registers, stacks, RAM, tapes etc. Each medium has a different addressing mechanism, allocation machanism etc. It is for the wrong reason that the gap does not exist. Rather than presenting the high level language programmer with a uniform notion of storage, one is presented with a number of inconsistent concepts which are technology dependant.

# 2.2.4 Consequences of the Semantic Gap

The semantic gap is a significant contributor to software unreliability in the sense that a large set of programming errors that could be theoretically prevented or detected by the computing system are not prevented or even detected in current systems, i.e array bound checks, references to undefined or unset variables.

#### 2.3 The Von-Neumann Architecture

The basic reason for the semantic gap in current systems is that their architectures do not significantly differ from the Von-Neumann model developed in the 1940's. We may class all current machines as being of the Von-Neumann type.

Although the von Neumann architecture was a reasonable architecture for the first stored-program computer, it is alien to the execution of programs writen in high level languages.

In contrast to the four main characteristics of a Von-Neumann architecture given in Chapter-1, high level languages have the following characteristics:-

1) Storage is presented as a set of discrete named variables. There is no concept of one variable being 'next' to another. There is no reason to believe that variables in one subroutine are located in the same storage device as the variables in another. In short, the concept of a single sequential storage bears little resemblance to the concept of storage in programming languages.

2) Programming languages deal with multi-dimensional, not just linear, data types.

3) In programming languages there is a sharp distinction between data and instructions.

## 2.4 Parallel Systems

Some of the architectures which have moved away from the Von-Neumann mode are multi-processor and multi-computer systems. However, there is some confusion as to the definition of such term. Some clarification and extension of notation is first required.

#### 2.5 Multi-Processor Systems And Attributes

One of the fundamental problems with traditional multi-processor configurations is the interconnection of memories and processors, and also their interconection to the outside world. This section analyses the attributes of multi-processor computer systems.

# 2.5.1 Multi-Procssor Computer Systems

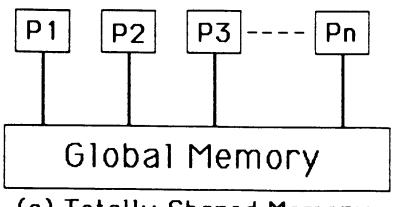

This section discusses the clasification of various multi processor computer system schemes available to the computer architect, with reference to reliability. A "black box" approach, synonymous with the integrated circuit will be used to represent the micro partitioning of systems, e.g. processor, memory, etc. Macro partitioning is used to represent a stand alone general purpose, i.e. non specialised, computer system. The figures in this section, i.e. figures 2.1. and 2.2., are single user systems which are either a host mainframe or user terminal.

(a) Totally Shared Memory

(b) Limited Shared Memory

Figure 2.1 Single User Tightly Coupled Computer System

#### 2.5.2 Tightly Coupled Computer Systems

A tightly coupled Computer System [17], is a multiple processor, shared memory, computer system. Figure 2.1.a. shows a "totally shared memory" structure, while figure 2.1.b. shows a "limited shared memory" structure.

The major advantage of the totally shared memory is its inherent flexibility. best is illustrated This by considering a processor, say P2, as failed. From figure 2.1.a., any other processor may address each others memory space during a recovery process. By comparison, recovery is difficult in figure 2.1.b, where the recovery process has to access the local memory, i.e. M2. However, the provision of local memory does provide a closed process environment, resulting in the confinement of processing errors to the local memory. Local memory provides an additional speedup [33] in computation, because contention for shared memory access is reduced.

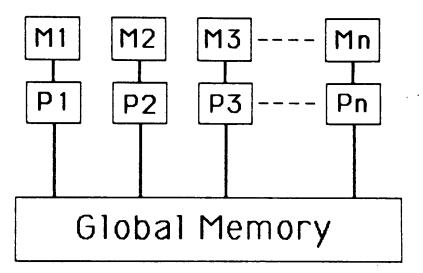

#### 2.5.3 Loosely Coupled Computer Systems

Loosely Coupled Systems [10] are multiple computer systems in which there is no shared memory, and all inter processor communication takes place through input-output channels.

Loosely Coupled Systems have more structure than Tightly Coupled Systems because their inter processor communication is intelligent. This enables intelligent inter process communication between communicating processes, at the machine level, e.g. through input-output channels. This is not possible in Tightly Coupled Computer Systems, as any processor may access any location in the shared memory, e.g. when a faulty processor writes to an output area of another processor, producing systemic process corruption.

#### 2.6 Multi-Processor Classifications

Multi-Processor Classification has enabled a classification scheme to represent inherent qualities of two dissimilar system structures. When considering the execution of a program, as an execution of communicating processes in the single user systems of figure 2.1. and 2.2., the Tightly Coupled Computer Sytems offers a more reliable programming environment through its closed, i.e. local, memory architecture.

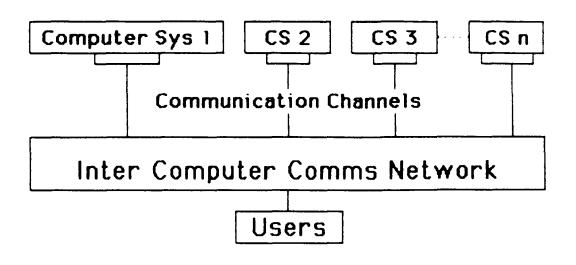

In a multi user interactive system, employing a multi-processor architecture, the input-output to the user terminals is performed by a fast, uni-processor based, communication processor. This type of system is shown in figure 2.3. While the execution environment of figure 2.3 is more reliable than the conventional uniprocessor systems, the reliability of the front-end communication processor is a single point of failure. With this in mind, the ideal multi-user, multi-processor machine provides a process execution environment which is loosely coupled, together with a loosely coupled input-output to the system users.

Figure 2.2 Single User Loosely Coupled System

Figure 2.3 Multi-User Multi-Processor Computer System

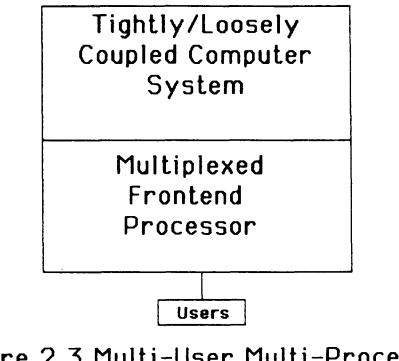

Quick proposes a change in the system classification scheme which includes [12] input-output architecture to the execution environment. The Tightly/Loosely Coupled Computer Systems shown here, together with Flynn's classification [11] e.g. Multi Instruction Multi Data - MIMD, require extension, or clarification.

The extended classification is:-

1 (a) Tightly Coupled, Single I/O (i.e. Single channel I/O)

(b) Tightly Coupled, Parallel I/O (i.e. Multiple channel

I/O)

2 (a) Loosely Coupled, Single I/O (i.e. Single channel I/O)

(b) Loosely Coupled, Parallel I/O (i.e. Multiple channel I/O)

Relating the above classifications to fifth generation requirement; the system structure would have the input-output equivalent of 1(b) or 2(b).

The proposals for fifth generation architectures requires a move away from the multiplexed front-end processor. The multiplexed input-output channel does not offer the speed required for the fifth generation human interface. Dedicated input-output channels seem to be the only mechanism capable of matching applications to architectural requirement.

#### 2.7 Bounded Parallel Systems

A machine architecture is bounded if there are up to, say 64 processors where the architecture is defined in terms of maximum system configuration. That is, the maximum number of processors that can be integrated into the system is 64.

The limiting factors here are based on technological limitations such as pinout numbers on integrated circuits. Bounded systems tend to be cheaper designs than more flexible unbounded systems.

#### 2.8 Unbounded Parallel Systems

A machine architecture is unbounded if it is designed with maximum flexibility and extensibility as a fundamental system requirement. Such systems should be capable of supporting in excess of 10,000 processors, and ideally millions of processors. In reality; it is difficult to design systems that are truly unbounded. The physical interconnection of the main components require a fixed of hardwired connections. An unbounded number interconnection scheme demands maximum flexibility in the interconnection, and hence requires soft and not hard connections. It can be said that they approach the unbounded state.

#### 2.9 Engineered Bounded Systems

Four architectures which have moved away from the classical uni-processor architecture.

1) The VAX-11/782

2) The Burroughs B5000

3) The iAPX-432

4) C.mmp

#### 2.9.1 Multi-processor Configurations of the VAX-11/780

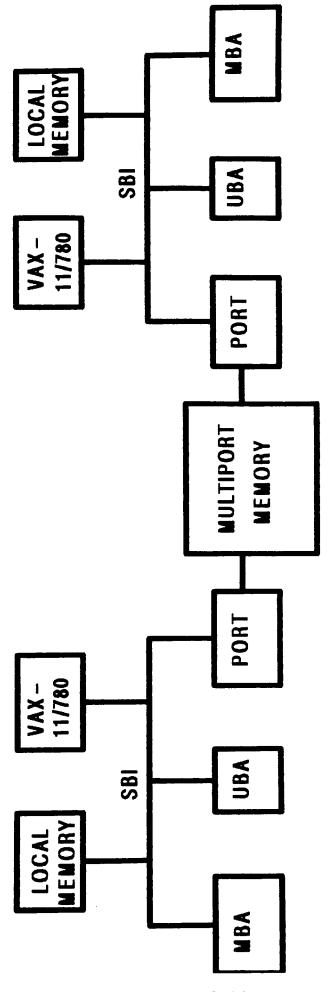

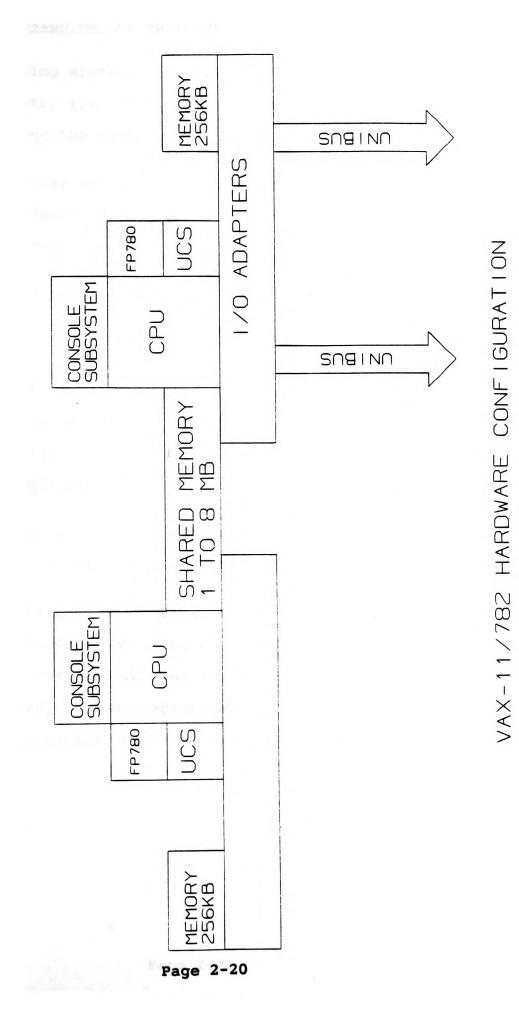

The simplest multi-processor configuration of the VAX family is the [35] VAX-11/782, a tightly coupled asymmetrical multi-processor. The 782 is based on two 780 processors using the MA780 shared memory subsystem (Figure 2.4).

At the centre of all VAX multi-processors is the multiport memory. This enables up to four VAX processors to share a bank of memory. This feature allows VAX users to develop multi computer configurations for very high throughput or enhanced availability.

Applications built around multiple cooperating processes can be configured to run on multi-processor systems with no programming modification. Processes in shared memory can be moved from one processor to another with complete transparency to the programs involved.

Page 2-16

An interesting point to note is that each processor in the multiport system operates independantly using its own copy of the operating system stored in its local memory. This 'local operating system' is discussed further in chapter 5.

Port Arbitration

The high throughput of VAX multi-processor configurations is due to each port having a buffer for commands and data. Each port is served on a demand basis, that is, first-in first-served. No time is wasted in polling inactive ports. A serving algorithm guarantees that no port waits more than three memory cycles to gain access to shared memory.

A problem associated with multiport memory is that of one processor trying to read a location at the same time another is trying to modify it. The VAX eliminated this contention by locking out the second processor until the first has completed the transaction.

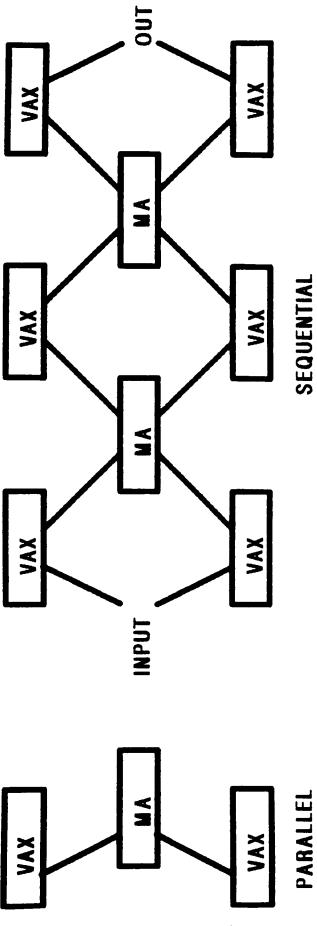

Parallel and Sequential Procesing

The multiport memory of the VAX can enhance system performance via two configurations:-

1) Parallel or 2) Pipeline processing.

Figure 2.5

# PARALLEL AND SEQUENTIAL VAX CONFIGURATIONS

Page 2-18

In the parallel mode; two or more processors divide the task between them, allowing processors to pool resources. Pipelining can increase total system throughput by allowing instantaneous data exchange between processors that are handling the sequential parts of an application. The following figure (Fig 2.5) illustrates possible configurations.